# Compiler Optimizations for Energy-Efficiency of Heterogeneous Computing Systems

(ヘテロジニアス計算機システムの電力効率向上のためのコンパイラ最適化手法)

薦田 登志矢

© 2014 - Toshiya Komoda ALL RIGHTS RESERVED.

## **Abstract**

Energy-efficiency has become one of the most important metric in recent computing systems. Power consumption of a large scale computing center is reaching to the physical limitation of power supply systems. Now, we have to scale system performance without increasing power consumption. To this end, heterogeneous systems with accelerators are becoming popular due to its high performance and its high energy efficiency. Peak performance and peak energy-efficiency of such systems are much higher than those of conventional homogeneous systems. However, it is not easy to achieve high energy-efficiency in practical situations because the actual energy efficiency highly depends on the optimizations used in the applications.

To get great performance from accelerators in practical situation, it is important to provide an easy programming environment to use accelerators. This is because the performance improvement is limited to a fraction of program codes which are not accelerated. To encourage programmers to utilize accelerators, programming environments should provide simple and high level abstraction of the underlying heterogeneous systems. However, current programming environments only provide low level and complicated APIs for users. Hence, we have to develop simpler and high performance programming environments in heterogeneous systems with accelerators.

Also, to draw the maximum energy-efficiency from the systems, it is also necessary to reduce unnecessary power consumption. For example, leakage power consumed in processors should be taken into account. Plus, it is not necessary to execute tasks which are not on critical paths with the highest processor frequency. In homogeneous systems with CPUs, such power consumption has been successfully reduced by power gating (PG) and dynamic voltage and frequency

scaling (DVFS). However, it is unclear that how we should maximize the effectiveness of these techniques in heterogeneous systems with accelerators.

To this end, in this dissertation, we propose three new optimization techniques for the accelerator compilers in order to solve these problems. The three techniques can be orthogonally applied to applications running on heterogeneous systems. And each technique independently contributes to improving the energy-efficiency of the system.

First, to ease the programming process in accelerator platforms, we propose a directive based compiler which utilizes multiple accelerators automatically. The compiler provides single monolithic memory space on top of discrete accelerator memories, and programmers can transparently utilize multiple accelerators. The experimental in a machine with 2 GPUs show that the proposed compiler reduce 68% of the code lines in utilizing 2 GPUs while it achieves 71% of the performance compared to hand-written CUDA programs

Second, to reduce leakage power in CPU functional units, we propose a compiler directed sleep control technique. Using a static analysis, the proposed sleep control technique can effectively reduce leakage power in CPU functional units. The experimental result shows that the proposed technique can reduce 23.6% of leakage power compared to a conventional sleep control.

Finally, to avoid inefficient executions due to load imbalance between CPUs and accelerators, we investigate a runtime software technique with which we can utilize both CPUs and accelerators in parallel. In addition to balancing load between CPUs and accelerators, the proposed technique can cooperatively control the device frequencies and the task mapping between CPUs and accelerators to further optimize energy-efficiency of the system. The experimental result shows that the proposed technique achieves up to 14.4% higher performance compared to other power capping techniques where the task mapping is not orchestrated with the device frequency settings.

Through these experiments about the three proposed techniques, we demonstrate that compiler optimization techniques can greatly help us achieve high energy-efficiency in heterogeneous systems with accelerators.

# **Contents**

| 1 | Intr       | oductio | n                                                         | 1  |  |

|---|------------|---------|-----------------------------------------------------------|----|--|

|   | 1.1        | Proble  | ems for Improving Energy-Efficiency                       | 2  |  |

|   | 1.2        | Contri  | bution                                                    | 4  |  |

|   |            | 1.2.1   | Improving Programmability (Chapter 3)                     | 5  |  |

|   |            | 1.2.2   | Reducing Leakage Power (Chapter 4)                        | 6  |  |

|   |            | 1.2.3   | Reducing Dynamic Power (Chapter 5)                        | 6  |  |

|   | 1.3        | Organ   | ization of the Dissertation                               | 7  |  |

| 2 | Background |         |                                                           |    |  |

|   | 2.1        | Hetero  | ogeneous System                                           | 9  |  |

|   |            | 2.1.1   | GPU Computing Server                                      | 10 |  |

|   |            | 2.1.2   | Other Examples of Heterogeneous Systems with Accelerators | 10 |  |

|   | 2.2        | Progra  | amming Model for Accelerators                             | 12 |  |

|   |            | 2.2.1   | CUDA and OpenCL                                           | 12 |  |

|   |            | 2.2.2   | OpenACC                                                   | 13 |  |

|   | 2.3        | Power   | Management Technique                                      | 14 |  |

|   |            | 2.3.1   | Power Gating                                              | 15 |  |

|   |            | 2.3.2   | DVFS                                                      | 16 |  |

|   |            | 2.3.3   | Power Capping                                             | 17 |  |

| 3 | Mul        | ti-Devi | ce Execution in a Directive Based Compiler                | 19 |  |

|   | 3.1        | Drawb   | backs of Current GPU Programming Environments             | 19 |  |

iv CONTENTS

|   | 3.2  | Open A   | ACC Compiler with Software Distributed Shared Memory   | 21 |

|---|------|----------|--------------------------------------------------------|----|

|   |      | 3.2.1    | Directive Extensions                                   | 22 |

|   |      | 3.2.2    | Implementation and Optimization in multi-GPU platforms | 25 |

|   | 3.3  | Evalua   | tion                                                   | 31 |

|   |      | 3.3.1    | Performance and Programmability                        | 32 |

|   |      | 3.3.2    | Evaluation in a Supercomputer Node                     | 37 |

| 4 | Con  | ıpiler B | ased Sleep Control in CPU Functional Units             | 41 |

|   | 4.1  | Drawb    | acks of Conventional Sleep Control Techniques          | 41 |

|   | 4.2  | Sleep    | Control Based On Precise Analysis of Idle Length       | 43 |

|   |      | 4.2.1    | Architecture Support for Compiler Based Sleep Control  | 45 |

|   |      | 4.2.2    | Code Analysis to Detect Fine-Grained Idle Periods      | 45 |

|   | 4.3  | Evalua   | tion                                                   | 50 |

| 5 | Coo  | perative | e DVFS and Heterogeneous Task Mapping                  | 55 |

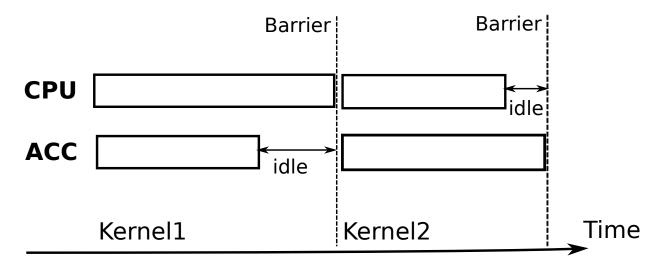

|   | 5.1  | Drawb    | acks of Conventional Power Capping Techniques          | 55 |

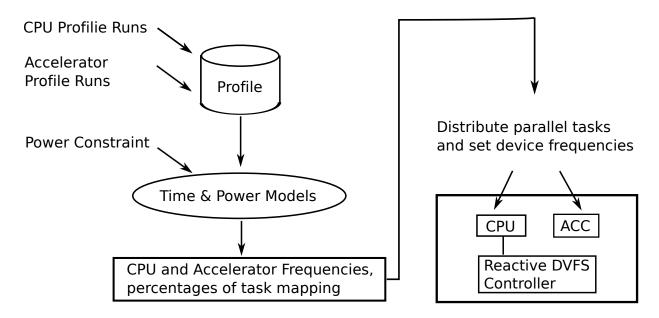

|   | 5.2  | Model    | -based DVFS and Task Mapping                           | 57 |

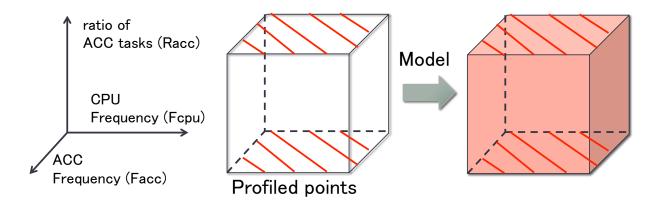

|   |      | 5.2.1    | Model Parameters and Profile Information               | 58 |

|   |      | 5.2.2    | Empirical Models                                       | 60 |

|   |      | 5.2.3    | Parameter Selection                                    | 62 |

|   | 5.3  | Evalua   | tion                                                   | 63 |

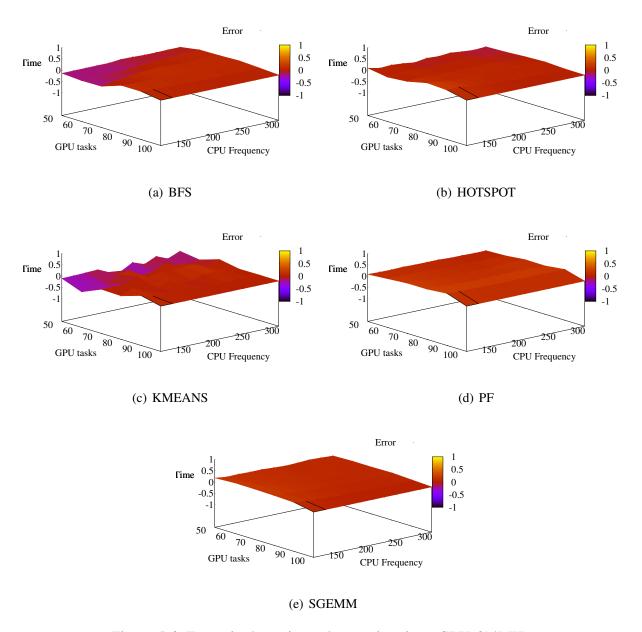

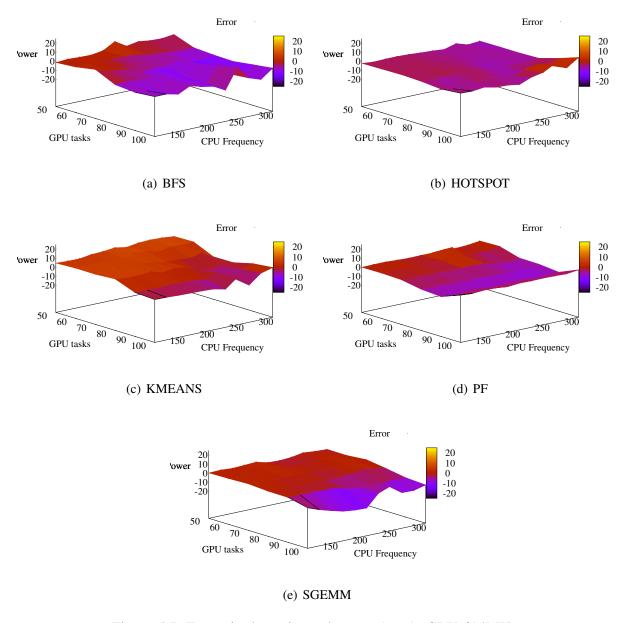

|   |      | 5.3.1    | Model Verification                                     | 64 |

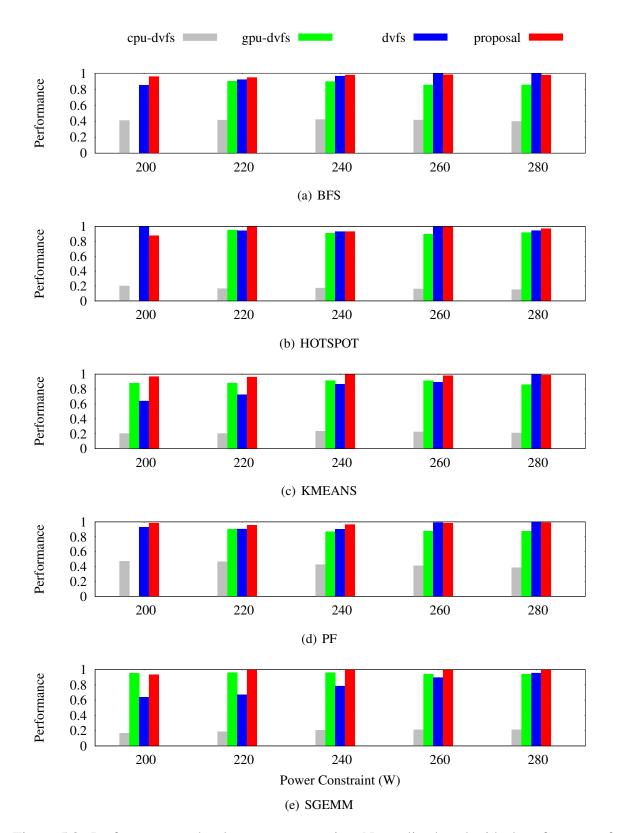

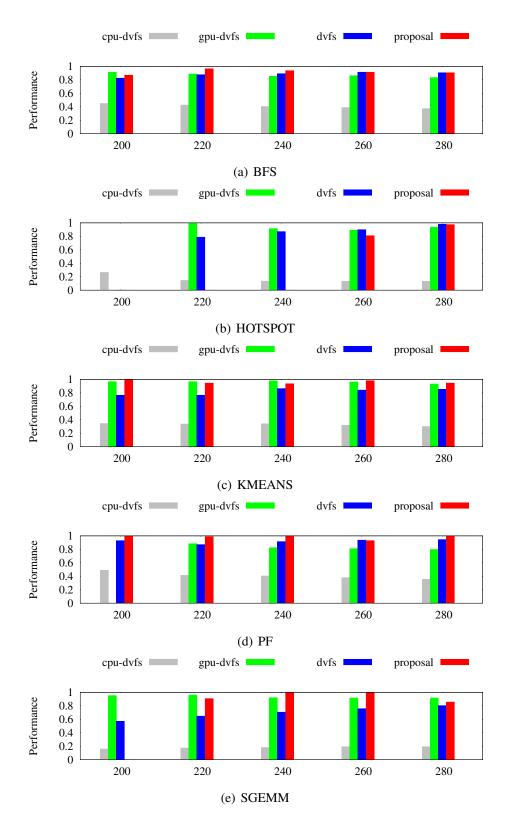

|   |      | 5.3.2    | Performance Under the Power Constraint                 | 65 |

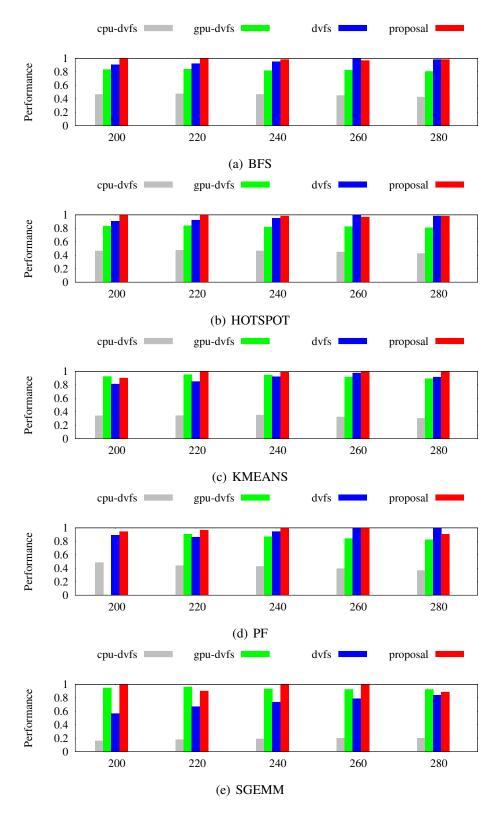

|   |      | 5.3.3    | Sensitivity on Different Input Data                    | 68 |

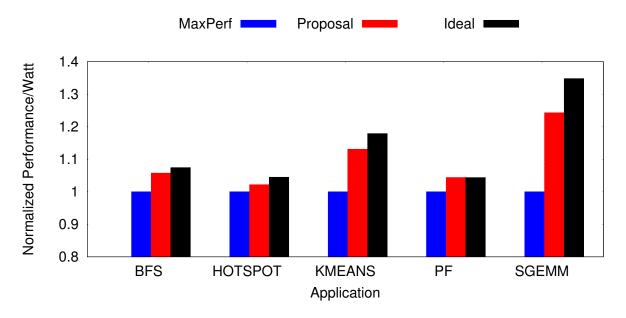

|   |      | 5.3.4    | Optimizing for Energy-Efficiency                       | 70 |

| 6 | Disc | ussion   |                                                        | 75 |

|   | 6.1  | Combi    | nation of the Proposed Techniques                      | 76 |

|   | 6.2  | Extens   | ion to Other Heterogeneous Systems                     | 77 |

| CONTENTS | V |

|----------|---|

|----------|---|

| 7            | Related Work   |                             |    |  |  |

|--------------|----------------|-----------------------------|----|--|--|

|              | 7.1            | GPU Programming Environment | 81 |  |  |

|              | 7.2            | Runtime Power Gating        | 83 |  |  |

|              | 7.3            | Power Capping               | 83 |  |  |

| 8 Conclusion |                | clusion                     | 85 |  |  |

| Ac           | Acknowledgment |                             |    |  |  |

| Bil          | Bibliography 8 |                             |    |  |  |

# **List of Figures**

| 1.1  | Trends of power and energy-efficiency of supercomputers in Top500 (extracted |    |  |

|------|------------------------------------------------------------------------------|----|--|

|      | from Green500 web site [1])                                                  | 2  |  |

| 2.1  | Heterogeneous computing system                                               | 10 |  |

| 2.2  | An example of CPU-GPU heterogeneous systems                                  | 11 |  |

| 2.3  | CUDA vector addition                                                         | 13 |  |

| 2.4  | OpenACC Vector Addition                                                      | 14 |  |

| 2.5  | Power gated circuit and the power transition during sleep mode               | 16 |  |

| 3.1  | Comparison of current GPU programming environments                           | 20 |  |

| 3.2  | Overview of the proposed multi-device OpenACC compiler                       | 22 |  |

| 3.3  | Execution steps of parallel loops in the proposed system                     | 23 |  |

| 3.4  | An simple example of the proposed directives                                 | 24 |  |

| 3.5  | An overview of the prototype system                                          | 26 |  |

| 3.6  | A flowchart to determine the placement policy of each array                  | 29 |  |

| 3.7  | Two-level dirty-bit mechanism to keep consistency of the replicated arrays   | 30 |  |

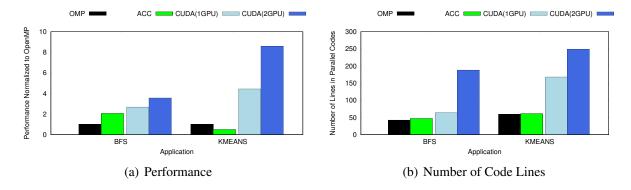

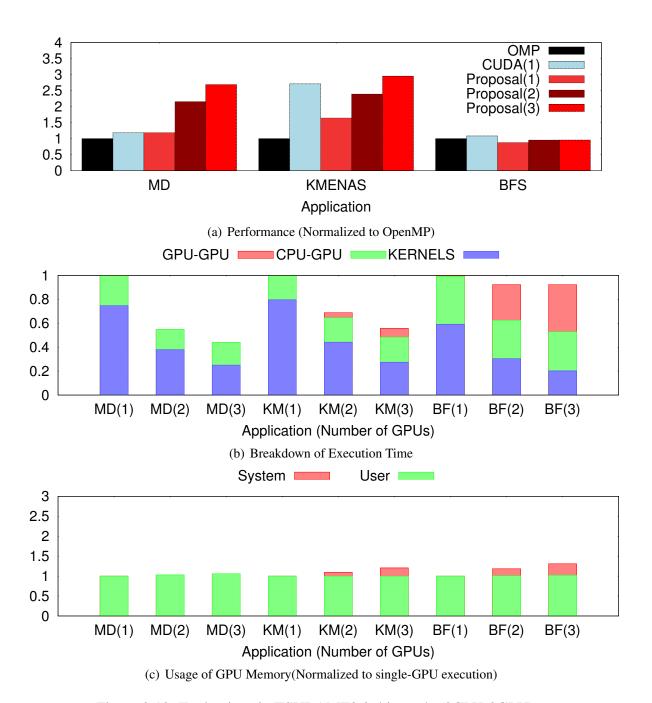

| 3.8  | Performance and lines of code (LOC). Normalized to the CUDA 2GPU versions.   | 33 |  |

| 3.9  | Performance trends when the size of input data changes. Normalized to the    |    |  |

|      | CUDA 2GPU versions with base inputs                                          | 34 |  |

| 3.10 | Evaluations in TSUBAME2.0 thin-node (2CPU-3GPU)                              | 39 |  |

LIST OF FIGURES vii

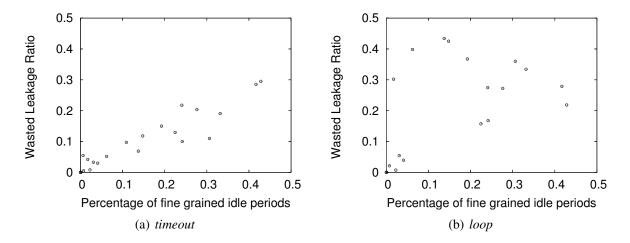

| 4.1  | Correlation between fraction of fine grained idle periods and $WLR$ (BET=20      |    |

|------|----------------------------------------------------------------------------------|----|

|      | cycles)                                                                          | 43 |

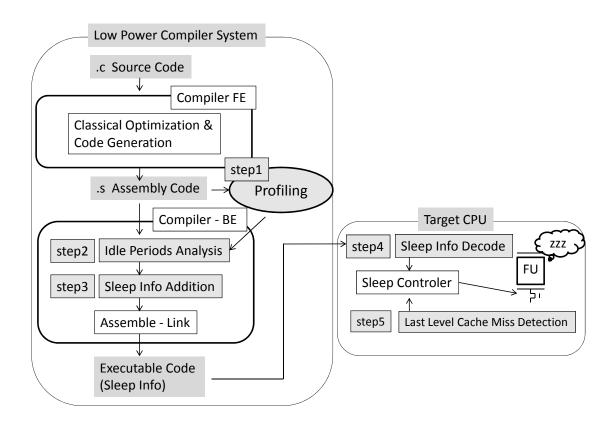

| 4.2  | An overview of the proposed sleep control system                                 | 44 |

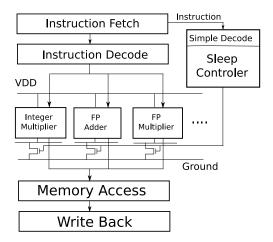

| 4.3  | Architectural support for run-time PG in functional units                        | 45 |

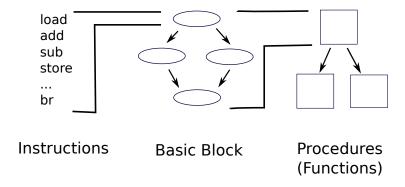

| 4.4  | Structures in programs                                                           | 46 |

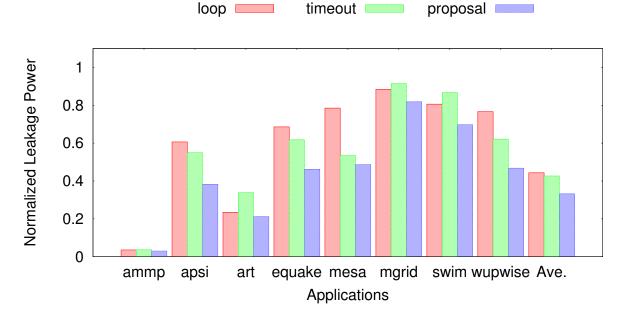

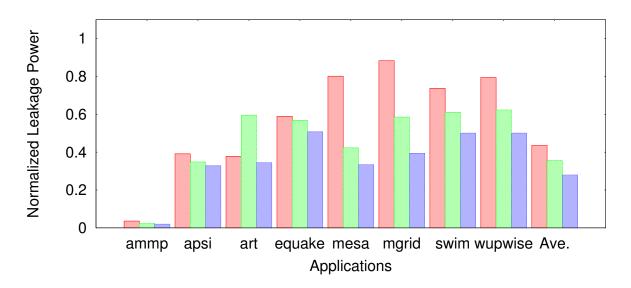

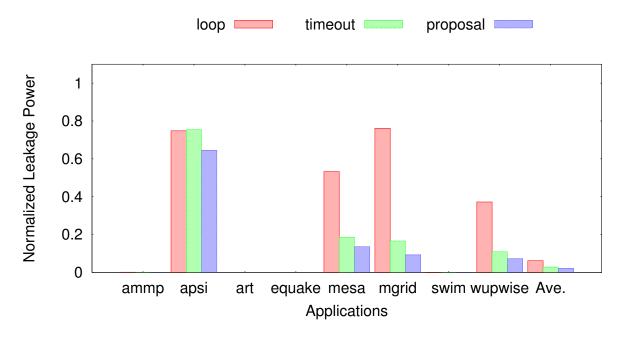

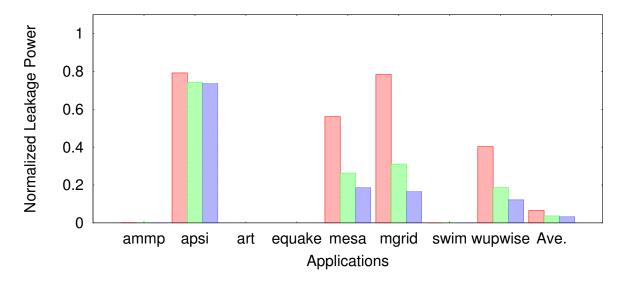

| 4.5  | Normalized leakage power (BET=20cycle, FPALU)                                    | 52 |

| 4.6  | Normalized leakage power (BET=40cycle, FPALU)                                    | 52 |

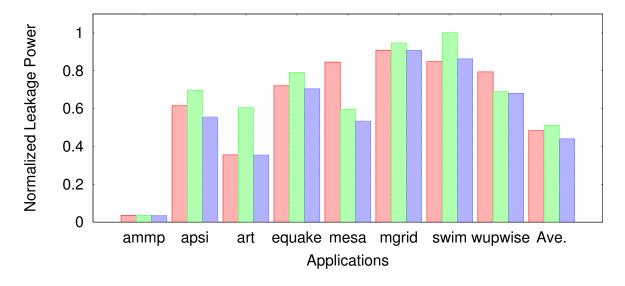

| 4.7  | Normalized leakage power (BET=20cycle, FPMULT)                                   | 53 |

| 4.8  | Normalized leakage power (BET=40cycle, FPMULT)                                   | 53 |

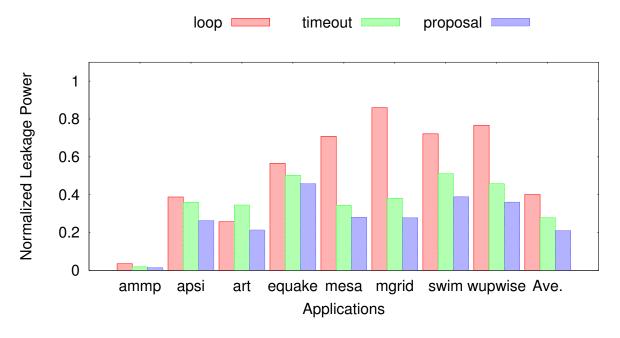

| 4.9  | Normalized leakage power (BET=20cycle, INTMULT)                                  | 54 |

| 4.10 | Normalized leakage power (BET=40cycle, INTMULT)                                  | 54 |

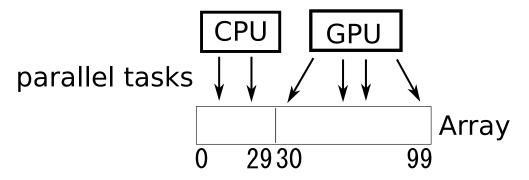

| 5.1  | Hybrid computation with a CPU and a GPU                                          | 56 |

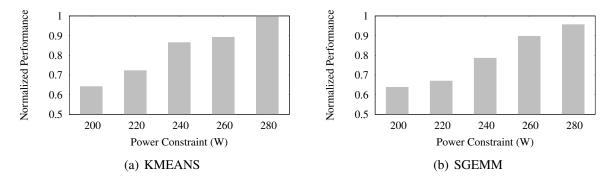

| 5.2  | Performance with conventional DVFS control. Normalized to the ideal execution    |    |

|      | without load imbalance.                                                          | 57 |

| 5.3  | An overview of the profile-based power capping                                   | 58 |

| 5.4  | Parameter space represented as a three-dimensional cube                          | 59 |

| 5.5  | Fine-grained synchronization between the CPU and the accelerator                 | 63 |

| 5.6  | Errors in the estimated execution time: GPU 614MHz                               | 66 |

| 5.7  | Errors in the estimated power (watt): GPU 614MHz                                 | 67 |

| 5.8  | Performance under the power constraint. Normalized to the ideal performance      |    |

|      | for each power constraint                                                        | 69 |

| 5.9  | Performance with data 2 times larger than profiled. Normalized to the ideal per- |    |

|      | formance for each power constraint                                               | 71 |

| 5.10 | Performance for the data 4 times larger than profiled. Normalized to the ideal   |    |

|      | performance for each power constraint                                            | 72 |

| 5.11 | Normalized energy-efficiency.                                                    | 73 |

# **List of Tables**

| 3.1 | Machine setup for the evaluation                                                    | 32 |

|-----|-------------------------------------------------------------------------------------|----|

| 3.2 | A: Total device memory usage in single GPU execution, B: # of parallel loops,       |    |

|     | C: # of kernel executions, D: # of arrays with localaccess directive / # of arrays  |    |

|     | used in parallel loops.                                                             | 33 |

| 3.3 | Number of code Lines                                                                | 37 |

| 4.1 | Wasted leakage energy ratio $(WLR)$ of conventional techniques (%, BET=20cycle).    | 43 |

| 4.2 | Idle length prediction in a basic block                                             | 46 |

| 4.3 | Simulation setup                                                                    | 51 |

| 4.4 | Average leakage reduction from <i>timeout</i> sleep control (%)                     | 52 |

| 5.1 | Model parameters and profile information                                            | 59 |

| 5.2 | Machine setup for the evaluation                                                    | 64 |

| 5.3 | Description of the benchmarks                                                       | 64 |

| 5.4 | Average Errors of the Model (the percentage of GPU tasks: 50% - 90%)                | 65 |

| 5.5 | Selected parameters in the parameter exploration for the highest energy-efficiency. | 74 |

## **Chapter 1**

## Introduction

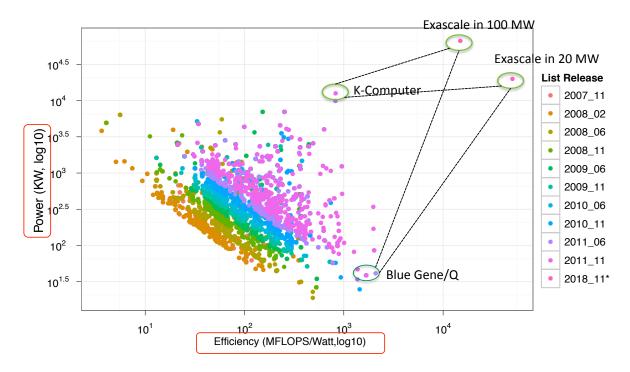

Energy-efficiency, which is given by performance per power, has become one of the most important metric in recent computing systems [17, 44]. The maximum power consumption of a large scale computing center is reaching to tens of Mega Watt, which is the physical limitation of the power supply and the cooling system. In Figure 1.1, pairs of the energy-efficiency (x-axis) and the power consumption (y-axis) of Top500 supercomputers are shown in a log scale scatter plot. Points of exascale systems are plotted on the top right corner of Figure 1.1. We can see that more than ten times improvement in energy-efficiency is required to build exascale computing systems.

To improve energy-efficiency of such computing systems, heterogeneous systems equipped with accelerators are becoming popular. Accelerators are designed to maximize performance and energy-efficiency for specific applications. Among such accelerators, GPUs, which is originally used for image processing applications, have become the center of attention. Previous studies have already shown that GPUs can boost performance and energy-efficiency of many practical applications, such as stencil computations, linear algebra, data mining, monte carlo simulations, graph processing and many others [26]. At the time of 2013, tens of supercomputers in Top500 systems are equipped with GPUs.

Figure 1.1: Trends of power and energy-efficiency of supercomputers in Top500 (extracted from Green500 web site [1]).

### 1.1 Problems for Improving Energy-Efficiency

Heterogeneous systems equipped with accelerators have much potential to provide higher performance and higher energy-efficiency than conventional homogeneous systems. However, because the hardware architecture of such systems is very different from conventional systems, conventional compilers cannot always draw the maximum energy efficiency from the systems.

Energy-efficiency of a computing system is defined by the following equations:

$$Eff = \frac{Perf}{Power}. (1.1)$$

Here, Eff is the value of energy-efficiency of the system, Perf is the average performance achieved by the applications running on the system and Power is the average power consumption during the application execution.

In heterogeneous systems, we can offload data parallel tasks in the applications to accelerators in order to improve energy-efficiency. It can significantly improve the performance (Perf) with

small increase of the power (Power). The actual performance with accelerators can be explained by using Amdahl's law as shown in the following equation:

$$Perf = Perf_{CPUs} * \frac{1}{(1-P) + \frac{P}{X}}.$$

(1.2)

Here,  $Perf_{CPUs}$  is performance only with CPUs, P is the percentage of tasks offloaded to accelerators and X is a speedup ratio by utilizing accelerators.

In current accelerator platforms, typical values of the speedup ratio X is large, up to fifteen for data parallel applications [36]. Meanwhile, the equation 1.2 tells us that, even if the value of the speedup ratio X is large, it is important to increase the percentage of the tasks offloaded to accelerators. However, values of the percentage (P in the equation 1.2) tend to be low because the difficulty in optimizing programs for accelerators. In current accelerator programming environments, such as CUDA and OpenCL, low level architecture of accelerators are exposed to programmers. It significantly decreases the programmability in using accelerators and prevents programmers to utilize accelerators in many cases. To increase the percentage of offloaded tasks in practical situations, it is necessary to improve the accelerator's programmability.

Also, to improve the energy-efficiency, it is useful to reduce power consumption in processors if we can do that with small performance degradation. Even in homogeneous systems, more than half of power consumption in a computing node is occupied by processors (56% to 64% [53]). Although power consumption in processors depends on the types and the number of accelerators installed into the system, the percentage of power consumption in processors gets much larger in accelerator platforms. Power gating (PG) and Dynamic voltage and frequency scaling (DVFS) are two of the most effective power optimization techniques to reduce power consumption in processors. They may also be effective when reducing the power consumption of heterogeneous systems. However, they have not been well studied in heterogeneous systems with accelerators yet.

In particular, we are going to tackle the following three problems to improve energy-efficiency of heterogeneous systems.

Improving programmability of accelerators Directive-based programming models have been shown to be effective to ease the programming difficulty in utilizing accelerators [9, 22, 34, 56, 59]. However, existing directive based compilers are limited to single accelerator environments. It is necessary to extend them to multiple-accelerator environments, which is popular in practical situations.

Reducing leakage power of processors In today's high performance processors, leakage power is a non-negligible fraction in total power consumption of active processors. Power gating (PG) is a circuit technique to make circuit blocks asleep to reduce the leakage power. PG has been studied and shown to be effective in various circuit blocks in CPUs and accelerators [25, 30, 6]. However, we found that conventional PG techniques are not effective for CPU functional units. This is because idle periods in CPU functional units are very short and we cannot ignore the energy overhead caused by PG mode transitions. It is necessary to develop a sleep control technique to take the energy overhead into account.

Reducing dynamic power of processors To enable system administrators to optimize power utilization in large scale systems, it is important to provide knobs to control power consumption in each computing node. Dynamic voltage and frequency scaling (DVFS) is an effective technique to realize such power management with minimum performance degradation [17]. Unlike in homogeneous systems, it is not easy to predict the performance and power fluctuation with frequency scaling in heterogeneous systems because task mapping between CPUs and accelerators affects the amount of fluctuation. Hence, to apply DVFS to such systems, it is necessary to develop a technique to guide the settings of DVFS and heterogeneous task mapping cooperatively.

#### 1.2 Contribution

In this dissertation, we propose three new compiler and runtime techniques. The three techniques can be orthogonally applied to applications running on heterogeneous systems. Although the

1.2. CONTRIBUTION 5

techniques mainly target at heterogeneous systems equipped with GPUs, which are the most popular accelerator platforms, they should be applicable to heterogeneous systems equipped with other accelerator devices, too. Brief summaries of the proposed techniques are described in the following subsections.

#### **1.2.1** Improving Programmability (Chapter 3)

The industry and a lot of academic researchers have been studying high-level programming models for accelerators to ease the programming complexity [8, 43, 52]. Among those, directive-based accelerator programming models [9, 22, 34, 56, 59] have become the center of attention because of their simplicity and their similarity to OpenMP, which is popular in multiprocessor systems. OpenACC is the first industry standard of such a directive based accelerator programming model, released in 2011 [3]. Previous work reported promising results of the OpenACC programming model [35, 38, 48, 58].

However, the previous work also pointed out some limitations of the current OpenACC compilers. One of the biggest limitations is that the current OpenACC compilers do not automate the utilization of multiple accelerators. In the application development with the low level languages such as CUDA and OpenCL, utilization of multiple GPUs is a popular technique to further improve the performance [57]. For wide acceptance of OpenACC platforms, it is necessary to integrate the multi-device execution into OpenACC compilers.

In order to integrate multi-device execution into an OpenACC compiler, we propose a new compiler design and a new memory management technique among multiple accelerators. The compiler system includes a software distributed shared memory which is customized for multiple accelerator environments. In addition, we also propose a small set of new directives to optimize data movement. The directives allow compilers to optimize the data movement among physically disjointed memories according to the application characteristic. With the proposed compiler, we can simplify the programming process in utilizing multiple accelerators. In terms of number of code lines, it brings us 68% of reduction to the program sizes when compared to programs written in a low level language (CUDA). Meanwhile, it achieves 71% of the performance of hand-tuned

CUDA programs.

#### 1.2.2 Reducing Leakage Power (Chapter 4)

Runtime power gating is a well known circuit technique to reduce leakage power consumption of active processors. It can make idle circuit blocks asleep to reduce the leakage power consumption during applications executions. Since the leakage power occupies a large fraction of power consumption in high performance processors, it is effective to make use of runtime power gating in order to improve the energy-efficiency of the system.

When we apply runtime power gating to circuit blocks in active processors, it is important to control sleep-wakeup mode transitions by considering the energy overhead. To avoid large energy overhead caused by excessive mode transitions, time-based sleep control techniques have been proposed both for CPUs and GPUs [25, 30, 6]. However, in CPU functional units, we found that these conventional techniques can miss a lot of chances to reduce the leakage power consumption. The problem is that time-based sleep control techniques are not effective for fine-grained idle periods, whose length is comparable to break even cycles, where the energy overhead can easily surpass the energy saving gained in sleep mode.

To reduce the leakage power consumed in such fine-grained idle periods, we propose a novel code analysis technique to predict the length of each idle period. With the proposed technique, the compiler can predict lengths of idle periods in cycle level accuracy. Using the prediction, the compiler can guide the sleep/wakeup mode transitions effectively. The experimental result for CPU functional units shows that the compiler based sleep control can reduce 23.6% of the leakage power compared to the conventional time-based technique.

#### **1.2.3** Reducing Dynamic Power (Chapter 5)

Dynamic voltage and frequency scaling (DVFS) is an effective circuit technique to reduce the dynamic power consumption of processors. Because the optimal frequency depends on application characteristic, researchers have investigated techniques to select the optimal processor frequency in various situations [28].

However, it is not easy to select the optimal frequencies of CPUs and accelerators when the application makes use of both CPUs and accelerators in parallel. Such hybrid computation is common in heterogeneous systems because it improves the performance and energy-efficiency [21, 39, 46, 50]. In this case, the optimal frequencies do not only depend on the application characteristics but also depend on task mapping between CPUs and accelerators. It is then necessary to develop techniques to cooperatively select the device frequencies and the task mapping.

To do so, we propose a proactive technique in which the settings of frequencies and task mapping are determined in advance of the execution. The proposed technique includes new empirical models of performance and power of the target heterogeneous system. They can predict performance and power of the system when we change device frequencies, task mapping or both of them. Using such models, the proposed technique enables us to select the optimal setting of device frequencies and task mapping. The experimental result shows that, when we optimize the system performance under the given power budget, the performance with the proposed technique is higher (up to 14.4%) than that with DVFS control techniques which don't consider the task mapping. In particular, the performance of the proposed technique is very close to the performance with ideal parameter settings under the given power budget.

## 1.3 Organization of the Dissertation

The remainder of this dissertation is organized as follows. Chapter 2 describes the background information about heterogeneous systems with accelerators and fundamental power management techniques. In Chapter 3, we attack the programmability problem in the accelerator platforms and propose a multi-device directive based compiler. In Chapter 4, we propose a compiler technique to reduce the leakage power consumed in CPU functional units. In Chapter 5, we propose a cooperative DVFS and task mapping technique which enables us to reduce the total power consumption of the heterogeneous systems with the minimum performance degradation. Then, limitation and future work of this dissertation is discussed in Chapter 6. Related work is shown

in Chapter 7 and the conclusion is presented in Chapter 8.

## Chapter 2

## **Background**

Recently, the amount of data processed in computer systems has been increasing rapidly. To this end, data parallel applications, where the same tasks are executed on individual data elements, has become important. The inherent parallelism in the data parallel applications can grow arbitrarily as the size of input data grows. They can be efficiently executed on parallel computing systems with more than ten thousands of processors. Accelerators, which have specialized architecture for data parallel computing, have emerged as the key computing elements [20]. In this section, we will describe the background information about the hardware organizations of the heterogeneous systems with accelerators, their programming environments, and the fundamental low power technology for computing systems.

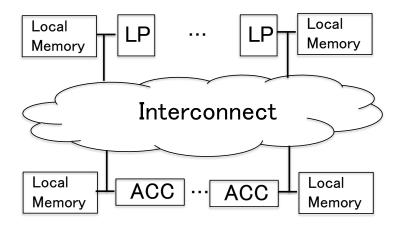

### 2.1 Heterogeneous System

Figure 2.1 shows an illustration of heterogeneous system equipped with accelerators. The system consists of latency processors (LP), accelerators (ACC), and the interconnection which connects these computing devices. Latency processors are usually conventional chip multi-processors, where an operating system is running. Plus, multiple accelerators are installed to the system in order to improve the performance and the energy efficiency. It is common that the accelerator devices have dedicated local memories to fulfill their high memory bandwidth requirement for the accelerators. Hence, the system may not have a single shared memory space and the communication performance between computing devices is often limited and asymmetric.

Figure 2.1: Heterogeneous computing system.

#### 2.1.1 **GPU Computing Server**

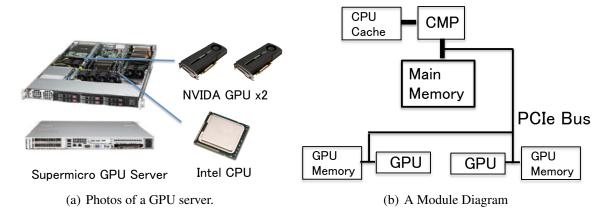

GPUs consist of more than hundreds of simple in-order cores. This means that most of the transistors on GPUs are used for actual computation. The GPU architecture is very different from conventional CPU architecture where most of transistors are used for non computational modules, such as instruction scheduling modules or cache modules. As a result, GPUs can provide much higher performance and energy-efficiency than CPU if the applications have massive parallelism and they are optimized for the GPU architecture [36].

Figure 2.2 shows photos and a module diagram of a commercial GPU server. An Intel CPU is used as a latency processor, and two NVIDIA GPUs are used as accelerators. Main memory can be used only by the CPU. The GPUs have dedicated high throughput memory, which is called GPU memory. A PCI express bus is used as interconnect between the CPU and the GPUs. When the tasks are offloaded to the GPUs, data movement between the main memory and GPU memory must be commanded. Due to the limited performance of the PCI express bus, this data movement often becomes performance bottleneck.

#### 2.1.2 Other Examples of Heterogeneous Systems with Accelerators

**Many Core Processors** An Intel Xeon Phi coprocessor is one of the most famous examples for many core processors [23]. It features tens of in-order cores with vector units on a single die.

Figure 2.2: An example of CPU-GPU heterogeneous systems.

Similar to GPUs, a Xeon Phi coprocessor is physically mounted in a PCIe slot and has dedicated memory. Communication between the CPU memory and the Xeon Phi memory is also required. Thus, in the system with Xeon Phi coprocessors, the memory organization is quite similar to that in the GPU server.

**FPGA** Field-programmable gate array (FPGA) is an integrated circuit which can be configured after manufacturing. FPGA can also be an efficient computing device for data parallel applications because the hardware logic in FPGA can be directly customized and optimized for an application. Traditionally, the FPGA configuration is specified by hardware description languages. However, recently, Altera have shown that it is possible to translate an OpenCL programs into FPGA configuration and FPGA can be used as general purpose accelerators [13].

**GPU Cluster** So far, we focus on heterogeneity inside single computing node. Beyond a single heterogeneous node, many practical computing systems include hundreds of such heterogeneous computing nodes connected with Infiniband interconnect or other high performance inter-node network. For example, more than 50 systems in the Top500 supercomputer systems consist of hundreds of GPU computing nodes. These systems are called GPU clusters [32].

### 2.2 Programming Model for Accelerators

Because the architectures of accelerators are very different from CPUs, we need special parallel programming environments to utilize the accelerators.

#### 2.2.1 CUDA and OpenCL

CUDA is a parallel computing platform and programming model created by NVIDIA and implemented by the graphics processing units that they produce. In this paper, we use CUDA to indicate the CUDA C/C++, which is the GPU programming interface in C/C++ languages. In CUDA, programmers can express massive parallelism in the application by using the special grammars. The parallel code is compiled into the assembly language used in the GPU. To get maximum performance gain from GPUs, programmers have to optimize the memory access in parallel codes by considering the GPU memory architecture, such as on-chip shared memory or a coalesce access mechanism. Furthermore, programmers have to manually manage and optimize the communication between a CPU memory and GPU memories because the GPUs have physically discrete memories and the communication between CPUs and GPUs tends to be the performance bottleneck.

Figure 2.3 shows an example of a vector addition program written in CUDA. We remove error checking codes for simplicity. The actual parallel tasks are written in the function which is declared with the special qualifier \_\_global\_\_ (the line 1–10). The function is executed on the GPUs. In the code at the line 12 to 35, data movement between the CPU memory and the GPU memory is manually commanded with the CUDA API functions such as *cudaMalloc* and *cudaMemcpy*.

For accelerators other than NVIDIA GPUs, including AMD GPUs, FPGAs, DSPs and others, OpenCL [4] is defined as a portable and standard programming interface for accelerator programming. The programming model and API of OpenCL is also low level and very similar to those of CUDA.

```

_global___ void

d_vectorAdd(const float *A, const float *B,

float *C, int numElements)

4

5

int i = blockDim.x * blockIdx.x + threadIdx.x;

6

if (i < numElements)</pre>

7

8

C[i] = A[i] + B[i];

9

}

10

11

12

void

13

vectorAdd(const float *h_A, const float *h_B,

float *h_C, int numElements)

14

15

16

float *d_A = NULL;

17

cudaMalloc((void **)&d_A, size);

18

float *d_B = NULL;

19

cudaMalloc((void **)&d_B, size);

20

float *d_C = NULL;

21

cudaMalloc((void **)&d_C, size);

22

23

cudaMemcpy(d_A, h_A, size, cudaMemcpyHostToDevice);

24

cudaMemcpy(d_B, h_B, size, cudaMemcpyHostToDevice);

25

26

int t_per_b = 256;

27

int b_per_g = (numElements + t_per_b - 1) / t_per_b;

28

d_vectorAdd <<<b_per_g, t_per_b>>>(d_A, d_B, d_C, numElements);

29

30

cudaMemcpy(h_C, d_C, size, cudaMemcpyDeviceToHost);

31

32

cudaFree(d_A);

33

cudaFree(d_B);

34

cudaFree (d_C);

35

```

Figure 2.3: CUDA vector addition.

#### 2.2.2 OpenACC

CUDA or OpenCL can be accepted for expert programmers while not for common programmers due to its low programmability. For wide acceptance of accelerator computing, more productive accelerator programming environments have been proposed [8, 43, 52]. Especially, the directive-based accelerator programming models have become the center of attention because of their simplicity and their similarity to OpenMP, which is popular in developing parallel applications for multiprocessor systems [9, 22, 34, 56, 59].

OpenACC is the first industry standard of such a directive based accelerator programming model, released in 2011 [3]. The OpenACC API is designed to offload the low-level accelerator programming process to the compiler. It assumes the similar execution model as CUDA. That

```

void

vectorAdd(const float *h_A, const float *h_B,

3

float *h_C, int numElements)

4

5

#pragma acc kernels copyin(h_A[0:numElements], h_B[0:numElements])\

6

copyout(h_C[0:numElements])

7

8

#pragma acc loop independent

for (i=0; i < numElements; ++i) {

9

10

h_C[i] += h_A[i] + h_B[i];

11

12

13

```

Figure 2.4: OpenACC Vector Addition.

is the main program runs on the CPU and the data parallel tasks are offloaded to the accelerators. Unlike CUDA or OpenCL, which provide the unique languages to describe parallel tasks for accelerators, the OpenACC API provides OpenMP-like directives to use accelerators. The directives allow programmers to run parallel tasks written in C or Fortran on accelerators only with a few additional lines of code. It can be thought as an accelerator extension of OpenMP.

Figure 2.4 illustrates a vector addition program written in OpenACC. As we can see, the amount of complexity in the program is smaller than that in the program shown in Figure 2.3. At the line 5-6, the *kernels* directive is used to identify the code regions to be offloaded to accelerators. In addition to annotate the parallel code regions, the *copyin* and *copyout* clauses indicate which arrays would be read or written on accelerators. The hint information about array accesses helps the OpenACC compiler to avoid generating unnecessary data movement between CPUs and accelerators. At the line 8, the loops are annotated with the *loop* directives. The loop is the actual candidates to be transformed into the kernel program which is executed on accelerators. Also, like OpenMP, the *reduction* clause can be used for scalar variables (not shown in the Figure 2.4).

### 2.3 Power Management Technique

Power consumption in processors consists of dynamic power  $(P_D)$  and leakage power  $(P_L)$ . Dynamic power is power consumed in switching activity of CMOS circuits. Given the capacitance

of the circuit  $C_L$ , the supply voltage  $V_{dd}$  and the frequency of the device, dynamic power is the product of energy per charge-discharge  $(C_L V_{dd}^2)$  and the number of switching per unit time  $(\alpha f_{clk})$ . On the other hand, static power is consumed due to the leakage current  $(I_{leakage})$  in CMOS circuits. This kind of power consumption is called leakage power consumption and it exists both in idle and active periods. The power consumption of processors can be modeled with the following mathematical equation [11]:

$$P_{processor} = P_D + P_L = \alpha C_L V_{dd}^2 f_{clk} + I_{leakage} V_{dd}. \tag{2.1}$$

A lot of researchers have investigated both circuit and architectural techniques to reduce both leakage and dynamic power of processors. Here, power gating and DVFS are explained as elementary circuit techniques which enable us to control the power consumption of the processors. Also, power capping is introduced as a key technology in computing center level power management.

#### 2.3.1 Power Gating

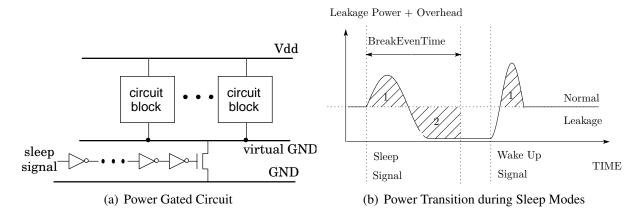

Power gating (PG) is one of the most important circuit techniques to reduce leakage power consumption of CMOS circuits [45]. As shown in Figure 2.5 (a), the sleep transistors are inserted between the circuit block and the ground wires to provide the sleep mode in which we can save the leakage current in the circuit block by cutting off the supply voltage.

The energy overhead of the mode transition is not negligible and BET (Break Even Time) must be considered. Power transition during a sleep/wakeup mode transition is shown in Figure 2.5 (b). BET is the time period when the energy saving in the sleep mode balances with the energy overhead caused by the mode transition. The energy overhead of mode transitions, the area slashed as 1 in Figure 2.5 (b), is mainly caused by switching activity in a sleep transistor and charging/discharging for capacitance of the target circuit block. The length of BET depends on the process technology, the structure of circuit blocks, and the temperature. In the case of PG in the CPU functional units, which is the main concern in this dissertation, the length of BET is less than 100 cycles [51]. In order to achieve large leakage power reduction by using runtime PG, we

Figure 2.5: Power gated circuit and the power transition during sleep mode.

need sophisticated sleep control technique to avoid unnecessary mode transitions and the energy overhead. Ideally, each functional unit should goes into the sleep mode only when the length of the following idle period exceeds the length of BET.

#### 2.3.2 **DVFS**

DVFS (Dynamic Voltage and Frequency Scaling) is a technique to reduce dynamic power consumption of processors. There is a trade off between the frequency and power consumption of the processor and we can improve the energy-efficiency of the system by tuning the frequency according to applications characteristic.

In the power model shown in equation 2.1, we can see that the power consumption of processors depends on the supply voltage. Thus, we can reduce the power consumption of processors by reducing the supply voltage. However, we have to decrease the clock frequency of the device according to the supply voltage because lower supply voltage results in longer signal propagation time. Given the threshold voltage of the transistors  $V_{th}$ , the relationship between the supply voltage and the clock frequency is formalized in the following equation:

$$f_{clk} \propto \frac{(V_{dd} - V_{th})^{\alpha}}{V_{dd}}.$$

(2.2)

$\alpha$  is a parameter which depends on process technology. It is usually from 1 to 2. In DVFS, as shown in equation 2.1 and the equation 2.2, there is a trade-off between the power consumption

17

of processors and the clock frequency. The amount of performance change caused by the fluctuation of the clock frequency depends both on the processor architecture and the applications characteristics.

#### 2.3.3 Power Capping

Power capping is an elementary technique which is used in the global power management of large scale computer systems. It eliminates the burst of power consumption in components or computing nodes and keeps the power consumption under the given power constraint. Based on power capping, we can optimize the power utilization among servers according to online activity of running applications [17].

At the component level, power capping techniques for CPUs [15] or system memories [28] have been already proposed. On a different level, power capping for a single computing node is important for large scale computing systems [37]. In homogeneous systems with CPUs, several power capping techniques have been proposed, but power capping in heterogeneous systems with accelerators has not been well studied.

## **Chapter 3**

# Multi-Device Execution in a Directive Based Compiler

In this chapter, we focus on a technique to utilize multiple accelerators from OpenACC, standard programming API for directive based accelerator programming.

The difficulty lies in the communication management among multiple accelerator memories. In the conventional programming models, such as CUDA or OpenCL, programmers have to manually distribute data among the different memories and have to keep consistency of the data replicated on the multiple memories. It is often the case that the complicated optimization is required to avoid the performance bottleneck at the data movement among the distributed memories. To integrate such optimized communication management into an OpenACC compiler, we propose a compiler and a runtime memory management mechanism which makes single memory space illusion on top of the multiple accelerator memories.

## 3.1 Drawbacks of Current GPU Programming Environments

Figure 3.1 shows the performance and the number of code lines in several parallel implementations of two GPU friendly applications KMEANS and BFS. The implementations include OpenMP (OpenMP), OpenACC (ACC), and CUDA {CUDA(1, 2GPU)} with one and two GPUs  $^1$ . Exper-

<sup>&</sup>lt;sup>1</sup>Note that we cannot implement a multi-GPU OpenACC program for *KMEANS* and *BFS* because these application requires us to use critical sections in the parallel loops. The current OpenACC API does not provide such functionality.

Figure 3.1: Comparison of current GPU programming environments.

imental setup is the same as that used in later evaluations: OpenMP uses one 6-core Intel CPU, OpenACC and CUDA uses one or two 448-core GPUs. In measuring the number of code lines, we only count the code lines which are used in actual parallel processing. The performance is normalized to the performance of OpenMP. Figure 3.1 (a) shows that we can achieve 3-8 times higher performance than that of *OpenMP* by utilizing multiple GPUs in *CUDA(2GPU)*.

However, in Figure 3.1 (b), we can see that we have to develop much larger programs to utilize multiple GPUs in CUDA. The numbers of code lines in CUDA(2GPU) is 4-5 times larger than those in the OpenMP implementation. The reason is as follows. In BFS, parallel tasks generate a lot of irregular write requests to visit the next graph node with chasing memory pointers. These irregular write requests can cause memory accesses to remote GPU memories in the multi-GPU execution. In the CUDA multi-GPU implementation, we have to manage special communication buffers on each GPU to manage these remote memory accesses. This increases the number of code lines of two GPU CUDA BFS. In KMEANS, complicated reduction operation is used to summarize the results of each parallel tasks. To implement the reduction on GPUs, we have to implement hierarchical parallel reduction algorithm which is optimized for the GPU memory hierarchy. In CUDA, this implementation needs a lot of code lines in the program.

As seen in this case study, no existing platform can provide both high programmability and high performance in utilizing multiple GPUs.

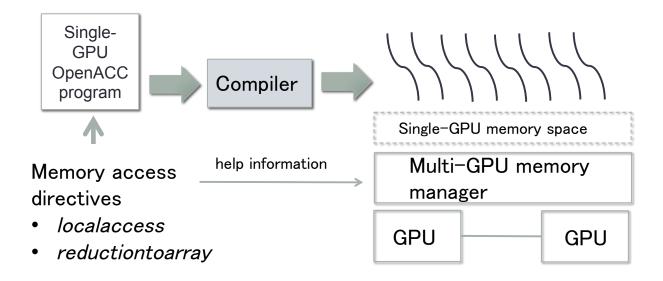

# 3.2 OpenACC Compiler with Software Distributed Shared Memory

To overcome the drawbacks of the current programming environments, we propose an OpenACC compiler which is integrated with software distributed shared memory. Figure 3.2 shows the concepts of the proposed compiler. To avoid the complicated programming interface for using multiple accelerators, the proposed compiler receives OpenACC programs. Unlike conventional platforms, it is unnecessary to rewrite the program to utilize multiple accelerators. The *compiler* and the *Multi-GPU memory manager* in the proposed system automatically distribute parallel loops and manage data among the physically disjointed memories. However, it is not easy for compilers to automate efficient communication among the memories because this highly depends on the applications characteristics, as explained in the previous case study. To solve the problem, we propose new directives for programmers to express the applications memory access pattern in parallel loops (*Memory access directives* in Figure 3.2). With the directives, the compiler can safely assume which data items are accessed on a certain device. It greatly helps compiler reduce unnecessary communication.

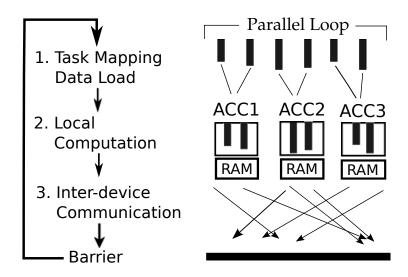

Figure. 3.3 illustrates the overall steps of the multi-device execution in the proposed compiler. Parallel loops are executed on the multiple accelerators with three steps. First, the system maps tasks and data to the multiple accelerators. The iteration space of the parallel loop is divided into tasks. The system also determines the mapping of the tasks to the multiple accelerators. At the same time, all the data potentially read by the tasks mapped to each accelerator are loaded into the corresponding accelerator memory. Here, the memory access information given by the newly introduced directives is used to reduce unnecessary data load. Next, actual computations are executed in parallel on the multiple accelerators. In this step, all write requests on data replicated among multiple accelerator memories and all write requests on data which is not on the local accelerator memory are recorded by the system. This is done by additional codes instrumented in parallel kernel functions. Finally, the system handles necessary inter-accelerator communications, which include handling of writes to the replicated data, and include the handling of

Figure 3.2: Overview of the proposed multi-device OpenACC compiler.

irregular writes whose destinations do not present in the local accelerator memory. In the final step, the memory access information given by the newly introduced directives is also used to update remote data items efficiently. Then, a global barrier operation among accelerators occurs and the next parallel loop will be executed.

#### 3.2.1 Directive Extensions

In order to allow compilers to optimize communication according to the application characteristic, we propose two new directives as an OpenACC extension for multiple accelerator environments. Note the proposed system uses these directives only for performance tuning purpose. The compiler can execute any OpenACC program on multiple accelerators without using these newly introduced directives.

The design of the directives are based on the common memory access patterns which are observed in typical data parallel applications. One directive is *localaccess* directive, which is used to describe the region of data elements read by each parallel task inside the parallel loop. The other is *reductiontoarray* directive, which is used to tell the compiler about complicated

Figure 3.3: Execution steps of parallel loops in the proposed system.

reduction operations to array elements inside the parallel loops. These directives are designed based on typical memory access patterns observed in common data parallel applications.

localaccess [clause] The directive allows programmers to specify the range of indices for a certain array which can be read in i-th iteration of the loop. When the directive is given, the compiler can aggressively optimize the generated code with the assumption that the i-th iteration of the loop does not read any part of the array outside the specified range of indices. The range of indices must be consecutive. Therefore, it is specified by a pair of a lower bound of indices and an upper bound of indices. To express constant stride read accesses, the directive supports stride(ArrayName[stride:left:right]) clause. This means that the i-th iteration of the loop use the array elements whose indices are from (stride\*i-left) to  $\{stride*(i+1)-1+right\}$ . To support non-uniform stride access, programmers can specify an index array which contains lower bounds of access indices for each iteration of the loop. The indirect(ArrayName[LowerBounds]) clause can be used for this purpose. We can specify an index array at LowerBounds and can specify the actual array to be read in the loops at ArrayName. The LowerBounds array contains lower bounds of indices used for the ArrayName in the i-th iteration of the loop. The upper bound is given by the lower bound on the i-th iteration of the loop like the compressed

```

#pragma acc loop

#pragma acc localaccess stride(x[1:0:0], b[1:0:0]) \

3

indirect(c[cIndex])

4

for (i=0; i < n; ++i)

5

6

for(j=cIndex[i]; j < cIndex[i+1]; ++j){</pre>

7

x[i] \star = c[j];

8

9

#pragma acc reductiontoarray (+:errors[0:e_size])

10

11

errors[b[i]] += x[i];

12

13

```

Figure 3.4: An simple example of the proposed directives.

sparse row format used in the field of sparse linear algebra.

We extend the scalar reduction clause for arrays. Unlike the conreductiontoarray [clause] ventional reduction clause, the directive is used inside parallel loops to annotate single reduction statement directly. We can specify the name of the destination array and the range of indices in the clause. The access index of the destination array can be dynamically determined. The compiler generates optimized reduction codes which can run efficiently on the multiple accelerator environment.

**Example** Fig. 3.4 illustrates an example of a C program annotated with the proposed directives. In the code, the read access patterns for the array x, the array b and the array c are passed to the compiler through the *localaccess* directive (line 2). On the other hand, the *errors* array does not have the *localaccess* directive. In this case, the compiler does not aggressively optimize the data movements for the array (detailed in Section 3.2.2). Also, we use the *reductiontoarray* directive to tell the compiler that the statement at line 10 must be treated as the reduction operations whose destinations are the elements in the array errors. Note that programmers do not have to consider the existence of multiple accelerators because no task mapping and no data transfer between multiple accelerators are manually commanded.

#### 3.2.2 Implementation and Optimization in multi-GPU platforms

We have implemented a prototype system of the proposed compiler on top of multi-GPU platforms. Although, we have implemented the prototype system for NVIDIA CUDA platforms, the proposed design of the system can be applicable to other accelerator platforms in which we can use an OpenCL programming environment.

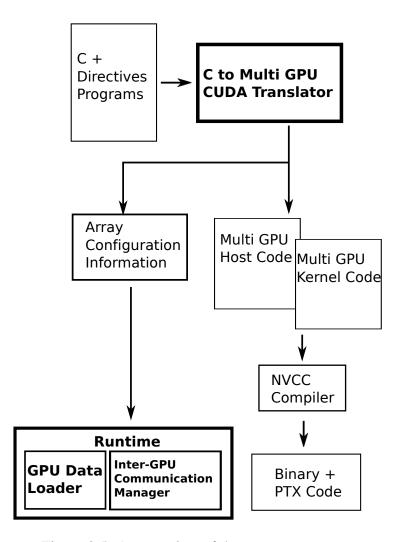

#### 3.2.2.1 Module Diagram

Figure 3.5 illustrates a module diagram of the prototype system of the proposed OpneACC compiler. *C to Multi GPU CUDA Translator* (translator) is designed as a source to source translator. The translator generates CUDA kernel codes and host codes from C programs annotated with the OpenACC directives and the proposed extension. In addition to generating CUDA codes, the translator also generates the information which summarizes memory access patterns for arrays. The information is used in the runtime system in order to optimize data movement among distributed memories. *GPU Data Loader* (data loader) manages necessary data movement between the CPU memory and the multiple GPU memories according to the OpenACC semantics. To make sure that the execution is correct, all the data which are potentially read by the kernel running on each GPU must be loaded into the corresponding GPU memory before the kernel execution. *Inter-GPU Communication Manager* (inter-GPU communication manager) is responsible for handling inter-GPU communication. It is called just after the kernels executed on every GPU. It checks write operations done by the kernel on each GPU and updates remote GPU memories.

#### 3.2.2.2 Translator

The translator generates a CUDA kernel and host codes which utilize multiple GPUs. In the current implementation, a parallel loop annotated with an OpenACC *loop* directive is transformed into a CUDA kernel function. The translator replaces the original loop with the call statement for the kernel function. Also, the translator generates the CUDA host code which includes the control codes to initialize the devices, to call the kernel functions, and to control the data movement among distributed memories.

Figure 3.5: An overview of the prototype system

**Handling Data Movement** The actual operations for data movement among the distributed memories are delegated to the runtime system. The translator just inserts statements to call the runtime functions at the program points where the data movements are required.

**Task Mapping and Thread Generation** In the current implementation, the tasks in the parallel loop are equally divided among the GPUs. Before the call of the kernel function on each GPU, the host program sets up the number of the thread blocks and the number of the CUDA threads per blocks for the GPU according to the number of the assigned tasks to the GPU.

Organizing Array Accesses on GPUs In the kernel functions, all indices in array accesses must be recalculated by considering data layout of the array on each local GPU memory. To do so, the host program includes the codes to ask the runtime system about the layout of the arrays among the GPU memories and includes codes to pass the information to the arguments of the kernel functions. The translator rewrites indices of the array accesses in the kernel function by using the arguments. In addition, the translator inserts additional codes for the inter-GPU communication manager to identify which parts of the arrays are written by the kernel (detailed in Subsection 3.2.2.4).

**Optimizing Kernel Functions** The translator applies two GPU-specific optimizations to kernel functions. One is the data layout transformation of two-dimensional arrays for enhancing the coalesced memory accesses. The transformation is applied to device arrays which satisfy the following three conditions: read-only, the access indices are all in affine forms, and the array has the *localaccess* directive. Also, to avoid the performance bottleneck at reduction operations, the translator uses the hierarchical reduction algorithm for the reductions in the kernel functions. At first level, the reduction is done on the shared memory for each thread block. Next, the values are collected among the thread blocks on the same GPU. Finally, the values are transferred and merged between multiple GPUs.

Generating Array Configuration Information The translator generates array configuration information, which is used by the data loader and the inter-GPU communication manager. The information summarizes memory access patterns of arrays. It is generated for every parallel loop and for every device array in the loop. The information contains several attributes of the array, including whether the array is read-only or write-only, the range of the access indices in each loop iteration (if the array has the *localaccess* directive), and the array is the destination of complicated reduction operations.

#### 3.2.2.3 Data Loader

In OpenACC, the compiler manages the data movement between the system memory and the device memory. The data loader is responsible for guaranteeing the semantics of the GPU memory management while it transparently manages multiple GPU memories.

The data loader is called at the entrance and the exit points of the *parallel* regions, the *kernels* regions and the *data* regions. In these regions, the data loader is called at the point where programmers command data movement by inserting OpenACC directives such as the *update* directives. The data loader is also called before every kernel calls to load the necessary data into the GPU memories because the necessary data can be different between different kernel calls.

In order to avoid unnecessary data movement among multiple GPU memories, the data loader makes use of two different policies to load arrays into GPU memories. One policy is replicabased policy. With the policy, all data elements in the array are replicated to all the GPU memories. The other policy is distribution-based policy. In the policy, an array is divided into subarrays and only the sub-array actually accessed by each GPU is loaded into the corresponding GPU memory. With the distribution-based policy, the arrays require less amount of data movement and less amount of device memory footprints than arrays with the replica-based policy.

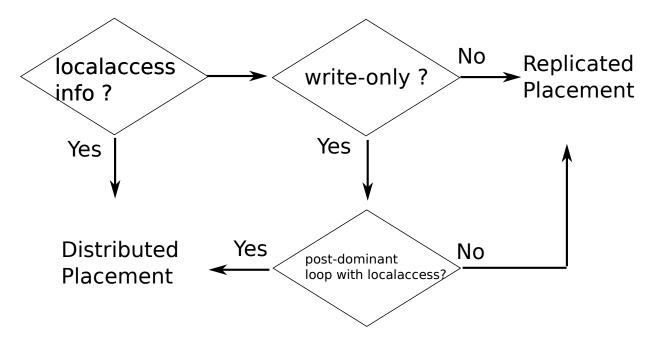

The data loader decides which placement policy should be used for each array according to the user hint information given from the *localaccess* directive. Figure 3.6 is the flow chart used to determine array placement policy. If an array is annotated with the *localaccess* directive at the top of the parallel loop, then, the data loader uses the distribution-based policy. Also, even if the array is not annotated with *localaccess* at the top of the corresponding parallel loops, the data loader uses distribution-based policy as far as the array is annotated with the *localaccess* directive at the top of the post dominant parallel loop. Otherwise, the data loader uses replica-based policy.

Note that the data loader can avoid additional data movement before the kernel calls when the read memory access pattern in the next kernel call is the same to that in the previous kernel call. This is common in iterative algorithms, the same parallel loop is executed many times, as seen in the applications evaluated in the evaluation chapter.

Figure 3.6: A flowchart to determine the placement policy of each array.

### 3.2.2.4 Inter-GPU Communication Manager

The inter-GPU communication manager is called just after the kernel functions executed on the GPUs. It handles necessary data exchanges between multiple GPU memories, including update operations at the writes to the replicated data and the remote write operations to the data which exist only in the remote GPU memory. To maximize the performance at the communication step, the communication manager directly exchanges the data between the GPU memories and the communications are executed asynchronously.

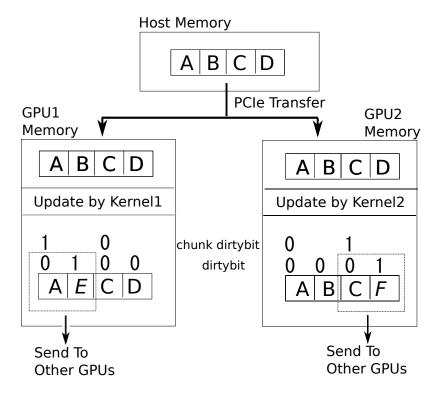

**Replicated Array** When write accesses occur in replicated arrays, the inter-GPU communication manager must update other copies on the different GPU memories to keep consistency.

To do this, the manager prepares the dirty bit arrays on the GPU memories for replicated arrays. In order to identify which elements of the array are written in a kernel execution, the translator inserts additional operations to turn on the dirty bits at every writes accesses to the replicated arrays. However, with the single level dirty bits, the manager has to transfer all array data, including clean elements and the dirty bits, to other GPU memories because the manager

Figure 3.7: Two-level dirty-bit mechanism to keep consistency of the replicated arrays.

cannot check the contents of dirty bits efficiently on the sender GPU. It degrades the performance of the inter-GPU communications.

To solve the problem, we use two-level dirty-bit mechanism. It is illustrated in Fig. 3.7. A dirty bit array is subdivided into chunks whose sizes are constant. Each chunk also maintains single bit, which indicates all the dirty bits in the chunk are clean. The bit is used as the second level dirty bit. The translator add codes to turn on the second level dirty bits in kernel functions. With the second level dirty bits, the inter-GPU communication manager avoids unnecessary data transfers at chunks which have no dirty data. The optimal size of the chunks is dependent both on applications and hardware characteristics. In the evaluation chapter, we experimentally choose 1MB to the chunk size of the second level dirty bit arrays.

**Distributed Array** In the case of the arrays which are subdivided and distributed among multiple GPUs, we have to handle irregular writes to the data which do not exist in the local GPU memory. To correctly handle writes to data on remote GPU memories, the manager must know

that which write accesses missed on the local GPU memory in the previous kernel execution. To tell the manager about the write misses, the translator insert check codes at every write accesses on distributed arrays to identify the write misses. When the write access causes write miss, a pair of the written data and the destination address are temporarily buffered into the system buffers on the local GPU. After the kernel execution, the inter-GPU communication manager transfers the records of the write misses to the remote GPU memories where the destination exists. Then, the communication manager calls the CUDA kernels to complete the write access on the remote GPUs. If the compiler can statically analyze that the write address is always within the range described by the *localaccess* directive, we can eliminate the check code to avoid the additional performance overhead.

### 3.3 Evaluation

The translator is implemented by using ROSE compiler infrastructures developed at Lawrence Livermore National Laboratory [5]. It also uses parts of an existing C to CUDA translator [56], which is publicly available. The runtime system is implemented with C++ on top of the CUDA 4.0 platform. We evaluated the proposed compiler system in two different machines. One is the desktop machine equipped with two GPUs. The other is a thin-node of TSUBAME2.0 supercomputer at Tokyo Institute of Technology. Each platform differs by the type and the number of CPUs and GPUs. Also, the performances of communication buses are different. The details of the platforms are shown in the Table 3.1. We use three benchmark applications *BFS*, *MD*, and *KMEANS* selected from rodinia [12] and shoc [14] benchmark suites. They exhibit different inter-GPU communication characteristics. *BFS* is highly memory intensive with a lot of irregular writes. It is one of the most difficult applications to be efficiently executed in multiple GPU environments. On the contrary, *MD* requires no inter-GPU communications. *KMEANS* is in the middle of these two applications. It requires small amount of inter-GPU communications due to the existence of reduction operation whose destination is the array which is used in all GPUs. We summarize the details of the applications in Table 3.2.

We compare the performance of the several versions of the applications. The versions are as follows.

- OpenMP (*OpenMP*): The programs are written with OpenMP. They are compiled by the gcc compiler with the O2 optimization flag. The number of running threads is set to 12 in the Desktop Machine and 24 in the supercomputer node.

- CUDA (*CUDA*(1, 2)): The programs are written in CUDA. They are compiled by the nvcc compiler with the O2 optimization flag. The number in the label denotes the number of GPUs which is used in the implementation.

- Proposal(*Proposal*(1, 2)): The programs are written with the OpenACC API with the proposed extensions (the *localaccess* directive and the *reductiontoarray* directive). The generated CUDA codes are compiled by the nvcc compiler with the O2 optimization flag. The number in the label denotes the number of GPUs which is used in the implementation.

## 3.3.1 Performance and Programmability

In this subsection, we show the results of performance and the programmability in Desktop Machine in detail.

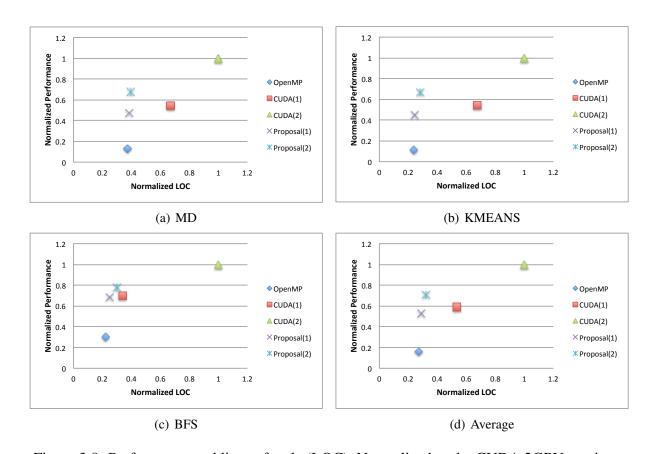

In Figure 3.8, we plot the pairs of the performance and the number of code lines (LOC) for each platform. The x-axis denotes LOC normalized to that of CUDA(2). The y-axis denotes performance normalized to that of CUDA(2). Each point represents each implementation of the application. We measure the execution time spent in the parallel regions, including the time

Table 3.1: Machine setup for the evaluation.

| Desktop Machine                                |                                              |  |

|------------------------------------------------|----------------------------------------------|--|

| CPU Intel Core i7 x 1 (6core, Hyper Threading) |                                              |  |

| GPUs                                           | Nvidia Tesla C2075 x2                        |  |

| Supercomputer Node                             |                                              |  |

| CPU                                            | Intel Xeon x 2 (12=2x6core, Hyper Threading) |  |

| GPUs                                           | Nvidia Tesla M2050 x3                        |  |

Figure 3.8: Performance and lines of code (LOC). Normalized to the CUDA 2GPU versions.

spent on the CPU-GPU communications and the GPU-GPU communications. In measuring the number of code lines, we only count codes related to actual parallel processing. We exclude I/O related operations to prepare the input data for parallel processing. However, we count codes related to transform data layout of arrays to enhance coalesce memory accesses on GPUs and codes related to prepare index arrays specified in the localaccess directive with the indirect clause. In the figure, a point is better if it is plotted in upper-left region because it is better for

Table 3.2: A: Total device memory usage in single GPU execution, B: # of parallel loops, C: # of kernel executions, D: # of arrays with localaccess directive / # of arrays used in parallel loops.

| Application | Source  | Description     | Input      | A       | В | С  | D   |

|-------------|---------|-----------------|------------|---------|---|----|-----|

| BFS         | SHOC    | Graph Traversal | 5M node    | 444.9MB | 1 | 10 | 2/3 |

| MD          | SHOC    | Simulation      | 73728 Atom | 39.8MB  | 1 | 1  | 2/3 |

| KMEANS      | Rodinia | Clustering      | kdd_cup    | 69.2MB  | 2 | 37 | 2/5 |

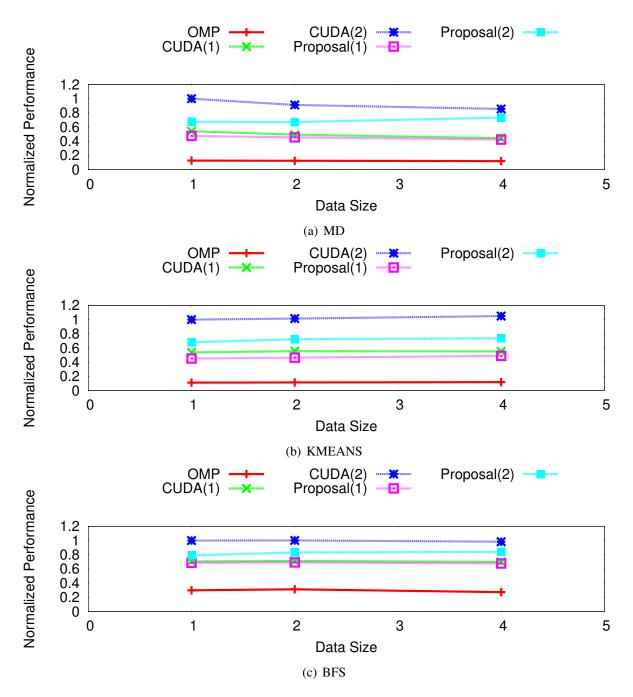

Figure 3.9: Performance trends when the size of input data changes. Normalized to the CUDA 2GPU versions with base inputs.

platforms to have the low LOC (x-axis) and the high performance (y-axis).

First of all, we can see that the points of Proposal(1, 2) are at the upper-left of other points, which represents other platforms (OpenMP and CUDA(1, 2)). This means that we can achieve better performance with smaller programs in the proposed system than in the other platforms. Comparing Proposal(1) and Proposal(2), in the proposed system, we can improve the performance by utilizing 2 GPUs with small increase of LOC. On average, the performance with Proposal(2) achieves 71% of the performance with CUDA(2) while the LOC with Proposal(2) is 32% of the LOC with CUDA(2) (Figure 3.8 (d)). Also, Figure 3.9 shows the performance when we vary the size of input data. The performance is normalized to the OpenMP versions with the base data sizes, which are show in the Table 3.2. The performance trend does not significantly differ in the different data size.

Next, we look at the detailed performance analysis for each application through comparing *CUDA (2GPU)* versions and the proposed compiler.

MD In MD, there's no inter-GPU communications and the largest data array, which occupies the most of the CPU-GPU communication, are accessed with the constant stride in parallel loops. Hence, with the *localaccess* directives, the compiler can successfully avoid most of the unnecessary data movement as same in the optimized CUDA program. Therefore, in Figure 3.8 (a), *Proposal(2)* achieves almost same performance to *CUDA(2)* at large input data. This is because the runtime overhead becomes relatively smaller when the size of input data gets large and the percentage of computation time grows.

**KMEANS** Both in CUDA and the proposed compilers, KMEANS achieved the highest speed up by utilizing two GPUs among the evaluated applications. This is because it is possible to apply GPU specific optimizations to the parallel loops in KMEANS, such as data layout transformation to enhance coalesce accesses or parallel reductions on the GPU shared memory. On the other hand, for large data, the difference between performance of *Proposal(2)* and that of *CUDA(2)* is the largest among the applications. This is because that there is some difference in the imple-

36

mentations. First, in the proposed compiler, the data layout transformation is done on the CPU while it is done on the GPU in the CUDA program. Second, at the end of each iteration of the KMEANS parallel kernels, it is necessary to communicate some small arrays which contain the results of the reduction operations. The proposed compiler uses dirty-bit based coherence mechanism to communicate the small arrays. It incurs non-negligible performance overhead due to the execution time of the runtime memory manager and the communication time of the dirtybit array. The performance overhead is originated from unoptimized implementations in the compiler and the runtime memory manager. Hence, it seems to be reduced if we further optimize the implementations of them.

BFS Although the runtime memory manager has to handle a lot of irregular write requests which incurs inter-GPU communications, these requests still exist in the hand-written CUDA program. Then, the performance difference is not very large in BFS across the input data sets. One interesting observation is that the CUDA program uses the smaller size data type for the inter-GPU communication because the programmer can know the values of the communication data do not exceed a certain constant value. In particular, char type (1byte) is used for communicating data whose original type is integer (4byte). Such kind of application specific optimizations cannot be done by the proposed compiler. It is a fundamental limitation of the automatic GPU memory management. However, in this case, the effect is not very large and the proposed compiler achieves modest performance (79%-84% of the performance of *CUDA(2)*).

Finally, Table 3.3 shows the details of LOC in *OpenMP*, single GPU OpenACC (equivalent to *Proposal(1)*), *Proposal(2)*, and *CUDA(1)*. We can see that the numbers of code lines needed to implement the parallel programs for the proposed multi-GPU OpenACC compiler are almost same to the numbers of code lines in OpenMP and OpenACC. In summary, the proposed multi-GPU OpenACC compiler can provide comparable programmability to OpenMP or conventional single-GPU OpenACC, which provide better programmability than CUDA.

## 3.3.2 Evaluation in a Supercomputer Node

To see scalability of the proposed system, we evaluate the proposed system on the machine with more than 2 GPUs. Figure 3.10 (a) shows the performance of the proposed system in a thin node of TSUBAME2.0. We do not evaluate CUDA(2) and CUDA(3). The computing node is equipped with 3 GPUs. The y-axis is the performance normalized to the performance of OpenMP. Also, we show the breakdown of the execution time in Figure 3.10 (b). To investigate the memory overhead caused by the runtime system, including the data replication and the temporary buffers on GPUs, Figure 3.10 (c) shows the GPU memory usages in the applications with the proposed system. The bars in the figure indicate the amount of memory used to store the user data (*User*) and the amount of memory used in the runtime system (*System*). The values are normalized to the total device memory usage in the single GPU execution, where no system memory or no replicated data exists.

In Figure 3.10 (b), we can see that the time spent on the data transfer between CPUs and GPUs (*CPU-GPU*) are the main reason that prevents us from achieving linear speed up to the number of GPUs (shown in Figure 3.10 (a)). Because the proposed system does not incur large overheads in the data transfer between the CPU and the GPUs, the limitation is originated in the application characteristics. Thus, the data transfer between CPUs and GPUs still prevents the linear speed up even when we manually make use of multiple GPUs with CUDA or OpenCL. To

|        |                   | OpenMP | OpenACC | Proposal(2GPU) | CUDA(1GPU) |

|--------|-------------------|--------|---------|----------------|------------|

|        | Actual Processing | 40     | 40      | 40             | 42         |

| BFS    | Directive         | 2      | 7       | 9              | _          |

| БГЗ    | API Call          | _      | _       | _              | 22         |

|        | Other             | _      | _       | 7              | _          |

|        | Total             | 42     | 47      | 56             | 64         |

|        | Actual Processing | 26     | 26      | 26             | 26         |

| MD     | Directive         | 1      | 2       | 3              | _          |

|        | API Call          | _      | _       | _              | 23         |

|        | Other             | _      | _       | _              | _          |

|        | Total             | 27     | 28      | 29             | 49         |

|        | Actual Processing | 51     | 54      | 54             | 113        |

| KMEANS | Directive         | 8      | 7       | 16             |            |

|        | API Call          | _      | _       | _              | 34         |

|        | Other             | _      | _       | _              | 21         |

|        | Total             | 59     | 61      | 70             | 168        |

Table 3.3: Number of code Lines.

solve the problem, we have to rewrite the applications by redesigning the algorithm. However, this is beyond the scope of this work.