# 修士論文

# システムLSIにおける 基板雑音の能動的低減手法

平成19年2月2日提出

指導教官 池田誠助教授

東京大学大学院 工学系研究科 電子工学専攻 学籍番号 56431 風間 大輔

# 目次

| 第1章 | 序論                                    | 1  |

|-----|---------------------------------------|----|

| 1.1 | 背景                                    | 1  |

| 1.2 | 受動素子を用いた基板ノイズ低減手法の問題点                 | 2  |

| 1.3 | 従来の能動的基板ノイズ低減手法の問題点                   | 2  |

| 1.4 | 研究の目的                                 | 3  |

| 1.5 | 本論文の構成                                | 4  |

| 第2章 | アナログ方式による雑音低減手法の評価                    | 5  |

| 2.1 | di/dt 検出回路を用いた能動的基板ノイズ低減手法の概要         | 5  |

| 2.2 | di/dt キャンセラーの低減効果に関する考察               | 7  |

| 2.3 | di/dt キャンセラー回路設計とその解析................ | 8  |

|     | 2.3.1 差動増幅器の周波数特性                     | 8  |

|     | 2.3.2 LRC回路の周波数特性                     | 10 |

|     | 2.3.3 単一 di/dt キャンセラー回路の周波数特性         | 12 |

| 2.4 | 複数 di/dt 検出回路を搭載した高利得キャンセラー           | 12 |

| 2.5 | 実験結果                                  | 14 |

|     | 2.5.1 ノイズ源の設計                         | 14 |

|     | 2.5.2 ノイズプローブの設計                      | 15 |

|     | 2.5.3 測定環境                            | 15 |

|     | 2.5.4 基板ノイズの測定結果                      | 17 |

|     | 2.5.5 di/dt キャンセラーの周波数特性              | 17 |

|     | 2.5.6 ノイズの振幅とパワーの関係                   | 19 |

| 2.6 | スケーリングに対する考察                          | 21 |

| 第3章 | アナログ方式による雑音低減手法における諸問題                | 22 |

| 3.1 | di/dt キャンセラーの低減効果に関する解析               | 22 |

|     | 3.1.1 高周波用ソケットを用いた測定環境                | 22 |

|     | 3.1.2 能動的基板ノイズ低減手法の距離依存性              | 24 |

|     | 3.1.3 カップリング容量の解析と基板抵抗の推定             | 26 |

|     | 3.1.4 複数 di/dt キャンセラーの利得の解析           | 28 |

| 3.2 | di/dt キャンセラーによる基板ノイズ低減手法の問題点          | 30 |

|     | 3.2.1 高利得キャンセラーによる制約                  | 30 |

|     | 3.2.2 インピーダンス依存性                      | 30 |

| 第4章   | デジタル方式による雑音低減手法の提案                              | 32 |

|-------|-------------------------------------------------|----|

| 4.1   | デジタル制御キャンセラーの特徴                                 | 32 |

|       | 4.1.1 デジタル制御による制御性と拡張性                          | 32 |

|       | 4.1.2 基板ノイズの周期性                                 | 33 |

|       | 4.1.3 高ノイズ耐性                                    | 34 |

|       | 4.1.4 高利得キャンセルシステム                              | 34 |

| 4.2   | 本研究の目的・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・      | 34 |

| 4.3   | サンプリング回路の構成.................................... | 35 |

|       | 4.3.1 サンプリングオシロスコープの特徴                          | 35 |

|       | 4.3.2 サンプリング回路に求められる仕様と構成                       | 37 |

|       | 4.3.3 サンプリング回路のシミュレーション                         | 41 |

| 4.4   | キャンセラー回路の構成・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 43 |

|       | 4.4.1 パルス制御回路                                   | 43 |

|       | 4.4.2 出力段の構成                                    | 43 |

|       | 4.4.3 キャンセラー回路のシミュレーション                         |    |

| 第5章   | デジタル方式の雑音低減回路の設計と評価                             | 48 |

| 5.1   | シミュレーションによる検討                                   | 48 |

|       | 5.1.1 シミュレーション条件                                |    |

|       | 5.1.2 シミュレーション結果                                |    |

| 5.2   | デジタル方式基板ノイズ低減回路の設計                              |    |

| 5.3   | 測定環境                                            |    |

| 5.4   | 実験結果と今後の課題・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・  |    |

| 第6章   | 結論                                              | 55 |

| 参考文献  | t<br>t                                          | 57 |

| 発表文献  | 就                                               | 60 |

| 付録:IR | ドロップ除去の検討                                       | 61 |

| 付録:チ  | ップ写真一覧                                          | 63 |

|       |                                                 |    |

| 謝辞    |                                                 | 66 |

# 図目次

| 1.1  | ガードリング                                                             | 3  |

|------|--------------------------------------------------------------------|----|

| 1.2  | フィードバック系の基板ノイズ低減手法 [10]                                            | 4  |

| 2.1  | di/dt キャンセラーの概念図 [12]                                              | 6  |

| 2.2  | di/dt キャンセラーの構成 [13]                                               | 6  |

| 2.3  | 基板ノイズの位相ダイアグラム[12]                                                 | 7  |

| 2.4  | 差動増幅器の周波数特性                                                        | 9  |

| 2.5  | 増幅器の入力の等価回路・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                    | 10 |

| 2.6  | 単一 di/dt キャンセラーの周波数特性                                              | 11 |

| 2.7  | 複数 di/dt 検出回路を用いた高利得キャンセラーの概念図                                     | 13 |

| 2.8  | di/dt キャンセラーのチップ写真 (0.35μmCMOS プロセス)                               | 13 |

| 2.9  | ノイズ源の構成 [12]                                                       | 14 |

| 2.10 | 基板ノイズプローブ[12]                                                      | 15 |

| 2.11 | $g_m$ と $g_{bs}$ の比率                                               | 16 |

| 2.12 | 測定環境 (di/dt キャンセラー)                                                | 16 |

| 2.13 | 基板ノイズ波形 (@ f <sub>op</sub> =300MHz)                                | 18 |

|      | キャンセラーの利得 vs. 基板ノイズの振幅                                             | 18 |

| 2.15 | 基板ノイズのスペクトル分布 (@ fop=300MHz)                                       | 19 |

|      | ·                                                                  |    |

| 2.17 | ノイズ源の動作周波数 vs. ノイズパワー低減率                                           | 20 |

| 3.1  | 高速信号用ソケットを用いた測定環境・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・              | 23 |

| 3.2  | 異なるチップにおける基板ノイズの大きさ                                                | 23 |

| 3.3  | ノイズ低減率の距離依存性                                                       | 25 |

| 3.4  | ノイズ低減効果の距離依存性 $@f_{op}$ = $300MHz$ $\dots$ $\dots$ $\dots$ $\dots$ | 25 |

| 3.5  | 異なるカップリング容量によるノイズ低減効果の違い                                           | 27 |

| 3.6  | サイズの異なるキャンセラーのノイズ低減率の違い                                            | 29 |

| 3.7  | キャンセラーの利得 vs. ノイズ振幅変化                                              | 29 |

| 4.1  | 提案手法の全体図・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                       | 33 |

| 4.2  | 位相キャリブレーションによる本手法の利点                                               | 35 |

| 4.3  | デジタル制御キャンセラーの概念図                                                   | 36 |

| 4.4  | サンプリングオシロスコープの概念図                                                  | 37 |

| 4.5  | サンプリング回路の構成・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                    | 38 |

| 4.6  | コンパレータ回路の構成 [21]                                         | 39 |

|------|----------------------------------------------------------|----|

| 4.7  | DLL 回路の構成                                                | 40 |

| 4.8  | 位相検出回路                                                   | 41 |

| 4.9  | チャージポンプ回路                                                | 41 |

| 4.10 | サンプリング回路のシミュレーション結果                                      | 42 |

| 4.11 | ノイズキャンセル回路の回路構成                                          | 44 |

| 4.12 | ノイズキャンセル信号の生成フロー                                         | 45 |

| 4.13 | パルスジェネレータ回路の回路構成                                         | 46 |

| 4.14 | 出力段の構成                                                   | 47 |

| 4.15 | キャンセル回路のシミュレーション結果                                       | 47 |

| 5.1  | シミュレーション条件                                               | 49 |

| 5.2  | 位相キャリブレーション時の基板ノイズ波形・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |    |

| 5.3  | 最小化された基板ノイズ波形・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・        | 52 |

| 5.4  | デジタル制御キャンセラーのチップ写真 (90nm CMOS プロセス)                      | 53 |

| 5.5  | 測定環境 (デジタル制御キャンセラー)                                      | 53 |

| 5.6  | 基板ノイズ波形                                                  | 54 |

|      |                                                          |    |

| 6.1  | RC 積分回路                                                  | 61 |

| 6.2  | di/dt 積分回路出力と実際の電流波形の比較                                  | 62 |

| 6.3  | di/dt キャンセラー                                             | 63 |

| 6.4  | 複数 di/dt キャンセラー                                          | 64 |

| 6.5  | di/dt キャンセラー TEG1                                        | 64 |

| 6.6  | di/dt キャンセラー TEG2                                        | 64 |

| 6.7  | di/dt キャンセラー TEG3                                        | 65 |

| 6.8  | デジタル制御キャンセラー                                             | 65 |

# 表目次

| 1.1 | 高周波での受動素子を用いた基板ノイズ低減手法の問題点                     | 2  |

|-----|------------------------------------------------|----|

| 3.1 | 注入位置の異なる TEG                                   | 24 |

| 3.2 | 消費電力の距離依存性・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 26 |

| 3.3 | 設計した TEG の種類                                   | 27 |

| 3.4 | 設計した TEG <b>の</b> 種類                           | 28 |

| 6.1 | 提案手法の比較・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・    | 56 |

# 第1章

# 序論

### 1.1 背景

近年、LSI (Large Scale Integrated Circuit:集積回路)の微細化に伴い無線通信に向けたデジタル回路とアナログ回路が混載した SoC (System on Chip:システム・オン・チップ)の市場が拡大している。SoC は集積度を上げることで高性能だけでなく、多機能化・低コスト化を図ってきたが、一方で電源電圧の低電圧化、動作周波数の高速化によりデジタル・ブロックからのノイズの影響が無視できなくなってきている。デジタル回路から発生したノイズは同一基板内を伝搬し、センシティブなアナログ回路の動作に影響するため、設計における重大な問題となっている。このノイズは基板ノイズと呼ばれる。アナログ回路は閾値付近にバイアス点が置かれることが多いため、基板ノイズによる閾値の変動の影響を受けやすい。そのため基板ノイズはアナログ回路において設計時に予想される利得・周波数帯域が得られない、またジッタ発生などの主な要因となる。またデジタル回路においても、トランジスタの応答速度が変動するため、論理合成時のタイミング制約を満たさなくなり、結果ロジックエラーを引き起こす要因となる。

基板ノイズの発生する原因は大きく

- 電源・グラウンド線とのカップリングによって生じるノイズ

- ソース・ドレインの電圧が高速に変動し、 $C \times dv/dt$  の電流が基板に流れこむことによるノイズ

- 電界によって加速されたドレイン端付近の電子が衝突を繰り返し、生成したホールが基板に流れこむことによるノイズ

の3つに分けられる[1]。中でもラッチアップを避けるため基板はグランド線とたくさんのコンタクトで接続されるため、特にグランド線とのカップリングの影響が支配的であることが知られている[2][3]。

グランド線に発生するノイズは、デジタル回路に流れる過渡的な大電流がグランド線内の寄生因子 (寄生抵抗  $R_{gnd}$ 、寄生インダクタンス  $L_{gnd}$ ) を通ることで生じる。よって簡単に次の式で表すことが出来る [4]。

第1章 序論 2

|                                   | Type        | Problems             |

|-----------------------------------|-------------|----------------------|

| Blocking Triple Well, Deep N-well |             | Less Capacitive      |

|                                   | Trench, SOI |                      |

| Absorption                        | De-cap      | Parasitic inductance |

|                                   | Guard Ring  |                      |

表 1.1 高周波での受動素子を用いた基板ノイズ低減手法の問題点

$$V_{gnd\_noise} = IR_{gnd} + L_{gnd} \frac{di}{dt}$$

(1.1)

このノイズがカップリングにより、基板内の抵抗によって減衰しながら伝搬する。 一般にデジタル回路とアナログ回路にはそれぞれ別の電源が与えられるため、基板 電圧変動はアナログ回路において最も重要なパラメータであるといえる。

このような背景から基板ノイズを低減するための手法が近年多く提案されている。 以下従来の基板ノイズ低減手法について触れ、その問題点を述べる。

## 1.2 受動素子を用いた基板ノイズ低減手法の問題点

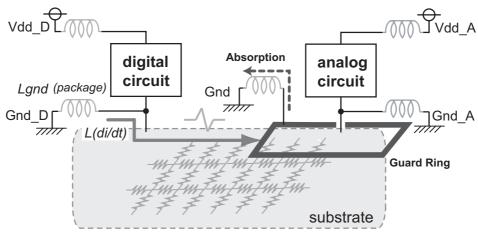

受動素子を用いた基板ノイズ低減手法の問題点について表 1.1 に代表的なものをまとめた。大きく分けると、(1) 基板ノイズがアナログ回路に伝搬しないようにキャパシタのような高インピーダンスのものでノイズを遮断する手法と(2) 低インピーダンスなグラウンドパスを作りノイズをチップ外に逃がす手法の2つに分類できる。これらの手法は一般的に基板ノイズを低減する有効的な手法であることが知られているが、両者の手法は次のような問題点を有する。(1) の手法では高周波になるにつれて容量効果が小さくなるので、高い周波数領域ではノイズを遮断できなくなる[5]。さらに SOI (Silicon on Insulator: シリコン・オン・インシュレータ) などのプロセスは非常に高価であることが知られている。(2) の手法では図 1.1 に示すようなガードリングという手法が存在するが、近年の LSI の高速化に伴いガードリング自身の寄生インダクタンス成分が無視できなくなり、ノイズを完全に除去できないという問題が存在する。逆にガードリングをつけることでノイズを増やしてしまうという報告例も少なくない。このような背景から近年では回路を使って能動的に基板ノイズを低減しようという研究が盛んに行われている。

#### 1.3 従来の能動的基板ノイズ低減手法の問題点

能動的基板ノイズ低減手法は対象となるノイズに対して、ノイズと逆位相の信号を 生成し注入することによって基板ノイズを低減しようとする手法である[9][10][11]。 第1章 序論 3

図 1.1 ガードリング

ここでは簡単に従来の能動的基板ノイズ低減手法を紹介し、その問題点について ふれる。論文 [9] に提案されている手法は図 1.2 にように、反転増幅器を用いて基 板ノイズと逆位相の信号をリアルタイムで生成し、基板に注入するという手法であ る。論文[11]で提案されている手法は、基板バイアスの変動によってトランジスタ が電流を流した場合、そのトランジスタ内を流れる電流と同じ量の電流をカレント ミラーを用いて基板に注入するという手法である。ここで問題となるのは、2つの 従来手法がともにフィードバック系をなすところにある。フィードバック系では入 力が基板ノイズそのものであるため、ノイズを低減すれば入力が小さくなり、キャ ンセル信号が小さくなる。その結果ノイズが増減を繰り返すという不安定な動作に ロックしてしまうことがある。この場合十分にノイズを低減することが期待できな い。さらに前者の手法では、入力が基板ノイズそのもので小さいため高い利得の増 幅器が必要となり、増幅器の遅延によってキャンセル信号が基板ノイズに対して追 従することができなくなる。一般にこの増幅器の遅延がキャンセラーの周波数帯域 を律速するため、実用的な周波数帯域を実現することが難しい。このようにフィー ドバック型の能動的基板ノイズ低減手法には不安定な動作と狭周波数帯域という2 つの問題点がある。

## 1.4 研究の目的

このような背景から、より広帯域でより安定した能動的基板ノイズ低減手法を提案することを本研究の目的とする。そのためにはフィードバック系ではない基板とは独立した系からノイズキャンセル信号を生成することが必要であることが以上の説明から分かる。本研究ではこのようなフィードフォワード型の能動的基板ノイズ低減手法についてアナログ方式、デジタル方式の両手法について検討を行う。フィードフォワード型のキャンセラーにはフィードバック型のキャンセラーと異なり、キャンセラーを制御する必要性が生じるが、近年ではオンチップで電源ノイズ・基板ノ

第1章 序論 4

イズを測定する回路が数多く提案されており [6][7][8]、このような回路を利用することでフィードフォワード型のキャンセラーを制御することも容易になると考えられる。本研究ではアナログ方式によるノイズ低減手法として di/dt 検出回路を用いた能動的基板ノイズ低減手法について検討し、その改善と問題点ついて議論する。またデジタル方式によるノイズ低減手法としてデジタル制御パルス生成回路による基板ノイズ低減手法を提案し評価する。

## 1.5 本論文の構成

本論文の構成は以下のようになっている。第2章ではアナログ方式によるノイズ 低減手法として di/dt 検出回路を用いた基板ノイズ低減手法について紹介し、その解 析と改善点について説明する。第3章では、第2章で説明したアナログ方式による 基板ノイズ低減手法における諸問題について検討し、議論を行う。続いて第4章で はデジタル制御方式による基板ノイズ低減手法の提案を行い、第5章でそのシミュ レーション結果と設計、そして実験結果を示す。最後に第6章で結論を述べる。

図 1.2 フィードバック系の基板ノイズ低減手法[10]

# 第2章

# アナログ方式による雑音低減手法の評価

本章では、前研究により提案されている di/dt 検出回路を用いたフィードフォワード型能動的基板ノイズ低減手法 [12] に関して、さらなるノイズ低減に向けた検討を行う。

### 2.1 di/dt 検出回路を用いた能動的基板ノイズ低減手法の概要

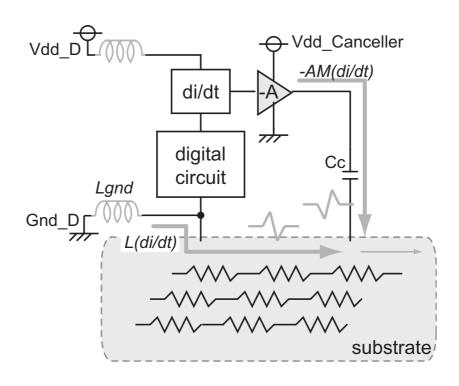

基板ノイズの主たる要因はデジタル回路とのカップリングである。基板はグラウ ンドレベルに安定させるため、グラウンドラインに接続されているが、これにより、 基板電圧はグラウンドラインの電圧ばらつき(グラウンドバウンス)の影響を強く受 ける[2][3]。論文[6]では、オンチップノイズ測定回路を用いて基板ノイズがグラウ ンドバウンスの約8分の1の振幅を持つ波形が得られることが示されている。グラ ウンドバウンスは、デジタル回路の過渡的に流れる電流 / とグラウンドラインのイ ンピーダンス  $(Z=R+j\omega L)$  の乗算によって表現され、回路の動作周波数が高くなっ てくるとL(di/dt)による電圧ドロップが顕著になると考えられる。つまり高周波にお いて基板ノイズはdi/dtにほぼ比例したノイズ波形を示すと仮定することができる。 このような di/dt に比例した信号は di/dt 検出回路を用いることで生成可能であるこ とが知られており[13]、di/dt 検出回路を用いたフィードフォワード型・基板ノイズ 低減手法 (di/dt キャンセラー) の概念図を図 2.1 に示す [12]。di/dt 検出回路はピック アップインダクタと差動増幅回路によって構成され、ピックアップインダクタはデ ジタル回路の電源線に結合するように配置する。di/dt 検出回路は電磁誘導によって ピックアップインダクタの両端にデジタル回路に流れる電流の時間変化  $dI_1/dt$  に比 例した電圧を誘起する。先に述べたように基板ノイズは di/dt に比例することから、 図 2.2 に示すようにピックアップインダクタを反転増幅器に接続することによって di/dt に比例した逆位相のキャンセル信号を生成することが可能となる。このキャン セル信号を基板ノイズに対して適切な位相で注入することができれば、基板ノイズ を低減することが可能となる。

前研究により提案された di/dt 検出回路を用いた能動的基板ノイズ低減手法 [12] は、フィードバック系ではないため広帯域で動作可能な安定な基板ノイズ低減手法として期待される。しかしながら前研究ではその低減率が 30 % 未満という結果か

図 2.1 di/dt キャンセラーの概念図[12]

図 2.2 di/dt キャンセラーの構成 [13]

ら、本章ではより効果的に基板ノイズを低減するdi/dt キャンセラーを実現することを目的とし、回路構成の解析と改善について言及する。

# 2.2 di/dt キャンセラーの低減効果に関する考察

前節で述べたとおり、前設計における基板ノイズ低減率は30%未満といまだ低い。その要因には di/dt キャンセラーの生成するキャンセル信号が基板ノイズに比べて小さいことが挙げられる。ここでは理想的な di/dt キャンセラーの基板ノイズ低減効果について検討する。

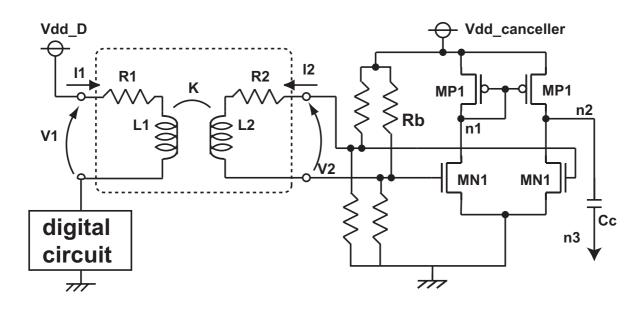

基板ノイズは前章で述べたとおり、グラウンドバウンスによって支配的に発生し、そのノイズは  $IR_{gnd}+L_{gnd}(di/dt)$  に比例する。ここで di/dt キャンセラーの利得を変化させながら基板ノイズの位相変化を測定することで基板ノイズの各成分を解析した。測定結果によって得られた基板ノイズの位相ダイアグラムを図 2.3 に示す。横軸はIR 成分を表し、縦軸はL(di/dt) 成分を表す。キャンセラーの利得を大きくすると基板ノイズの位相が徐々に変化していいる様子が観測され、これは di/dt 成分の減少に起因することがわかる。これにより di/dt キャンセラーによって基板ノイズの di/dt 成分のみの低減が出来ていることが確認できる。さらに、より高い利得を持ったキャンセラーを搭載することによって di/dt 成分を完全に除去することができれば、最大で 60%の基板ノイズが低減できることがわかる。そのため本章では 60%の基板ノイズが低減できることがわかる。そのため本章では 60%の基板ノイズを低減可能な di/dt キャンセラーを構築することを目標とし、キャンセラーの改善を行う。

図 2.3 基板 ノイズの位相ダイアグラム [12]

# 2.3 di/dt キャンセラー回路設計とその解析

簡単により大きな利得を得るにはトランジスタサイズやインダクタサイズを大きくすることが考えられるが、より定量的な設計論を導くためにdi/dt キャンセラーの周波数解析を行い、より効果的な設計論を導く。この設計においてもっとも重要なことは基板ノイズに対して逆相のキャンセル信号を作り出すことであり、キャンセル信号の位相変動が大きいとdi/dt キャンセラーは基板ノイズを増やしてしまうことになる。この制約のために、周波数軸上での位相特性は広帯域で安定であることが求められ、必要な利得との間にトレードオフが生じる。ここではdi/dt キャンセラーの周波数特性を利得と位相の観点からまとめ、適切な位相特性の範囲内で最大の利得を得ることを目的とする。di/dt キャンセラーの周波数特性は図 2.2 における増幅器の周波数特性と増幅器の入力側のLRC 回路の 2 つのLP (Low Pass: 低域通過)特性によって律速される。以下より、この 2 つの特性を解析し、di/dt キャンセラー全体の周波数特性について言及する。

#### 2.3.1 差動増幅器の周波数特性

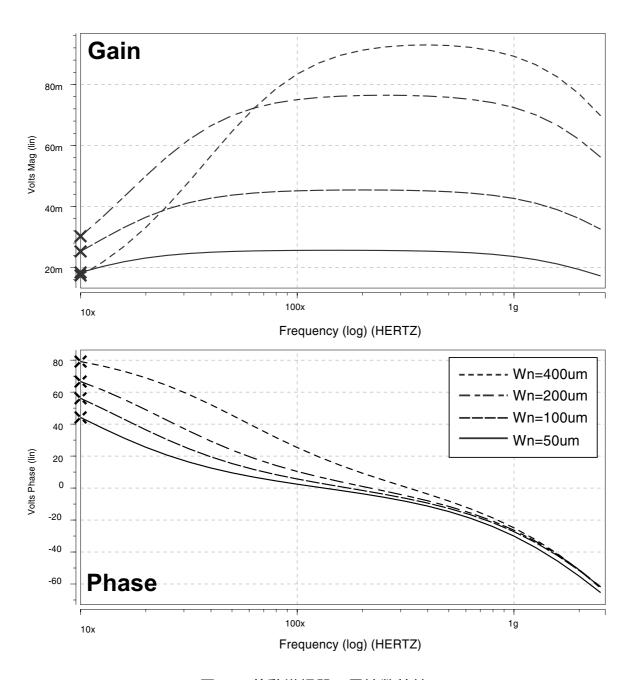

増幅器の出力は基板そのものであり、基板は純抵抗としてモデル化できることが知られている[14][15]。この低負荷は1段構成の増幅器の広帯域特性を実現させることを可能とさせ、一方で利得の高い多段回路では逆に周波数特性が劣化する。そのため、今回の設計では4トランジスタで構成させる1段の反転増幅器を用いる。基板抵抗は十分に小さいことが予想されるため、この回路構成において高い利得を得るためには、よりトランジスタサイズの大きい反転増幅器が必要となる。増幅器のトランジスタサイズを変動させた際の増幅器の周波数特性を図2.4に示す。

ここで P 型トランジスタのサイズは N 型トランジスタの 2 倍とし、出力のカップリング容量  $C_c$ 、基板の負荷抵抗  $R_{sub}$  はそれぞれ 25pF、 $30\Omega$  とした。低周波領域では出力につけたカップリング容量と基板抵抗との間で HP (High Pass:高域通過)特性が生じる。この HP 特性は次の式で表される。

$$V_{HPF_{out}} = \frac{1}{1 + j\omega R_{sub}C_c} V_{HPF_{in}}$$

(2.1)

そのため、HP カットオフ周波数は  $1/(2\pi R_{sub}C_c)$  で表される。この特性はカップリング容量  $C_c$  を十分に大きくすることで十分な帯域を特性を実現することができる。一方で、差動増幅器の周波数特性はトランジスタのオン抵抗が負荷抵抗に比べて十分大きいとすると、増幅器の"本質的な"遅延によって律速され、以下の式によって表される。

$$f_{amp} = \frac{g_{m_{MP1}}}{C_E}, \tag{2.2}$$

ここで $C_E$  はカレントミラーの2つのP型トランジスタのゲート容量である。図 2.4 に示すように、増幅器のトランジスタサイズを変化させても出力抵抗が非常に小さ

い場合には増幅器は増幅器のトランジスタサイズによらず、フラットな利得を持つ 広周波数帯域を有することが可能となる。位相特性も100MHz-700MHz において比 較的小さな位相回転しか許さないことが分かる。

図 2.4 差動増幅器の周波数特性

#### 2.3.2 LRC 回路の周波数特性

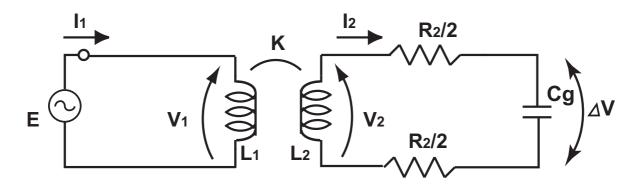

増幅器の入力特性は、スパイラルインダクタと差動増幅器の容量成分を含め図 2.5 のような等価回路で表すことができる。相互インダクタンス M は

$$M = K\sqrt{L_1L_2} \tag{2.3}$$

で表され、キルヒホッフの法則により以下の等式が導かれる。

$$j\omega MI_1 - (R + j\omega L_2 + \frac{1}{j\omega C_g})I_2 = 0$$

(2.4)

これにより、増幅器の差動入力電圧 AV は次の式で表されることが分かる。

$$\Delta V = \frac{M}{(1 - \omega^2 C_g L_2) + j\omega C_g R_2} \frac{di}{dt}$$

(2.5)

低周波領域では入力はM(di/dt)に近似することが可能であるけれども、周波数が高くなってくるとこの近似が適用できなくなってくる。ここにキャンセラーの利得と位相回転のトレードオフが生じることがわかる。位相特性を安定にするためには、 $j\omega C_{g}R_{2}\ll 1$ が必要となり、次のLP特性が得られる。

$$f_t \ll f_R = \frac{1}{2\pi C_g R_2} \tag{2.6}$$

さらに、di/dt キャンセラーの利得をフラットにするためには、さらに次の不等式が得られる。

$$f_t \ll f_L = \frac{1}{2\pi \sqrt{C_g L_2}} \tag{2.7}$$

キャンセラーはこれらの2つのLP (Low Pass: 低域透過)特性を満たす必要がある。

図 2.5 増幅器の入力の等価回路

図 2.6 単一 di/dt キャンセラーの周波数特性

#### 2.3.3 単一 di/dt キャンセラー回路の周波数特性

増幅器の周波数特性とLRC回路の周波数特性を用いて、di/dt キャンセラー全体の 周波数特性が得られる。図 2.6 にその特性を示す。

この特性では、利得は $30\Omega$  の出力抵抗を接続した際のキャンセル電流と1 次側のインダクタに流れる電流比を表し、位相特性はその位相差を表している。この位相差は一次側の電流に対して90 度進んでいることが求められる。図2.6 が示すように、増幅器の利得を上げるためにトランジスタサイズを大きくすると、特に $C_g$  と $L_2$  の共振特性と $C_g$  と $R_2$  による LP 特性によって位相特性が著しく劣化することが分かる。位相特性はノイズをキャンセルする上でもっとも重要な特性であるので、利得を大きくすることが難しい。

それぞれのLP特性を周波数特性を満たしながら、ここで基板抵抗がトランジスタのオン抵抗に比べて非常に小さいとすると、ノイズキャンセル信号は次の式で表すことができる。

$$I_{cancel} = \frac{M}{(1 - \omega^2 C_o L_2) + j\omega C_o R_2} \frac{di}{dt} g_m$$

(2.8)

この式からわかるように、比較的一定の位相特性を満たすには、十分な大きさのトランジスタサイズを設定することができない。前研究では、これらの制約によって単一の di/dt キャンセラーでは十分なキャンセル信号を生成することができないことが示された。

### 2.4 複数 di/dt 検出回路を搭載した高利得キャンセラー

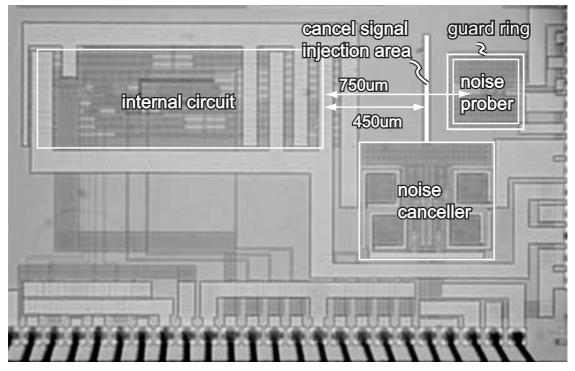

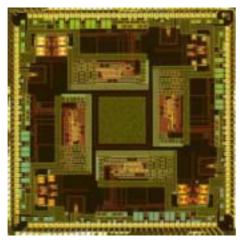

このような考察から、位相特性の良い di/dt キャンセラーを複数搭載し、利得を調整することができる高利得キャンセルシステムを構築した。図 2.7 に概念図を示す。各 di/dt キャンセラーは独立にキャンセル信号を生成することができるので、位相特性を小さく保ったまま利得を高くすることが可能となる。入力 (1 時側に流れる電流)はキャンセラーとは独立であるため、キャンセル信号は di/dt キャンセラーの数に比例する。本提案回路は Rohm 社の  $0.35\mu mCMOS$  プロセスを利用して設計を行い、設計したチップ写真を図 2.8 に載せる。レイアウトサイズは  $3.0mm \times 1.8mm$  となっている。基板ノイズは左に示したノイズ源 (内部回路) によって発生され、基板内を伝搬する。右側に設けたノイズプローブはオフチップ観測用に搭載し、基板ノイズを増幅している。ノイズプローブはノイズ源から、 $750\mu m$  離れたところに位置している。キャンセル信号を注入する位置はその中間に配置し、ノイズ源から  $450\mu m$  離れている。ノイズ源クロック毎に電流を消費する仮想的なデジタル回路を想定している。測定ではキャンセラーをオン/オフした時の、プローブの出力である基板ノイズの測定を行った。

図 2.7 複数 di/dt 検出回路を用いた高利得キャンセラーの概念図

図 2.8 di/dt キャンセラーのチップ写真 (0.35µmCMOS プロセス)

## 2.5 実験結果

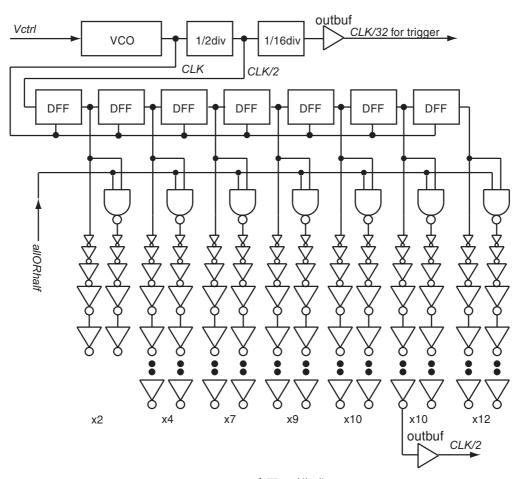

#### 2.5.1 ノイズ源の設計

図 2.9 にノイズ源の回路構成を示す。テスト回路は VCO (Voltage Controled Oscillator : 電圧制御発振器) を搭載し、DC 電圧  $V_{ctrl}$  を用いてノイズ源の動作周波数を調整した。分周回路は 10101… の信号がシフトレジスタに入力する。D フリップフロップを縦列に接続し、各フリップフロップの出力にインバータチェーンを接続することで、クロック毎にインバータチェーンが動作する。このようにクロックに同期して電流を消費するため、仮想的なデジタル回路として想定できる。この回路は一般的なノイズ源として利用されているものであり [2]、クロック度に同じ電流を消費し、その過渡的な電流によってグラウンドノイズが発生し、コンタクトを通して基板ノイズが伝搬する。

図 2.9 ノイズ源の構成[12]

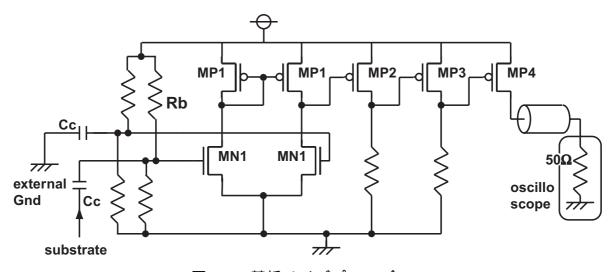

#### 2.5.2 ノイズプローブの設計

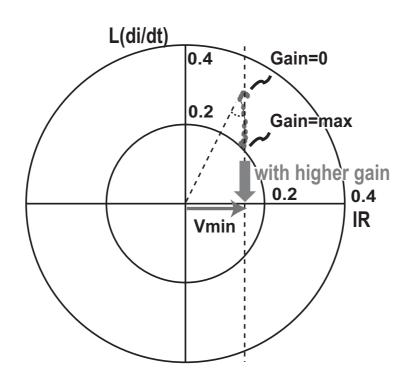

基板ノイズを測定するプローブ回路を図 2.10 に示す。初段に差動増幅回路を用いて一方の端子に参照 GND に接続し、もう一方に基板を接続する。入力端子は抵抗  $R_b$  を用いて  $1/2V_{half}$  に安定されており、増幅器は最大の利得が得られるように設定する。バイアス抵抗  $R_b$  は AC 信号にとって開放端になるように十分大きく設定した  $(R_b=10k\Omega)$ 。カップリング容量  $C_c$  を間に挟むことで動作点まで基板ノイズのレベルシフトを行い、後段は PMOS のみで構成されたソース接地回路で増幅を行う。

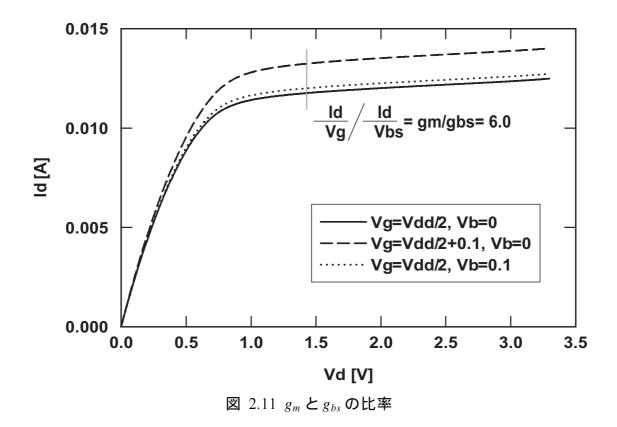

ここで NMOS は基板とコンタクトを持つため、基板電圧の変動によって基板ノイズの波形を変える恐れがある。そのため今回の設計では、増幅器の MN1 の基板コンタクトは基板に接続しないことでこの影響を軽減した。後段の PMOS ドライバにおいても基板コンタクトを除くために NMOS を必要としない構成を用いた。ここで  $\Delta I_d/\Delta V_g$  と  $\Delta I_d/\Delta V_{bs}$  との比率は  $g_m/g_{bs}$  で表され、図 2.11 に示すように HSPICE シミュレータにより 6.0 に設定した。

図 2.10 基板ノイズプローブ[12]

#### 2.5.3 測定環境

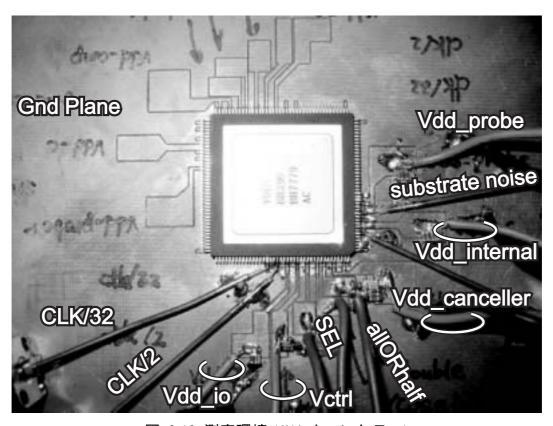

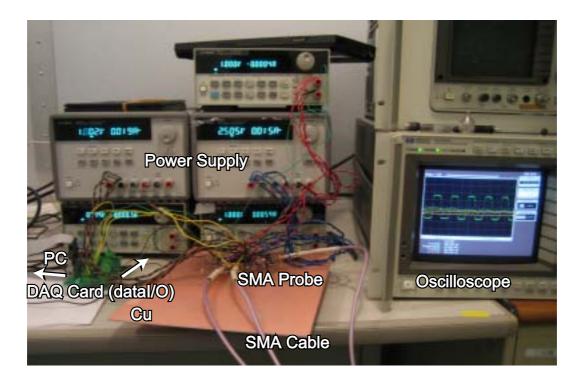

チップの測定環境を図 2.12 に示す。高周波のノイズ波形を測定するために、チップをグラウンドに落とした銅板上にマウントし、パッケージピンから SMA プローブでの測定を行った。内部回路、キャンセラー、プローブ、IO それぞれの電源は DC 電源からリード線を通して供給されている。それぞれのパーケージピンは銅板上の"シマ"にマウントされ、各"シマ"の電圧は複数のデカップリング容量によって安定化されている。高速なクロック (CLK/2、CLK/32) や測定対象である基板ノイズの出力ピンには  $50\Omega$  の伝送線路を直接接続し、できるだけ反射を減らすように測定環境を構築した。測定はシールドルーム内で行い、測定には HP54750 オシロスコープを用いた。

図 2.12 測定環境 (di/dt キャンセラー)

#### 2.5.4 基板ノイズの測定結果

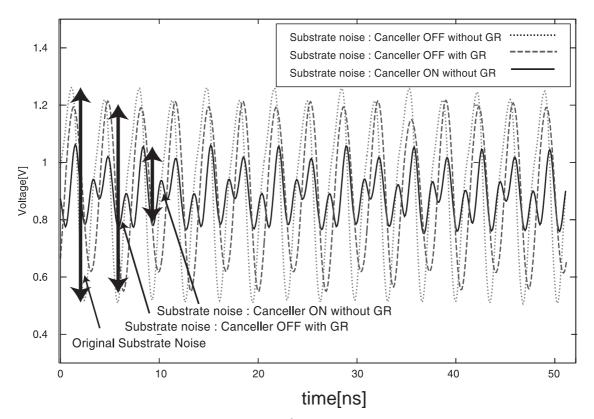

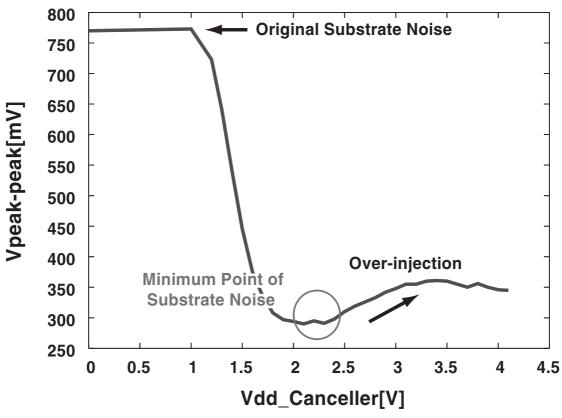

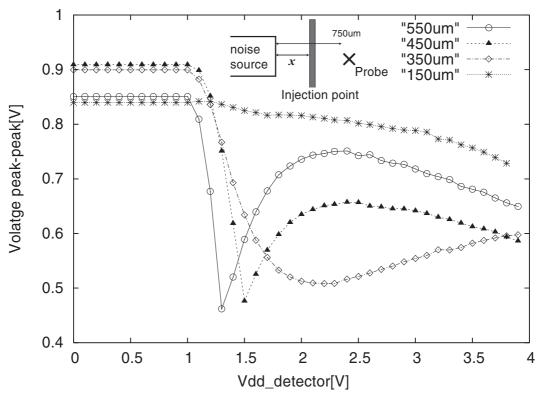

ノイズ源の動作周波数を 300MHz に設定し、キャンセラーをオフ時/オン時の基板 ノイズの様子を図 2.13 に示す。横軸は時間、縦軸はプローブの出力電圧値を示して いる。キャンセラーのオフ時/オン時というのは、図 2.2 に示す *Vdd\_canceller* が 0V の時の基板ノイズの様子と *Vdd\_canceller* をスイープして最も基板ノイズが低減し た時の基板ノイズの様子を示している。

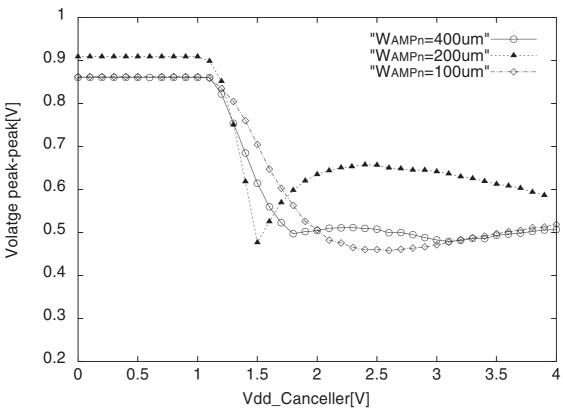

これについて以下に説明する。今回アナログ方式のフィードフォーワード型のキャンセラーを提案しているため、どの程度の振幅をもったキャンセル信号を基板に注入すべきかを制御する必要がある。そのため実験では、キャンセラーの電源電圧 *Vdd\_canceller* をスイープし、キャンセラーの利得を変動させながら基板ノイズの振幅の変化を測定した。図 2.14 に示すようにキャンセラーの電源電圧を 0V から徐々に大きくしていくと、1.3V あたりから基板ノイズの振幅が急激に減少する。これは反転増幅器が線形状態に入ったものと考えることができる。1.6V あたりになると基板ノイズは一定値に収束し、それよりもキャンセラーの利得を高くすると、逆に基板ノイズの振幅が徐々に増加していく様子が見てとれる。これは、キャンセル信号が過注入になっていることが考えられ、さらに電圧を高くするとキャンセラーが飽和状態に入り振幅が安定している様子が分かる。つまり、キャンセラーを動作させる場合には基板ノイズがもっとも減衰する最小点が見られることがわかり、先ほど図 2.13 で示したキャンセラーがオンの時の波形はこのときの状態を指している。

図 2.13 から分かるように、ノイズの振幅に注目すると、di/dt キャンセラーをオンした場合は最小で 62%のノイズが低減できることがわかった。ノイズの低減率は以下の式で定義する。

Suppression Ratio [%] =

$$\frac{Vpp_{canceller:OFF} - Vpp_{canceller:ON}}{Vpp_{canceller:OFF}} \times 100$$

(2.9)

一方で、プローブを囲んだガードリングを接地した場合には 12%のみのノイズ低減が見られ、di/dt キャンセラーのほうがより有効な基板ノイズ低減効果を有していることがわかった。

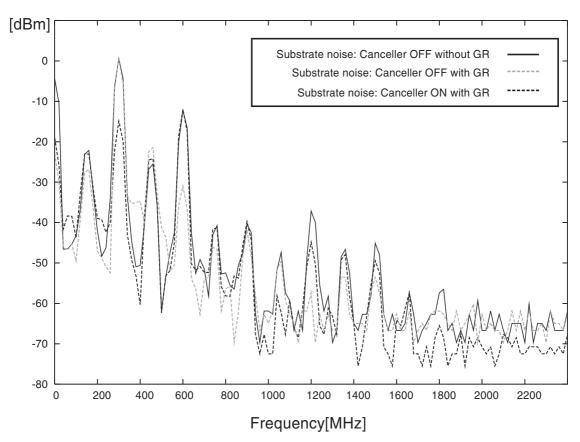

#### 2.5.5 di/dt キャンセラーの周波数特性

続いて di/dt キャンセラーの周波数特性について解析を行った。図 2.15 は先ほどの動作周波数を 300MHz に設定した場合の、基板ノイズのスペクトル分布を示したものである。このスペクトル分布はスペクトルアナライザを用いて測定したものであり、縦軸の単位は [dBm] を用いている。ガードリングを用いた場合はすべての帯域全般の基板ノイズが減衰しているのに対し、di/dt キャンセラーを用いた場合は、ノイズの中心周波数 (300MHz) 付近のノイズが大きく低減されていることがわかる。ノイズの中心周波数はクロックの中心周波数と同じであり、電流のスペクトル分布も同様に 300MHz に集中する。di/dt キャンセラーのゲインは 1 時側 (デジタル回路)

図 2.13 基板ノイズ波形 (@f<sub>op</sub>=300MHz)

図 2.14 キャンセラーの利得 vs. 基板 ノイズの振幅

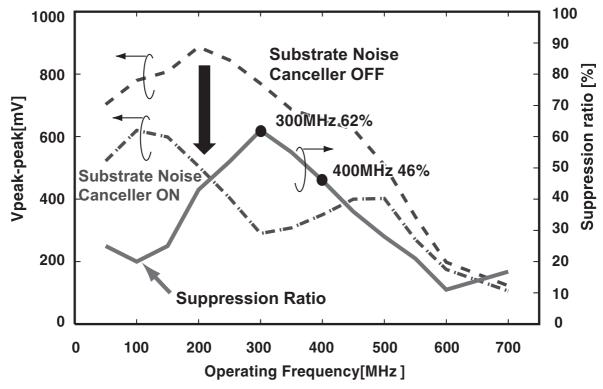

に流れる電流に比例するため、中心周波数付近のノイズが最も効率的に低減されていると考えられる。続いて、ノイズ源の動作周波数を変動させながら、キャンセラーの基板ノイズ低減率の解析を行った。結果を図 2.16 に示している。測定は動作周波数 100MHz から 700MHz の範囲で行い、結果から 10%から 62%のノイズ低減効果が得られることが分かった。

図 2.15 基板ノイズのスペクトル分布 (@fon=300MHz)

# 2.5.6 ノイズの振幅とパワーの関係

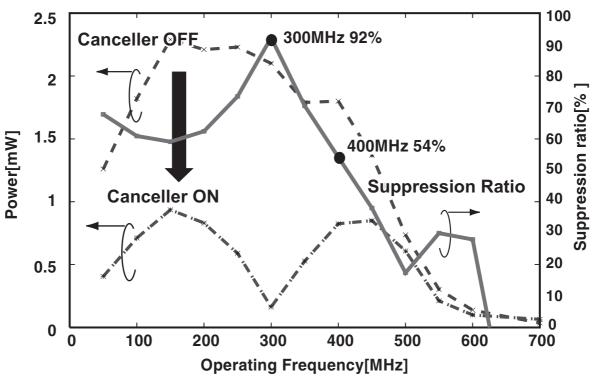

続いてノイズの振幅とパワーの関係性について考察を行う。基板ノイズのスペクトル分布(図 2.15 参照)に対して各周波数のスペクトル分布を積分した値をノイズのパワーとして定義し、各動作周波数でのパワーの低減率を測定した。測定結果は図 2.17 となり、ノイズの振幅で評価した際と同様にノイズのパワーのスペクトル分布が減少している様子がみてとれる。しかもその低減効果はノイズの振幅したときの同じように、動作周波数が 300MHz のときに最大の低減率を示した。このためノイズの振幅低減することとパワーを低減することはほぼ同等の効果が得られることがわかった。

図 2.16 ノイズ源の動作周波数 vs. ノイズ振幅低減率

図 2.17 ノイズ源の動作周波数 vs. ノイズパワー低減率

## 2.6 スケーリングに対する考察

最後に提案回路における面積のオーバーヘッドと基板ノイズ削減率に関する考察を行う。高い利得を得るためには1次側の電源線と高い結合が必要となり、必然的に2次側のインダクタのサイズは大きくなる。インダクタサイズとその個数は1次側に流れる電流 I<sub>1</sub> とデジタル回路が発生する基板ノイズの量によって決定され、インダクタの面積が支配的になることは必然である。しかしながらスケーリングにより動作周波数が高くなると、電流の時間変化 di/dt も増加するので 2 次側の誘電起電力は大きくなる。このことは"より少ない小さい"インダクタで十分なキャンセラーが実現できることを期待させる。

さらにカップリング容量はLow-Kの導入によってスケーリングによっても面積のスケーリングが期待できないが、動作周波数の高周波数化によって、必要なカップリング容量のサイズも小さくなる。そのためカップリング容量のハードウェアコストは回路の動作周波数に反比例して小さくなることが期待される。

# 第3章

# アナログ方式による雑音低減手法における諸 問題

前章ではシミュレーション上での単一の di/dt キャンセラーの周波数特性を解析し、複数のキャンセラーを搭載することでキャンセラーの利得を上げ、最大で 62%のノイズが低減できることを実証した。しかしながら、シミュレーション上での di/dt キャンセラーの周波数特性は"キャンセラーの負荷である基板が増幅器に対して十分に低負荷"という仮定条件の下で成立し、さらにフィードフォワード型のキャンセラーにおいてキャンセル信号を注入する位置による影響やカップリング容量による影響に対しては研究の例がなく、検討が必要である。ここでは複数の異なる di/dt キャンセラーの TEG (Test Element Group: 特性評価用素子)を設計し、その効果を解析することでアナログ方式によるノイズ低減手法の効果を解析し、アナログ方式による基板ノイズ低減手法の問題について議論する。

# 3.1 di/dt キャンセラーの低減効果に関する解析

#### 3.1.1 高周波用ソケットを用いた測定環境

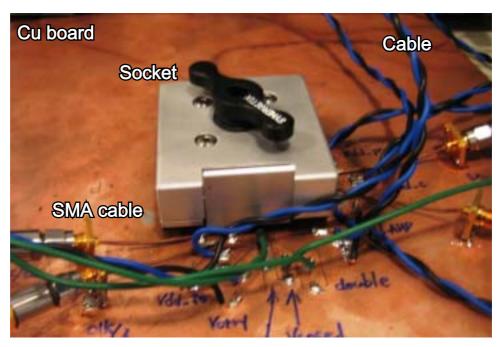

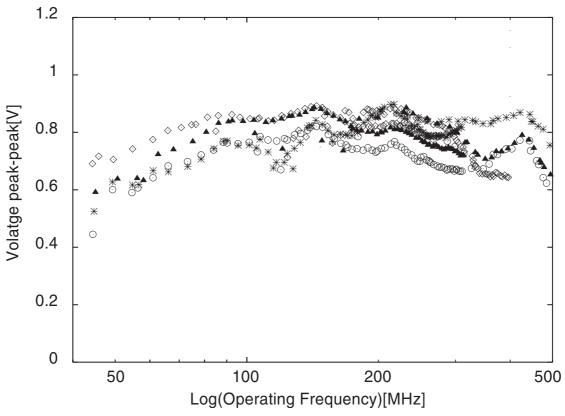

第1章で述べた通り、基板ノイズはデジタル回路のグランドバウンスの影響を強く受けるため、グラウンドのインピーダンスに強く依存する。そのため、測定環境の誤差によって周波数による基板ノイズの変動を引き起こしかねない。これは複数の異なるチップを測定する上で比較をより困難にするため、今回の測定では高速信号を測定するためのソケットを利用し、リード線、デカップリングコンデンサによるインピーダンスの変動を取り除いた。図3.1 にソケットを用いて測定した場合の測定環境を示す。ソケットは500MHz 以下の周波数帯域を有している。このソケットを銅板上にマウントし、ソケットから銅板上のパターンを通してSMA プローブを用いて CLK/2 信号、ノイズ信号、トリガ (CLK/32) 信号を取り出す。銅板パターン上にデカップリングキャパシタ、リード線を半田付けしてあるため、ソケット内のチップを変えることでインピーダンスのばらつきは"チップとソケットとの接触"と"チップ内のプロセスばらつき"の2つのみと考えられる。図3.2 に複数のチップにおけるキャンセラーがオフ時の基板ノイズの振幅を測定した。横軸はノイズ源である

図 3.1 高速信号用ソケットを用いた測定環境

図 3.2 異なるチップにおける基板ノイズの大きさ

デジタル回路の動作周波数、縦軸は基板ノイズの振幅を表している。これからみて分かるように、異なるチップにおいても基板ノイズはほぼ同量の振幅を示し、これらの効果はほとんど無視できるものと考えることができ、ノイズ低減率は基板ノイズの振幅に依存せず、キャンセラーの生成するキャンセル信号にのみ依存すると考えることができる。これによりキャンセラーの低減率によって異なるチップの評価が可能となる。

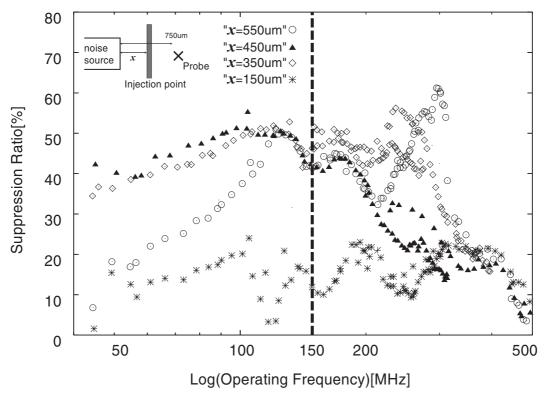

#### 3.1.2 能動的基板ノイズ低減手法の距離依存性

|           | Distance from Noise Source |

|-----------|----------------------------|

| Position1 | 150μm                      |

| Position2 | 350μm                      |

| Position3 | $450\mu m$                 |

| Position4 | 550μm                      |

表 3.1 注入位置の異なる TEG

ここではフィードフォワード型・能動的ノイズ低減手法において、キャンセル信号 を注入する最適な位置について検討する。キャンセル信号を注入する最適な位置を 検討することは、より小さな利得で十分なキャンセル信号を生成できることを期待 させる。設計した TEG はノイズ源の右端のコンタクトから表 3.1 に示してある距離 だけ離れたところにメタルから P+コンタクトで P 基板にキャンセル信号を注入する ように設計した。図3.3にノイズ源の動作周波数を変化させながら測定した基板ノ イズの低減率を示す。横軸は対数表示でノイズ源の動作周波数を表す。ここで、各 低減率はキャンセラーがオフ時の場合の基板ノイズの振幅と図 2.14 に示してあるノ イズの振幅の最小値との比を指す(式2.9)。図3.3を見て分かるように、注入位置が ノイズ源に近いほど基板ノイズの低減率が低く、注入位置がノイズ源から離れるに したがって基板ノイズの低減率が一定値に飽和することがわかる。この結果を解析 するために、各チップのノイズ源の動作周波数を 150MHz に設定した際の基板ノイ ズの変化を観測した。注入位置の異なる各キャンセラーにおいて、キャンセラーの 利得を変動させ、基板ノイズの振幅を測定すると図 3.4 のような実験結果が得られ た。利得はキャンセラー電源電圧を変動することによって調整した。注入位置がノ イズ源からそれぞれ350、450、550µm離れている場合、キャンセラーの利得を高く するにつれ基板ノイズの振幅が減少し、ある点で飽和する様子が見られる。一方、 ノイズ源に最も近い 150μm の場合、この飽和が見られない。さらにノイズ源から 350、450、550µm離れている場合において、キャンセラーとノイズ源の距離が離れ れば離れるだけ"より小さな"利得で基板ノイズが最小値に達する様子がわかる。

基板は前章にでも述べたように、抵抗網としてモデル化することができる[14][15]。

図 3.3 ノイズ低減率の距離依存性

図 3.4 ノイズ低減効果の距離依存性 @ $f_{op}$  = 300MHz

|                   | Noise Source | 350µm | 450μm  | 550µm  |

|-------------------|--------------|-------|--------|--------|

| Power             | 110mW        | 122mW | 13.8mW | 3.8mW  |

| Ratio             | 100%         | 111%  | 12.5%  | 3.45%  |

| (Canceller/Niose) | 100%         | 11170 | 12.370 | 3.4370 |

表 3.2 消費電力の距離依存性

そのためノイズ源から発生したノイズは減衰しながら伝搬していくことが予想される。このことから基板ノイズは距離が離れるほど減衰するので、小さい利得で十分なノイズ低減を実現することができる。このことは「より小さな面積」でキャンセラーを構成することが可能であることが期待され、さらに消費電力においても「より低消費」で実現できることが期待できることがわかる。表 3.2 に動作周波数 150MHz の時の消費電力の比較を示す。表ではノイズが最小値になったときのキャンセラーの消費電力を表し、比率はノイズ源の消費電力に対するキャンセラーの消費電力の割合を表す。ノイズ源に対して消費電力は遠くなればなるほど低い利得でノイズを低減できるので、低い消費電力で基板ノイズをキャンセルできることがわかった。

周波数特性においても、高い周波数においてはキャンセラーのLP (Low Pass:低域通過)特性よって十分なキャンセル信号を生成することができなくため、ノイズ源から注入位置を遠ざけることでキャンセラーの周波数帯域の向上も期待できる。

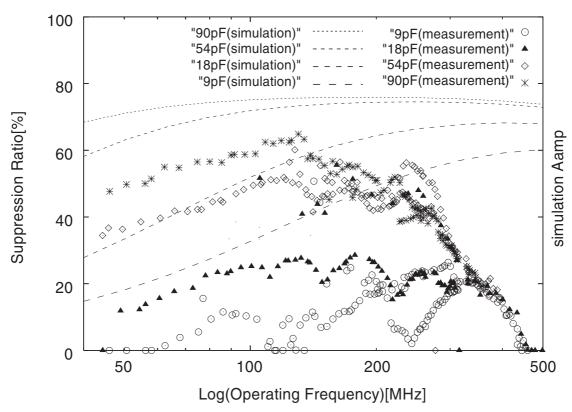

#### 3.1.3 カップリング容量の解析と基板抵抗の推定

続いてカップリング容量負荷に関する検討を行う。出力のカップリング容量は第2章で説明したとおり基板抵抗と HPF (High Pass Filter :高域通過フィルタ)を形成する。そのハイパス特性は入力信号  $V_{HPF_{int}}$  と出力信号  $V_{HPF_{out}}$  を用いて

$$V_{HPF_{out}} = \frac{1}{1 + j\omega R_{sub}C_c} V_{HPF_{in}}$$

(3.1)

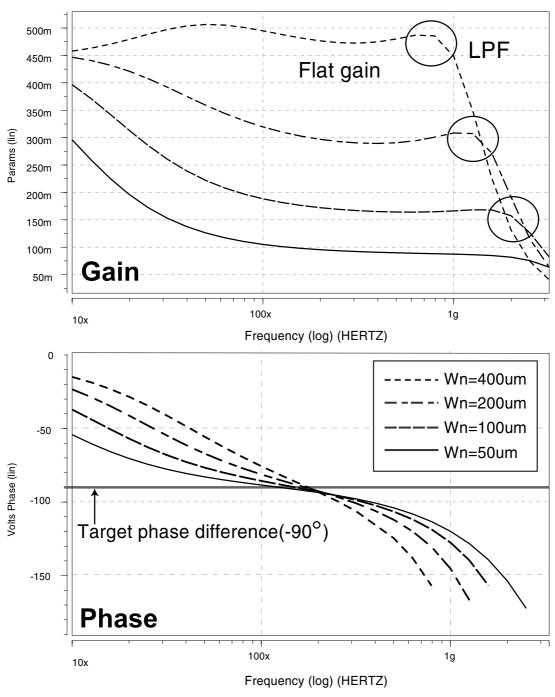

であると想定されるため、設計したカップリング容量から基板抵抗を推定するができる。設計した TEG は表 3.3 に示してある。 $Wn_{AMP}$ 、 $Wp_{AMP}$  はそれぞれ増幅器の NMOS と PMOS のトランジスタサイズ、 $L_1$  と  $L_2$  はそれぞれ 1 次側と 2 次側のインダクタサイズ、、M は  $L_1$  と  $L_2$  の相互インダクタンス、 $C_c$  はキャンセラーの出力端のカップリング容量サイズを表す。ソケットを用いた測定結果を図 3.5 に測定結果を示す。結果から分かるように容量が高いほど高い低減効果を示すことを示していることがわかる。

ここでカップリング容量を 54pF と 90pF に設定した場合、動作周波数 220MHz の時にノイズ低減効果が等しくなる。このとき、両者は HP 特性を十分に示しているといえる。一方でカットオフ周波数の目安となる-3dB の減衰は今回の動作周波数の

|          | $Wn_{AMP}$ | $Wp_{AMP}$ | $L_1$  | $L_2$  | M      | $C_c$  |

|----------|------------|------------|--------|--------|--------|--------|

| $C_c$    | 200μm      | $400\mu m$ | 0.41nH | 53.3nH | 3.23nH | 54.0pF |

| $2C_c$   | $200\mu m$ | $400\mu m$ | 0.41nH | 12.1nH | 3.23nH | 89.9pF |

| $1/2C_c$ | $200\mu m$ | $400\mu m$ | 0.41nH | 12.1nH | 3.23nH | 18.1pF |

| $1/4C_c$ | $200\mu m$ | $400\mu m$ | 0.41nH | 12.1nH | 3.23nH | 9.1pF  |

|          |            |            |        |        |        |        |

表 3.3 設計した TEG の種類

図 3.5 異なるカップリング容量によるノイズ低減効果の違い

範囲では見られない。そのため今回の測定した周波数帯域 (40MHz から 150MHz 程度) は、54pF の時の HP カットオフ周波数よりも高く、十分な完全な HP 特性を示す 周波数よりも低い周波数帯にあたり、その HP 特性の差によって生まれるものである考えられる。

この測定結果をシミュレーションを用いて検討する。4Trで構成される差動増幅器を4つ並列接続し、負荷にカップリング容量と基板抵抗を接続し、出力の4HP特性について調べた。ここで基板抵抗は可変抵抗をモデルとし、注入位置から基板が負荷としてどの程度の抵抗に見えるかについて検討した。シミュレーション結果では抵抗は $20\Omega$ 程度を想定した時、測定結果と同等の4HP特性を示すことが確認できた(図 3.5)。単一の4Idは4HP中では基板抵抗と増幅器のオン抵抗の並

|              | $Wn_{AMP}$ | $Wp_{AMP}$ | $L_1$  | $L_2$  | М      | $C_c$  |

|--------------|------------|------------|--------|--------|--------|--------|

| $2W_{AMP}$   | 400μm      | 800µm      | 0.41nH | 53.3nH | 3.23nH | 54.0pF |

| $1/2W_{AMP}$ | 100μm      | $200\mu m$ | 0.41nH | 53.3nH | 3.23nH | 54.0pF |

| $1/4W_{AMP}$ | 50μm       | 100μm      | 0.41nH | 53.3nH | 3.23nH | 54.0pF |

| Std          | 200μm      | $400\mu m$ | 0.41nH | 53.3nH | 3.23nH | 54.0pF |

| $1/2L_2$     | 200μm      | $400\mu m$ | 0.24nH | 26.4nH | 1.63nH | 54.0pF |

| $1/4L_2$     | 200μm      | 400μm      | 0.14nH | 12.1nH | 0.78nH | 54.0pF |

表 3.4 設計した TEG の種類

列に接続した抵抗成分によって決まる。よって基板抵抗と同程度まで増幅器のサイズを大きくした場合、特性は増幅器のオン抵抗の影響が無視できなくなり、増幅器のオン抵抗と基板抵抗の並列抵抗によって決まる。さらに今回のように複数の di/dt キャンセラーを実装したことにより増幅器のオン抵抗は並列接続になるため、単一の場合よりも高いカットオフ周波数を示すようになる。これによりキャンセラーはより大きなカップリング容量が必要になる。

今回の実験では、100MHz 以上の基板ノイズに対しては 100pF 以上のカップリング容量が必要であることがわかった。

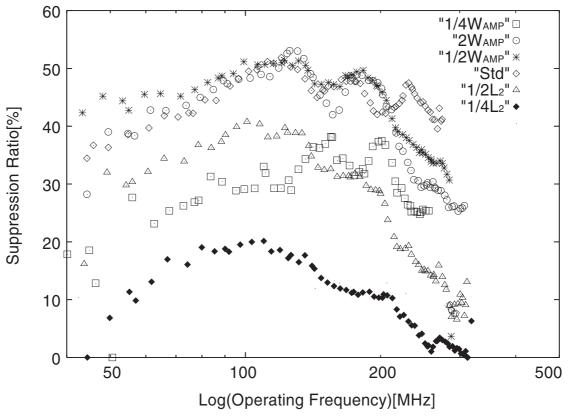

#### 3.1.4 複数 di/dt キャンセラーの利得の解析

ここではサイズの異なるキャンセラーを測定することで、di/dt キャンセラーの特性 について解析する。表 3.4 に実際に設計したチップの種類を載せる。 $Wn_{AMP}$ 、 $Wp_{AMP}$ はそれぞれ増幅器の NMOS と PMOS のトランジスタサイズ、 $L_1$  と  $L_2$  はそれぞれ 1 次側と2次側のインダクタサイズ、M は $L_1$  と $L_2$  の相互インダクタンス、 $C_c$  はキャ ンセラーの出力端のカップリングキャパシタサイズを表す。以下ではキャンセラー のサイズを変更したときの基板ノイズ低減率を測定し、前章でのシミュレーション のキャンセラーの特性との比較する。図3.6から分かるとおり、低い周波数ではト ランジスタサイズを大きくするとキャンセラーの低減率はある一定の値で飽和する ことがわかる。これはトランジスタサイズを十分に大きくするとノイズ di/dt 成分が 最大に削減されていることを示している。一方で、図 3.7 に 150MHz におけるキャ ンセラーの利得と基板ノイズの振幅の関係をプロットすると、増幅器のサイズを大 きい場合よりも、小さい増幅器のほうが低い利得で最小点に達した。第2章におけ る di/dt キャンセラーの特性は基板抵抗が増幅器のオン抵抗に比べて十分に小さい という仮定で成立する。この仮定においては負荷抵抗の基板が非常に低インピーダ ンスであるために、キャンセラーの利得は増幅器のトランスコンダクタンスのみに 依存することになる(第2章)。しかしながら、前節のカップリング容量と基板抵抗 による HP 特性を検証した結果、複数のキャンセラーを搭載した場合増幅器の出力

図 3.6 サイズの異なるキャンセラーのノイズ低減率の違い

図 3.7 キャンセラーの利得 vs. ノイズ振幅変化

インピーダンスは基板抵抗と同等程度まで低くなっていることがわかる。このように増幅器のサイズを大きくしトランジスタのオン抵抗が基板抵抗と同等近くまで低くなったとき、キャンセラーの利得は増幅器のトランスコンダクタンスと出力インピーダンスの乗算で表されるために、必ずしも増幅器のサイズに比例しない。さらに高周波領域においては入力側のLRC特性によってキャンセル信号の位相回転が大きくなる。また前節より、より大きなキャンセラーはより高いHPカットオフ周波数を持つことがわかる。これらの影響からトランジスタサイズを大きくすることとキャンセラーの数を増やすことによって得られる利得は基板抵抗によって律速され、またその位相特性はLP特性・HP特性ともに劣化する。

このことから複数キャンセラーを搭載してもキャンセラーの利得はキャンセラーの数に比例しなくなることがわかる。

一方でインダクタのサイズを2分の1、4分の1に下げると、低減率も同様に2分の1、4分の1になっている様子がわかる。つまり増幅器側で利得を稼ぐよりも、キャンセラーの入力信号を大きくすることの方がより大きなキャンセル信号を生成できることがわかる。

## 3.2 di/dt キャンセラーによる基板ノイズ低減手法の問題点

#### 3.2.1 高利得キャンセラーによる制約

前節での解析結果から、di/dt キャンセラーにおける基板ノイズ低減手法の問題点についてまとめる。

- 1. ノイズ源の近くでは十分にノイズを低減することができない。

- 2. 複数の di/dt キャンセラーを搭載することで基板抵抗と同程度まで出力抵抗が低くなり、より大きなカップリング容量が必要になる。

- 3. キャンセラーの出力抵抗が基板抵抗と同程度まで下がることで、キャンセラー の利得はキャンセラーの数に比例しなくなる。

- 4. サイズの大きい増幅器を搭載するよりも、サイズの大きいインダクタを搭載 するほうがより大きなキャンセル信号を生成できる。

上記の問題1.2.3 は、そもそもキャンセラーの入力信号が小さいことに起因する。di/dt キャンセラーの入力信号は4で示したように、デジタル回路に流れる電流とピックアップインダクタのサイズによってほぼ決まるため、面積、周波数特性を犠牲にして高い利得を必要とする。

#### 3.2.2 インピーダンス依存性

di/dt キャンセラーは基板ノイズの di/dt 成分を集中して低減しているため、図 2.14 に示すようにあるところで最小点がある。これはキャンセラーの周波数特性による

ものも考えられるが、抵抗成分によって生じる IR 成分が除去できてないことが考えられる。つまり di/dt キャンセラーのノイズ低減効果はキャンセラーの利得と同時に、そもそもグラウンドのインピーダンス分布に強く依存する。一方で、電源のインピーダンスはボード、パッケージ、オンチップ上の配線がそれぞれの寄生インダクタンスと寄生容量による共振特性を示すことが知られており、これらの電源モデルを正確に抽出することは非常に難しいとされている。これらのことから、設計者が設計時に di/dt キャンセラーによるノイズ低減効果を予想しにくいという問題点がある。またグラウンド線が抵抗成分によって支配的な場合では、di/dt キャンセラーは十分な基板ノイズ低減が期待できない。

これらの考察から分かるように、di/dt キャンセラーによるアナログ方式の基板 ノイズ低減手法には、入力信号が小さいため面積・周波数帯域を犠牲して高い利得 を必要とする点とキャンセラーの基板ノイズ低減率がグランド線のインピーダンス に依存するという二つの問題点がある。

# 第4章

# デジタル方式による雑音低減手法の提案

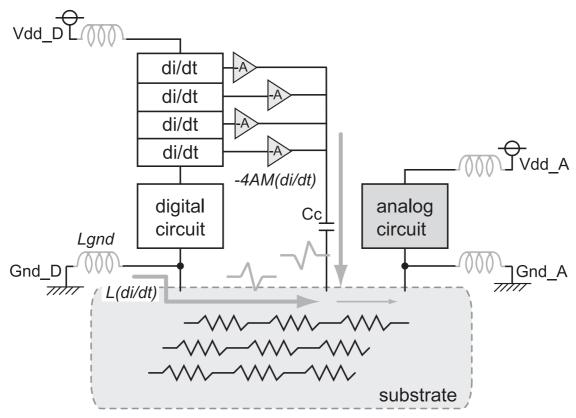

第1章で紹介した通り、従来のフィードバック型の能動的基板ノイズ低減手法ではフィードバック系をなすことにより狭周波数帯域で不安定であるという問題がある。一方で第2章で説明したdi/dt 検出回路を用いたアナログ方式によるフィードフォワード型・能動的基板ノイズ低減手法ではノイズ低減効果がグラウンド線のインピーダンス分布に依存するため、設計時にインピーダンスやノイズの振幅等を十分に見積もり必要があり、基板のインピーダンスが抵抗成分が支配的な場合有効な手段とはならない。またキャンセラーの入力信号が小さいため、非常に大きな面積や周波数帯域を犠牲にする必要がある。このような背景から、本研究ではキャンセル信号を自由に制御可能な高利得のフィードフォワード型・能動的基板ノイズ低減手法として、デジタル方式による能動的基板ノイズ低減手法を提案する。以下、提案手法の特徴と、その構成について説明する。

### 4.1 デジタル制御キャンセラーの特徴

#### 4.1.1 デジタル制御による制御性と拡張性

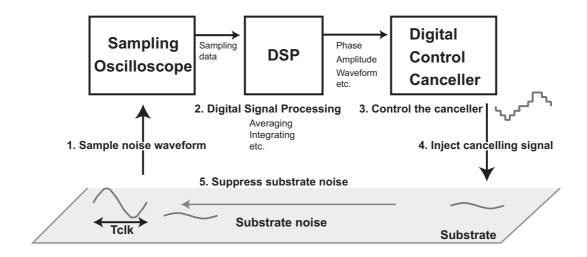

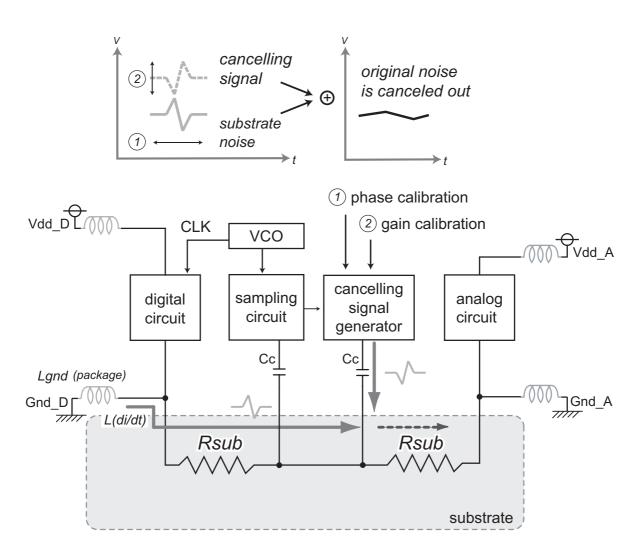

フィードフォワード型のキャンセラーではキャンセル信号の増減を制御するシステムが存在することを仮定しているため、その制御性は非常に重要である。近年LSIの高速化にともない、オンチップで電源ノイズ、グランドノイズ、基板ノイズなどを測定するオンチップノイズ測定回路が多く提唱されている[6][7][8]。これらの手法には高速なノイズがパッケージの寄生インダクタ成分によってチップの外まで伝わらないという背景から、ノイズをチップ内でサンプリングしてノイズ耐性の強いデジタル信号に変換してチップ外に出すといった手法も多い[6][16][17]。デジタル制御可能なキャンセラーはこれらののデジタル化されたノイズ波形のサンプリング結果を用いて制御することが可能となると考えられる。このような制御はアナログ方式のノイズ低減手法では非常に難しい上に拡張性に乏しい。一方デジタル回路を用いた場合、測定結果をDSP(Digital Signal Processing:デジタル信号処理)回路で演算処理することで、実際に"発生しているノイズに応じて"キャンセラーを制御することが可能となる。図4.1にその全体図を示し、以下そのフローについて説明する。

図 4.1 提案手法の全体図

- 1. ノイズ検出回路によって基板ノイズ波形をサンプリングし保存する

- 2. DSPによって"発生しているノイズに応じて"に演算処理する(平均化、積分など)

- 3. DSP の出力結果に基づき、キャンセラーがキャンセル信号を生成する

- 4. キャンセル信号を基板に注入する

- 5.1~4を目的の波形が得られるまで繰り返す

本手法では実時間フィードバック系ではなく、ノイズの観測とキャンセル信号の注入をある一定の間隔で繰り返すことで、キャリブレーション可能なフィードフォワード型のキャンセラーを実現する。これにより効果的なキャンセル信号をキャンセラーが自動的に生成することが可能となり、設計者を制約する問題がなくなる。DSPはdi/dtキャンセラーのようにノイズの振幅を小さくするだけでなく、ノイズの周波数分布を変えたり、平均的なノイズ信号を除去したりとユーザーの要求によって基板ノイズの影響を低減ことが期待される。

#### 4.1.2 基板ノイズの周期性

フィードフォワード型のデジタル制御キャンセラーでは、一度波形をサンプリングしキャンセル信号を生成するため、基板ノイズが"周期的"であることを仮定している。ここでは基板ノイズの周期性について議論する。基板ノイズはデジタル回路の電源線と基板とのカップリングによって生じることを第1章で説明した。デジタル回路はクロックに同期して動作することが一般であるため、それによって生じるノイズもクロックに強く依存し、そのスペクトル分布はクロック周波数にほぼ集中する。また複数の回路が搭載される回路が場合においても、ノイズを支配的に発生する箇所は電流を多く消費するブロックに限定することができる。中でもクロック

バッファ、I/O、メモリは支配的なノイズ源として知られ [18][20]、特にクロックバッファは電流消費が多く、クロックに対して周期的なノイズを発生することが知られる [18][19]。さらに演算器がある命令を繰り返し行うような周期的な動作をすることも多く、このときも周期的なノイズが発生することがわかる。ロジック回路が瞬間的にパルス上に発生するノイズはデカップリング容量なので幾分抑えることが可能になるが、このような周期的な大電流によるノイズを低減することは非常に重要であると考えられている [19]。

以上のことから、本提案手法では基板ノイズが"周期性"を持つことを仮定し、周期的なノイズを低減するためのキャンセラーを実現する。このように周期的に発生する基板ノイズに対しては、ノイズに同期してフィードフォワード的にキャンセル信号を生成&注入するこで基板ノイズを低減させることが可能であると考えられ、デジタル制御のフィードフォワード型のキャンセラーが実現可能だと考えられる。

### 4.1.3 高ノイズ耐性

本研究のような基板ノイズを低減する回路は、低減回路自身が被低減対象である 基板ノイズに対して強い耐性が求められる。もし基板ノイズに対するノイズ耐性が 弱いと位相の変動が生じ、ノイズを増やすことにもならない。アナログ回路に比べ てはるかにノイズ耐性の強いデジタル制御によってキャンセラーを構築することで、 キャンセラーの誤動作を防ぐことができる。

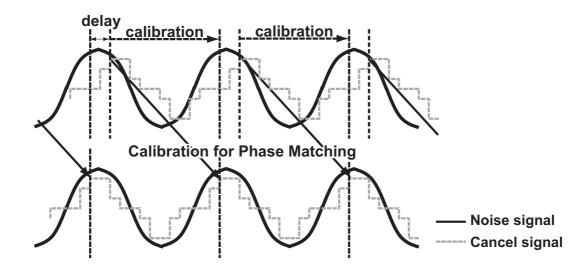

#### 4.1.4 高利得キャンセルシステム

アナログ方式の能動的基板ノイズ低減手法では、入力信号が非常に小さいために、大面積や狭周波数帯域といった犠牲を払う必要があった。しかしデジタル制御による基板ノイズ低減手法では、ノイズキャンセルのために十分なバッファが必要となる場合においても、ノイズ波形が"周期的"であることを仮定しているため、位相を1周期遅らせることでキャンセル信号とノイズ波形の位相を合わせることができる。図4.2に示すように、生成した信号はクロックに同期して発生する波形に対して幾分遅れることが予想されるが、この手法では周期的なノイズを仮定しているため、タイミングを遅らせて位相を合わせることが容易に可能となる。またデジタル制御を用いているため、その制御も比較的容易である。また入力信号もデジタル信号を用いることで、アナログ方式における入力信号が小さいことによって生じる諸問題が解消される。

### 4.2 本研究の目的

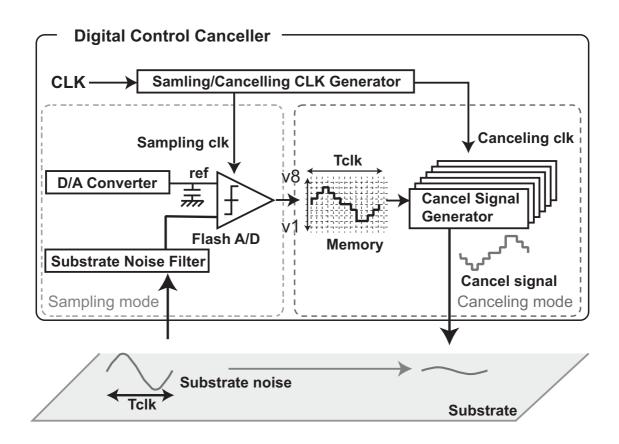

本研究ではDSP以外の波形サンプリング回路とデジタル制御によるキャンセラー回路を実現することを目的とし、デジタル制御でノイズが低減できることを検討する。つまりノイズ波形のサンプリングを行い、演算処理を全く行わず得られたノ

図 4.2 位相キャリブレーションによる本手法の利点

イズの波形データから逆位相のキャンセル信号を生成・注入することで、基板ノイズが低減できることを検討する。ノイズ波形をキャンセラーにフィードバックし続けることで、キャンセル信号の位相と振幅の両方を最適に制御することが可能となり、基板電圧を求められる電圧内に制御する"基板ノイズ・イコライザ(equalizer)"としての動作が期待される。図 4.5 に提案手法のブロック図を示す。主な構成要素は、サンプリング回路、サンプリング(キャンセリング)クロックジェネレータ、メモリ、キャンセル信号ジェネレータである。ここで基板ノイズはデジタル回路のクロックと同周期で発生するものと仮定する。今回は1周期の基板ノイズに対して3ビット電圧解像度と4ビットの時間解像度を目標とし、デコーダ回路を含んだSRAMを用いた場合の面積と比較してフリップフロップを用いた場合の方が面積が十分小さくなることから、今回はフリップフロップをメモリに用いた。より高い解像度が必要な場合にはSRAMを用いることも可能である。デジタル回路にもちられるクロックを参照クロックとして、サンプリング(キャンセリング)クロックジェネレータが波形をサンプルするタイミングと、キャンセル信号を基板に注入するタイミングを制御する。

以下では、サンプリング回路の構成とキャンセラー回路の構成に分けて説明を行い、それぞれシミュレーション結果を示す。

## 4.3 サンプリング回路の構成

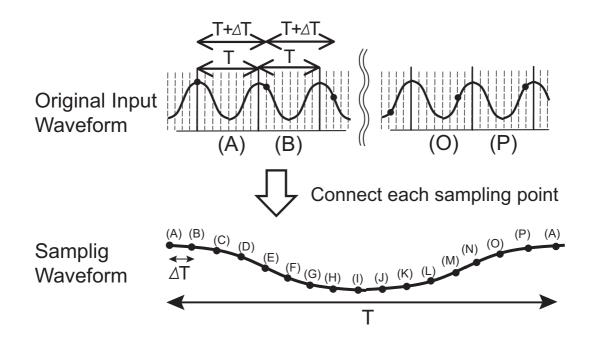

#### 4.3.1 サンプリングオシロスコープの特徴

今回、基板ノイズがクロックに対して周期的な波形をとることを前提としている。 オンチップサンプリング・オシロスコープを用いた測定はこのような周期性のある 高速な波形を取得するための手法であり、オンチップノイズ測定手法として多くの

図 4.3 デジタル制御キャンセラーの概念図

図 4.4 サンプリングオシロスコープの概念図

ものが提案されている [6][16][17]。オンチップでノイズ測定を行う背景としては、高速な信号がパッケージの寄生成分の影響からチップ外に出てこない問題が生じるため、チップ内でデジタル変換するという利点が考えられる。ノイズのように高速なアナログ信号は実時間でサンプリングすることが不可能であるので、サンプリングオシロスコープでは周期的な波形を数周期にわけてサンプリングすることで高速波形取得を可能とする。図 4.4 にその概念図を示す。周期 T の入力波形に対してサンプリング周期  $T+\Delta T$  で 1 回のサンプリングを行い、時間解像度を 4 ビットとした場合は計 16 回のサンプリングを行う。サンプリングした各点の値を 1 周期分の波形に重ね合わせると、下の波形のように 1 周期分の波形をサンプリングすることが出来る。

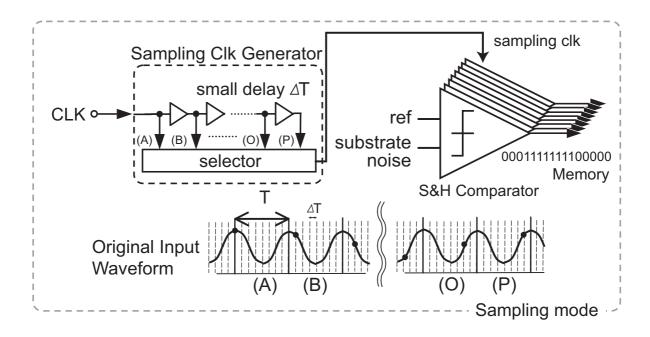

### 4.3.2 サンプリング回路に求められる仕様と構成

基板ノイズをサンプリングする時の回路構成を図 4.5 に載せる。構成はコンパレータとサンプリングクロックジェネレータとメモリと基板ノイズフィルタ (低域通過フィルタ)と参照電圧生成回路である。コンパレータの入力となる基板ノイズは基板ノイズフィルタに通して余分な高周波成分を除去し、コンパレータの入力に対して適切なバイアスまで昇圧する。今回の設計ではクロックに対して"周期的な"ノイズを対象とし、サンプリングクロックジェネレータがサンプリングしたいタイミング(図 4.4 の A、B・・)を選択し、先に説明した通り複数クロックの間に1回サンプリングを行う。サンプリング回路はキャンセラーを制御する上で最も重要な波形情報を取得することから、基板ノイズによるサンプリングクロックのジッタやコンパレー

図 4.5 サンプリング回路の構成

タのロジックエラーに対して考慮する必要が考えられる。特にサンプリングクロックのジッタは不可避な問題であると考えられるため、フラッシュA/Dを用いることで電圧解像度におけるジッタの影響を軽減した。また基板ノイズの影響によりコンパレータが比較結果が出力するまでに時間がかかることも考えられるため、サンプル&ホールドのコンパレータを用いて一度ホールドし、比較できる十分な時間を確保した。コンパレータの出力はセレクタ指定されたアドレスのメモリに保存する。今回の設計では1クロック分の波形をを16回に分けてサンプリングを行った。以下に、各構成要素の回路構成についての説明を行う。

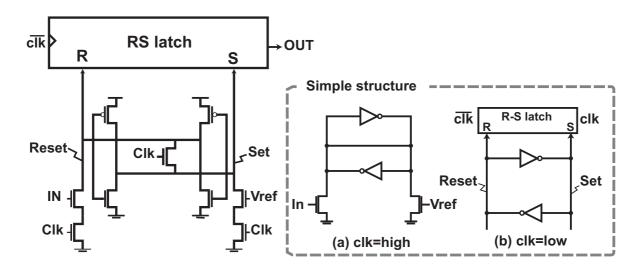

### コンパレータの構成

コンパレータの回路構成は図 4.6 のようになっており、簡単なインバータを双対接続させた SRAM のような構成をとっている。図 4.6 の右に示すようにクロックが high の場合、インバータの出力と入力をフィードバックさせ動作点で安定させる。次にクロックに low がはいると、入力に入った信号 (基板 ノイズ)と参照電圧の電圧差に応じてコンパレータが 1 ビットの出力を出し、その結果が直ちに SR ラッチによってラッチされる。このコンパレータは従来のコンパレータと比べてより高速であることが知られ [21]、今回は回路構成も小さいこの回路を採用した。コンパレータの面積はメモリと比べても十分に小さく、さらにサンプリング・オシロスコープはジッタの影響も大きいので、本回路ではこのコンパレータを用いてフラッシュ型A/Dコンバータを構築した。コンパレータの入力は基板をカップリング容量を通してバイアス回路へと接続することで、基板ノイズをグランドレベルからコンパレータの動作点まで昇圧している。バイアス回路は抵抗ラダーによって構成した。

図 4.6 コンパレータ回路の構成 [21]

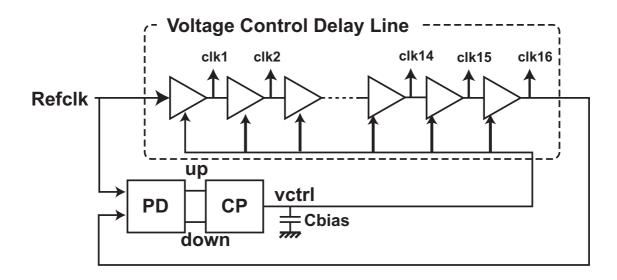

## サンプリング (キャンセル) クロックジェネレータの構成

先に説明したとおり、周期 T の波形を時間解像度 4 ビットでサンプリングするためにはサンプリング周期 T+T/16でサンプリングする必要がある。そのため、クロック波形の位相が 360/16=22 度ずつ異なるクロックを生成するための位相補間が必要である。このように位相が異なるクロックは DLL(Delay Locked Loop:遅延同期ループ) を用いて生成することが可能である [22][23][24]。図 4.7 に DLL の概念図を示す。DLL は電圧制御遅延回路 (VCDL: Voltage Control Delay Line)、位相検出回路 (PD: Phase Detector) とチャージポンプ回路 (CP: Charge Pump) によって構成される。電圧制御遅延回路はバイアス  $V_{ctrl}$  によって遅延時間  $T_{buf}$  が制御可能なバッファをカスケード接続したものである。 $V_{ctrl}$  が変化することで、 $V_{buf}$  が長くなったり短くなったり変化する。

いま参照クロック  $(CLK_{ref})$  として周期  $T_{ref}$  のクロック信号が DLL に入力されるとする。ここで電圧制御遅延回路の遅延時間  $T_{vcdl}$  が、

$$T_{ref}/2 \le T_{vcdl} \le 2T_{ref} \tag{4.1}$$

の範囲内でのみ制御可能な遅延回路であった場合、電圧制御遅延回路の出力のクロック信号 (CLK16) と参照クロック  $CLK_{ref}$  の立ち上がりの位相差は電圧制御遅延回路の出力のクロック信号と参照クロックの周波数差を表している。位相検出回路とチャージポンプによってこの位相差が0 になるまで  $V_{ctrl}$  の電圧を変動させ、最終的に  $T_{vcdl} = T_{ref}$  となるまでフィードバックを繰り返す。 $T_{ref} = T_{clk16}$  になり位相差がゼロになった時を"ロック状態"と呼ぶ。この時電圧制御遅延回路がN 個のバッファによって構成されていた場合、各バッファ[i] の出力するクロックは次の式で表される位相差を持っている。

$$V[t_{ref}] - V[t] = (T_{ref}/N) \times i \tag{4.2}$$

図 4.7 DLL 回路の構成

つまり N 個のバッファを接続した場合、参照クロックから解像度 N の位相差を持つクロックを生成することができる。今回は 16 個のバッファを接続することで図 4.4 に示す (A) から (P) の各ポイントのサンプリングクロックを生成することができる。サンプリングクロックはそれぞれセレクタによって選択され、先ほど説明したフラッシュA/Dのサンプリングトリガとして用いる。参照クロックにデジタル回路のクロックをクロック信号を入力することで、デジタル回路のクロックに対して位相補間したクロックを生成することができる。

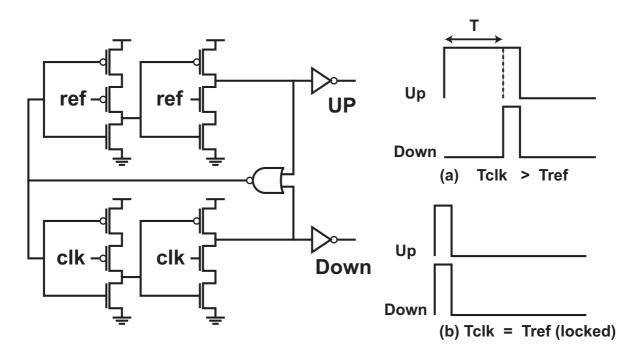

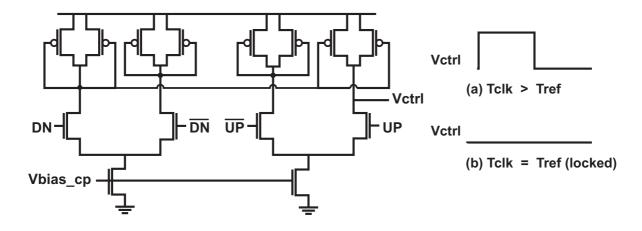

続いて位相検出回路とチャージポンプの回路構成について説明する。位相検出回 路では参照クロック  $CLK_{ref}$  と電圧制御遅延回路の出力クロック  $(CLK_{16})$  の位相差に 比例した時間幅のパルスを生成する回路であり、チャージポンプ回路はそのパルス 幅に応じて図 4.7 の  $C_{bias}$  に電荷を蓄積する。位相検出回路とチャージポンプ回路の 回路構成を図4.8と図.4.9に載せる。各クロック信号は立ち上がりによってそれぞ れ Up 信号、Down 信号をハイにする。この両信号がともにハイになったら、ともに ロー信号になるようにフィードバックをかける。こうすることで、図 4.8 に示すよ うに (a) 参照クロック  $CLK_{ref}$  と電圧制御遅延回路の出力クロック (CLK16) の間に位 相差が存在する場合、Up信号はDown信号に比べて位相差だけ長い時間幅のパルス を生成する。もし(b) ロック状態 ( $T_{vcdl} = T_{ref}$ ) の場合、Up 信号と Down 信号は同じ幅 の時間幅のパルスを生成する。図 4.9 に示すチャージポンプ回路は差動増幅回路と 同じ構成をしており、(a)参照クロック  $CLK_{REF}$  と電圧制御遅延回路の出力クロック (CLK16)の間に位相差が存在する場合、Up信号はDown信号に比べて位相差分パル ス幅が長いので、そのパルス幅の時間の間差動信号が入力されることになる。これ により、Up 信号が長い場合 Vctrl には電荷が蓄電され、Down 信号が長い場合 Vctrl から電荷が放電される。もし(b) ロック状態 ( $T_{vcdl} = T_{ref}$ ) の場合、Up 信号と Down 信 号は同相信号であるから Vctrl は蓄電も放電も行わない。電圧制御遅延回路の遅延

が位相差が小さくなるように変化し、最終的にロック状態にはいる。

図 4.8 位相検出回路

図 4.9 チャージポンプ回路

### 4.3.3 サンプリング回路のシミュレーション

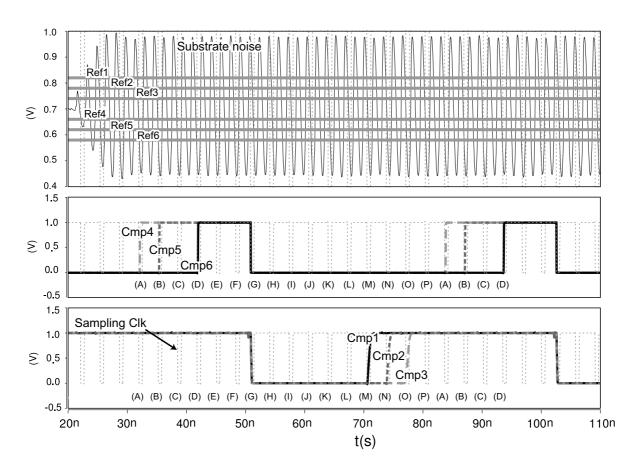

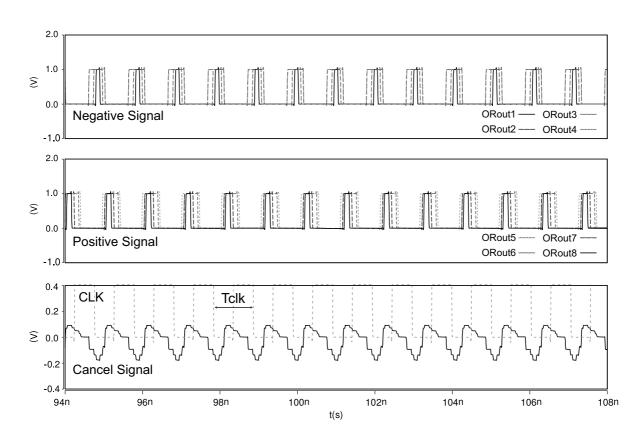

ここではサンプリング回路のシミュレーションを行う。シミュレーションには90nm-CMOS プロセスのモデルを利用した。シミュレーションはフラッシュA/D とサンプリングクロックジェネレータによって構成される。電圧解像度は6とし、バイアス電圧0.7Vを中心に電圧解像度0.4Vずつ離れている。動作周波数1GHzを目標とし、時間解像度 $\Delta T$ は1/16[ns]=62.5[ps]とする。シミュレーション結果を図4.10に示す。

サンプリングクロックのネガティブトリガ (オンからオフ) によって、コンパレータの比較結果がラッチされている様子を示している。基板ノイズが参照電圧より電圧が高い場合 0 が保存され、低い場合 1 が保存されている様子が分かる。基板ノイズが基準電圧より電圧が高い (Ref1、Ref2、Ref3) は負のキャンセル信号が必要なことを記憶し、基準電圧より電圧が低い部分 (Ref4、Ref5、Ref6) は正のキャンセル信号が必要なことを記憶する。これらの結果から基板ノイズの波形取得ができることが確認できた。

図 4.10 サンプリング回路のシミュレーション結果

## 4.4 キャンセラー回路の構成

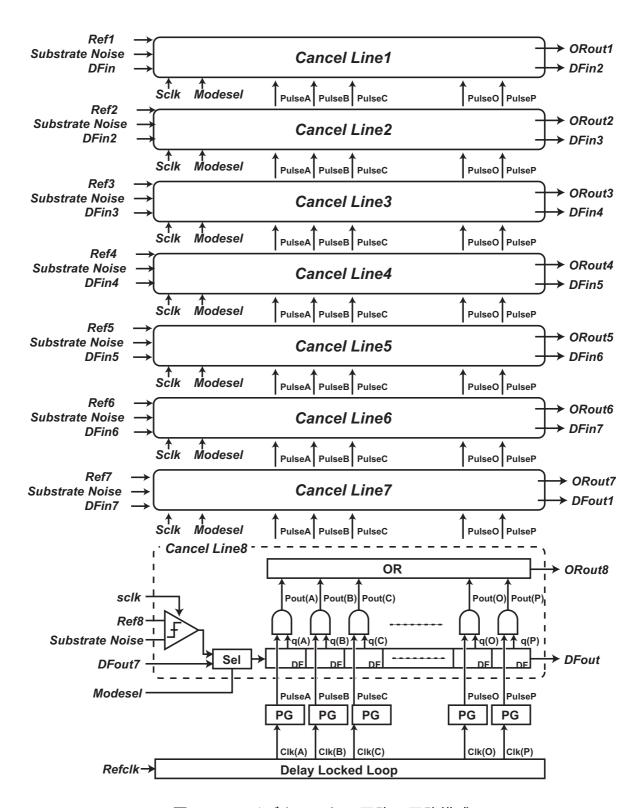

続いて先ほど説明したサンプリング回路からキャンセル信号を生成するキャンセラー回路の構成について説明を行う。前章で記憶したメモリの波形から逆位相の信号を生成するためには、クロック信号よりも高速な D/A 変換が必要となる。今回のようにクロックよりも高速な D/A 変換を行うためには、電圧解像度と時間解像度分のパラレル処理が必要となる。一方で第2章に説明した複数 di/dt 検出回路を用いた基板 ノイズキャンセラーに分かるように、キャンセル信号はキャンセラーをパラレルに配置ことによって注入位置で重ね合わせることができる。そのため、メモリに保存した結果から時間分割でキャンセル信号を発生させ、注入位置で重ね合わせることで、高速な D/A 変換が期待できる。以下、メモリに保存したノイズ波形データからキャンセル信号を発生するためのフローを説明する。

#### 4.4.1 パルス制御回路

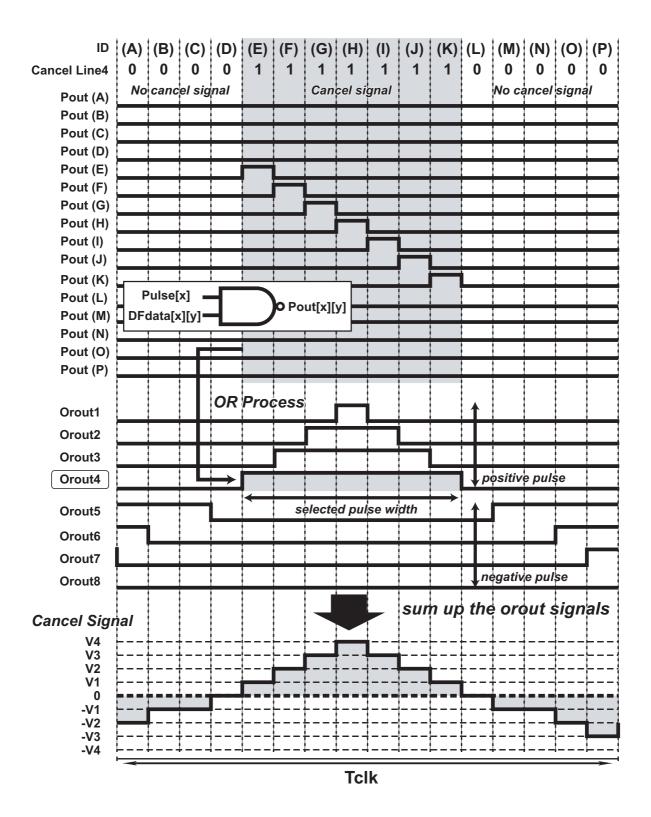

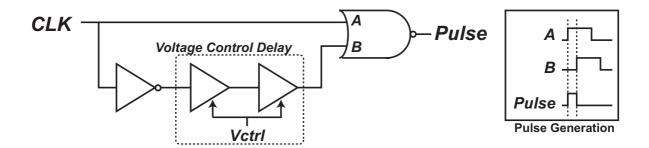

'波形をサンプリングした結果から、メモリにはそれぞれのタイミング (A,B⋯P) に おいてノイズキャンセル信号が必要か不要であるかを保存していることになる。キャ ンセル信号を生成する回路構成図を図 4.11 に示し、キャンセル信号の生成フロー を図 4.12 に示す。図 4.11 に示すように、パルス制御回路ではサンプリングクロッ クジェネレータで用いた DLL をキャンセルクロックジェネレータとして利用する。 CLK(A),CLK(B)···はそれぞれデジタル回路のクロック CLK<sub>digital</sub> と同周波数で異なる 位相を持つクロックである。これらのクロックから図 4.13 に示すパルスジェネレー タを用いてパルス Pulse[x]を発生させる。ここでパルス幅を決める遅延回路に電圧 制御遅延回路のバッファを接続することで、パルス Pulse[x] の時間幅を約 $T_{CLK}/16$  に 相当する時間幅に設定することが出来る。パルス発生回路に電圧制御遅延回路の バッファを用いることで、DLL がロックする範囲であれば、デジタル回路の動作周 波数に追従して動作することができる。Pulse[x] とそれぞれの電圧解像度 [y] におけ る時間位相 [x] に対応する波形データ DFdata[x][y] との論理積 Pout[x][y] をとると、 キャンセル信号が必要なタイミング(基板ノイズの絶対値が参照電圧よりも大きい) ではパルスが生成され (Pout[x][y]=1)、キャンセル信号が不要なタイミング (基板ノ イズの絶対値が参照電圧よりも小さい)ではパルスが生成されない(Pout[x][y]=0)。 この論理積の出力 Pout(A)、Pout(B)···Pout(P) のすべての論理和をとることで、周期  $T_{CLK}$  の間にキャンセル信号が必要な時間幅のパルス ORout[y] が生成される。

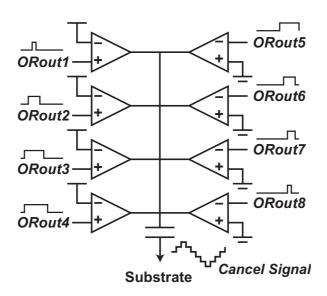

#### 4.4.2 出力段の構成

パルス生成回路で発生したパルス ORout[y] はキャンセル信号のオン・オフを切り替えるために用いる。出力段の構成を図 4.14 に示す。パルスを十分に増幅し、基板に注入する電流源のオン・オフの切り替えを行う。電圧解像度分のキャンセル信号ジェネレータを並列動作させ出力を重ねあわせることで、図 4.11 に示すメモリに保

図 4.11 ノイズキャンセル回路の回路構成

図 4.12 ノイズキャンセル信号の生成フロー

図 4.13 パルスジェネレータ回路の回路構成

存した波形 (Cancel Signal) を生成することができる。キャンセラーの出力と基板の間にはカップリング容量を間に挿入することで、グランドレベルまでシフトレベルし、仮想的に負のキャンセル信号を生成する。

#### 4.4.3 キャンセラー回路のシミュレーション

ここではキャンセラー回路のシミュレーションを行う。あらかじめメモリに保存したデータから、クロック信号に同期して周期的なキャンセル信号を生成できることを確認する。シミュレーションには 90nm プロセスのモデルを利用した。ここで出力段の増幅器を構成する 80 NMOS トランジスタ幅を 80 とし、ゲート長は最小ゲート長 1000 mm とした。シミュレーション結果を図 4.15 に示す。まずメモリから発生したパルスが論理和をとることで、メモリに保存されたパルス幅の信号 1000 の配性[100 の 100 の

図 4.14 出力段の構成

図 4.15 キャンセル回路のシミュレーション結果

## 第5章

## デジタル方式の雑音低減回路の設計と評価

### 5.1 シミュレーションによる検討

ここでは HSPICE シミュレーションを用いて、提案するデジタル方式による能動的基板 ノイズ低減手法について検討する。シミュレーションには 90nmCMOS プロセスのモデルを用いた。

## 5.1.1 シミュレーション条件

ノイズ源は 2.5.1 で説明したものと同じ回路を用いる。図 2.9 に示す D フリップフロップにインバータチェーンを接続した仮想的なデジタル回路を設計する。この回路はクロック毎に等電流を消費するため、クロックに対して周期的なノイズ波形を生成することが予想され、 $0.35\mu m$  プロセスを用いた実測結果ではこのことが確認された (図 2.13)。プローブの設計も同様に 2.5.2 で説明した前段に差動増幅器、後段にPMOS で構成されたソース接地増幅回路を用いた。プローブのゲインは HSPICE シミュレーションによると  $A_{probe}=6.2$  となる。

シミュレーション条件の全体図を図 5.1 に載せる。デジタル回路とアナログ回路 (ここではプローブ回路を想定) はそれぞれ別々の電源線・グランド線が用意されるのが一般であるから、シミュレーションにおいてデジタル回路の電源  $VDD_D$ ・グランド  $GND_D$ 、アナログ回路の電源  $VDD_A$ ・グランド  $GND_A$  を定義した。ここでデジタル回路のグランドとアナログ回路のグランドは基板を通して接続される。基板ノイズはデジタル回路 (ノイズ源) のグランド線とのカップリングにより生じるので、グランド線の寄生抵抗成分とパッケージの寄生インダクタンス成分をグランド線のインピーダンスモデルとして定義した。基板は第3章で説明した通り、数 GHz 以下の帯域では抵抗網としてモデル化できることが知られる。今回はデジタル回路の動作周波数を 1GHz に設定し、基板ノイズの中心スペクトルも 1GHz を想定しているため、シミュレーションでは基板抵抗を各ノードを抵抗で接続した基板モデルを用いた。ノード間を抵抗で接続した基板モデルはシミュレーション時間が短く、精度も高いことで知られている [25]。 1 周期のサンプリング解像度は 4 ビットを想定しているため、サンプリング/キャンセル信号の時間解像度  $\Delta T$  は 1/16[ns] = 62.5[ps] となる。

図 5.1 シミュレーション条件

### 5.1.2 シミュレーション結果

ここではキャンセラーを ON/OFF したときの基板 ノイズの変化についてシミュレーションを行う。

本提案手法ではノイズ波形をサンプリングし、そのデータを基にキャンセル信号を生成しノイズと同期して注入する。しかしこのときキャンセル信号には位相情報が存在しないので、キャンセル信号と基板ノイズの信号が最も打ち消しあうように位相を合わせる必要である。この位相のキャリブレーションを位相キャリブレーション操作と定義する。また本手法では、従来手法のフィードバック型のキャンセラーとは異なりフィードフォワード型のキャンセラーであるため、基板ノイズが最も最小になるようにキャンセル信号の振幅を制御する必要がある。この操作を利得キャリブレーションとする。

以下、2つのキャリブレーションによる基板ノイズを応答を観測し、最も効果的な 位相とキャンセル信号の振幅について検討する。

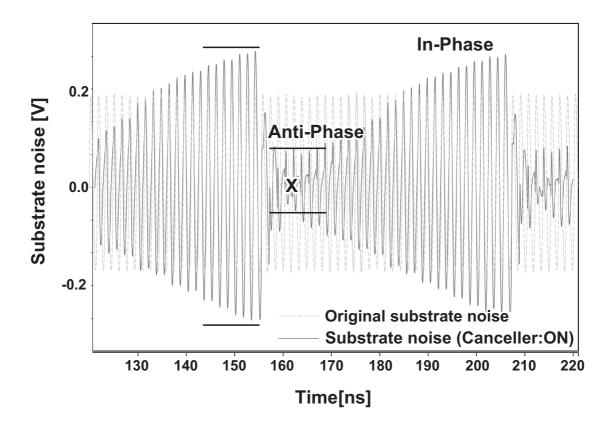

### 位相キャリブレーション

サンプリングオシロスコープで取得した波形からノイズを逆位相のキャンセル信号を生成した後、基板ノイズと同期を合わせて基板に注入する必要がある。ここでは注入するキャンセル信号の位相を各周期ごとにずらしながら、基板ノイズ低減効果をまず検討する。図 5.2 にシミュレーション結果を載せる。図から分かるように、基板ノイズの振幅が周期的に変動している様子が分かる。この振幅の変化はノイズの位相とキャンセル信号の位相差がどれだけ-180度に近いかに依存する。すなわち、基板ノイズとキャンセル信号の位相差がほぼ等しい場合互いに重なり合いノイズの振幅が増大し、逆に-180度に近いと互いに打ち消し合い、ノイズの振幅が減少する。ここではノイズの振幅が最も減少するタイミングでキャンセル信号を注入することが最適な位相だと考え、図 5.2 では点 X がもっともキャンセル信号と基板ノイズが逆位相に近く、もっとも低減効果が大きいと言える。このときのキャンセル信号の位相は基板ノイズの最も小さくなるキャンセル信号をキャンセラーが生成しているものと考えることができくため、このときメモリに保存されているデータを位相が最適な波形として適用する。

### 利得キャリブレーション

本手法では従来のフィードバック手法と異なり、フィードフォワード型の能動的基板ノイズ低減手法を提案してる。そのため、どの程度のキャンセル信号の振幅が適切であるかは、位相と同様に基板ノイズの振幅を見ながら制御しなければならない。本提案手法ではノイズの波形情報のみをサンプルし、また基板ノイズは減衰しながら伝搬するため、キャンセル信号の振幅を制御する必要がある。第2章で説明した図 2.14 に示すようにキャンセラーの利得を上げていくとノイズの振幅が変動し、

振幅の最小値が存在する。キャンセラーの利得は電源電圧を制御することで調整できる。基板ノイズの最も小さくなるキャンセル信号をキャンセル信号ジェネレータが生成しているものと考えることができくため、このときの電源電圧を最適なキャンセラーの利得として適用する。

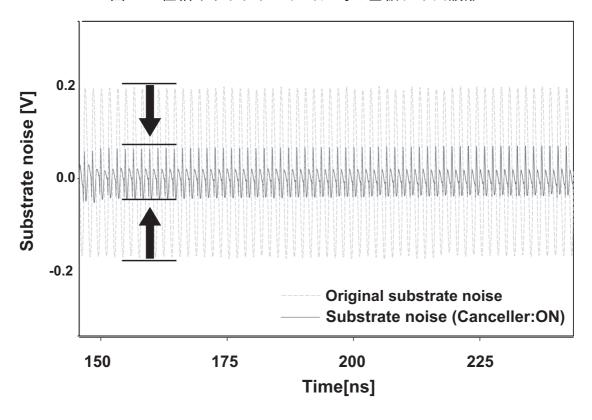

### 基板ノイズ低減効果

最後に最適な位相と利得でノイズキャンセラーをON・OFF した際の基板ノイズの変化を観測する。図 5.3 に基板ノイズの変化を観測する。基板ノイズが安定して低減できている様子が観測できる。

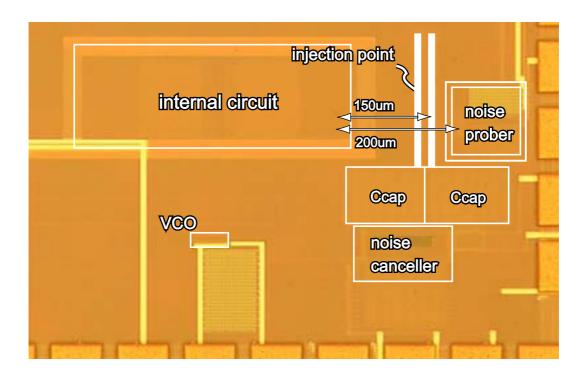

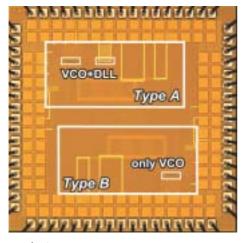

### 5.2 デジタル方式基板ノイズ低減回路の設計

以上に説明したデジタル方式基板ノイズ低減回路の設計を行った。設計は90nm CMOS プロセス (1P6M VDD=1.0V)を用いて行った。設計したチップの写真とフロアプランを図5.4 に示す。ノイズ源であるデジタル回路を左に配置し (internal circuit)、GND とのコンタクトからノイズが破門状に伝搬する。右端にあるプローブ (noise prober)を用いて基板ノイズを増幅し、オシロスコープを駆動できるまで十分に増幅する。今回はHP54750 オシロスコープをSMA ケーブルを通して測定するため、この出力インピーダンスを $50\Omega$  に設定し、反射を極力低減する。ノイズをサンプリングする位置とキャンセル信号を注入する位置はノイズ源とプローブの間に配置し (ノイズ源から $150\mu m$  離れた距離)、P+コンタクトでP基板に接続する。提案するノイズキャンセラー (noise canceller) は中央に位置し、ノイズ源を駆動するクロックを参照クロックとして入力することで、ノイズ源の動作周波数に依存したサンプリングクロックとキャンセリングクロックを生成する。全体のチップ面積は $900\mu m \times 600\mu m$  であり、ノイズキャンセラーの面積は $300\mu m \times 60\mu m$  を占める。

## 5.3 測定環境

測定環境を図 5.5 に示す。チップは第 2 章と同様にパッケージ化されたチップを接地された銅板上にマウントする。各回路 (VCO (Voltage Control Oscillator:電圧制御発振器)、ノイズ源、キャンセラー、プローブ) の電源は銅板上に彫られた"シマ"からリード線を通して電源から供給される。高速な信号 (CLK/8、CLK256、基板ノイズ) は SMA ケーブルを通して、それぞれオシロスコープに接続され、CLK256 をトリガとして用いる。サンプリング/キャンセリングデータはオフチップである National Instruments の DAQ カードを I/O として用いて PC 制御できるように測定環境を構築した。

図 5.2 位相キャリブレーション時の基板ノイズ波形

図 5.3 最小化された基板ノイズ波形

図 5.4 デジタル制御キャンセラーのチップ写真 (90nm CMOS プロセス)

図 5.5 測定環境 (デジタル制御キャンセラー)

## 5.4 実験結果と今後の課題

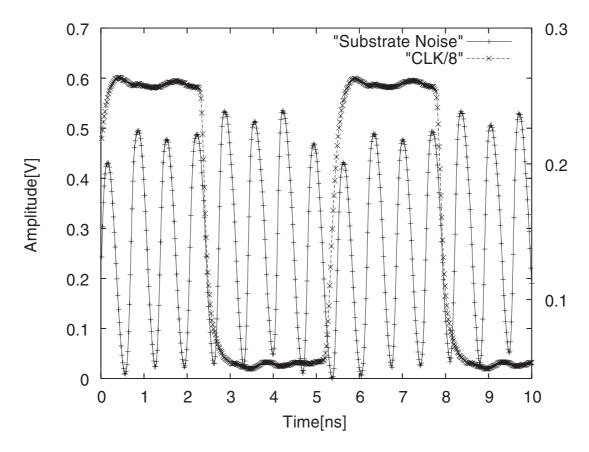

測定結果を図 5.6 に示す。今回の設計ではデジタル回路によって生成したノイズを測定することができた。8 分周したクロックの1 周期内に8 つの山が存在するため、クロックと同周期のノイズが発生していることが確認できる。しかしながら、実験結果ではキャンセラーによって基板ノイズの変動が確認できなかった。この原因として I/O の不良、DLL の擬似ロック状態、キャンセラーのゲインが小さいなどが考えられる。これらの検討項目は今後の課題とする。

図 5.6 基板ノイズ波形

## 第6章

# 結論

本研究ではシステムLSIにおける能動的基板雑音低減手法に関する検討・評価を行った。フィードフォワード型の能動的基板ノイズ低減手法は従来のフィードバック型の能動的基板ノイズ低減手法に比べて、より広帯域で動作し、より安定して動作するという利点がある。本研究ではフィードフォワード型の能動的基板ノイズ低減手法として、アナログ方式とデジタル方式の両手法について検討した。

基板ノイズはデジタル回路のグラウンド線とのカップリングにより支配的に生じ、寄生インダクタンス成分がグランド線のインピーダンスにおいて支配的な場合、基板ノイズはデジタル回路に流れる電流の時間変化 di/dt に比例する。アナログ方式のフィードフォワード型能動的ノイズ低減手法として、di/dt 検出回路を用いた基板ノイズ低減手法の解析・改善を行い、寄生インダクタンスによって生じるノイズの低減を実現した。

- di/dt 検出回路を用いた能動的基板ノイズ低減手法の解析を行い、 複数の di/dt キャンセラーを搭載することで広帯域・高利得基板ノイズキャンセラーを実現 した。

- 動作周波数300MHzにおいて62%(8.4dB)の基板ノイズ低減を実現した。

- 100MHz から 700MHz の動作周波数において 10-62%の基板ノイズ低減を実現した。

さらにフィードフォワード型の能動的基板ノイズ低減手法において以下の点について解析した。

- ◆ よりノイズ源から離れた被対象回路側でキャンセル信号を注入することで、より小さな利得(低消費電力)で高いノイズ低減率を実現できる。

- 複数のキャンセラーを搭載した場合、より大きなカップリング容量が必要と なる。

- 複数のキャンセラーは出力抵抗が基板抵抗に比べて十分に大きい場合、利得はキャンセラーの数に比例するが、出力抵抗が基板抵抗と同等まで低くなったときキャンセラーの数に比例しない。

第6章 結論 56

基板ノイズはクロックバッファ等の周期的な動作を繰り返すブロックから支配的に発生し、デジタル回路のクロックに対して周期的な波形を示す。

デジタル制御によるフィードフォワード型能動的基板ノイズ低減手法として、基板ノイズ波形をサンプリングし、キャンセル信号をクロックに同期させながら注入する手法を提案した。デジタル制御による基板ノイズ低減には次のような利点がある。

- 実際に"発生しているノイズに応じて"自由にキャンセラーの動作を制御することができる。

- 対象となる基板ノイズに対するノイズ耐性が強い。

- 周期性を仮定しているため、キャンセル信号の位相キャリブレーションが非常 に容易で、高利得キャンセルシステムを実現できる。

本研究ではキャンセル信号として基板ノイズの波形と逆位相の信号をパルス状に 基板に注入する回路について提案、検討を行った。

- 基板ノイズをサンプリングし、サンプリングした波形から逆位相のキャンセル信号を生成することをシミュレーション上で示した。

- 90nm プロセスを用いた設計を行い、動作周波数 1GHz において基板ノイズを 低減できることをシミュレーション上で示した。

両者の特徴を表 6.1 にまとめる。

Conv. Techniques di/dt Canceller Digital Control Canceller Feedback Feedforward Feedforward Type Unstable Stable Stability Stable Narrow Broad CLK-dependent Bandwidth Random Operation **Target Operation Random Operation** Repeat Operation Gain Noise-dependent Not High High Gain Calibration No Need Gain Phase and Gain Controllability Little Little Good Extensibility Little Little Good Noise Tolerance High Tolerance Average Average Area Small Middle Large

表 6.1 提案手法の比較

今後の検討課題は、測定によりデジタル制御による基板雑音の能動的低減手法の優位性を示すことである。また、より拡張性の高い基板ノイズ低減システムを構築することを目標とする。

# 参考文献

- [1] M. Badarougle, P. Wambacq, G. Vam del Plass, S. Donnay, G. G. E. Gielen and H. J. De Man, "Evolution of Substrate Noise Generation Mechanisms," *IEEE Transactions on Circuits and Systems*, Vol.53, No.2, pp.296-305, Feb. 2006,

- [2] Marc van Heijningen, M. Badaroglu, S. Donnay, G. G. E. Gielen and H. J. De Man, "Substrate Noise Generation in Complex Digital System; Efficient Modeling and Simulation Methodology and Experimental Verification," *IEEE Journal of Solid-State Circuits*, Vol.37, No.8, pp.1065-1072, Aug. 2002,

- [3] M.Heiajningen et al. "Analysis and Experimental Verification of Digital Substrate Noise Genaration for Epi-Type Substrates," *IEEE Journal of Solid-State Circuits*, 2000.

- [4] T. Rahal-Arabi, G. Taylor, M. Ma and C. Webb, "Deisng & Validation of the *Pentium<sup>R</sup> III and Pentium<sup>R</sup>* 4 Processors Power Delivery," in Dig. of Tech. Papers of *IEEE Symposium on VLSI Circuits (VLSI Symp.)*, pp. 220-223, Jun. 2002,

- [5] D. Kosaka, M. Nagata, Y. Hiraoka, I. Imanishi, M. Maeda, Y. Murasaka and A. Iwata, "Isolation Strategy against Substrate Coupling in CMOS Mixed-Signal/RF Circuits," in Dig. of Tech. Papers of *Symposium on VLSI Circuits (VLSI Symp.)*, pp.276-229, jun. 2005.

- [6] M. Takamiya, M. Mizuno and K. Nakamura, "An on-chip 100GHz-sampling 8-channel sampling oscilloscope with embedded sampling clock generator," in Dig. of Tech. Papers of *IEEE International Solid-State Circuits Conference (ISSCC)*, pp.182-183, Feb. 2002,

- [7] A. Muhtaroglu, G. Taylor and T. Rahal-Arabi, "On-Die Droop Detector for Analog Sensing of Power Supply Noise," *IEEE Journal of Solid-State Circuits*, Vol.39, No.4, pp.651-660, Apl. 2004,

- [8] E. Alon, V. Stojanovic and M. A. Horowitz, "Circuits and Techniques for High-Resolution Measurement of On-chip Power Supply Noise," *IEEE Journal of Solid-State Circuits*, Vol.40, No.4, pp.820-828, Apl. 2005,

- [9] K. M-Fukuda, S. Maeda, T. Tsukada and T. Matsuura, "Substrate Noise Reduction using Active Guard Band Filters in Mixed-Signal Integrated Circuits," *IEEE Transactions on Fundamentals*, pp.313-320, Feb. 1997.

参考文献 58

[10] T. Tsukada, Y. Hashimoto, K. Sakata, H. Okada and K.Ishibashi, "An On-Chip Active Decoupling Circuit to Suppress Crosstalk in Deep-Submicron CMOS Mixed-Signal SOCs," *IEEE Journal of Solid-State Circuits*, Vol.40, No.1, Jan. 2005.

- [11] Y. Komatsu, K. Ishibashi1, M. Yamamoto1, T. Tsukada1, K. Shimazaki, M. Fukazawa and M. Nagata, "Substrate-Noise and Random-Fluctuations Reduction with Self-Adjusted Forward Body Bias," in Proc. of *IEEE Custom Integrated Circuits Conference*, 2005.

- [12] T. Nakura, M. Ikeda and K. Aasda, "Feedforward Active Substrate Noise Cancelling Technique using Power Supply di/dt Detector," in Dig. of Tech. Papers of *IEEE Symposium On VLSI Circuits (VLSI Symp.)* pp.284-287, June 2004.

- [13] T. Nakura, M. Ikeda and K. Asada, "Power Supply di/dt Measurement using On-chip di/dt Detector Circuit," in Dig. of Tech. Papers of *IEEE Symposium on VLSI Circuits* (*VLSI Symp.*), pp.106-109, June 2004.

- [14] 木村智寿, 奥村万規子, "基板抵抗網モデルの抽出,"電子情報通信学会信学技報, VLD98-83, pp.81.87, 1998 年 10 月.

- [15] M. Nagata, Y. Murasaka, Y. Nishimori and T. Morie "Substrate Noise Analysis with Compact Digital Noise Injection and Substrate Models, "in Proc. of *IEEE Asia and South Pacific Design Automation Conference (ASP-DAC)*, pp.71-76, Jan 2002.

- [16] Y. Zheng and K. L.Shepard, "On-Chip Oscilloscopes for Noninvasive Time-Domain Measurement of Waveforms in Digital Integrated Circuits," *IEEE Transactions on Very Large Scale Integraton (VLSI) Systems*, Vol.11, No.3, pp.336-344, Jun. 2006,

- [17] W. Xu and E. G. Friedman, "On-Chip Test Circuit for Measuring Substrate and Line-to-Line Coupling Noise," *IEEE Journal of Solid-State Circuits*, Vol.41, No.2, pp.474-482, Feb. 2006,

- [18] M. Badaroglu, G.V.del Plas, P.Wambacq, S.Donnay, G.E.Giellen and H.G.De Man, "SWAN: High-Level Simulation Methodology for Digital Substrate Noise Generation," *IEEE Transactions on Very Large Scale Integraton (VLSI) Systems*, Vol.14, No.1, pp.23-33, Jan. 2006,

- [19] K. M.-Fuluda and T. Tsukada, "On-Chip Active Guard Band Filters to Suppress Substrate-Coupling Noise in Analog and Digital Mixed-Signal Integrated Circuits," in Dig. of Tech. Papers of *IEEE Sympousium on VLSI Circuits (VLSI Symp.)*, pp.57-60, Jan. 1999,

参考文献 59

[20] M. Badaroglu, S. Donnay, H. J. De Man, Y. A. Zinzius, G. G. E. Gielen and W. Sansen, "Modeling and Experimental Verification of Substrate Noise Generation in a 220-Kgates WLAN System-on-Chip With Multiple Supllies," *IEEE Journal of Solid-State Circuits*, Vol.38, No.7, pp.1250-1260, Jul. 2003,

- [21] M. Takamiya and M. Mizuno, "A Sampling Oscilloscope Macro toward Feedback Physical Design Methodology," in Dig. of Tech. Papers of *IEEE Sympousium on VLSI Circuits (VLSI Symp.)*, pp.240-243, Jun. 2004,

- [22] C.-K. K. Yang and M. A. Horowitz, "A 0.8-μm CMOS 2.5Gb/s Oversampling Reciever and Transmitter for Serial Links," *IEEE Journal of Solid-State Circuits*, Vol.31, No.12, pp.2015–2023, Dec. 1996,

- [23] S. Kim, K. Lee, Y. Moon, D-K. Jeong, Y. Choi and H. K. Lim, "A 960-Mb/s/pin Interface for Skew-Tolerant Bus using Low Jitter PLL," *IEEE Journal of Solid-State Circuits*, Vol.32, No.5, pp.691–700, May. 1997,

- [24] H.-H. Chang, J.-W. Lin and C.-Y. Yang, "A Wide-Range Delay-Locked Loop With a Fixed Latency of One Clock Cycle," *IEEE Journal of Solid-State Circuits*, Vol.37, No.8, pp.1021–1027, Aug. 2002,

- [25] G. Van del Plas, C. Soens, M. Badaroglu, P. Wambacq and S. Donnay, "Modeling and experimental verification of substrate coupling and isolation techniques in mixed-signal ICs on a lightly-doped substrate," in Dig. of Tech. Papers of *IEEE Symposium On VLSI Circuits (VLSI Symp.)* pp.280-283, June 2005.

## 発表文献

## 本研究に関する発表文献

- 1. 風間大輔,名倉 徹,池田 誠,浅田 邦博"複数 di/dt 検出回路を用いた基板ノイズ 低減手法,"電子情報通信学会ソサイエティ大会, C-12-22, p.83, 2006 年 9 月

- 2. Taisuke Kazama, Toru Nakura, Makoto Ikeda and Kunihiro Asada, "Optimization of Active Substrate Noise Cancelling Technique using Power Line di/dt Detector," in *Proceedings of IEEE Asian Solid-State Circuits Conference (A-SSCC)*, sess. 8-3, pp. 239–242, Oct. 2006.

- 3. 風間大輔, 池田 誠, 浅田 邦博 "di/dt 検出回路を用いたアクティブ基板ノイズ低減手法の検討," 2006 年電子情報通信学会技術研究報告, CPM2006-130, pp.7-12, 2007 年 1 月

- 4. Taisuke Kazama, Toru Nakura, Makoto Ikeda and Kunihiro Asada, "Design of Active Substrate Noise Canceller using Power Line di/dt Detector," in *Proceedings of IEEE Asia and South Pacific Design Automation Conference (ASP-DAC)*, sess. 1D-5, pp. 100–102, Jan. 2007.

## その他の発表文献

- 1. Taisuke Kazama, Makoto Ikeda and Kunihiro Asada, "Shot Reduction Technique for Character Projection Lithography using Combined Cell Stencil," *SPIE 25th Annual BACUS Symposium on Photomask Technology 2005*, vol. 5992, Nov. 2005.

- 2. Taisuke Kazama, Makoto Ikeda and Kunihiro Asada, "LSI Design Flow for Shot Reduction of Character Projection Electron Beam Direct Writing Using Combined Cell Stencil," *IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences*, Vol. E89-A, No. 12, pp. 3546–3550, Dec. 2006.

# 付録:IRドロップ除去の検討

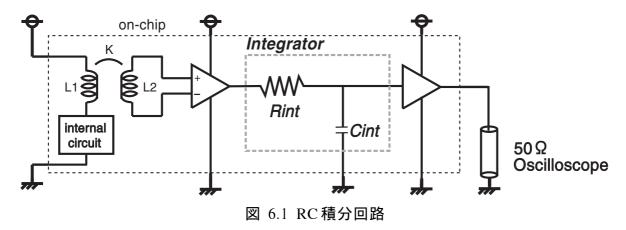

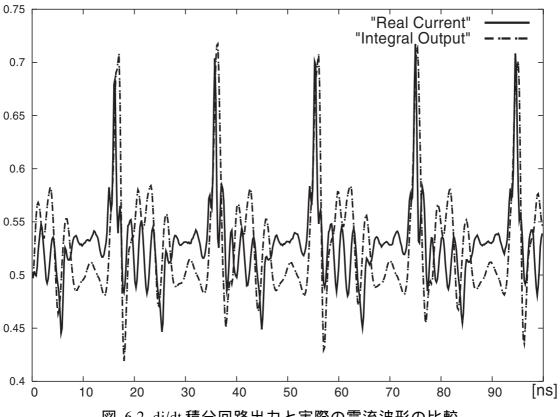

ここでは di/dt 検出器と積分器を組み合わせて IR 成分と L(di/dt) 成分の両方を低減することについて検討する。今回 RC 積分器を用いて電流に比例した信号を生成する。 RC 積分器は図 6.1 のように抵抗 R と容量 C によって構成され、その出力  $V_{integral}$  は

$$V_{integral} = \frac{1}{1 + j\omega R_{int}C_{int}}V_{in}$$

(6.1)

で表される。式から十分に積分された信号を得ようとすると電流値が非常に小さく なり、電流値を大きく確保しようとすると十分に積分された信号が得られないこと が分かる。そのため、ノイズを削減するためにはある目標周波数が存在することを 仮定し、RC時定数を設定する必要がある。今回の設計ではまず、積分することで 電流Iに比例した電圧を生成することが可能であるかを目標とし、実際に回路に流 れている電流と比較することで積分可能であるかを検証した。今回は200MHzのノ イズをターゲット周波数として、RC時定数を適当な1.0[ns]とし、Rを1K、Cを 1pF とした。比較対象となる電流については  $1\Omega$  の抵抗を電源線に接続し、その両 端の電圧を測定することで数値計算により求めることが出来る。図 6.2 にその実測 結果を示す。電流のピーク波形が積分値の出力のピーク波形と一致していることが わかる。この時デジタル回路は50MHzで動作しており、逆に200MHzで動作させた 場合には上手く積分することが出来なかった。これはピークをもつ周波数成分が回 路の動作周波数の高調波成分を含んでいることに起因し、今回では200MHzがノイ ズの主要周波数成分であることが予想される。このことから、積分回路を用いてIR 成分を除去するためには可変抵抗(または可変容量)を搭載し、設計後も動作周波数 に合わせた積分係数を調整できるようにする必要があることがわかる。

図 6.2 di/dt 積分回路出力と実際の電流波形の比較

# 付録:チップ写真一覧

本研究で設計したチップ写真を図6.3から図6.8に載せる。

図 6.3、図 6.3、図 6.3、図 6.3 および図 6.3 のチップ試作は東京大学大規模集積システム設計教育研究センター (VDEC: VLSI Design and Education Center) を通しローム (株) および凸版印刷 (株) の協力で行われたものである。

図 6.8 のチップ試作は東京大学大規模集積システム設計教育研究センターを通し株式会社半導体理工学研究センター、富士通株式会社、松下電器産業株式会社、NECエレクトロニクス株式会社、株式会社ルネサステクノロジ、株式会社東芝の協力で行われたものである。

図 6.3 di/dt キャンセラー

設計時期 2005 年 7 月

増幅器のサイズを大きくした単一 di/dt キャンセラーを設計。 位相回 転が増大し低減効果小 (第2章3 節)。

RC 積分回路と di/dt キャンセラーを組み合わせたオンチップ電流波形測定回路の設計。実際の電流波形と比較。50MHz で電流波形の測定に成功(付録:IR 成分除去の検討)。

Rohm 0.35µm CMOS プロセス 1P3M VDD=3.3V

図 6.4 複数 di/dt キャンセラー

設計時期 2006年1月 複数 di/dt キャンセラーの設計。 300MHz で最大 62%の基板ノイズ を低減。100MHz-700MHz で 10-62%のノイズ低減を確認 (第2章 5節)。

Rohm 0.35µm CMOS プロセス 1P3M VDD=3.3V

図 6.5 di/dt キャンセラー TEG1

設計時期 2006 年 6 月 注入位置の異なる複数 di/dt キャン セラー TEG。ノイズ源から遠くな るほど低利得でノイズを低減でき ることを確認 (第 3 章 1.2 節)。 Rohm 0.35 $\mu$ m CMOS プロセス 1P3M VDD=3.3V

図 6.6 di/dt キャンセラー TEG2

設計時期 2006 年 6 月 カップリング容量の異なる複数 di/dt キャンセラー。カップリング 容量によるハイパス効果の検証。 基板抵抗の推定 (第 3 章 1.3 節)。 Rohm 0.35 μm CMOS プロセス 1P3M VDD=3.3V

図 6.7 di/dt キャンセラー TEG3

設計時期 2006 年 6 月 増幅器とインダクタサイズの異なる複数 di/dt キャンセラー。出力抵抗の低下により、より大きなインダクタで入力信号を上げることがより効果的であることを確認 (第3章1.4節)。

Rohm 0.35µm CMOS プロセス 1P3M VDD=3.3V

図 6.8 デジタル制御キャンセラー

設計時期 2006 年 7 月 デジタル制御でノイズ波形サンプ リング&キャンセル信号注入する キャンセラーを設計 (第 5 章 2 節)。 ASPLA 90nm CMOS プロセス 1P6M VDD=1.0V

# 謝辞

本研究を進めるにあたり,日頃から暖かい御指導をして頂き,また適切な御助言をして頂きました池田誠助教授、浅田邦博教授に心から感謝致します.

研究内容に対して数多くの貴重な御意見を下さいました浅田研究室 OB の名倉徹氏(日本電気(株))に深く感謝致します。

研究活動においてのみでなく、他の様々な場面においても常に議論を共にして頂き、多くの貴重なご意見を頂いた大学院生の吉田浩章氏、飯塚哲也氏、谷内出悠介氏に深く感謝致します。

日頃から研究活動を共にし,多くの助言を頂いた大学院生の James Tandon 氏、YunKyung Kim 氏、石井健氏、橋本紘和氏、門馬太平氏、Yong Song Cho 氏、Zhicheng Liang 氏、Ung-hyun Kim 氏、栗原 健一郎氏、曽我部 拓氏、山本 裕介氏、Caner Basci 氏、Pham Hai Dinh Minh 氏、Jin Myoung Kim 氏、井上 拓郎氏、猪飼 啓太氏、そして中村 大輔氏に深く感謝致します。

様々な場面において,数多くの御助言,御支援をして頂きました鄭若丹彡氏、佐々木昌浩氏(ともに東京大学大規模集積システム設計教育研究センター),技官の鈴木真一氏,秘書の横地順子氏,丸山由香子氏に深く感謝致します。

本チップ試作は東京大学大規模集積システム設計教育研究センターを通し株式会社半導体理工学研究センター、富士通株式会社、松下電器産業株式会社、NECエレクトロニクス株式会社、株式会社ルネサステクノロジ、株式会社東芝、ローム(株)および凸版印刷(株)の協力で行われ、御協力頂いたことに深く感謝致します。