# 修士論文

# 完全空乏型SOI MOSFET における シングル・イベント・トランジェントパルスの 解析

Analysis of Single Event Transient Pulses of a Fully-Depleted SOI MOSFET

2006年2月3日提出

指導教員 齋藤 宏文 教授

電子工学専攻 46379 会見真宏

# 概要

近年,宇宙放射線や中性子線が引き起こすソフトエラーの一種である,シングル・イベント・トランジェント (Single Event Transient、以下 SET) が問題視されている.SET とは,高エネルギー荷電粒子がデバイスに入射することで生じる電流(電圧)パルスである.論理回路中を伝播して誤動作を引き起こすため,その対策が急務となっている.一方,SOI デバイスは,埋め込み酸化膜が存在し、イオン化放射の影響を受ける体積が少ないため、ソフトエラー対策に有効なデバイスとして知られている。しかし、その SET 特性は未だ明らかにされていない部分が多い.そこで,我々が開発している耐放射線完全空乏型 SOI MOSFET におけるSET パルスの解析をシミュレーションにより行った.

# 目次

| 第1章          | 序論                                                     | 1  |

|--------------|--------------------------------------------------------|----|

| 1.1          | 宇宙機における高性能半導体装置の必要性とソフトエラーの問題                          | 1  |

| 1.2          | 宇宙における放射線環境                                            | 2  |

| 1.3          | 放射線が半導体に及ぼす影響とその対策・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 4  |

|              | 1.3.1 放射線が半導体に及ぼす影響                                    | 4  |

|              | 1.3.2 既存のソフトエラー対策技術                                    | 9  |

| 1.4          | 本研究の目的                                                 | 13 |

| 第2章          | シミュレーション手法                                             | 14 |

| 2.1          | シミュレーションに用いたデバイスと回路構成                                  | 14 |

| 2.2          | シミュレーションに用いた物理モデル                                      | 16 |

| 第3章          | シミュレーション結果と考察                                          | 20 |

| 3.1          | デバイスの静特性                                               | 20 |

| 3.2          | 論理回路における SET パルス                                       | 22 |

| 3.3          | トランジスタ単体における SET 電流                                    | 28 |

|              | 3.3.1 SET による電子、正孔電流の変化                                | 28 |

|              | 3.3.2 SET によるポテンシャルの変化                                 | 29 |

|              | 3.3.3 インパクトイオン化の影響                                     | 35 |

|              | 3.3.4 再結合の影響                                           | 38 |

|              | 3.3.5 寄生バイポーラ効果以外の SET 電流成分の分析                         | 41 |

| 3.4          | SET <b>電流を用いた</b> SET <b>パルス幅の推定</b>                   | 43 |

|              | 3.4.1 インバータ回路のモデル化                                     | 43 |

|              | 3.4.2 パルス幅の推定                                          | 46 |

| <b>笙</b> 4 音 | 幺≐≘슮                                                   | 18 |

# 第1章 序論

# 1.1 宇宙機における高性能半導体装置の必要性とソフト エラーの問題

人工衛星や宇宙ステーションで使われる半導体は、太陽宇宙線や銀河宇宙線にさらされる。このような放射線が当たることにより引き起こされる現象としてソフトエラーが問題となっている。ソフトエラーとは、放射線が LSI チップを構成するトランジスタ中を通過することにより発生する電荷が原因で、LSI 中のメモリや論理回路が一時的に誤動作する現象である。宇宙ステーション・ミール内に持ち込んだノートパソコンは平均して約 15 時間に 1 回、ソフトエラーで誤動作したと言われている [1]。

ソフトエラーの原因は大きく分けて2種類ある。1つはシングル・イベント・ア プセット (Single Event Upset、以下 SEU) と呼ばれ、メモリやフリップフロップ等 のデータ保持セル内をイオンが貫き、その電圧変動がビット反転を引き起こす現象 である。もう1つはシングル・イベント・トランジェント (Single Event Transient、 以下 SET) と呼ばれ、NOT や NAND 等の論理セル内に入射したイオンが発生さ せた電圧パルスが回路中を伝播し、フリップフロップにラッチされて誤ったデー タを記憶させてしまう現象である [2,3]。ゲート長が  $0.3\mu\mathrm{m}$  より大きい場合は、論 理回路において SET はめったに観測されない。発生した SET パルスのほとんど が回路中を伝播できず、フリップフロップに到達して捕捉されることがないため である。また、SETパルスが捕捉されるには、クロックの立ち上がりと同時にフ リップフロップに到達していなければならないが、周波数が遅い回路においては 時間当たりのクロック立ち上がり回数が少ないため、その確率が小さい。そのた め、ゲート長が大きく、周波数の遅い古い世代の回路における SET の影響はあま り問題にならず、これまで宇宙用のマイクロプロセッサーの品質保証にはレジス タの SEU 耐性のみが評価されてきた。しかし、近年、デバイスの微細化、クロッ ク周波数の高速化の要求に伴い、論理回路における SET の影響が無視できない問 題になっている [4]。

我が国においては、これまでこういったソフトエラーに強い最先端の宇宙用半導体部品は、一般に使用されている電子部品等(以下、民生品という)に比べ、高価で入手し難く、最先端の部品はあきらめて2、3世代前の古い部品を用いざるを得ない状況だった。安価で、高性能、高機能化の進んだ民生品が宇宙に適用可能と

なれば、人工衛星等の低コスト化、高性能化が可能であるが、現在の民生品は放射線の影響の少ない地上環境で用いられることを想定して開発されたもので、放射線環境を一切考慮していない。したがって、民生品を宇宙環境においても用いようとする場合は、その耐放射線性を考慮する必要がある。そこで、一般民生用の半導体素子に対する放射線照射による影響への関心が高まり、本格的に検討されるようになった [5]。

以上は宇宙環境における話であるが、地上で用いる民生部品においても,微細化が進んだことにより,部品内部の不純物材料から発生する放射線問題に加えて,地上に降り注ぐ宇宙線中性子シャワーの問題が顕在化している。中性子線によるソフトエラーの問題は、航空機だけでなくハイエンドサーバー等 IT 基盤技術においても危惧されている [6]。

## 1.2 宇宙における放射線環境

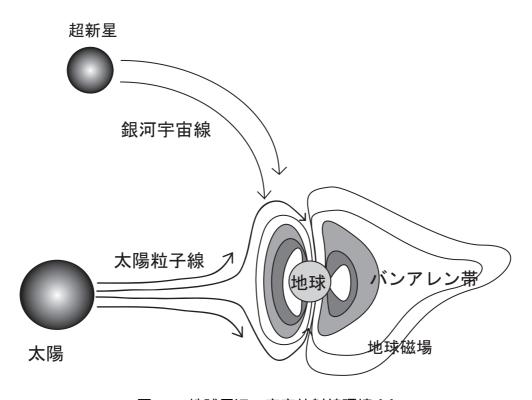

図1.1に地球をとりまく宇宙放射線環境の模式図を示す。

図 1.1: 地球周辺の宇宙放射線環境 [7]

宇宙放射線は銀河宇宙線、太陽粒子線、捕捉粒子線の三種類に分類され、それぞれ含まれる成分やエネルギーが異なる[8]。

銀河宇宙線は銀河の彼方から飛来する荷電粒子であり、超新星爆発などが起源だとされている。主に陽子、 粒子、鉄などの重イオン粒子からなる [9]。

太陽粒子線は、太陽表面の大爆発の結果として太陽表面から放出される高エネルギー粒子線である。ほとんどが陽子と電子で他に数%の 粒子と微量の重粒子が含まれる。太陽は11年周期で活動しており、太陽表面の爆発(太陽フレア)やそれに伴うコロナ物質放出などにより数MeVから時には数GeVにおよぶ大量の高エネルギー粒子が放出されている[10]。

捕捉粒子線とは太陽粒子線などが地磁気の磁力線に捕捉されたものである。地球の地磁気によって捕捉された荷電粒子がドーナッツ状に存在する放射線帯はバンアレン帯として知られている。バンアレン帯は数 100keV ~ 数 100MeV の電子や陽子で構成されている。捕捉電子、陽子は赤道上空を中心に分布し、南北両極付近の高緯度ではほとんど存在していない。放射線帯は完全に左右対称ではなく、地球の磁場を作る双極子が地球の中心から少しずれているため、放射線強度が強くなる場所がある。高度が約 350 ~ 1500km の間の低高度では、南米のブラジル上空にバンアレン帯が局所的に低高度にまで広がっている領域があり、SAA(South Atlantic Anomaly) と呼ばれている。人工衛星がその領域を通過する際、バンアレン帯の高エネルギー陽子の被ばくや陽子によるシングルイベント現象が発生し、機器が誤動作することが多い [11]。

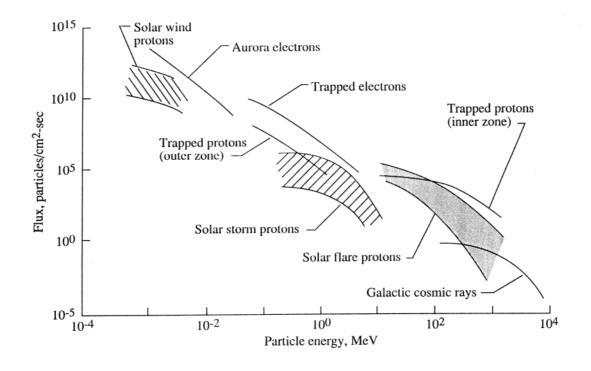

図 1.2 に地球周辺の宇宙放射線環境におけるエネルギー分布を示す。

図 1.2: 地球周辺の宇宙放射線環境における粒子のエネルギー分布 [12]

以上は宇宙環境での話であるが、地球上で観測したり、我々が日常浴びている宇宙線は宇宙空間から飛来する多種多様な放射線粒子が地球の大気や、地球の地殻と相互作用した結果生じた粒子である。宇宙からやって来る宇宙線(一次宇宙線)は、まず上層の大気にぶつかり、空気中の窒素や酸素の原子核に衝突し、陽子、中性子、パイ中間子、ミュ・粒子など多数の二次粒子(二次宇宙線)を発生させる。この粒子がまた、大気の窒素や酸素の原子核と次々と衝突し、多数の粒子を発生させる。エネルギ・の高い一次宇宙線ほど、より多数の二次粒子を発生させる。

大気の上層部で連鎖状に発生した二次宇宙線のうち、地表まで降ってくるのは大部分がミュー粒子である。他にニュートリノや電子なども含まれている。ミュー粒子や電子のように電気を帯びた粒子が、物質の中を通ると、周りの分子や原子に含まれる電子をはじき飛ばしてイオン化する。デバイスの微細化に伴い、地上における宇宙線の影響も無視できない問題となっている [13]。

## 1.3 放射線が半導体に及ぼす影響とその対策

#### 1.3.1 放射線が半導体に及ぼす影響

放射線により半導体素子が受ける影響には、大別すると、放射線の総照射量に応じて素子特性が劣化するトータルドーズ効果と、一個の粒子が入射することによって素子に機能障害が生ずるシングルイベント効果がある。

#### I. トータルドーズ効果

トータルドーズ効果とは、放射線による半導体デバイスの損傷が蓄積され、半永久的に特性を劣化させる現象である [14]。放射線の種類やエネルギーによらず、それらが発生させた電離の総量だけによって劣化が決まる。絶縁用酸化層内の正電荷捕獲、酸化層と基板界面の界面準位の発生、基板結晶の欠陥発生などの損傷によって起こる。トータルドーズ効果は宇宙放射線に曝される半導体部品の性能劣化の代表的な現象である。

#### II. シングル・イベント効果

半導体に単発の高エネルギー粒子が入射することによって起こる現象をシングル・イベント効果 (Single Event Effect、以下 SEE) という。SEE は、宇宙機が運用される宇宙環境に存在する、プロトン (陽子線)、重粒子線などの高エネルギー粒子により引き起こされる。1 個の粒子が半導体デバイスの逆バイアスされた接合部に入射したとき一回だけパルス状の電流が発生するため、このように呼ばれるようになった。

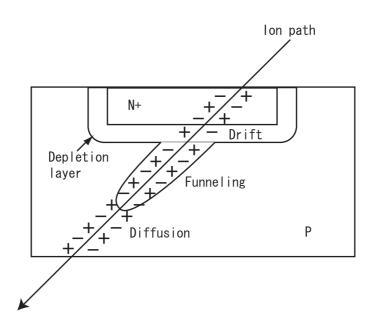

図 1.3 は、Fe イオンのような重イオンが半導体素子の pn 接合部分を貫通したと きの電荷生成及び収集の様子を示している。半導体デバイスに入射した高エネル ギー粒子はその運動エネルギーを電離により失う。この電離作用により高エネル ギー粒子の軌跡沿いに電子と正孔が作られる [15]。たとえば 5MeV 粒子が入射 する場合、電子-正孔対の数はイオンの飛跡に沿って、半径 $0.1 \mu m$  以内の円柱状に 初期密度として、 $10^{18} pairs/cm^3$ を超える量が発生する。これは、不純物密度また は多数キャリア密度を超える量であり、飛跡に沿って電気的に中性な領域(プラズ マ柱)が形成される。これが動径方向に両極性拡散過程により拡散していき、空 乏層内キャリア密度まで電界が回復しプラズマ濃度が下がった時点で、空乏層内 で電界が回復し、プラズマ柱に沿って伸びていくことになる。これ以降、電子-正 孔対は電子及び正孔に別れ、空乏層内で発生したものは空乏層電界により吸収さ れる(ドリフト)。さらに高エネルギー粒子の侵入により発生した多量の電荷によ り,それまで空乏層に印加されていた電界の一部が基板内部にまで印加されるよう になるため、空乏層より深い場所でのキャリアも収集され、発生電流に寄与する。 N+電極から漏斗 (funnel) のように伸びた電界により電荷が収集される現象を、そ の電界の形状からファネリングとよび、イオンによる異常電荷収集の最大の原因 と考えられている [16]。最後に、飛跡の先の電子及び正孔は拡散により遅れて電 極に到達する。

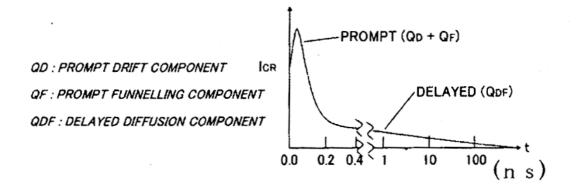

図 1.4 に重イオンが発生させた電流パルスモデルを示す [17]。光速度に近い放射線により半導体素子中に電子-正孔対が形成される時間は 1ps 以下である。発生電流には、100ps 程度の早い成分と数 ns 以上の遅い成分がある。早い収集過程は、空乏層内でのドリフトとファネリングによって引き起こされ、これら 2 つの過程は 50ps から数 100ps で終わる。その後、1ns ~数  $\mu s$  の間、空乏層端近傍のキャリアも拡散で吸収され、遅延成分として現れる。

高エネルギー粒子によって発生する電荷量は、それが物質中を通過する際、飛程の単位長さ当りに平均して失うエネルギー Linear Energy Transfer(以下、LET)で決まる [18]。その単位は  $MeV/(mg/cm^2)$  などが用いられる。一般に LET は入射粒子の原子番号の二乗に比例し、粒子の速さにほぼ反比例する。X 線やガンマ線のように電磁波で物質との相互作用の程度が小さく LET の小さいものを低 LET 放射線といい、中性子線やアルファ線のように粒子の質量が大きくて物質と相互作用しやすく LET の大きいものを高 LET 放射線という。

シングルイベント効果によるエラーは、ソフトエラーとハードエラーに分類できる。ソフトエラーは、メモリー素子をリセットしたりリライトしたりすることによって正常な動作に戻すことができるため、非破壊的なエラーといえる。その代表例はSETとSEUである。それに対して、ハードエラーは永久的なもので、ハードエラーの代表的な例はシングル・イベント・ラッチアップである。以下、それぞれについて解説する。

図 1.3: シングル・イベント効果

図 1.4: 電極に吸収されたキャリアによる電流波形 [17]

#### i. シングル・イベント・ラッチアップ

バルク CMOS デバイスではウエル領域によって基板とトランジスタとの電気的分離を行っているため、電源- GND 端子間にシリコンチップ上に寄生的に pnpn型のサイリスタ構造が存在する。図 1.5 に CMOS 集積回路の中に存在する寄生サイリスタ構造を示す。このサイリスタの寄生トランジスタの部分に電荷が発生すると、電極間が導通状態になり、外部電源を切るまで IC に大電流が流れ続け、ついには焼損することもある。この現象を SEL という。

図 1.5: シングル・イベント・ラッチアップ

#### ii. シングル・イベント・アップセット

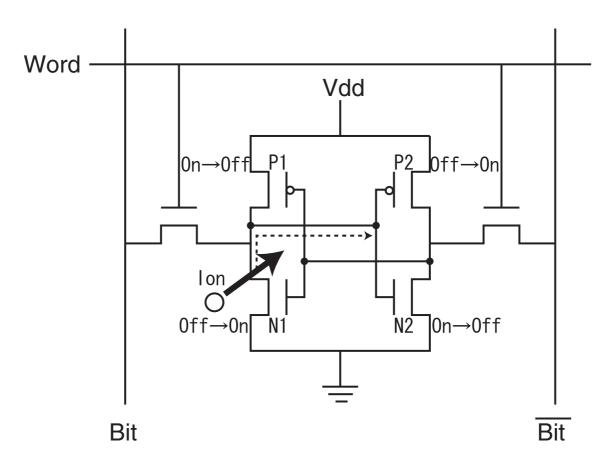

トランジスタに重イオンが入射することにより、本来なら逆バイアスされているために電流が流れるはずの無い場所に電流が流れるため、オフ状態のトランジスタがオンしてしまうことがある。データ保持セル内でこれが起こると、状態が反転してしまうことがある。この現象は、「高エネルギー粒子による一回の反転事象」ということで、シングル・イベント・アップセット(SEU)と呼ばれる。

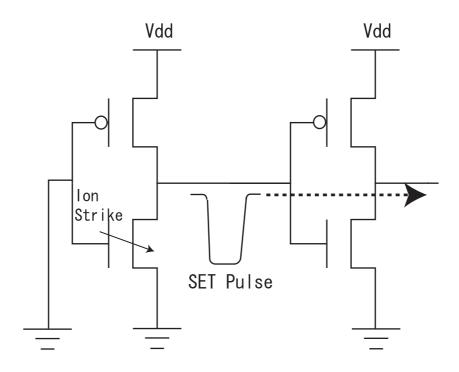

図 1.6 は、CMOS SRAM セルに重イオンが入射したときの SEU の模式図である。オフトランジスタ N1 のドレインにイオンが入射し(図の太線矢印)、ドレインの電位変動が N2、P2 に伝達される(図の破線)。P2 がオンになることによって、そのソース側の電位が上昇し、P1 がオフ、N1 がオンになる。以上の電位変化により、トランジスタのオン・オフが反転してしまり、誤動作を引き起こす。

図 1.6: CMOS SRAM セル内でのシングル・イベント・アップセット

#### iii. シングル・イベント・トランジェント

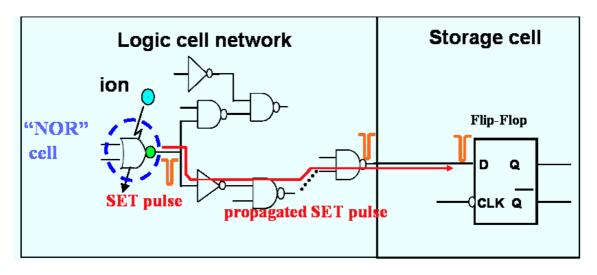

集積回路 (特に組み合わせ論理回路) を入射する重イオンによって生じた過渡電流 (あるいは電圧) をシングル・イベント・トランジェント (SET) と呼ぶ。本論文では、その過渡電圧を SET パルス、過渡電流を SET 電流と定義する。組み合わせ論理回路で生じた SET パルスがラッチまで伝播すると、ii で述べた SEU を引き起こす可能性がある。

図1.7にイオン入射により論理セル内で発生した SET パルスがセル内を伝播していき、データ保持セルでフリップフロップにキャプチャされる様子を示す。論理セルの出力電圧変動中に、フリップフロップにクロックが印可されると変動した信号がデータとして保持されてしまう。これが、SET パルスによるデータ保持セルの誤動作である。SET は、SEU と異なり、高速動作時に顕在化してくる放射線障害である。ゲート長の大きい回路では遠くまで伝播せず、クロック周波数の遅い回路ではラッチされることもほとんどなかったので、SET による SEU はこれまでほとんど無視されていた。しかし、近年の回路の微細化、クロック周波数の高速化に伴い、組み合わせ回路で生じた SET パルスがラッチされやすくなり、深刻

な問題となってきている [4]。

SET パルスによる誤動作を防ぐには、それがデータ保持セルに到達する前に、フィルタを挿入してパルスをカットすればよい。しかし、そのためには SET パルスの幅や大きさなどを明らかにしておく必要がある。特に後述の SOI デバイスにおいては、その特性は不明な部分が多く、調査が必要である。

図 1.7: シングル・イベント・トランジェント

#### 1.3.2 既存のソフトエラー対策技術

前節では、放射線が半導体素子に及ぼす効果について述べたが、放射線に対して耐性の強い半導体素子の開発は、宇宙開発の分野において非常に重要な課題である。宇宙開発の初期から、半導体素子に対する耐放射線性の研究は続けられてきた。

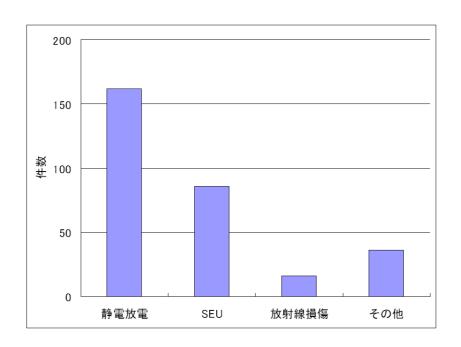

図1.8に宇宙機の異常件数とその原因のヒストグラムを示す。このように、宇宙機の機器異常の原因の1/4以上がSEUによるものである。よって本論文ではSEU、およびSETが引き起こすSEUに絞り、その対策を考える。SEU及びSETによるソフトエラー対策は、システムレベルでの対策、回路レベルでの対策、そしてデバイスレベルでの対策の3つに分けられる。本節では、それぞれのレベルでの主なソフトエラー対策技術を紹介する。

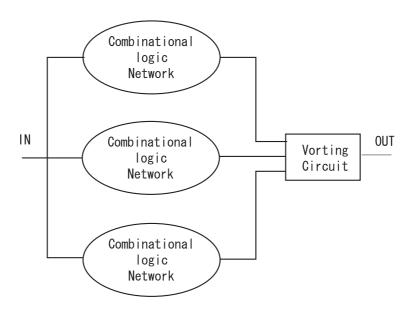

#### 多数決回路

放射線のシステムレベルでの対策として、多数決回路が挙げられる。多数決回路では、回路の冗長化によってシステムの信頼性を高めてある。冗長化とは、リソースを多重化することである。組み合わせ論理で最もよく用いられる冗長化手

図 1.8: 宇宙における機器異常の原因の分類 [19]

法は、図 1.9 に示すような三重冗長 (TMR:Triple Mode Redundancy) の多数決論 理構成である [4]。2005 年 8 月にバイコヌールから打ち上げられた衛星「れいめい」がこの手法を採用している [20]。この手法では、同時に 2 つ以上の回路要素がエラーを起こさない限り、エラーの伝播は阻止されるので、放射線が入射するとエラーを起こす領域が  $10 \sim 100$  分の 1 に縮小する。この手法の欠点は、組み合わせ論理回路に 3 倍の面積が必要となり、さらに多数決回路のための面積と時間の遅れがあるということである。また、多数決回路自体がエラーを起こす可能性もあり、その対策も考慮する必要がある。

図 1.9: 三重冗長

#### ローパスフィルタ

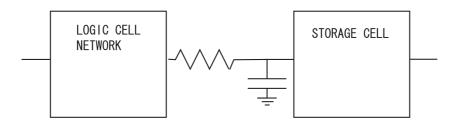

回路レベルでのソフトエラー対策として、ローパスフィルタが挙げられる。図 3.5 に回路におけるローパスフィルタの例として RC フィルタを示す [4]。論理回路 の出力端に RC フィルタをつけることで、SET の伝播を阻止し、ラッチ回路への パルスの入力を阻止することができる。

しかし、この方法ではRとCの実装面積コストが高いという難点がある。そのため、パルスの幅、大きさを考慮して必要最低限の大きさにすることが重要になる。

図 1.10: RC フィルタ

#### Silicon on Insulator

プロセスレベルでの耐放射線性強化技術として、Silicon on Insulator (以下、SOI)技術が挙げられる。前節までの対策手法では機器のリソース規模が大きく

なってしまうが、本対策では大きさはそのままで耐放射線性を上げることが可能 である。

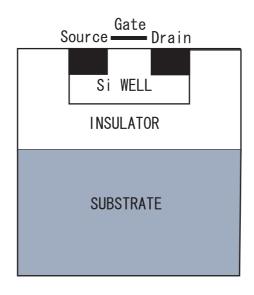

SOI デバイスは、高速・低消費電力回路向けのデバイスであるだけではなく、耐 環境用のデバイスとして古くから知られている。SOI CMOS は図 1.11 に示すよ うに、とても薄いシリコン結晶層の上に通常構造の MOSFET を作ったものであ る [21]。薄いシリコン層は、厚い埋め込み  $SiO_2$ 層 (通常 1000 かそれ以上) によっ て基板と隔てられている。それゆえ個々の MOSFET は、そのさらに下のシリコン 基板と電気的に絶縁されている。SOI 基板は , シリコン基板中に酸素をイオン注 入したり,表面を酸化したシリコン基板を貼り合わせるなどの方法によって作ら れる。最近の SOI 基板品質の向上と、すでに確立されている CMOS 製造技術との 高い親和性ゆえ、VLSIへの応用にとくに適している。SOI 層の膜厚が50nm 程度 と、チャネルの空乏層深さより薄く、チャネル部分が空乏化している構造の SOI を完全空乏型 (Fully Depleted: FD) SOI と呼び, SOI 層がチャネル空乏層より も厚い部分空乏型 (Partially Depleted : PD ) SOI と区別している。FD デバイ スにおいてはボディ領域が完全に空乏化されていることから、急峻なサブスレッ ショルド特性が得られる。一方、PD 型の MOSFET では、ドレイン電流-ドレイン 電圧特性において、ドレイン電圧の増加に伴ってインパクトイオン化が激しく起 こって正孔がボディ領域に蓄積され、急激なドレイン電流増加(キンク)が生じ る [22]。

図 1.11: SOI MOS 構造

SOI デバイスはバルク CMOS より接合容量 (ソース・ドレイン領域と基板間の容量)が小さく、基板バイアス効果が小さいなどの優れた特徴がある。また、SOI 構造では、個々のトランジスタ素子は絶縁体で電気的に分離されており、バルク

中の寄生サイリスタが存在しないため、ラッチアップが物理的に起きない [23]。

## 1.4 本研究の目的

SOI デバイスは、ラッチアップが起きず、放射線環境に強いデバイスとして期待されているが、その SET 特性は未だ明らかにされていない部分が多い . SET 特性がわかれば、ローパスフィルタを用いてデータ保持回路へのパルスの伝播を阻止することができ、SOI の放射線耐性をさらに高めることが可能である。そこで、本論文では、我々が開発している 0.2- $\mu$ m FD-SOI MOSFET における SET パルスの解析をシミュレーションにより行った .

シミュレーションでは論理回路中の SET パルスのパルス形状を調べ、さらに、その原因となっている SET 電流について詳細に調べた。それらの結果から、SET 電流と SET パルスの関係を考察する。

本論文は、本章を含めて4章からなる。第2章においてSETパルスをシミュレーションするための手法について述べる。第3章でSETパルス、電流のシミュレーション結果と考察を述べ、最後の第4章において結論を述べる。

# 第2章 シミュレーション手法

Synopsys 社の TCAD シミュレータを用いて、重イオンが SOI デバイスの通過 した際の SET パルスのシミュレーションを行った。本章ではシミュレーションに 用いたデバイスと、シミュレーション手法を述べる。

## 2.1 シミュレーションに用いたデバイスと回路構成

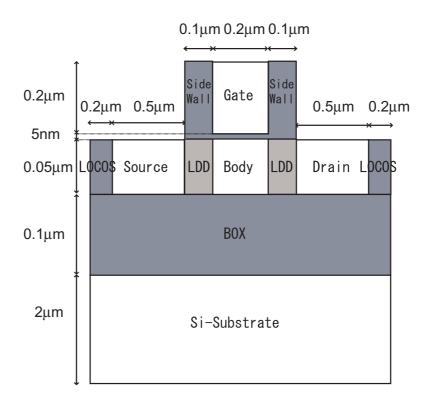

シミュレーションに用いたデバイスは、デバイスの寸法、ドーピング濃度を宇宙研で開発している耐放射線完全空乏型 SOI デバイス [24] を参考にして設定した。シミュレーションに用いたデバイスの寸法を図 2.1、ドーピング濃度を表 2.1 に示す。本シミュレーションでは不純物密度分布は一様としている。デバイスは、SOI素子間を分離するため、外側に LOCOS(Local Oxidation of Silicon) 酸化膜を設けてある。また、LDD(Lightly Doped Drain) と呼ばれる、中濃度のソース、ドレイン拡張領域を用いて、ホットエレクトロン効果を緩和するように設計されている。

表 2.1: シミュレーションに用いた SOI MOSFET のドーピング濃度

| Location              | Material | Doping material | Doping concentration |

|-----------------------|----------|-----------------|----------------------|

| Gate                  | Poly Si  | Phosphorus      | 5e+19                |

| Body                  | Si       | Boron           | 3e+17                |

| Source, Drain         | Si       | Arsenic         | 1e+20                |

| LDD                   | Si       | Arsenic         | 1e+18                |

| Substrate             | Si       | Boron           | 5e+14                |

| BOX, LOCOS, Side Wall | Oxide    | -               | -                    |

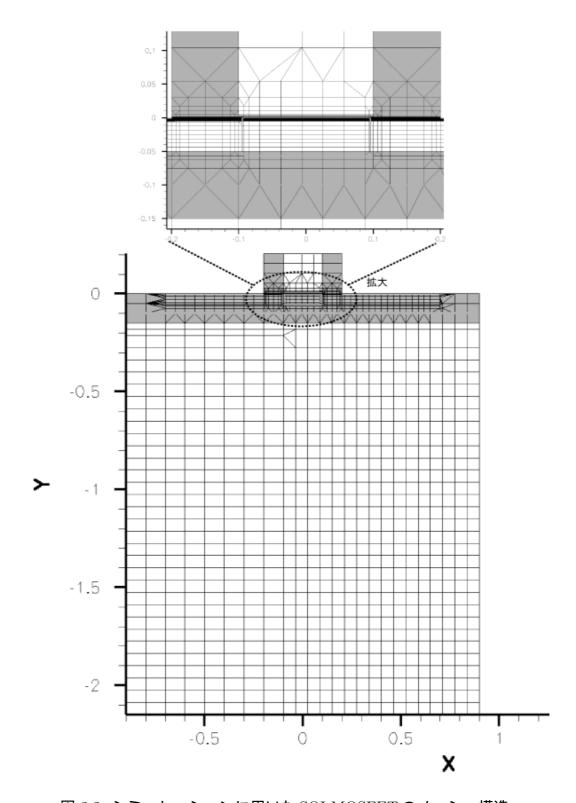

SOI MOSFET の二次元のデバイス構造と、その構造に対するメッシュ生成には Synopsys 社の MESH ツールを使用した。シミュレーションに用いたデバイスは図 2.2 のようにメッシュを切ってある。BOX 上部のシリコン層 (SOI 層) はメッシュを細かくしてあり、特に、電流特性に深く関係するチャネル領域のy(高さ)方向のメッシュは 0.5nm と非常に細かく切ってある。

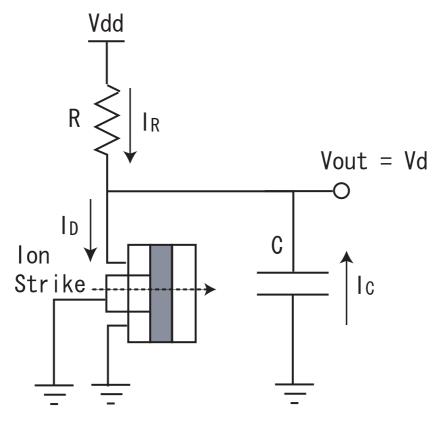

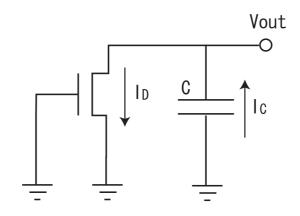

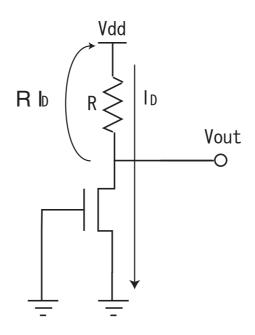

この SOI デバイスを用いて、論理回路の基本構成要素であるインバータを作成し、それに重イオンが入射した場合のシミュレーションを行った。本研究では、図

図 2.1: シミュレーションに用いた SOI MOSFET の寸法

2.3 のように 2 つのインバータが直列接続している場合を想定した。初段のインバータは接地し、NMOS はオフ状態にした。初段のインバータを構成する NMOS に重イオンが当たった事で生じる SET パルス、すなわち初段のインバータの出力電圧の変動を解析した。ここで、初段のインバータの PMOS はオン抵抗で置き換えが可能であり、初段のインバータの出力ノードの負荷容量は次段のインバータのゲート容量で近似できる。よって、この回路の等価回路は図 2.4 のようになる。本論文ではこの図 2.4 の回路を用い、R 及び C それぞれの値を変えることで、インバータで発生した SET パルスの形状を調べた。シミュレーションには、Synopsys社の DESSIS を用いた。先ほど述べた 2 次元の SOI-NMOSFET デバイスモデルに、抵抗 R と容量 C の SPICE モデルを接続することで図 2.4 の回路を実装し、デバイスシミュレーションと回路シミュレーションを同時に行う Mixed-Mode シミュレーションを行った。電源電圧は 2 V に設定し、重イオンが通過する場所は、SOI デバイスで最もパルスが大きくなるゲート中央に設定した [27]。

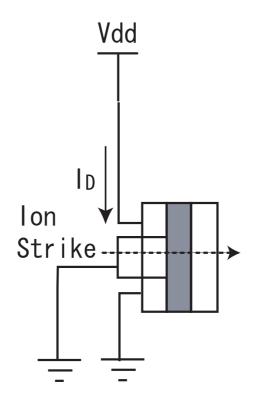

さらに、SET パルスの発生原因である SET 電流を調べるため、図 2.5 の回路を用いてトランジスタ単体における重イオン入射シミュレーションを行った。 ノード電圧が変わると現象が複雑になり、原因の特定が困難になるので、ソース、ゲート電極は 0V、ドレイン電極は 2V に固定してシミュレーションを行った。

## 2.2 シミュレーションに用いた物理モデル

移動度モデルについて、濃度依存性、高電界飽和(速度飽和)及び直行方向電界依存性を指定した。再結合モデルは、Shockley-Read-Hall モデル、Auger、バンド間トンネリングモデル、アバランシェモデル、放射モデルを用いた。その他、バンドギャップナローイングのモデルを使用した。さらに、SOI は熱がこもりやすい構造になっているため、熱力学輸送モデルを用いたシミュレーションを行った。

重イオンの入射は,ガウス型の電子-正孔対生成関数によりモデル化したものを 用いた。

重イオンによる電子-正孔対発生率 G(w,t) は式 (2.1) で定義される [25]。

$$G(w,t) = G_{LET} \times R(w) \times T(t) \tag{2.1}$$

$G_{LET}$  は LET により発生する電子-正孔対密度であり、式 (2.2) で定義される。

$$G_{LET} = \frac{1}{2w_t d} [LET] \tag{2.2}$$

式 2.2 の LET は重イオンの LET である。LET の単位は pC/ $\mu$ m で表される。 $w_t$  はイオンの動径方向の半径で、50nm に設定した。d はデバイスの幅で、 $1\mu$ m に設定した。

R(w) は空間分布であり、式 (2.3) で定義される。

$$R(w) = e^{-\left(\frac{w}{w_t}\right)} \tag{2.3}$$

T(t) は時間変動項であり、式 (2.4) で定義される。

$$T(t) = \frac{2 \times \exp(-\frac{(t-time)}{s_{hi}})^2}{s_{hi}\sqrt{\pi}(1 - \operatorname{erf}(\frac{time}{s_{hi}}))}$$

(2.4)

${

m time}$  項はガウス関数のピーク位置である。 $s_{hi}$  項はガウス関数の特性時間であり、値が小さいほどガウス関数が鋭くなる。シミュレーションでは  ${

m time}=5{

m ps},\ s_{hi}=0.5{

m ps}$  に設定した。

図 2.2: シミュレーションに用いた SOI MOSFET のメッシュ構造

図 2.3: インバータチェーン中の SET パルスの伝播

図 2.4: シミュレーションに用いたインバータ等価回路

図 2.5: シミュレーションに用いたトランジスタ単体回路

# 第3章 シミュレーション結果と考察

# 3.1 デバイスの静特性

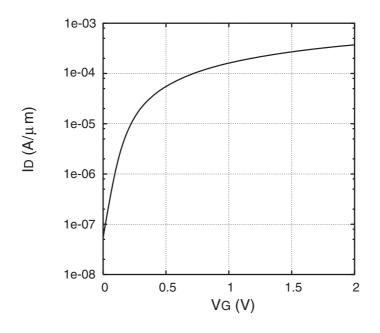

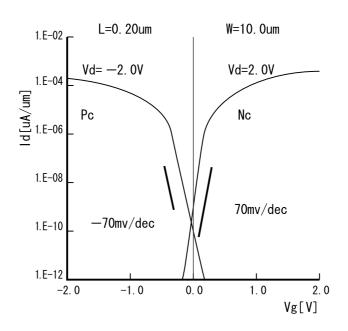

図 3.1 は 2.1 節で述べたデバイスの  $I_D-V_G$  静特性のシミュレーション結果である。ドレイン電圧を 2V、ソース電流を 0V に設定し、ゲート電圧を 2V から 0V まで変化させたときのドレイン電流を示してある。グラフより、オフ電流は 54nA、最大電流は 0.37mA、閾値電圧は 90mV である。また、サブスレッショルドスロープは 70mV/dec であり、完全空乏型 SOI MOSFET の特徴である急峻なサブスレッショルド特性が得られている。図 3.2 は実際に報告されている実デバイスの  $I_D-V_G$  静特性を示している。オフ電流以外はシミュレーションの値とよく一致している。

図 3.1: SOI MOSFET シミュレーションによる  $I_D - V_G$  特性

図 3.2: SOI MOSFET 実デバイスでの  $I_D - V_G$  特性 [26]

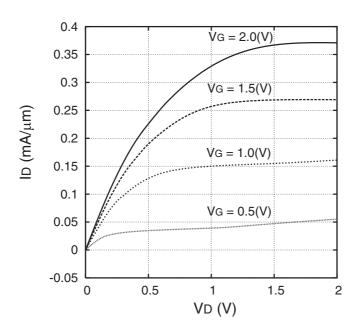

図 3.3 は 2.1 節で述べたデバイスの  $I_D-V_D$  特性のシミュレーション結果である。ドレイン電流-ドレイン電圧特性にキンク特性が見られないので、このデバイスは部分空乏型ではなく、完全空乏型であることがわかる。

図 3.3: SOI MOSFET シミュレーションによる  $I_D - V_D$  特性

オフ電流の差は本研究では問題としない事とする。これを合わせるには、不純物密度分布の調整等複雑な制御を必要とする(本シミュレーションでは不純物密度分布は一様)。本研究では、物理現象の理解を目的としており、可能な限り単純なデバイスモデルを利用することが望ましい。本シミュレーション結果は、完全空乏型 SOI MOSFET の性質を十分反映していることから、これ以上の細かな調整は行わないこととした。

# 3.2 論理回路における SET パルス

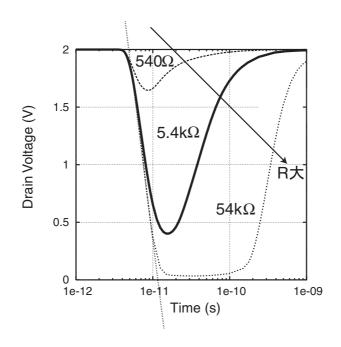

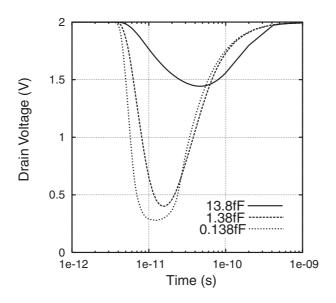

論理回路中の SET パルスを調べるため、図 2.4 の回路の NMOS ゲート中央に LET $0.1 \mathrm{pC}/\mu\mathrm{m}$  の重イオンを入射させるシミュレーションを行った。図 3.4 に PMOS オン抵抗の値である  $5.4 \mathrm{k}$  を基準として  $\mathrm{R}$  を 1/10,10 倍にした場合の SET パルスを示す。 $\mathrm{C}$  はゲート酸化膜容量である  $1.38 \mathrm{fF}$  に固定してある。通常、電圧が電源電圧  $(\mathrm{Vdd}=2\mathrm{V})$  の 2 分の 1 倍になるときにインバータの論理が反転するので、電圧が  $1\mathrm{V}$  以下になっている時間をパルス幅と定義する。 $\mathrm{R}=540$  の場合はドレイン電圧が常に  $1\mathrm{V}$  以上なので、論理が反転することはなく、 $\mathrm{SET}$  パルスが論理回路中を伝播することもない。一方、 $5.4 \mathrm{k}$  、 $54 \mathrm{k}$  のときは  $V_D$  が  $1/2\mathrm{Vdd}$  を下回り、パルス幅は、 $5.4 \mathrm{k}$  で  $30 \mathrm{ps}$ 、 $54 \mathrm{k}$  で  $30 \mathrm{ps}$  である。これら 3 つの抵抗値の  $\mathrm{SET}$  パルスを比較すると、パルス幅の始点を決める、電圧降下時の傾きは  $\mathrm{R}$  を変えて

も変わらず、パルス幅の終点を決める、電圧が上昇するまでの時間はRにほぼ比例して遅れてくることがわかる。

図 3.4: 図 2.4 の SET パルス ( C=1.38fF, R 変化)

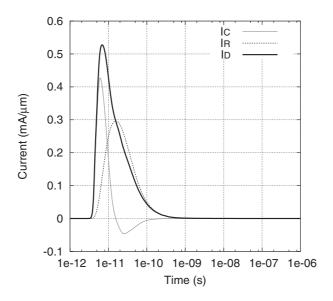

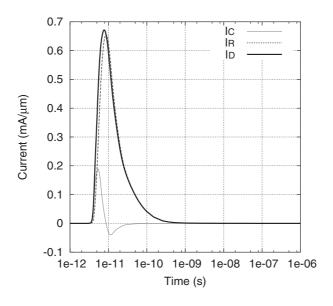

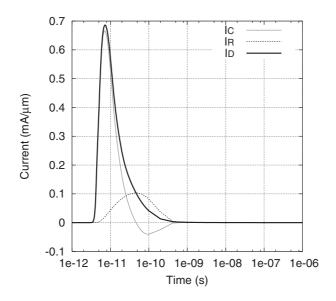

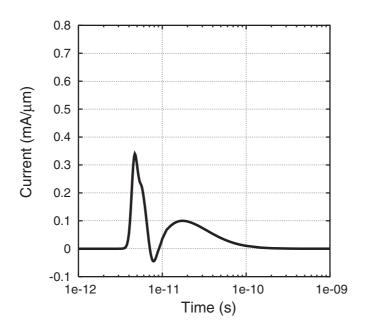

次に、R、C、NMOS のそれぞれを流れる SET 電流を調べた。R=5.4k 、540 、54k それぞれの電流パルスを図 3.5, 3.6, 3.7 に示す。C と R に流れる電流を足すと NMOS ドレイン電流になる。R=5.4k ,54k の図 3.5, 3.7 において、C と R に流れる電流のドレイン電流に対する割合は、最初は C に流れる電流の割合が大きく、約 10ps 以降から R に流れる電流が支配的になっていることがわかる。一方、R=540 の図 3.6 においては、最初から R がドレイン電流に対して支配的になっている様子がわかる。

図 3.5: 図 2.4 の SET 電流( R=5.4k , C=1.38fF)

図 3.6: 図 2.4 の SET 電流 ( R=540  $\,$  , C=1.38fF)

図 3.7: 図 2.4 の SET 電流 (R=54k , C=1.38fF)

図 3.8 に C をゲート容量である 1.38fF を基準とし、1/10,10 倍にした場合の SET パルスを示す。R は PMOS オン抵抗の 5.4 k に固定してある。パルス幅は、C=0.138fF のとき 28ps、1.38fF のとき 30ps、13.8fF のときは 0ps である。Cが大きいほど立ち下がり時間が遅く、ピーク値が小さいことがわかる。1.38fF と 0.138fF の 2 つにおいては、立ち上がり時間がほぼ同じである。

図 3.8: 図 2.4 の SET パルス (R=5.4k , C 変化)

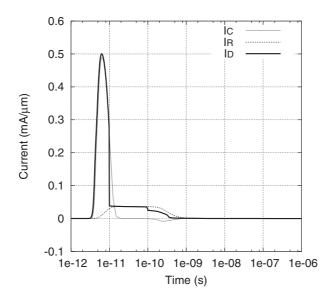

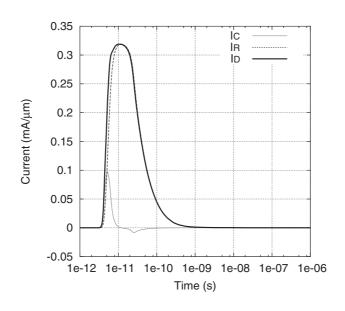

C が 0.138fF のときの電流パルスを図 3.9 に示す。R に流れる電流がドレイン電流の支配的成分になっている様子がわかる。一方、C が 13.8fF のときの電流パルスを図 3.9 に示す。C に流れる電流がドレイン電流のピークの支配的成分になっており、R を流れる電流は遅れて出てきている様子がわかる。

図 3.9: 図 2.4 の SET 電流 ( C=0.138fF, R=5.4k )

図 3.10: 図 2.4 の SET 電流( C=13.8fF, R=5.4k )

これらの電圧、電流成分の考察については3.4.1節で述べる。

## 3.3 トランジスタ単体における SET 電流

前節では論理回路中のSETパルスについて述べたが、その発生原因についての物理的メカニズムを明らかにすることは、SETパルス特性を論じる上で重要である。そこで、本節ではトランジスタ単体に重イオン入射シミュレーションを行い、SETパルスの発生原因であるSET電流成分について解析を行った。

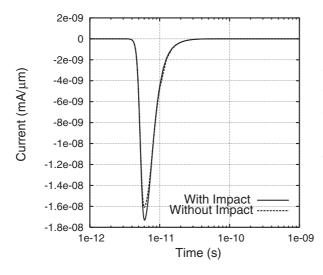

#### 3.3.1 SET による電子、正孔電流の変化

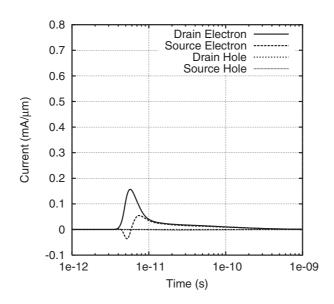

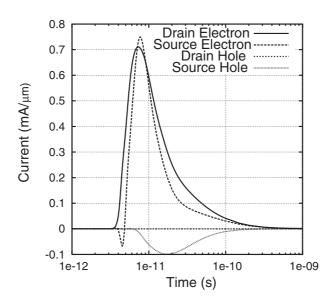

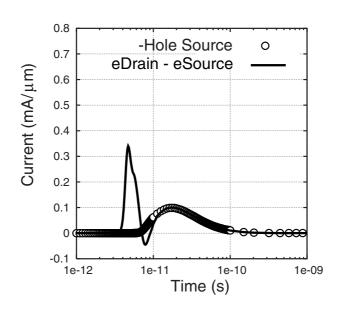

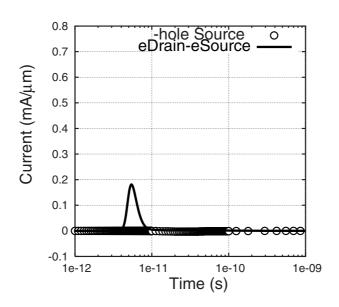

図 3.11 に LET 0.01 pC/ $\mu$ m の場合、図 3.12 に LET 0.1 pC/ $\mu$ m の場合のソース、ドレインそれぞれの電子、正孔電流の変化を示す。電流はドレイン ソース方向を正とする。LET 0.1 pC/ $\mu$ m の場合と LET 0.01 pC/ $\mu$ m の場合共に、ソース電子電流が一度負になった後、正に転じる傾向が確認された。また、ドレイン電子電流とソース電子電流の関係には,LET に対する依存性が確認された。すなわち、LET 0.1 pC/ $\mu$ m の場合は、ドレイン電子電流パルスとソース電子電流パルスの形状がほぼ一致するのに対し、LET 0.01 pC/ $\mu$ m の場合は一致していない。一方、正孔電流は、ドレイン正孔電流が終始ほぼ 0 の値をとっており、ソース正孔電流は、LET 0.1 pC/ $\mu$ m においては電子電流のピーク値付近から増え始め、電子電流がなくなるまで続いている。これらの電流変化の原因について、3.3.2 節で解説を行う。

図 3.11: LET0.01pC/ $\mu$ m における SET 電流

図 3.12: LET0.1pC/ $\mu$ m における SET 電流

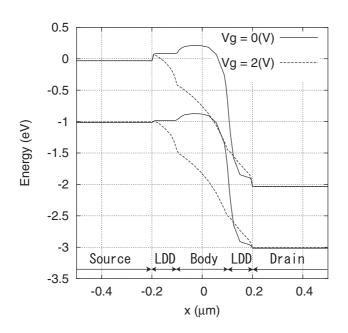

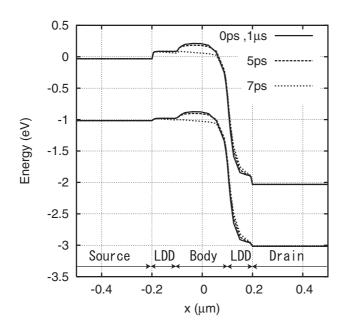

### 3.3.2 SET によるポテンシャルの変化

まず、SET シミュレーションを行わず、MOSFET の正常動作においてポテンシャルがどう変化しているのかを見た。図 3.13 にゲート電圧を 0V から 2V に変化させたときの、価電子帯上端、伝導帯下端のポテンシャルの変化を示す。Vg=0V 時にポテンシャル障壁が 2 段になっているのは、中濃度の LDD 領域があるためである。ゲートに電圧がかかり、ボディのポテンシャルが押し下げられている様子が確認できる。

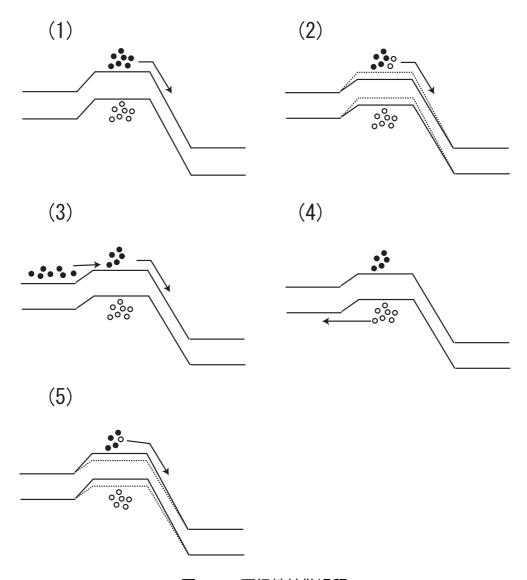

図 3.13: ゲート電圧が 0V 及び 2V のときの SOI バンド図 上側が価電子帯ポテンシャル、下側が伝導帯ポテンシャル

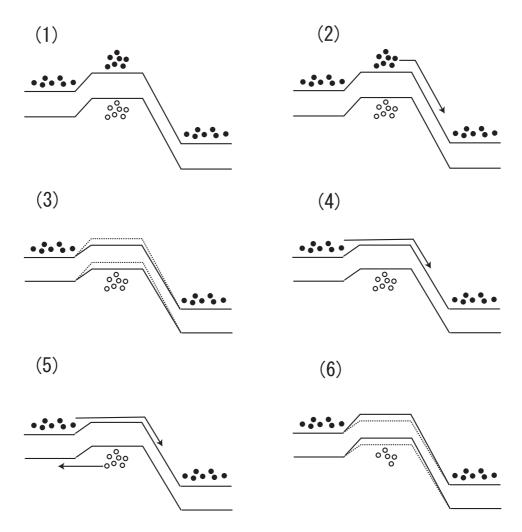

次に、重イオンが入射した場合のポテンシャルの変化について考える。図 3.14 に SOI デバイスのゲートに重イオンが入射した場合の電子(黒丸)と正孔(白丸) の様子と、バンド状態の概念図を示す。まず、重イオンが入射することによって ボディに電子-正孔対が発生する。これが図の(1)である。ボディに発生した電子 は、ボディとドレイン間のポテンシャル差により、直ちにドレイン方向に流れ込 む。また、電子が大量に注入した結果、濃度勾配が大きくなり、ボディからソース へ拡散電流が流れる。これが図の(2)である。イオン入射直後にこの現象が起こっ ており、図 3.12 でそのときに相当する 4~5ps 時を見てみると、ソース電流はマイ ナスになり、ドレイン電流はプラスになっている。したがって、発生した電子が ソース、ドレインの両極に流れ込んでいる様子がわかる。一方、入射した重イオ ンが発生させた正孔は、ソース方向に流れるが、ソース端には正孔に対する電位 障壁があり、一部の正孔はボディ領域に蓄積される。この結果、ボディが正バイア スされ、ボディ領域のポテンシャルが低下する。これが図の(3)である。ボディの ポテンシャルが低下することにより、MOSFET の閾値電圧が低下し、ソースから ドレインに電子が流れ込み、ドレイン電流が異常増加する。これが寄生バイポー ラ効果と呼ばれる現象で、図の(4)で示される。さらに時間が経過すると、正孔が ソース領域に拡散する。これが図の(5)である。ボディの正孔が少なくなると、ボ ディのポテンシャルが上昇する。正孔が十分に無くなると、ソースからドレイン に電流が流れなくなり、寄生バイポーラ効果が終了する。これが図の(6)である。

シミュレーションでは、図 3.12 の 5ps において、ソース電流がマイナスからプラスに転じていることが確認できる。したがって、その時間において寄生バイポーラ効果が始まっているものと考えられる。発生した正孔が無くなり、電流がオフ電流に落ち着く 1ns 程度まで寄生バイポーラ効果は続く。

図 3.14: 重イオンの入射と SOI のバンド図

その他の効果としては、インパクトイオン化による正孔の発生があり、それによる寄生バイポーラ効果にも注意を払う必要がある(3.3.3 節でその影響を述べる)。また、正孔の消滅にはドレイン領域における再結合も考えられ、その効果については3.3.4 節で述べる。

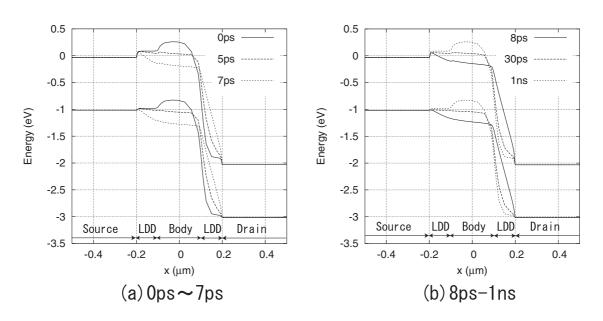

図 3.15 にシミュレーションによる価電子帯、伝導帯ポテンシャルの時間変化を示す。LET は  $0.1pC/\mu m$  に設定した。生成関数のピーク時の 5ps のときは、発生した正孔によりボディのポテンシャルが下がり、ソース LDD と同じ位になっている。この時間において、ソース電流は正になり、寄生バイポーラ効果が始まる。さ

らに 2ps 経過した 7ps の時は、5ps 時よりもボディのポテンシャルが下がっている。したがって、寄生バイポーラ効果も大きくなっているものと予想される。実際、図 3.12 では、7ps の時にドレイン電子電流がピーク値をとっている。8ps 時は、7ps 時よりポテンシャルが上昇している。このときは、図 3.12 で、ソース電子電流がピーク値をとり、ドレイン電子電流を上回っているときである。これは、ソースから入った電子がボディ領域に蓄積するため、一時的にドレイン電流のほうが大きくなってしまうためだと考えられる。さらに時間が経過し、30ps になったときには、ボディのポテンシャルが再びソース LDD と同じ程度まで上昇する。それとともに、寄生バイポーラ効果の影響も弱くなり、電子電流は減少する。最後に 1ns になったときには、初期状態のポテンシャルと変わらなくなり、電流が流れなくなる。

図3.13のバンド図と比較してみると、図3.13ではゲートにかかる電圧によってボディのポテンシャルが低下しているが、図3.15ではボディに溜まった正孔によりそのポテンシャルが低下している。したがって、正常動作と寄生バイポーラ効果の違いはボディのポテンシャル低下の原因がゲート電圧か正孔かの違いだけであることが確認できた。

図 3.15: LET0.1pC/ $\mu$ m における価電子帯、伝導帯ポテンシャルの時間変化

図 3.16 は LET0.01pC/ $\mu$ m の場合の価電子帯、伝導帯ポテンシャルの時間変化である。LET0.1pC/ $\mu$ m の場合と違い、5ps ではほとんどボディのポテンシャルが下がらず、7ps においても LDD と同じくらいしか下がらない。これは、発生する正孔が少ないため、ポテンシャル低下が小さく、寄生バイポーラ効果の始まる時間が遅れていることを示している。

図 3.16: LET0.01pC/ $\mu$ m における価電子帯、伝導帯ポテンシャルの変化

以上の議論を元に、SET ドレイン電流成分を分析する。図 3.12 において、ドレイン正孔電流はドレイン電子電流に比べて無視できるほど小さいので、ここではドレイン電流のドレイン電子電流成分のみ考える。図 3.14 においてソース電子電流が流れるのは (4) の時であるので、ソース電子電流は寄生バイポーラ効果によりドレインに流れる電流である。よってドレイン電子電流からソース電子電流を引くと、寄生バイポーラ以外の電流成分が現れる。図 3.17 に、その電流成分を表す。ピークが 2 つあり、1 番目のピークは図 3.14 の (2) の過程、つまり最初に発生した電子のドリフトによるものであると考えられる。2 番目のピークについては、従来はインパクトイオン化によるものであると考えられていたので、次節においてインパクトイオン化を有効にした場合、無効にした場合におけるシミュレーションを行い、その影響を確かめる。

図 3.17: LET $0.1 pC/\mu m$  におけるドレイン電子電流とソース電子電流の差分 (寄生バイポーラ効果以外の電流成分)

#### 3.3.3 インパクトイオン化の影響

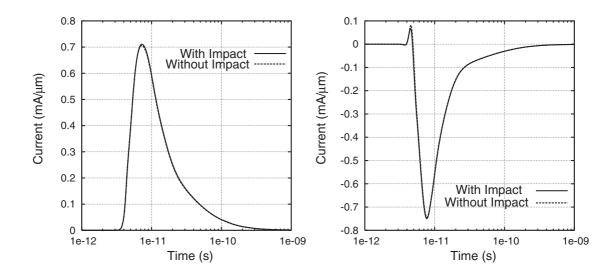

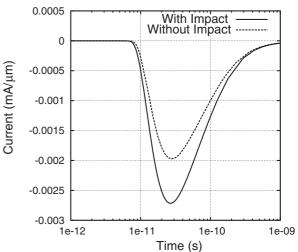

図 3.18-3.25 にインパクトイオン化を有効にした場合と無効にした場合でそれぞれの電流を比較したグラフを示す。電流は、中心のボディから各電極の反対方向を正にとってある。LET $0.1 \mathrm{pC}/\mu\mathrm{m}$  の場合である図 3.18-3.21 を見ると、インパクトイオン化の有る無しで電流の違いがない。よって、図 3.17 における 2 番目のピークはインパクトイオン化によって発生したものではないと考えられる。

一方、LET $0.01 \mathrm{pC}/\mu\mathrm{m}$  の場合は、図 3.22-3.25 を見ると、電流が異なっている。LET $0.01 \mathrm{pC}/\mu\mathrm{m}$  の場合は、インパクトイオン化を入れないほうが電流量が減少している。これは、インパクトイオン化を有効にした場合だと、重イオンだけでなく、インパクトイオン化によっても電子-正孔対が発生し、寄生バイポーラ効果が起こるためである。

図 3.18: インパクトイオン化有効無効 図 3.19: インパクトイオン化有効無効 LET0.1pC/ $\mu$ m ドレイン電子電流 LET0.1pC/ $\mu$ m ソース電子電流

図 3.20: インパクトイオン化有効無効 LET0.1pC/ $\mu$ m ドレイン正孔電流

図 3.21: インパクトイオン化有効無効 LET0.1pC/ $\mu$ m ソース正孔電流

0.05 With Impact — Without Impact ----0.04 0.03 0.02 Current (mA/µm) 0.01 0 -0.01 -0.02 -0.03 -0.04 -0.05 -0.06 1e-12 1e-11 1e-09 Time (s)

図 3.22: インパクトイオン化有効無効 LET0.01pC/ $\mu$ m ドレイン電子電流

図 3.23: インパクトイオン化有効無効 LET0.01pC/ $\mu$ m ソース電子電流

図 3.24: インパクトイオン化有効無効 LET0.01pC/ $\mu$ m ドレイン正孔電流

図 3.25: インパクトイオン化有効無効 LET0.01pC/ $\mu$ m ソース正孔電流

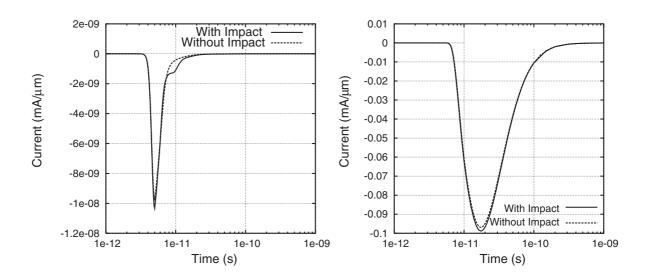

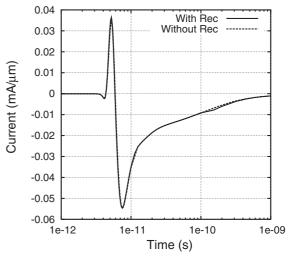

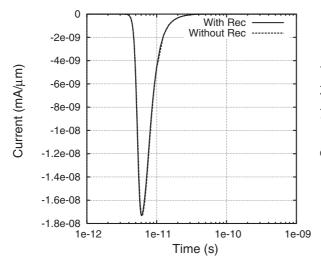

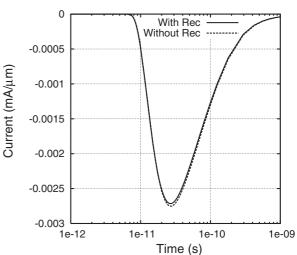

#### 3.3.4 再結合の影響

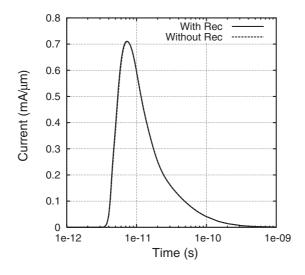

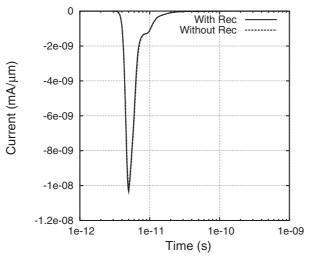

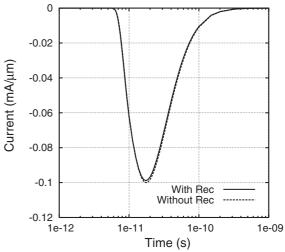

ボディに発生した正孔が消えるまでの時間は、寄生バイポーラ効果の持続時間であり、パルス幅に影響する。ボディに溜まった正孔のほとんどはソース電極に流れるか、ソース及びソース側 LDD の電子と再結合する。本節ではソース、ソース側 LDD による再結合をなくしたシミュレーションを行い、その内の再結合の影響を調べた。図 3.26-3.33 に再結合を入れた場合と入れない場合でそれぞれの電流を比較したグラフを示す。図を見ると、LET0.1pC/ $\mu$ m、0.01pC/ $\mu$ m の場合いずれも再結合有り無しでほとんど電流が変わらない。よって、本デバイスでは発生した正孔がほとんど再結合せずにソース電極側に流れて消えるものと考えられる。

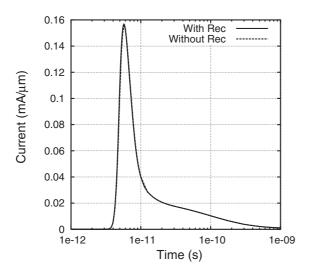

図 3.26: 再結合有り無し LET $0.1 \mathrm{pC}/\mu\mathrm{m}$  ドレイン電子電流

図 3.27: 再結合有り無し LET $0.1 \mathrm{pC}/\mu\mathrm{m}$  ソース電子電流

図 3.28: 再結合有り無し LET $0.1 \mathrm{pC}/\mu\mathrm{m}$  ドレイン正孔電流

図 3.29: 再結合有り無し LET $0.1 \mathrm{pC}/\mu\mathrm{m}$  ソース正孔電流

図 3.30: 再結合有り無し LET $0.01 \mathrm{pC}/\mu\mathrm{m}$  ドレイン電子電流

図 3.31: 再結合有り無し LET $0.01 \mathrm{pC}/\mu\mathrm{m}$  ソース電子電流

図 3.32: 再結合有り無し LET $0.01 \mathrm{pC}/\mu\mathrm{m}$  ドレイン正孔電流

図 3.33: 再結合有り無し LET $0.01 \mathrm{pC}/\mu\mathrm{m}$  ソース正孔電流

#### 3.3.5 寄生バイポーラ効果以外の SET 電流成分の分析

3.3.2 節において、図3.17 のドレイン電子電流とソース電子電流の差分は寄生バイポーラ効果以外の SET 電流成分を表すと述べた。ドレイン電子電流とソース電子電流の差分のピークは2 つあり、第 1 のピークはボディに発生した電子のドリフトによるものである。第 2 のピークについて、その原因はインパクトイオン化によるものではないことを3.3.3 節において示した。本節では、その2つ目のピークの発生原因を考察する。

図 3.34 にドレイン電子電流とソース電子電流の差分及びソース正孔電流を示す。 これを見ると、2 つ目のピークはソースに流れる正孔電流と対応していることがわ かる。

図 3.34: LET0.1pC/ $\mu$ m ドレイン電子電流とソース電子電流の差分 (寄生バイポーラ効果以外の成分) 及びソース正孔電流

この現象を説明するのに、図 3.35 のバンド図を用いる。まず、(1) で発生した電子-正孔対の内、電子がドレイン側にこぼれる。これが 1 個目のピークである。先ほどの図 3.14 では、この過程で電子が全部こぼれるものとしたが、電子は全部こぼれずに、次の (2) で電子が減った分、ポテンシャルが下がる。そして (3) で、ポテンシャルが下がった分、バイポーラ効果により電流が流れる。(4) で正孔がソースに拡散し、最後に (5) で逃げた正孔と同じ量の電子がドレインに流れる。その後は、ボディに発生した電子、正孔がなくなるまで (3) (4) (5) (3) …と続く。この (4)、(5) の両極性拡散過程が図 3.34 で (Fレイン電子電流とソース電子電流の差分) = (Yース正孔電流) として見えているものと考えられる。

図 3.35: 両極性拡散過程

以上は LET $0.1 {

m pC}/\mu {

m m}$  の話であるが、次に LET が小さいときについて調べる。図 3.36 に LET $0.01 {

m pC}/\mu {

m m}$  のときのドレイン電子電流とソース電子電流の差分を示す。LET $0.01 {

m pC}/\mu {

m m}$  の場合、ボディに発生する電子が少なく、(1) の過程で電子がこぼれてもポテンシャルが十分に下がらないため、最初のピークしか観測されないものと考えられる。

図 3.36: LET $0.01pC/\mu m$  ドレイン電子電流とソース電子電流の差分 (寄生バイポーラ効果以外の成分) 及びソース正孔電流

### 3.4 SET 電流を用いた SET パルス幅の推定

トランジスタ単体の SET 電流から、インバータ回路の SET パルス幅を見積もることを考える。トランジスタ単体の SET 電流は、近年、照射試験によるデータが揃いつつあり [28]、そこから論理回路中のパルス幅を見積もれれば、フィルタ等の回路設計がしやすくなり、有意である。

#### 3.4.1 インバータ回路のモデル化

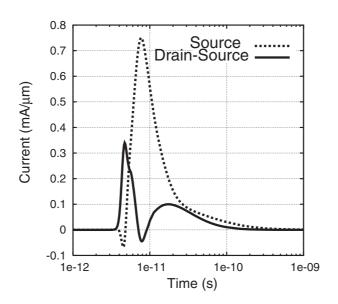

3.3 節の議論から、SET ドレイン電流を時間毎の発生原因に分けることができる。図 3.37 にドレイン電流の構成成分である、ソース電子電流及びドレイン電子電流とソース電子電流の差分を示す。ソース電子電流は寄生バイポーラ効果による電流寄与分であった。ドレイン電子電流とソース電子電流の差分は寄生バイポーラ効果以外の電流寄与分であり、最初のピークは電子のドリフトによるもので、第2のピークは両極性拡散によるものであった。SET 電流は、10ps 以前の電子のドリフト、寄生バイポーラ効果による電流変動の大きい成分と10ps 以降の寄生バイポーラ効果、両極性拡散による電流変動の小さい成分とに分けることができる。この結果を用いて、SET パルスの立上がり時、立下り時におけるインバータ回路のモデル化を考える。

図 3.37: LET $0.1 pC/\mu m$  ソース電子電流 (寄生バイポーラ効果成分) 及びドレイン電子電流とソース電子電流の差分 (寄生バイポーラ効果以外の成分)

SET パルスの立下り時は  $I_D$  の成分は電子のドリフトと寄生バイポーラ効果によるものであり、非常に早く変化する。この場合、図 2.4 の R に流れる電流  $I_R$  が無視できる。実際、図 3.5, 3.7 においては、10ps 以前には  $I_C$  がドレイン電流の支配的成分であることは既に述べた。よって、図 2.4 の回路は図 3.38 のように近似できる。この回路の時定数は NMOS のオン抵抗と C より、7.45ps であり、R を変えても時定数は影響を受けない。したがって、図 3.4 で R が異なる場合でも電圧が降下する傾きが同じになると考えられる。しかし、R が小さいと、R に流れる電流の大きさが無視できなくなり、早い段階でこの近似ができなくなる。図 3.6 では、R=540 においてドレイン電流と R を流れる電流のパルス波形がほぼ一致しており、ドレインで発生した R=540 においてはほかの 2 つの抵抗値より最初の電圧の傾きが緩くなる。また、R=540 においてはほかの R=540 においては同かの R=540 においてのが大きなるので、他の R=540 においてのが大きいほどピークになるまで立下がり時間が遅くなったのは、図 R=540 の R=540 においてのが大きいほどピークになるまで立下がり時間が遅くなったのは、図 R=540 の R=540 においてのが大きいほどピークになるまで立下がり時間が遅くなったのは、図 R=540 の R=540 においていることのである。

図 3.38 では、Vout が 0.5Vdd のときに論理反転が起き、そのときの C の電荷は 0.5CVdd である。

図 3.38:  $I_D$  の変動が大きいときの図 2.4 近似回路

次に、図 3.38 の過程が終わり、R からの回復電流により  $V_D$  が上がっていく立上がり過程を考える。このとき、 $I_D$  の電流成分は寄生バイポーラ効果と両極性拡散から成り、ゆっくり変化するので、C はすぐにチャージアップしてしまう。そのため、図 2.4 の C に流れる電流  $I_C$  は無視できる。実際、図  $3.5,\ 3.7$  において、10ps 以降は  $I_R$  がドレイン電流の支配的成分になっている。よって図 2.4 は図 3.39 のように近似できる。

図 3.39:  $I_D$  の変動が小さい場合の図 2.4 近似回路

この回路の R にかかる電圧は  $V=R\cdot I_D$  である。インバータの論理が反転するのは、R にかかる電圧が  $1/2V_{DD}$  のときだから、

$$1/2V_{DD} = R \cdot I_D$$

$$I_D = V_{DD}/2R$$

よってドレイン電流がこの値のときまで、論理反転が起きる。

R が大きいときは  $I_D$  が小さくなるため、パルスが立上がるまでに時間がかかる。図 3.4 において R が大きいとパルス幅の終点が遅れたのはそのためであると考えられる。また、図 3.8 において、1.38fF と 0.138fF の立上がり時間に C による違いが強く現れなかったのは、回路が図 3.39 のように近似できるため、立上がり時間が C に強く影響されることはないためであると考えられる。

### 3.4.2 パルス幅の推定

通常の回路での R は NMOS のオン抵抗である 5.4k 、C はゲート容量である 1.38fF から大きく外れることはないので、ここでは R=5.4k と C=1.38fF の場合 のみを考える。

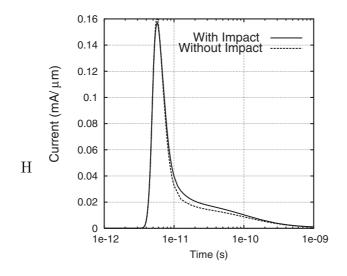

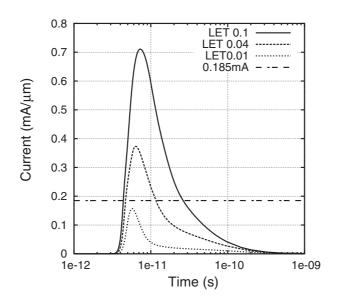

トランジスタ単体の SET 電流を LET0.01, 0.04,  $0.1 \mathrm{pC}/\mu\mathrm{m}$  について図 3.40 に示す。

図 3.40: LET0.01, 0.04, 0.1pC/µm のときのドレイン電流

${

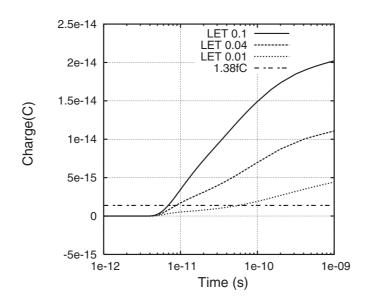

m LET0.01,~0.04,~0.1pC/\mu m}$  についての SET 電流の積分値 (発生電荷) を図 3.40 に 示す。

図 3.41: LET0.01, 0.04, 0.1pC/µm のときの SET 電流の積分値 (発生電荷)

前節においてパルスの立下り時、立上り時のインバータ回路の近似回路を示し、論理反転を起こすときの NMOS を流れる電流、C の電荷を求めた。それらによるとパルスの立下がり時の C(1.38fF) の電荷は 0.5CVdd=1.38fC であり、パルスの立上がり時のドレイン電流は  $IV_{DD}/2R=0.18mA$  (R=5.4k) である。これらを用いて単体トランジスタでの SET 電流から、インバータ回路における SET パルス幅を見積もることができる。

LET $0.1 ext{pC}/\mu ext{m}$  のとき、パルスの立下り時の電荷になる時間を図 3.41 から求めると  $7 ext{ps}$  である (実線と破線の交点の時間)。一方、パルスの立上がり時の電流になる時間を図 3.40 から求めると、 $27 ext{ps}$  時である (実線の遅い成分と破線の交点の時間)。よって、同 LET のときはパルス幅は  $27-7=20 ext{ps}$  であると見積もれる。実際のインバータ回路シミュレーションでのパルス幅は  $30 ext{ps}$  であるので、 $10 ext{ps}$  の差でパルス幅を見積もることができた。

同様にして、LET $0.04 \mathrm{pC}/\mu\mathrm{m}$  のときの SET パルス幅は図 3.40 から  $3\mathrm{ps}$  と見積もられ、LET $0.01 \mathrm{pC}/\mu\mathrm{m}$  のときは論理反転が起きないものと見積もられる。

## 第4章 結論

本論文では、0.2- $\mu$ m 完全空乏型 SOI MOSFET における SET パルスについて、インバータ回路のシミュレーションにより調べた。その結果、インバータの NMOS で発生した SET パルスの幅は、NMOS につながっている素子によって変動することが確認された。SET パルスの立下りの傾きは、PMOS のオン抵抗によらず、NMOS のオン抵抗及び次段のゲート容量で決まっていることがわかった。また、立下り時間は単体トランジスタの SET 電流の積分による電荷と次段のゲート容量から求めることができ、立上り時間は単体トランジスタの SET 電流と PMOS オン抵抗により求められることがわかった。それらを用いて、単体トランジスタの SET 電流から、インバータ回路における SET パルス幅の見積もりを出すことが可能である。近年、単体トランジスタの SET 電流については照射試験のデータが集まりつつあるので、同手法により、実際の論理回路における SET パルス幅が見積もれれば、回路設計上有意である。

また、SET パルスの原因となる SET 電流について、トランジスタ単体のシミュレーションを行うことにより調べた。その結果、SET 電流の立下りの遅い成分において、ドレイン電流がソース電流より大きくなってしまう現象について、従来はその違いがインパクトイオン化により生じているものとされたが、両極性拡散によるものであることがわかった。そして、SET 電流の早い成分は、最初に発生した電子のドリフト及び寄生バイポーラ効果によるもので、遅い成分は、寄生バイポーラ効果と両極性拡散によるものであることがわかった。

# 謝辞

本研究の機会を与えて下さり、指導ご鞭撻を賜った東京大学大学院工学系研究 科電子工学専攻教授、齋藤宏文先生に深甚なる謝意を表します.また,本研究に 関して適切なご指導ご鞭撻を賜った宇宙科学研究本部宇宙探査工学研究系助教授 の廣瀬和之先生、同助手小林大輔氏に深く感謝いたします.さらに,日頃からご 助力頂いた齋藤・水野・坂井研究室の諸氏に心より感謝いたします.

# 参考文献

- [1] 粟屋 伊智郎, "宇宙で見られる機器異常," 第3回放射線安全研究センターシンポジウム.

- [2] P. E. Dodd, M. R. Shaneyfelt, J. A. Felix, and J. R. Schwank, "Production and propagation of single-event transients in high-speed digital logic ICs," *IEEE Trans. Nucl. Sci.*, vol. 51, no. 6, pp. 3278–3284, Dec. 2004.

- [3] J. Benedetto, P. Eaton, K. Avery, D. Mavis, M. Gadlage, T. Turflinger, P. E. Dodd, and G. Vizkelethyd, "Heavy ion-induced digital single-event transients in deep submicron processes," *IEEE Trans. Nucl. Sci*, vol. 51, no. 6, pp. 3480–3485, Dec. 2004.

- [4] S. P. Buchner, and M. P. Baze, "Single-event transients in fast electronic circuits," *IEEE NSREC Short Course*, pp. 1–105, 2001.

- [5] 大西一功,松田純夫, "半導体素子に対する放射線照射効果-最新の研究動向-," 電子情報通信学会誌, vol.85 no.9 pp. 662-669, 2002.

- [6] 廣瀬 和之, 齋藤 宏文, "宇宙用高性能半導体メモリー (SOI-SRAM) の開発," ISAS ニュース, no.261, 2002.

- [7] "宇宙と地球の放射線環境-その未来予測への挑戦-," 月間地球, 海洋出版株式会社, no. 22, pp. 18, 1998

- [8] E. G. Stassinopoulos, and J. P. Raymond, "The space radiation environment for electronics," *Proc. IEEE*, vol. 76, no. 11, pp. 1423-1442, Nov. 1988.

- [9] Srinivasan, G. R., Modeling the Cosmic-Ray-Induced. Soft-Error Rate in Integrated Circuits, An Overview. IBM Journal of Research and Development, Jan. 1996,

- [10] http://www.cosmic.rise.waseda.ac.jp/research/particle/particle\_jp.htm,早稲田大学理工学研究長谷部研究室,高エネルギー宇宙粒子グループ.

- [11] http://www.nasda.go.jp/lib/nasda-news/2003/02/kenkyuu\_ j.html , NASDA NEWS,No.255 2003 FEB.

- [12] K. Oishi, "Issues in space radiation shielding for linarbase", JAERI-Conf95-016 (1995), p.125

- [13] http://www.kek.jp/newskek/2003/sepoct/sparkchamber.html, 高エネルギー加速器 研究機構.

- [14] J. E. Gover, and J. R. Srour, "Basic Radiation Effects in Nuclear Power Electronics Technology", Sandia Laboratory Report, SAND85-0776, 1985.

- [15] A. Holmes-Siedle, and L. Adams, Handbook of Radiation Effects. Now York: Oxford Univ. Press, 1993.

- [16] 関口弘喜, 西島俊二, 平尾敏雄, 梨山勇, "固体中のシングルイベント計測とその応用," 応用物理, 第 65 巻, 第 2 号,pp.126-131,1996

- [17] 大西一功, "放射線による半導体素子の劣化・故障," REAJ 誌, Vol.26 No1, pp.37-45, 2004

- [18] 後川昭雄,大西一功, "耐放射線強化素子研究の現状," 応用物理, Vol.55 No.3 pp.225-233, 1986.

- [19] Koons, H., C., J. E. Mazur, R. S. Selesnick, J. B. Blake, J. F. Fennel, J. L. Roeder, and PC. Anderson, "The Impact of the Space Environment on Space Systems," Engineering an TechnologyGroup, The AerospaceCorp., Report TR-99(1670), El Segundo, CA, 1999.

- [20] 齋藤宏文, "INDEX 衛星プロトタイプモデル開発," 宇宙科学シンポジウム, 2002.

- [21] Yuan Taur, Tak H.Ning, Fundamentals of Modern VLSI Devices, Cambridge Univ. Press, 1998.

- [22] 土屋敏章, SOI CMOS デバイスの基礎と応用, REALIZE INC, pp.16.

- [23] 根元規生, 松崎一浩, 内藤一郎, 阿久津亮夫, "民生部品のシングルイベント耐性に関する評価," 信学技報, 1996.

- [24] K. Hirose, H. Saito, Y. Kuroda, S. Ishii, Y. Fukuoka, and D. Takahashi, "SEU resistance in advanced SOI-SRAMs fabricated by commercial technology using a rad-hard circuit design," *IEEE Trans. Nucl. Sci*, vol. 49, no. 6, pp. 2965–2968, Dec. 2002.

- [25] DESSIS Manual, ISE TCAD Release 10.0, pp. 15.286-15.287.

- [26] 福田保裕, 伊藤秀二, 伊藤眞宏, "SOI-CMOS デバイス技術," 沖テクニカルレビュー, 第 185 号 vol.68 no.1, 2001.

- [27] J. R. Schwank, V. Ferlet- Cavrois, "Radiation Effects in SOI Technologies", *IEEE Trans. Nucl. Sci.*, vol. 50, no. 3, 2003.

- [28] T. Hirao, T. Shibata, J. S. Laird, S. Onoda, Y. Takahashi, K. Ohnishi, and T. Kamiya: "Experimental Study of Single-Event Transient Current in SOI Devices" European conference on Radiation and its effects on components and system, Sept., 2003.