# 博士論文

# **Doctoral Dissertation**

# Exploring Lightweight User-level Threading Frameworks for Massive Fine-Grained Parallelism

(細粒度並列プログラムを効率的に実行する軽量なスレッド処理系)

2019-12-06 提出

東京大学大学院 情報理工学系研究科 電子情報学専攻

Department of Information and Communication Engineering Graduate School of Information Science and Technology The University of Tokyo

岩崎 慎太郎

## Shintaro Iwasaki

学籍番号: 48-177402

指導教員 田浦 健次朗 教授

Advisor Prof. Kenjiro Taura

## Abstract

As the growth of CPU clock speed has been no longer sustained, modern processors adopt a multicore architecture to provide more computing power to users. Since multithreading becomes essential to unleashing the power of modern multicore machines, more and more applications, libraries, and runtime systems are parallelized by threads. The key to achieving high performance on massively parallel processors is keeping all cores busy. Fine-grained multithreading that decomposes a problem into many small pieces of work is considered to be a promising approach to exploiting parallelism in irregular and complex parallel programs. A threading overhead becomes more and more important since it dictates the finest grain size of threads.

Multithreading programming with a traditional *OS-level thread*, however, imposes significant threading overheads, leading to poor scalability of fine-grained and irregular multithreaded programs on highly parallel systems. To overcome the heavyweight nature of OS-level threads, another thread implementation has gained popularity. A *stackless thread* is a lightweight threading method that trims down overheads by removing context switches on fork and join operations. A stackless thread has a few hundred times lower fork-join overheads than an OS-level thread does. However, omitting context switches lacks several scheduling capabilities including suspension and intermediate termination, limiting its programmability.

A *user-level thread* (ULT) is an alternative threading technique that implements a context switch in user space. A ULT is positioned between the two opposite threading techniques; thanks to a lightweight user-level context switch, it is more efficient than an OS-level thread while more capable than a stackless thread. Nonetheless, because of its limited functionality than that of an OS-level thread and its higher threading overhead than that of a stackless thread, parallel unit abstractions in major parallel systems are based on either OS-level threads out of fear of missing capabilities or lightweight stackless threads for performance. This prevailing practice imposes high threading overheads or excessively limits the functionality, making high-performance multithreading unnecessarily challenging.

This dissertation presents that a ULT can be a solid replacement of an OS-level thread and a stackless thread as a means of multithreading. To investigate a highly optimized implementation of ULTs, we design a user-level threading library that accommodate several user-level threading techniques with different trade-offs of performance and functionality. We also develop a ULT-based runtime implementation for OpenMP, which is one of the most popular high-level multithreading programming models. Our OpenMP library demonstrates that mapping lightweight ULTs to OpenMP threads and tasks remarkably enhances the performance of real-world applications without violating the OpenMP standard.

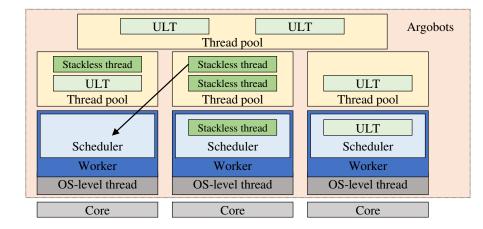

We first show the design of a highly customizable user-level threading library that offers optimization opportunities to knowledgeable developers. Our proposed framework, Argobots, is a highly optimized user-level threading library that balances generality and specialization by providing a low-level interface to define and control the runtime behavior. The default policies and parameters in Argobots are well optimized for generic use, while Argobots provides flexibility to manage memory resources and customize scheduling algorithms via several functions. Argobots exposes three different parallel execution units associated with an OS-level thread, a stackless thread, and a ULT, each of which provides different capabilities so that users can control the concurrency with necessary features.

Minimizing threading overheads is indispensable to exploiting fine-grained parallelism. We perform an in-depth analysis of performance vs. functionality trade-offs of user-level threading techniques. We identify a point during the execution of a thread that triggers a context switch as one of the highest sources of overheads. This point, which we refer to as a *deviation*, disrupts an otherwise low-overhead run-to-completion execution. We conduct a comprehensive investigation of a wide spectrum of userlevel threading methods with respect to how they handle deviations while covering both parent- and child-first scheduling policies.

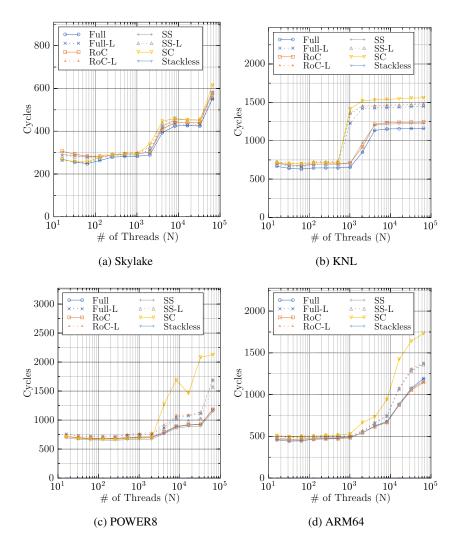

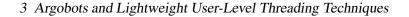

We implement Argobots with these user-level threading techniques and evaluate their performance on various CPU architectures including Intel Skylake, Intel Xeon Phi, IBM POWER8, and 64-bit ARM. Our evaluation involves an instruction- and cache-level analysis of all methods. Our experiments present that threading methods that assume the absence of deviation and dynamically provide context-switching support on deviation offer the best trade-off between performance and functionality when the likelihood of deviation is low.

To showcase that a ULT can be substituted for a thread abstraction in a high-level multithreading programming model, we developed BOLT, a highly optimized ULT-based OpenMP library derived from LLVM OpenMP. BOLT significantly improves performance over existing OpenMP implementations using OS-level threads thanks to lightweight threading operations. We find that such performance improvement is hardly obtained by a simple adaption of lightweight ULTs. Specifically, it is accomplished on three fronts: (1) advanced data reuse and thread synchronization strategies; (2) a novel thread coordination algorithm that adapts to the level of oversubscription; and (3) an implementation of the modern OpenMP thread-to-CPU binding interface tailored to ULT-based runtimes.

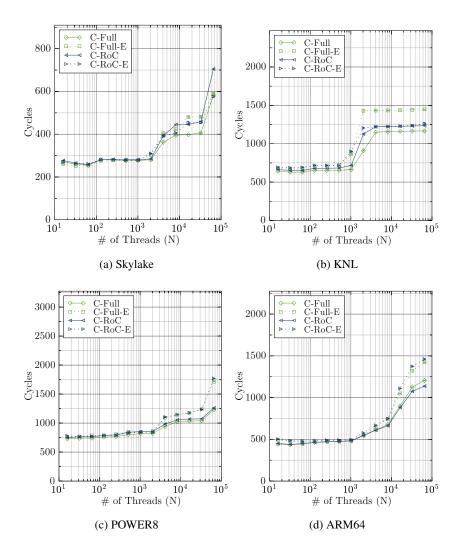

Our evaluation focuses on OpenMP nested parallel regions, which are often unintentionally introduced in real-world applications as a result of independent OpenMP parallelization in multiple software layers. Nested parallel regions have been known to cause the destructive performance with leading OpenMP runtimes because of their reliance on heavyweight OS-level threads. Our BOLT runtime system can successfully exploit such nested parallelism; our experimental results show that BOLT outperforms all existing runtimes under nested parallelism while transparently achieving similar performance compared with leading state-of-the-art OpenMP runtimes under flat parallelism.

These lightweight threading frameworks with our extensions and optimizations are publicly available. Thanks to numerous collaborators and contributors, these libraries are maintained high quality and used by several research and industrial projects. Our developed lightweight threading libraries, Argobots and BOLT, prove that a ULT is a scalable and practical tool for multithreading, which elevates the performance of massive and fine-grained parallel programs in the era of multicore and many-core processors.

## Acknowledgment

This thesis contains texts and experiments in publications I wrote while I was studying at the University of Tokyo and Argonne National Laboratory [1–4]. I would like to thank all the coauthors for helping me form this thesis.

First and foremost, I would like to thank Taura-sensei for his tremendous support for as long as six years at Taura Laboratory. He is undoubtedly one of the most passionate and most knowledgeable advisors I have ever met. As a mentor, a teacher, and an advisor, he taught me all skills, techniques, knowledge, and a mindset to be a good researcher. I would not choose a research career if I would have not met him at the University of Tokyo. He also gave me a precious chance to study at Argonne National Laboratory, where I conducted most of my studies in this dissertation.

At Argonne National Laboratory I could work with fantastic researchers. Abdelhalim Amer was my supervisor in the first two years of my internship at Argonne National Laboratory. We had many research discussions, all of which were extremely valuable to shape this dissertation. His careful and in-depth analysis and truly extraordinary writing skill helped me publish papers. Pavan Balaji is my supervisor for the rest of the years at Argonne National Laboratory. He always amazed me by showing his exceptional research and project management skills. I would like to specially thank him for letting me lead the Argobots and BOLT projects. He gave me countless opportunities to have presentations, seminars, and tutorials. They were held at not only Argonne National Laboratory but also other national laboratories such as Sandia and Oak Ridge National Laboratories and academic conferences including PACT, PPoPP, and SC. All of them are precious experiences for my future research career. I deeply thank Sangmin Seo, who devised the designs of Argobots and BOLT and implemented their initial versions, which became the base of my research.

I could not be happier than having prominent researchers as members of my Ph.D. program committee: Kitsuregawa-sensei, Aizawa-sensei, Nakajima-sensei, Sato-sensei, and Suda-sensei in addition to Pavan Balaji and Taura-sensei. I truly appreciate their constructive and critical feedback, which significantly improved my thesis. Irie-sensei and Toyoda-sensei also deserve many thanks for deep and insightful discussions we had during the advisor meetings, helping me develop my work.

It was my great pleasure to spend time with young brilliant students as friends at Taura Laboratory. I would especially thank Byambajav-kun, Christian-san (Helm-san), Endo-kun, Huynh-san, Ito-kun,

Inoue-san, Nakazawa-kun, Qiao-san, Sato-san, Shiina-kun, Shimazu-san, and Shoetsu-kun (Sato-kun) for great discussions on coding practice, programming languages, paper writing, and latest studies in the high-performance computing field.

I also thank all the colleagues at Argonne National Laboratory for helping my research and offering me invaluable help to stay in the United States. The staff members including Giuseppe Congiu, Rob Latham, Min Si, and Hui Zhou helped me develop and improve the Argobots interoperability layer in MPICH. Yanfei Guo deserves many thanks for driving the ECP SOLLVE project, which was the primary funding source of my internship at Argonne National Laboratory. Many thanks to Ken Raffenetti for setting up CI environments for Argobots and BOLT. They are essential to maintaining and improving the quality of these threading libraries. All of the staff members kindly helped me involve in the MPICH project and contribute to the MPICH implementation. I would also like to thank Gail Pieper for her revising and improving my papers.

I was inspired by many talented and hard-working internship students I have met at Argonne National Laboratory. I would specially thank Seonmyeong Bak, Yanhao Chen, Amal Fethi, Clément Mommessin, Poornima Nookala, Srinivasan Ramesh, Hengjie Wang, and Xi Wang. As a long-term visiting student, I particularly spent a long time with Kaiming Ouyang, Kwang (Sarunya Pumma), Shu-Mei Tseng, and Rohit Zambre. Without them, I could not have spent a fruitful and enjoyable time at Argonne. Special thanks go to Rohit Zambre for teaching me how to survive in the USA from A to Z. I truly appreciate his support.

The ongoing project on MPI+ULT is collaborative work with Qthreads and Open MPI developers at Sandia and Los Alamos National Laboratories. I would like to thank Stephen Olivier, Noah Evans, and Howard Pritchard for discussions on the MPI+ULT interoperability issues. Feedback in the MPI+ULT hackathon at Albuquerque helped me deeply think about this problem.

Last but not least, I would like to thank my family. I would never have gone through my career without their love, support, and encouragement.

This thesis includes work partially supported by the Exascale Computing Project, a collaborative effort of the U.S. Department of Energy Office of Science and the National Nuclear Security Administration, in particular, its subproject on Scaling OpenMP with LLVm for Exascale performance and portability (SOLLVE). I gratefully acknowledge the computing resources provided and operated by the Laboratory Computing Resource Center (LCRC) and the Joint Laboratory for System Evaluation (JLSE) at Argonne National Laboratory. I would like to acknowledge the Doctoral Student Special Incentives Program (IST-RA) of Graduate School of Information Science and Technology, the University of Tokyo, for financial support while I was in Japan.

## Contents

| 1 | Intro | oductio | n                                                                                             | 14 |

|---|-------|---------|-----------------------------------------------------------------------------------------------|----|

|   | 1.1   | Contrib | putions                                                                                       | 17 |

|   | 1.2   | Outline |                                                                                               | 20 |

| 2 | Bac   | kgroun  | d                                                                                             | 21 |

|   | 2.1   | Thread  | Implementations                                                                               | 21 |

|   |       | 2.1.1   | OS-Level Threads                                                                              | 22 |

|   |       | 2.1.2   | Stackless Threads                                                                             | 23 |

|   |       | 2.1.3   | User-Level Threads (ULTs)                                                                     | 25 |

|   | 2.2   | OpenM   | IP for Multithreading                                                                         | 28 |

|   |       | 2.2.1   | Programming Model of OpenMP                                                                   | 29 |

|   |       | 2.2.2   | Implementations of OpenMP                                                                     | 30 |

| 3 | Arg   | obots a | and Lightweight User-Level Threading Techniques                                               | 33 |

|   | 3.1   | Introdu | lection                                                                                       | 33 |

|   | 3.2   | Design  | of Argobots                                                                                   | 34 |

|   |       | 3.2.1   | Argobots Terminology                                                                          | 35 |

|   |       | 3.2.2   | Execution Model of Argobots                                                                   | 36 |

|   |       | 3.2.3   | Towards a Lightweight and Low-Level Threading Framework                                       | 37 |

|   | 3.3   | Perform | nance Comparison Between Stackless Threads and ULTs                                           | 40 |

|   |       | 3.3.1   | Stackless Threads in a User-Level Threading Library                                           | 42 |

|   |       | 3.3.2   | Threads with Full Threading Capabilities                                                      | 43 |

|   |       | 3.3.3   | Parent-First Fully Fledged Threads (Full)                                                     | 44 |

|   |       | 3.3.4   | Child-First Fully Fledged Threads (C-Full)                                                    | 45 |

|   |       | 3.3.5   | Performance Comparison                                                                        | 45 |

|   | 3.4   | Lightw  | reight Parent-First ULTs                                                                      | 49 |

|   |       | 3.4.1   | Removing Context Switch on Completion (RoC)                                                   | 50 |

|   |       | 3.4.2   | Removing Context Switch on Invocation (SS) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 51 |

|   |       | 3.4.3   | Lazy Stack Allocation (Full-L, RoC-L, and SS-L)                                               | 53 |

|   |       |         |                                                                                               |    |

## Contents

|   |     | 3.4.4 Removing Stack Change ( <b>SC</b> )                       |

|---|-----|-----------------------------------------------------------------|

|   | 3.5 | Lightweight Child-First ULTs 56                                 |

|   |     | 3.5.1 Eager Stack Release (C-Full-E)                            |

|   |     | 3.5.2 Removing Context Switch on Completion (C-RoC and C-RoC-E) |

|   | 3.6 | Trade-off of Performance and Functionalities                    |

|   |     | 3.6.1 Coverage of Our Techniques                                |

|   | 3.7 | Evaluation with a Microbenchmark                                |

|   |     | 3.7.1 Performance with Different Deviation Probabilities $(D)$  |

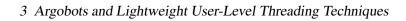

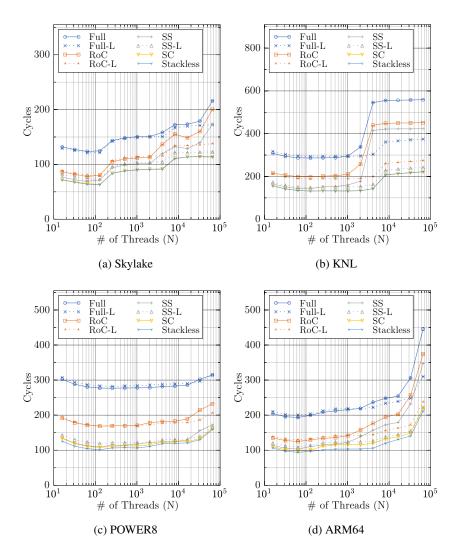

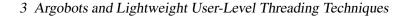

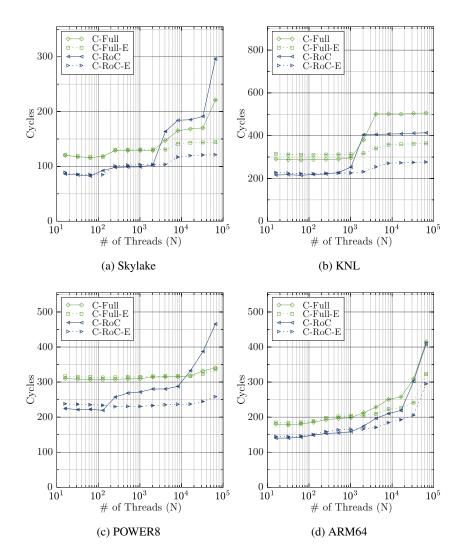

|   |     | 3.7.2 Performance with Different Numbers of Threads $(N)$       |

|   | 3.8 | How to Choose the Best Threading Technique                      |

|   | 3.9 | Summary                                                         |

| 4 | BOI | LT: OpenMP over Argobots 73                                     |

|   | 4.1 | Introduction                                                    |

|   | 4.2 | Fine-Grained Parallelism in Nested Parallel Regions             |

|   |     | 4.2.1 Current State in OS-Level Thread-Based Runtimes           |

|   |     | 4.2.2 Current State in ULT-Based Runtimes                       |

|   | 4.3 | BOLT: Lightweight ULT-Based OpenMP Runtime                      |

|   |     | 4.3.1 Basic Design of BOLT                                      |

|   |     | 4.3.2 Team-Aware Resource Management                            |

|   |     | 4.3.3 Scalability Optimizations                                 |

|   |     | 4.3.4 Thread Coordination Across Successive Parallel Regions    |

|   |     | 4.3.5 Thread-to-Place Binding                                   |

|   |     | 4.3.6 Performance Breakdown and Analysis                        |

|   | 4.4 | Evaluation with Microbenchmarks                                 |

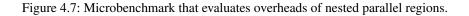

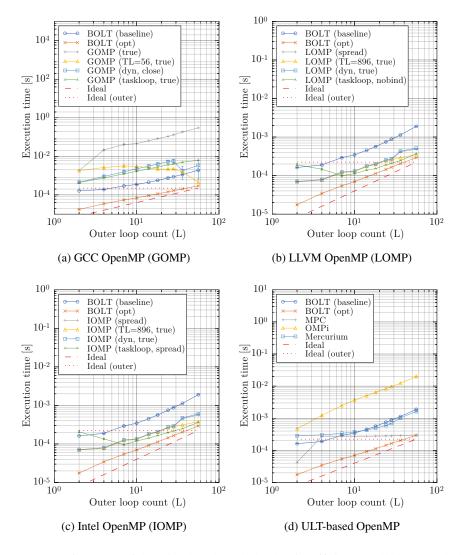

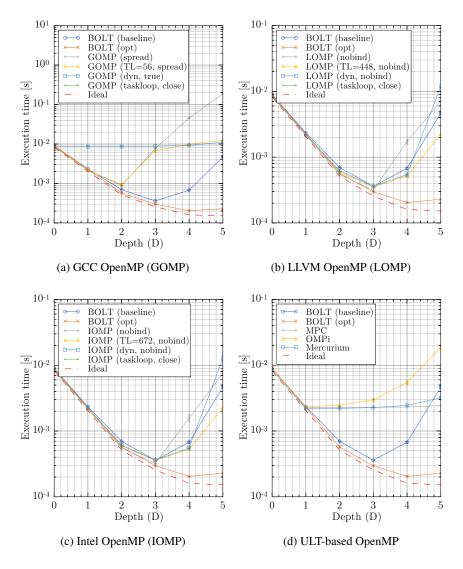

|   |     | 4.4.1 Doubly Nested Loops                                       |

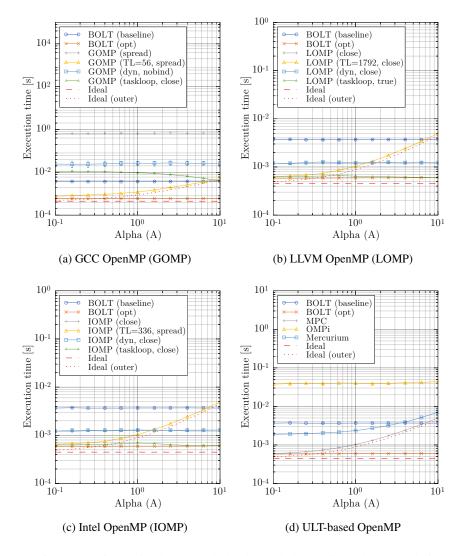

|   |     | 4.4.2 Deeply Nested Loops                                       |

|   | 4.5 | Summary                                                         |

| 5 | App | plication Benchmarks 98                                         |

|   | 5.1 | Evaluation of Lightweight Threading Techniques in Argobots      |

|   |     | 5.1.1 ExaFMM                                                    |

|   |     | 5.1.2 Distributed Graph500                                      |

|   | 5.2 | Evaluation of BOLT                                              |

|   |     | 5.2.1 KIFMM                                                     |

|   |     |                                                                 |

## Contents

|                                     |     | 5.2.2                                                  | 5.2.2 Qbox                                      |       |  |  |  |

|-------------------------------------|-----|--------------------------------------------------------|-------------------------------------------------|-------|--|--|--|

|                                     | 5.3 | Evaluation of Lightweight Threading Techniques in BOLT |                                                 |       |  |  |  |

|                                     |     | 5.3.1                                                  | OpenMP-Parallelized KMeans                      | . 116 |  |  |  |

| 6 Practicality of Argobots and BOLT |     |                                                        |                                                 | 119   |  |  |  |

|                                     | 6.1 | Suitabi                                                | ility of Argobots for Mainstream Use            | . 119 |  |  |  |

|                                     |     | 6.1.1                                                  | Interoperability with OpenMP                    | . 120 |  |  |  |

|                                     |     | 6.1.2                                                  | Interoperability with MPI                       | . 121 |  |  |  |

|                                     |     | 6.1.3                                                  | Summary                                         | . 122 |  |  |  |

|                                     | 6.2 | Suitabi                                                | ility of BOLT for Mainstream Use                | . 122 |  |  |  |

|                                     |     | 6.2.1                                                  | Standard Compliance of BOLT                     | . 122 |  |  |  |

|                                     |     | 6.2.2                                                  | Suggested OpenMP Changes                        | . 123 |  |  |  |

|                                     |     | 6.2.3                                                  | Using BOLT in the Real World                    | . 124 |  |  |  |

| 7 Related Work                      |     |                                                        | ork                                             | 126   |  |  |  |

|                                     | 7.1 | User-L                                                 | evel Threads                                    | . 126 |  |  |  |

|                                     |     | 7.1.1                                                  | Fully Fledged Threads                           | . 127 |  |  |  |

|                                     |     | 7.1.2                                                  | Saving Registers                                | . 127 |  |  |  |

|                                     |     | 7.1.3                                                  | Stack Separation                                | . 127 |  |  |  |

|                                     |     | 7.1.4                                                  | Scheduler Creation                              | . 128 |  |  |  |

|                                     |     | 7.1.5                                                  | Stackless Threads                               | . 128 |  |  |  |

|                                     |     | 7.1.6                                                  | Other Threading Techniques                      | . 128 |  |  |  |

|                                     | 7.2 |                                                        |                                                 |       |  |  |  |

|                                     |     | 7.2.1                                                  | ULTs in OpenMP                                  | . 129 |  |  |  |

|                                     |     | 7.2.2                                                  | ULTs in Parallel Programming Models             | . 130 |  |  |  |

|                                     |     | 7.2.3                                                  | Interoperability with Parallel Libraries        | . 130 |  |  |  |

|                                     |     | 7.2.4                                                  | Mitigating Overheads of Nested Parallel Regions | . 130 |  |  |  |

| 8                                   | Con | clusio                                                 | ns and Future Work                              | 132   |  |  |  |

| 1.1 | Fork-join overheads on an Intel Knights Landing processor using a microbenchmark             |    |  |  |

|-----|----------------------------------------------------------------------------------------------|----|--|--|

|     | presented in Figure 3.9 ( $(N, n) = (256, 0)$ ). This experiment used Pthreads, Argobots [1] |    |  |  |

|     | stackless threads, and Argobots ULTs as implementations of OS-level threads, stackless       |    |  |  |

|     | threads, and ULTs, respectively.                                                             | 16 |  |  |

| 2.1 | Flow of a function call. In reality, compiler optimizations might reorder and eliminate      |    |  |  |

|     | some of these instructions.                                                                  | 23 |  |  |

| 2.2 | Pseudocode of invocation of a stackless thread.                                              | 24 |  |  |

| 2.3 | Pseudo assembly code of user-level context switch.                                           | 26 |  |  |

| 2.4 | Pseudo assembly code to start and finish thread contexts                                     | 26 |  |  |

| 2.5 | Pseudocode of invocation of a ULT (Full in Chapter 3)                                        | 27 |  |  |

| 2.6 | Loop parallelization by the OpenMP's parallel for construct                                  | 29 |  |  |

| 2.7 | Compilation and execution flow of OpenMP programs.                                           | 30 |  |  |

| 2.8 | Pseudo assembly code of loop parallelization by the OpenMP's parallel for construct          |    |  |  |

|     | presented in Figure 2.6. This pseudo code assumes an OpenMP ABI used by LLVM                 |    |  |  |

|     | OpenMP [132]. We note that several internal parameters and implementation details are        |    |  |  |

|     | omitted for the sake of brevity.                                                             | 31 |  |  |

| 3.1 | Execution model of Argobots.                                                                 | 36 |  |  |

| 3.2 | Design of a user-defined scheduler in Argobots.                                              |    |  |  |

| 3.3 | Basic threading API of a user-level threading library and example code with this API.        |    |  |  |

|     | We use this API to discuss implementations of lightweight ULTs                               | 41 |  |  |

| 3.4 | Pseudocode of a stackless thread. Real schedulers might sleep when no ULTs are ready         |    |  |  |

|     | in the pool and have a branch to check a flag in order to terminate a scheduler              | 42 |  |  |

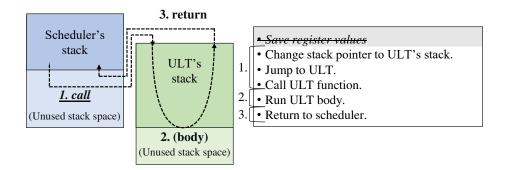

| 3.5 | Flow of fork-join (stackless threads)                                                        | 42 |  |  |

| 3.6 | Pseudocode of Full.                                                                          | 44 |  |  |

| 3.7 | Pseudocode of C-Full.                                                                        | 46 |  |  |

| 3.8 | Flow of fork-join without deviation (Full and C-Full).                                       | 47 |  |  |

|     |                                                                                              |    |  |  |

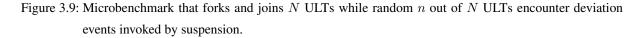

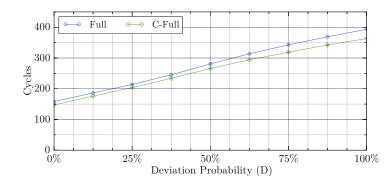

| 3.9  | Microbenchmark that forks and joins $N$ ULTs while random $n$ out of $N$ ULTs encounter              |    |  |  |

|------|------------------------------------------------------------------------------------------------------|----|--|--|

|      | deviation events invoked by suspension                                                               | 48 |  |  |

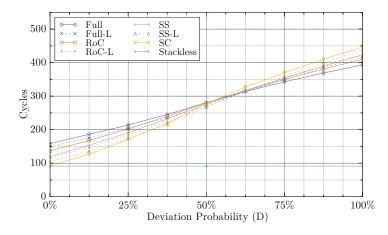

| 3.10 | Fork-join overheads on an Intel Skylake machine using a microbenchmark presented                     |    |  |  |

|      | in Figure 3.9 ( $N = 4,096$ ). Stackless shows the performance at $D = 0\%$ because a                |    |  |  |

|      | stackless thread does not allow any deviation.                                                       | 48 |  |  |

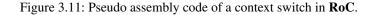

| 3.11 | Pseudo assembly code of a context switch in <b>RoC</b> .                                             | 50 |  |  |

| 3.12 | Flow of RoC when no deviation happens. The difference from Full (Figure 3.8) is                      |    |  |  |

|      | written in italic                                                                                    | 50 |  |  |

| 3.13 | Pseudo assembly code of a context switch in SS.                                                      | 51 |  |  |

| 3.14 | Flow of SS when no deviation happens. The difference from RoC (Figure 3.12) is                       |    |  |  |

|      | written in italic                                                                                    | 52 |  |  |

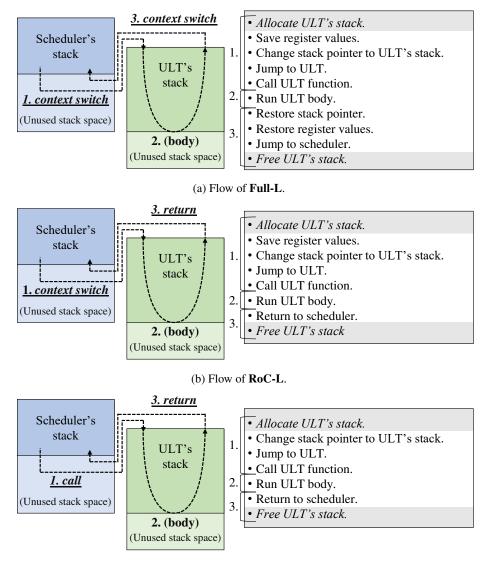

| 3.15 | Flow of threading techniques with lazy stack allocation (Full-L, RoC-L, and SS-L)                    |    |  |  |

|      | when no deviation takes place. The differences from Full (Figure 3.8), RoC (Fig-                     |    |  |  |

|      | ure 3.12), and <b>SS</b> (Figure 3.14) are highlighted by italicizing them                           | 53 |  |  |

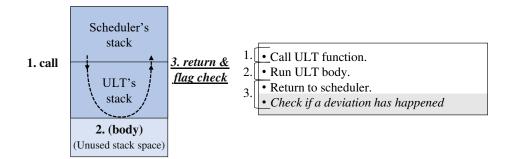

| 3.16 | Flow of <b>SC</b> when no deviation occurs. The difference from <b>SS</b> (Figure 3.14) is written   |    |  |  |

|      | in italic                                                                                            | 54 |  |  |

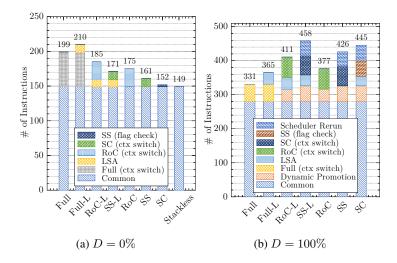

| 3.17 | Instruction breakdown of fork and join operations on Skylake (parent-first methods). We              |    |  |  |

|      | used Intel SDE [103] to obtain series of instructions.                                               | 55 |  |  |

| 3.18 | Fork-join overheads of the parent-first threading methods on Skylake                                 | 55 |  |  |

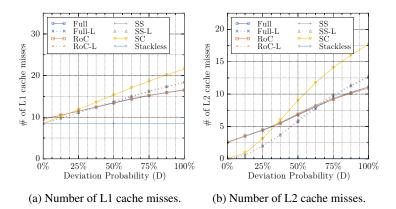

| 3.19 | Cache misses of the parent-first threading methods on Skylake. These values are ob-                  |    |  |  |

|      | tained by PAPI [41]. Almost no L3 cache miss happens in this experiment because each                 |    |  |  |

|      | ULT accesses a small portion of a call stack; we therefore omit the data. $\ldots$ $\ldots$ $\ldots$ | 56 |  |  |

| 3.20 | Flow of <b>C-Full-E</b> without deviation. The difference from <b>C-Full</b> (Figure 3.8) is written |    |  |  |

|      | in italic                                                                                            | 57 |  |  |

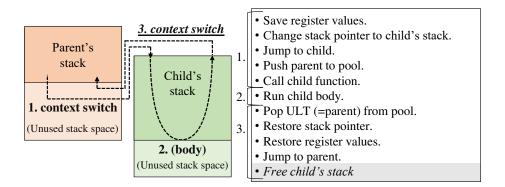

| 3.21 | Pseudo assembly code of context switch in C-RoC                                                      | 58 |  |  |

| 3.22 | Flow of C-RoC when no deviation occurs. We italicize the difference from C-Full                      |    |  |  |

|      | (Figure 3.8)                                                                                         | 58 |  |  |

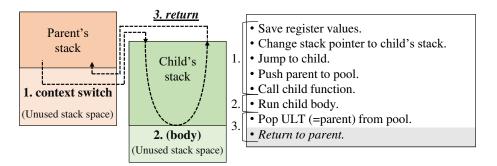

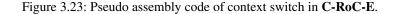

| 3.23 | Pseudo assembly code of context switch in C-RoC-E                                                    | 59 |  |  |

| 3.24 | Flow of C-RoC-E when no deviation happens. The difference from C-RoC (Fig-                           |    |  |  |

|      | ure 3.22) is emphasized by italicizing it                                                            | 59 |  |  |

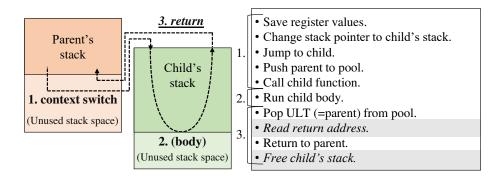

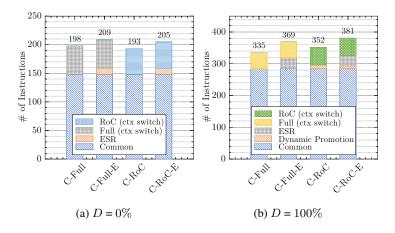

| 3.25 | Instruction breakdown for fork and join of the child-first methods on Skylake. We used               |    |  |  |

|      | Intel SDE [103] to obtain series of instructions.                                                    | 60 |  |  |

| 3.26 | Fork-join overheads of the child-first threading methods on Skylake                                  | 60 |  |  |

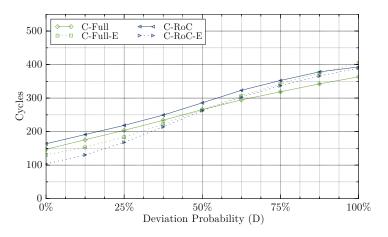

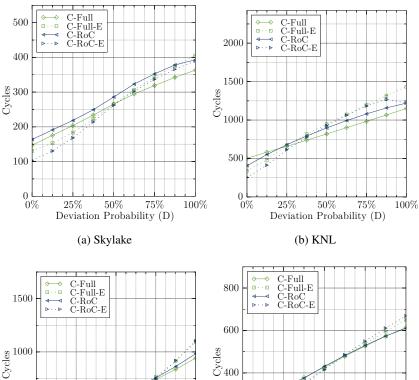

| Performance of the child-first methods on Skylake. Cache misses are obtained by PAPI [41]. |  |  |  |

|--------------------------------------------------------------------------------------------|--|--|--|

| ause each                                                                                  |  |  |  |

| 60                                                                                         |  |  |  |

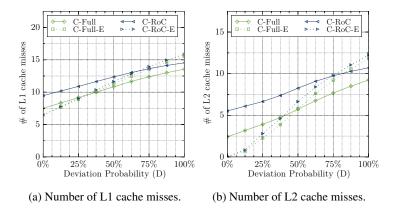

| ues ( $N =$                                                                                |  |  |  |

| 65                                                                                         |  |  |  |

| ues ( $N =$                                                                                |  |  |  |

| 66                                                                                         |  |  |  |

| ling tech-                                                                                 |  |  |  |

| 67                                                                                         |  |  |  |

| ling tech-                                                                                 |  |  |  |

| 68                                                                                         |  |  |  |

| ling tech-                                                                                 |  |  |  |

| 69                                                                                         |  |  |  |

| ling tech-                                                                                 |  |  |  |

| 70                                                                                         |  |  |  |

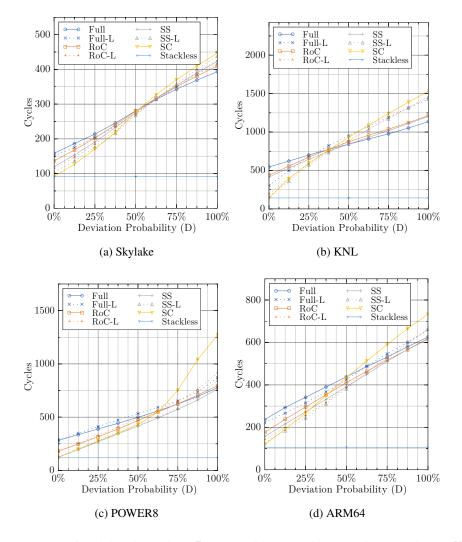

| s 64 (e.g.,                                                                                |  |  |  |

|                                                                                            |  |  |  |

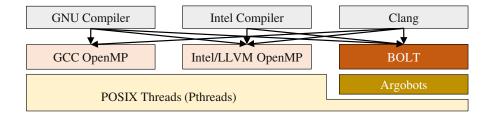

| IP, BOLT                                                                                   |  |  |  |

| ompiler 79                                                                                 |  |  |  |

|                                                                                            |  |  |  |

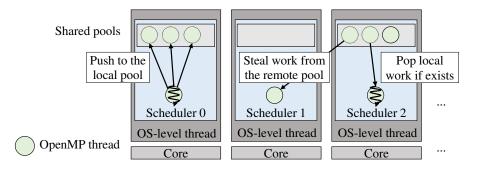

| ocal pool.                                                                                 |  |  |  |

| ling takes                                                                                 |  |  |  |

|                                                                                            |  |  |  |

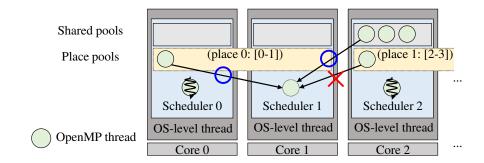

| nagement                                                                                   |  |  |  |

| cessary to                                                                                 |  |  |  |

|                                                                                            |  |  |  |

| own place                                                                                  |  |  |  |

| 87                                                                                         |  |  |  |

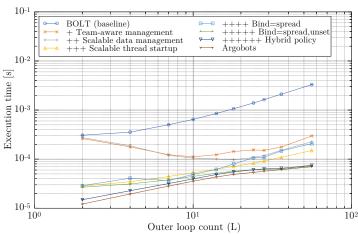

| 88                                                                                         |  |  |  |

| n Skylake 90                                                                               |  |  |  |

| 92                                                                                         |  |  |  |

| ke 93                                                                                      |  |  |  |

| n on Sky-                                                                                  |  |  |  |

| 94                                                                                         |  |  |  |

|                                                                                            |  |  |  |

| 4.12 | Kernels of the microbenchmarks that evaluate deeply nested parallel regions 95                  |  |  |  |

|------|-------------------------------------------------------------------------------------------------|--|--|--|

| 4.13 | <sup>3</sup> Performance of the microbenchmark that has deep nested parallel regions on Skylake |  |  |  |

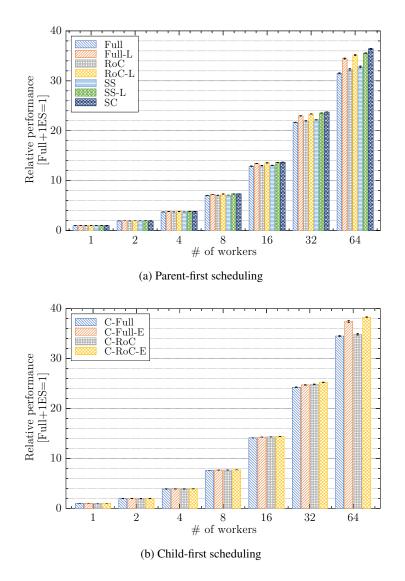

| 5.1  | Relative performance of ExaFMM on KNL. The baseline is the performance of fully                 |  |  |  |

|      | fledged threads (Full and C-Full) with a single worker                                          |  |  |  |

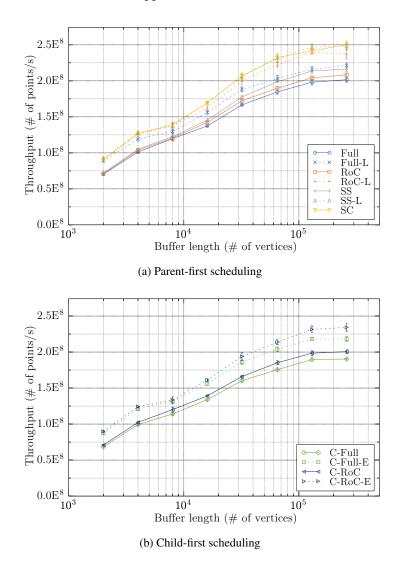

| 5.2  | Traversed edges per second of Graph500 using 1,024 cores                                        |  |  |  |

| 5.3  | Kernel of the upward phase in KIFMM; dgemv() is parallelized with OpenMP's parallel             |  |  |  |

|      | for in MKL                                                                                      |  |  |  |

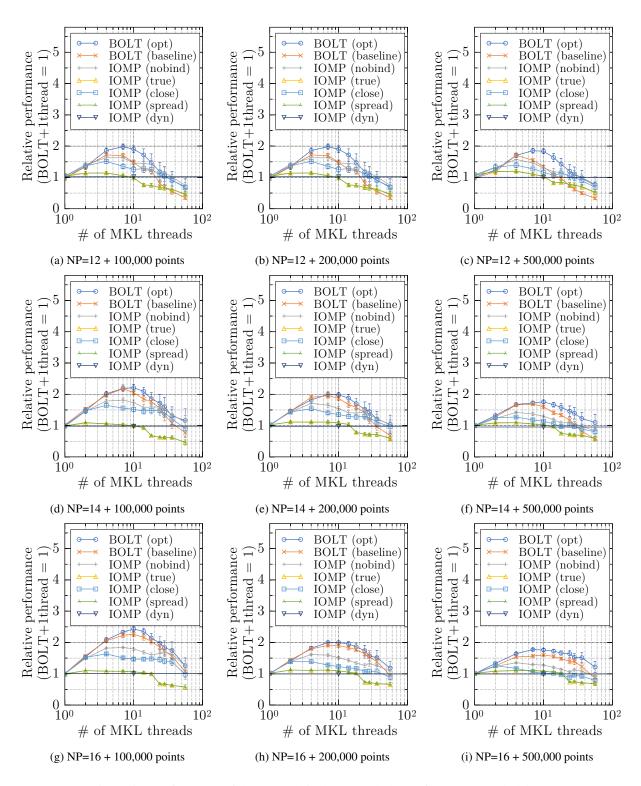

| 5.4  | Performance of the traversal in the upward phase of KIFMM on Skylake                            |  |  |  |

| 5.5  | Kernel of the 3D FFT in Qbox with a 2D FFTW plan                                                |  |  |  |

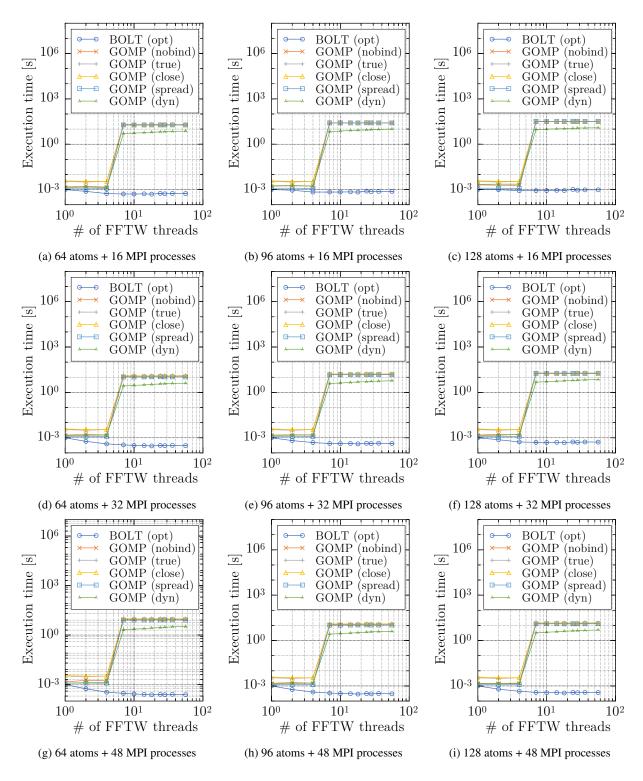

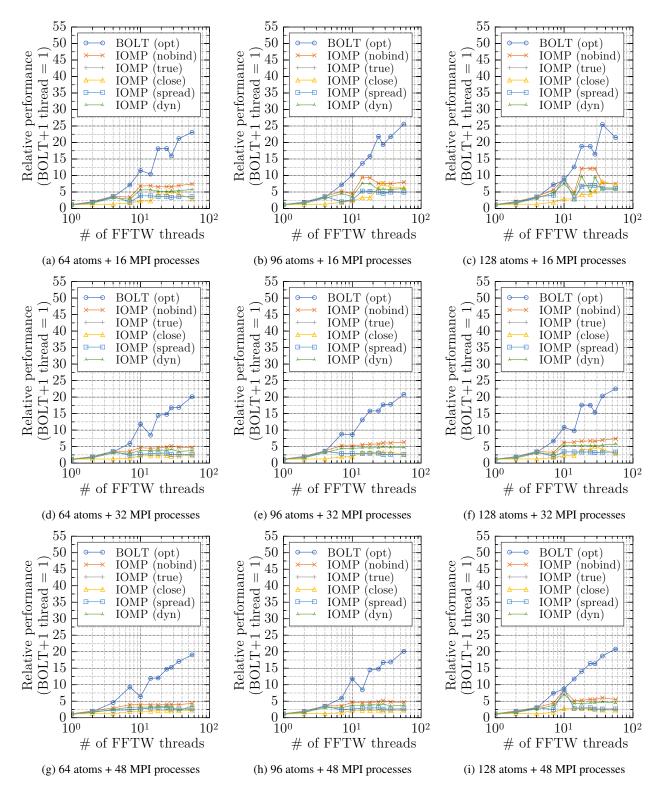

| 5.6  | Performance of the 3D FFT kernel in Qbox with a 2D FFTW plan compiled with GNU                  |  |  |  |

|      | C Compiler                                                                                      |  |  |  |

| 5.7  | Performance of the 3D FFT kernel in Qbox with a 2D FFTW plan compiled with Intel                |  |  |  |

|      | C Compiler                                                                                      |  |  |  |

| 5.8  | Performance of the 3D FFT kernel in Qbox with a 2D FFTW plan compiled with                      |  |  |  |

|      | Clang/LLVM                                                                                      |  |  |  |

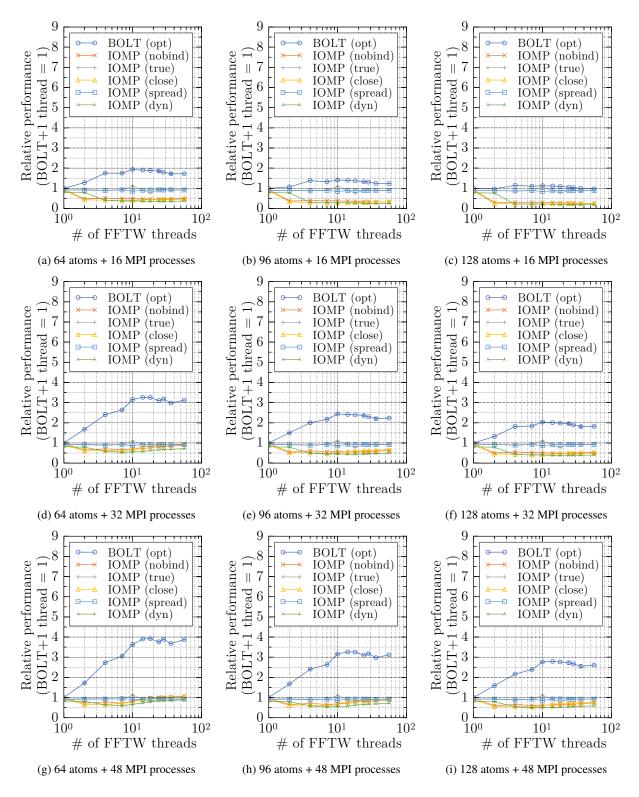

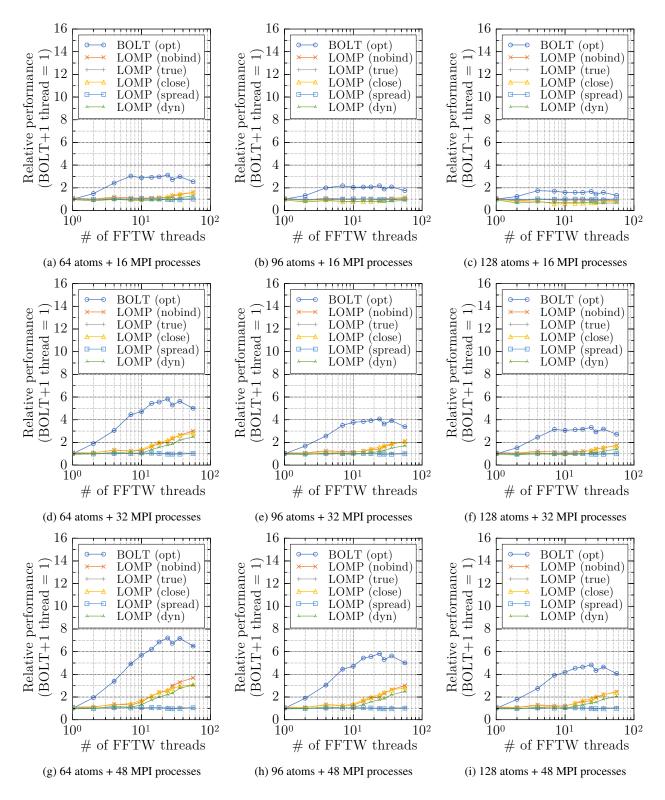

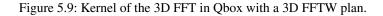

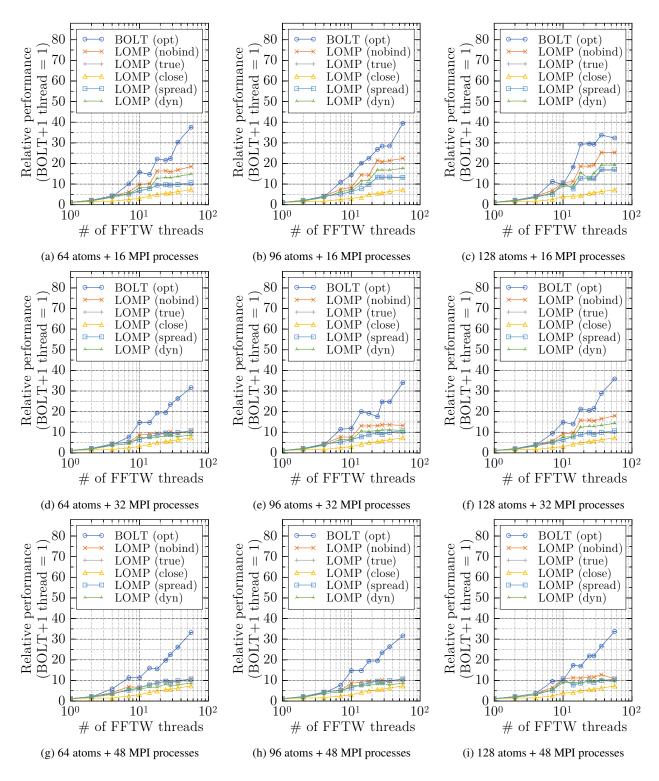

| 5.9  | Kernel of the 3D FFT in Qbox with a 3D FFTW plan                                                |  |  |  |

| 5.10 | Performance of the 3D FFT kernel in Qbox with a 3D FFTW plan compiled with GNU                  |  |  |  |

|      | C Compiler                                                                                      |  |  |  |

| 5.11 | Performance of the 3D FFT kernel in Qbox with a 3D FFTW plan compiled with Intel                |  |  |  |

|      | Compilers                                                                                       |  |  |  |

| 5.12 | Performance of the 3D FFT kernel in Qbox with a 3D FFTW plan compiled with                      |  |  |  |

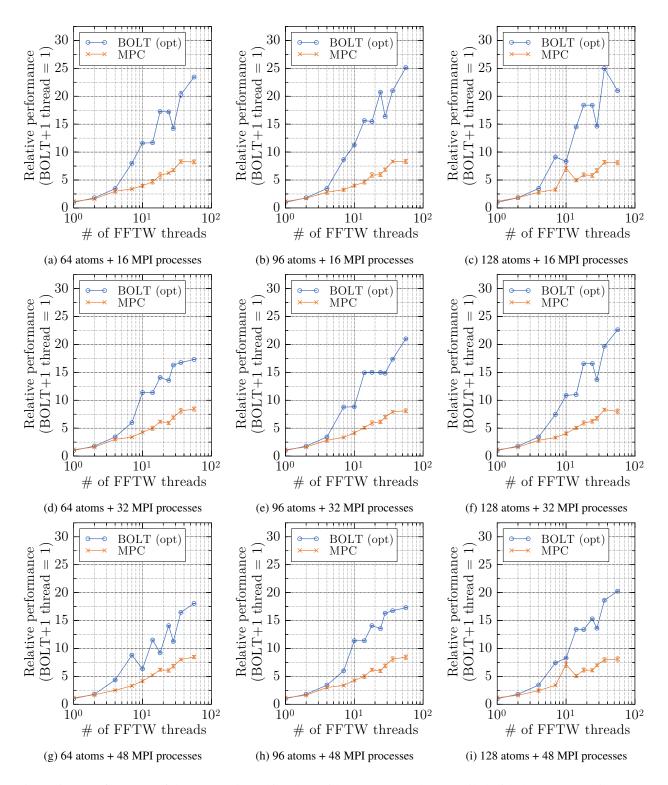

|      | Clang/LLVM                                                                                      |  |  |  |

| 5.13 | Performance of the 3D FFT kernel in Qbox with a 3D FFTW plan compiled with the                  |  |  |  |

|      | MPC compiler. Since MPC 3.3.0 is based on GCC 6.2, we used GCC 6.2 for BOLT for                 |  |  |  |

|      | a fair comparison                                                                               |  |  |  |

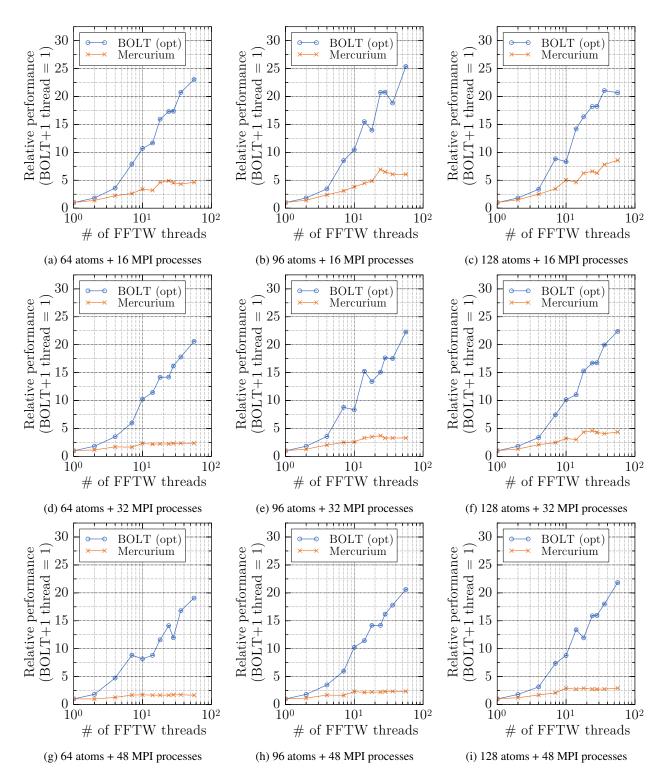

| 5.14 | Performance of the 3D FFT kernel in Qbox with a 3D FFTW plan compiled with the                  |  |  |  |

|      | Mercurium compiler. Since Mercurium used GCC 4.8.5 as a backend compiler, we used               |  |  |  |

|      | the same version of GCC for BOLT for a fair comparison                                          |  |  |  |

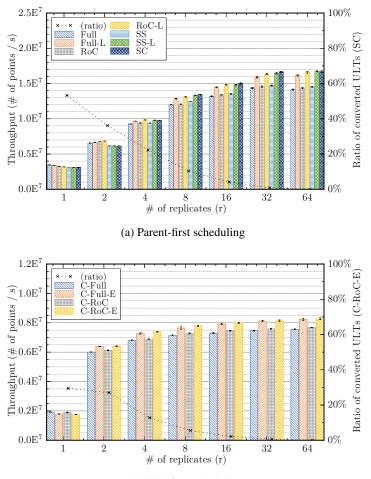

| 5.15 | Throughput of KMeans using 64 cores. The ratio of converted ULTs is calculated by               |  |  |  |

|      | dividing the number of promoted ULTs by the number of created ULTs during execution.            |  |  |  |

|      | We obtain these results with SC for parent-first scheduling and C-RoC-E for child-first         |  |  |  |

|      | scheduling. Other dynamic promotion techniques show similar results                             |  |  |  |

## **List of Tables**

| 1.1 | Difference of functionalities between an OS-level thread, a stackless thread, and a ULT. |  |  |  |  |

|-----|------------------------------------------------------------------------------------------|--|--|--|--|

|     | We assume Pthreads [95], Argobots [1] tasklets, and Argobots ULTs as implementations     |  |  |  |  |

|     | of each type of thread                                                                   |  |  |  |  |

| 3.1 | Summary of the threading techniques                                                      |  |  |  |  |

| 3.2 | Coverage of our analysis                                                                 |  |  |  |  |

| 3.3 | Experimental environments used for the evaluation in Section 3.7                         |  |  |  |  |

| 4.1 | Experimental environment used for microbenchmarks of BOLT                                |  |  |  |  |

| 5.1 | Experimental environment of ExaFMM                                                       |  |  |  |  |

| 5.2 | Experimental environment of Graph500                                                     |  |  |  |  |

| 5.3 | Experimental environment of KIFMM                                                        |  |  |  |  |

| 5.4 | Experimental environment of Qbox                                                         |  |  |  |  |

| 5.5 | Experimental environment of KMeans                                                       |  |  |  |  |

The exponential growth of computing power, which is known as Moore's Law, has driven scientific and social innovation in the world. The twentieth century witnessed this unprecedented growth achieved by shrinking the process of semiconductors, which increased clock speed without enlarging power consumption. Dennard's scaling was over, however, after entering the twenty-first century. Since the exponential growth of the single-core performance has become no longer sustainable, the semiconductor industry instead has increased hardware parallelism to enhance the performance of chips as a whole. Applications must be written to utilize hardware parallelism to truly exploit compute power in such modern highly parallel hardware.

One of the major sources of hardware parallelism is core-level parallelism. Multiple cores that run in parallel are embedded into a single processor. Multithreading is the dominant form of parallelization to execute a single program on multiple cores. In a multithreading programming model, multiple independent sequences of work are packaged as *threads* and distributed to cores so that they can be executed in parallel. Numerous research- and production-level parallel programming systems provide an implementation of threads and have successfully exploited thread-level parallelism in countless applications.

Despite the abundance of potential thread-level parallelism in programs, an overhead in threading operations such as thread creation and destruction (often referred to as fork and join), a yield operation, and synchronization dictates how small granularity of each thread in programs can be. For example, consider that a fork-join overhead is 10 microseconds on a certain processor. To keep the ratio of the parallelization overhead less than 5%, the average execution time of threads needs to be at least larger than 200 microseconds. As the numbers of cores in a single chip and compute nodes in a whole system are increasing, achieving strong scaling—shortening execution time while keeping the problem size—becomes increasingly challenging, which demands more lightweight thread implementation.

Moreover, in a highly parallel environment, dynamic load balancing with fine-grained parallelism becomes critical to achieve efficient utilization of CPUs. Such dynamic load balancing is required for not only irregular parallelism that often appears in recursive divide-and-conquer algorithms and graph algorithms but also apparently regular parallelism that becomes irregular because of nondeterminism of hardware performance. For example, even if each thread computes the same amount of data and thus the computation size looks uniform across threads, several speculative behaviors in modern pro-

| Table 1.1: Difference of functionalities between an OS-level thread, a stackless thread, and a ULT. We assu | ume |

|-------------------------------------------------------------------------------------------------------------|-----|

| Pthreads [95], Argobots [1] tasklets, and Argobots ULTs as implementations of each type of thread           | I.  |

|                                      | OS-level threads | Stackless threads | User-level threads (ULTs) |

|--------------------------------------|------------------|-------------------|---------------------------|

| Fork-join                            | $\checkmark$     | $\checkmark$      | $\checkmark$              |

| Synchronization other than fork-join | $\checkmark$     |                   | $\checkmark$              |

| Suspension                           | $\checkmark$     |                   | $\checkmark$              |

| Intermediate termination             | $\checkmark$     |                   | $\checkmark$              |

| Per-thread signal mask               | $\checkmark$     |                   |                           |

| Non-cooperative preemption           | $\checkmark$     |                   |                           |

cessors including out-of-order execution, branch prediction, hierarchical memory caches, and memory prefetching vary execution time of each thread. To keep all cores busy, fine-grained decomposition of a problem and dynamically balance computational load across cores are known to be effective, rendering lightweight threading more important.

Nonetheless, not all the popular thread implementations are suitable for fine-grained lightweight multithreading. A thread implementation provided by an operating system (OS), which is called an *OS-level thread*, <sup>1</sup> has been the most commonly used implementation of threads. An OS-level thread supports all the threading functionalities that nowadays people naturally expect for "threads": fork and join, suspension, various synchronization, thread-local storage, and non-cooperative preemption. However, an OS-level thread has been criticized because of its heavyweight nature associated with kernel operations.

Another thread implementation has been proposed to minimize the threading cost by simply implementing minimum thread functionalities with a function pointer and its argument. Such a thread does not have its stack and can be invoked by a mere function call. Its stackless implementation, however, lacks several threading capabilities including suspension and several types of synchronizations because it is unable to freely save and resume the execution context during execution. In this work, we refer to this thread implementation as a *stackless thread*<sup>2</sup>.

An OS-level thread and a stackless thread have extremely opposite trade-offs; an OS-level thread is more capable but heavyweight while a stackless thread is lightweight but lacks several threading features. A *user-level thread* (ULT) is a thread implementation positioned between these two threading techniques. Unlike a stackless thread, each ULT manages its call stack so that every thread has an independent execution context, enabling several threading operations including suspension and thread-thread

<sup>&</sup>lt;sup>1</sup>An OS-level thread is sometimes referred to as a kernel thread, or a kernel-level thread. In some literature, it is simply called a POSIX thread (Pthreads [95]) since, in most Linux systems, Pthreads follows a one-to-one mapping between a user thread and a kernel thread.

<sup>&</sup>lt;sup>2</sup>Some literature calls this a run-to-completion thread since such a thread cannot suspend while running. Other studies call this type of thread a task, a microtask, or a tasklet to differentiate it from an OS-level thread.

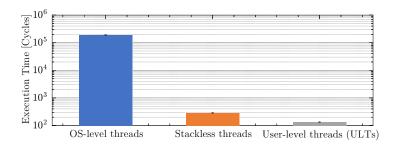

Figure 1.1: Fork-join overheads on an Intel Knights Landing processor using a microbenchmark presented in Figure 3.9 ((N, n) = (256, 0)). This experiment used Pthreads, Argobots [1] stackless threads, and Argobots ULTs as implementations of OS-level threads, stackless threads, and ULTs, respectively.

synchronization. ULTs are more lightweight than OS-level threads because ULT's context switch implemented in the user space (which is often called *user-level contest switch*) does not incur heavyweight kernel operations that are the performance bottlenecks of OS-level threads.

Table 1.1 overviews the difference of functionalities between three thread implementations: an OSlevel thread, a stackless thread, and a ULT. The table shows that an OS-level thread provides the widest variety of threading functionalities while a stackless thread only supports a basic fork-join operation. A ULT supports more threading operations than a stackless thread but fewer than an OS-level thread because some features require the involvement of an OS kernel.

A stackless thread, in contrast, achieves the best fork-join performance among three thread types. Figure 1.1 presents the fork-join overheads of three thread types on Intel Knights Landing 7210<sup>3</sup>. No-tably, OS-level threads incur more than 600 times larger fork-join overheads compared with stackless threads. ULTs are not as slow as OS-level threads, although they have 2.2x larger overheads than stackless threads because of the cost associated with user-level context switching and stack manipulations.

Such an opposite trade-off of performance and functionalities leads the community to settle on a black-and-white perspective. Nowadays, major multithreading systems avoid using ULTs because of its limited threading features than those of OS-level threads or its higher threading cost than that of stack-less threads. For example, thread implementations natively supported by major compilers such as C++ standard threads [104] and OpenMP multithreading extensions [102, 126, 132] map their "threads" to OS-level threads for their rich threading capabilities. On the other hand, numerous lightweight multithreading frameworks including Intel Thread Building Blocks (Intel TBB) [143] and OpenMP tasks [102, 126, 132] adopt a lightweight stackless thread for performance. This prevailing standpoint of the runtime developers often imposes excessive threading overheads when underlying thread implementations are OS-level threads, or unnecessarily limits the threading functionalities when runtimes

<sup>&</sup>lt;sup>3</sup>We used a microbenchmark shown in Figure 3.9 while setting n and N to 0 and 256. In Section 3.7 we explain the detailed experimental environment.

employ stackless threads, making the high-performance multithreading unnecessarily challenging from the viewpoint of performance or functionalities.

This thesis argues that a ULT is placed at the best position in this trade-off relationship and can be a solid replacement of an OS-level thread and a stackless thread as a means of high-performance multithreading. This work makes the following statements:

- 1. A ULT can be as efficient as a stackless thread. With proper designs and implementations, the threading overhead of ULTs can be as low as that of stackless threads without losing critical threading capabilities (Chapter 3).

- 2. A ULT can be a substitute for an OS-level thread as a thread abstraction in parallel programming languages. A ULT can be used for a thread abstraction in one of the most popular multithread-ing programming models, OpenMP [129]. Such a replacement significantly reduces threading overheads thanks to lightweight threading operations (Chapter 4).

We first show a highly optimized user-level threading library, Argobots [1], and describe numerous thread implementations in Argobots that have different trade-offs between performance and functionalities, proving that some user-level threading techniques have low threading overheads close to that of a stackless thread [2]. Next, we present our highly optimized OpenMP implementation over Argobots, BOLT [3]. BOLT shows that replacing OS-level threads with ULTs in an OpenMP threading layer can significantly improve the performance of fine-grained parallel programs without breaking the OpenMP specification. These artifacts demonstrate that a ULT is a scalable thread implementation with rich threading capabilities and suitable for multithreading in the era of multicore and many-core processors.

## **1.1 Contributions**

The primary contributions of this dissertation are twofold. First, a highly optimized user-level threading library with numerous lightweight user-level threading methods, some of which are as fast as a stackless thread. Second, design and implementation of a practical and scalable ULT-based OpenMP library. We develop both libraries with in-depth performance analysis and confirm the performance improvement by evaluating them with several applications. Specifically, our detailed contributions are as follows.

## Lightweight User-Level Threading Library

1. We first show design and implementation of a highly optimized user-level threading library, Argobots [1]. Argobots exposes a low-level interface to control scheduling and synchronization

methods so that application and runtime developers can keenly optimize programs running on top of Argobots.

- 2. We analyze the difference of performance and functionalities between two thread types in Argobots: a ULT and a stackless thread. Our highly optimized implementations of a ULT and a stackless thread reveal that a deviation [151, 152] is the fundamental cause of context switching and thus the associated fork-join cost when implementing ULTs.

- 3. We explore the full spectrum of threading techniques with an in-depth analysis at the instruction and cache levels. We characterize performance vs. functionalities trade-offs of these threading techniques regarding the probability of deviation while covering all feasible methods for building a generic threading library, including a few methods missing from the past literature.

- 4. Our detailed analysis demonstrates that some of our threading techniques have as low fork-join overheads as that of stackless threads. This result poses a question to the prevailing use of stackless threads for performance at the cost of several threading features that are useful to write parallel programs with ease.

- 5. We provide highly optimized implementations of all the methods within the same threading library for a fair comparison of all the threading techniques. Our implementation covers major hardware architectures in the high-performance computing community—Intel Skylake, Intel Knights Landing, ARM 64, and IBM POWER8 processors—and highlights the importance of lightweight user-level threading techniques for architectures that employ less powerful cores and have larger thread contexts.

- 6. We discuss Argobots from aspects of software maturity and composability. Thanks to its customizability, Argobots can be easily adopted by other runtime systems and libraries such as OpenMP [129] (i.e., BOLT) and MPI [121]. Argobots is used in several research and production runtimes, which enables these software components to interoperate via the Argobots interface.

## **ULT-based OpenMP Library**

We present that a ULT is suitable for thread implementation of multithreading programming models that traditionally use OS-level threads. Specifically, we target one of the most popular multithreading programming models in high-performance computing, OpenMP [130]. We describe the detailed design of a ULT-based OpenMP library, called BOLT, which integrates ULTs into LLVM OpenMP [132] without violating the OpenMP specification.

- 2. We showcase that naive use of lightweight ULTs by replacing call sites of OS-level threads in a runtime system originally designed for OS-level threads cannot fully exploit lightweight ULTs. In particular, our performance analysis finds several performance barriers of an OpenMP parallel region, which is the most popular parallelization method in OpenMP.

- 3. We focus on nested OpenMP parallel regions in LLVM OpenMP and devise several solutions to address the scalability issue: 1) several optimizations to remove bottlenecks in LLVM OpenMP (e.g., thread resource management and thread creation algorithms) which are negligible in the original LLVM OpenMP implementation relying on heavyweight OS-level threads, 2) an algorithm to implement OpenMP's thread-to-CPU binding interface tailored specifically to ULT-based runtimes, and 3) a novel thread coordination algorithm that transparently achieves high performance for both flat and nested parallelism, which is required by an OpenMP multithreading model since OpenMP is used for both coarse- and fine-grained parallelism.

- 4. Our evaluation with several microbenchmarks demonstrates that BOLT significantly outperforms existing OpenMP runtimes when parallel regions are nested without hurting performance under flat parallelism.

- 5. We assess the practicality of BOLT for mainstream use. Thanks to LLVM OpenMP, BOLT works with existing OpenMP-parallelized applications and libraries compiled with GCC, LLVM, and Intel OpenMP compilers without recompilation, which significantly improves practicality. We also discuss limitations in using ULTs for OpenMP threads that stem from the fact that 1) some well-known computational libraries assume an OS-level thread as an OpenMP thread and 2) the specification has been designed primarily for OS-level threads-based OpenMP runtimes.

## **Evaluation with Applications**

- We evaluate all the user-level threading methods in Argobots with highly optimized FMM implementation and distributed graph analytics code. We argue that ULTs in applications that require low fork-join overheads incur fewer deviations. Our evaluation indicates that, in such applications, user-level threading techniques that defer context management until a deviation happens show the best performance vs. functionality trade-off.

- 2. We evaluate BOLT with OpenMP-parallelized N-body and quantum chemistry code which have parallel regions unintentionally nested in multiple OpenMP-parallelized software layers. Our experiments show that our ULT-based lightweight OpenMP runtime, BOLT, can exploit such nested parallelism efficiently compared with existing OS-level thread-based and ULT-based OpenMP runtimes.

3. Our experiments evaluate the effect of choosing optimal user-level threading methods in BOLT. Our evaluation with KMeans code shows that adopting the optimal ULT type in the underlying Argobots layer enhances the performance of fine-grained multitasking of OpenMP when the deviation probability is low.

## 1.2 Outline

The organization of this thesis is as follows. In Chapter 2 we first describe the background of three types of thread implementation and then explain OpenMP as one of the most widely used multithreading programming models. Chapter 3 discusses the design and implementation of Argobots and explores the various lightweight user-level threading techniques implemented in Argobots with in-depth analysis from the viewpoints of performance and functionalities of threads. Chapter 4 presents the design and implementation of BOLT, an OpenMP library over Argobots. In Chapter 5 we evaluate the performance of Argobots and BOLT with several applications. Chapter 6 discusses the practicality of our proposed frameworks. Chapter 7 covers the related work and Chapter 8 gives conclusions of this thesis.

This chapter overviews the background knowledge about lightweight threading frameworks. The first section describes three major thread implementations–OS-level threads, stackless threads, and ULTs– and looks into the difference of threading features and associated overheads between these three techniques. The next section explains one of the most widely used multithreading programming models, OpenMP [130], and its representative implementations.

## 2.1 Thread Implementations

Modern compute resources expose several levels of parallelism: for example, parallelism in a single instruction (e.g., SIMD instructions), parallelism across multiple instructions (e.g., out-of-order execution and pipelining), core-level parallelism (e.g., multicore execution), and node-level parallelism (e.g., distributed computing). Multithreading is referred to as a means to exploit core-level parallelism by running *threads* in parallel on multiple cores. In comparison to multiprocessing (e.g., MPI [121], which runs *processes* that have isolated virtual memory spaces<sup>1</sup> in parallel), most *thread* implementations by default share the memory space among threads.<sup>2</sup> In multithreading, therefore, all data are visible to every thread without explicit memory read and write operations although correct multithreaded execution often requires explicit memory synchronizations such as a memory barrier and atomic operations. In this work, we define a thread as a schedulable work unit that executes a sequence of work in a shared memory environment. We note that we use the term *thread* instead of *task*, which is also a widely used term to refer to such a parallel work unit; literature on a *parallel programming model* tends to refer to such a lightweight parallel unit as a *task*, while their *underlying implementations* are often discussed as *threads*.

Since multithreading is a dominant form to exploit core-level parallelism, there exist several thread implementations that have different characteristics in terms of performance and capabilities. In this section, we overview three representative implementations of threads and discuss their performance and functionalities.

<sup>&</sup>lt;sup>1</sup>Some process implementations share memory space [89].

<sup>&</sup>lt;sup>2</sup>Some thread implementations do not transparently share memory and require explicit operations [14].

## 2.1.1 OS-Level Threads

OS-level threads are thread implementations that are provided by and integrated into OS. The most notable implementation is POSIX threads (Pthreads), which implements threads specified in the POSIX standard [95]. Although the POSIX specification defines only an interface and functionalities of threads, threads in most Pthreads packages are mapped to kernel threads managed by OS. Solaris threads [154] and Windows threads are other examples of OS-level threads. In the following, we assume Pthreads as an OS-level thread.

OS-level threads provide the widest range of functionalities. In addition to the most basic fork and join operations (pthreads\_create() and pthreads\_join()), most OS-level thread implementations support several synchronization objects such as a barrier (pthreads\_barrier\_t), a spinlock (pthreads\_spinlock\_t), a mutex (pthreads\_mutex\_t), and a condition variable (pthreads\_cond\_t). A yield operation (pthreads\_yield()) and an intermediate termination operation (pthreads\_exit()) provide scheduling flexibility. Furthermore, OS-level threads support thread-local storage (TLS, which is supported by pthread\_specific\_t), thread-core binding (cpu\_set\_t), and per-thread signal masks (signal\_set()). One of the unique functionalities of OS-level threads is non-cooperative preemption, which interrupts the currently running thread by a kernel timer, saves its execution context, and schedules other threads for fair scheduling. Because an OS-level thread is integrated into a kernel and thus considered as a first-level thread implementation, major compilers assume OS-level threads as "threads" by default. These compilers provide an efficient implementation of TLS accesses, which can be optimized by compilers. For example, most C++ compilers support TLS for OS-level threads by default as std::thread introduced in C++11 [104].

OS-level threads, however, suffer from high threading overheads incurred by kernel involvement. Because schedulers of OS-level threads are integrated into OS, any scheduling operation requires heavyweight system calls, which contributes to the enormous overheads of OS-level threads. For example, on an Intel Skylake machine, system calls to change the CPU affinity or update the register pointing to TLS cost more than a few hundred cycles. Another heavy operation associated with scheduling is context switching, which exchanges a stack and saves and restores register states. Context switching requires stack changes and pollutes caches. These overheads inflate the fork-join cost of OS-level threads, inhibiting scalability under fine-grained multithreading. Such a heavyweight but fully capable thread implementation is sufficient for coarse-grained multithreading, whereas more lightweight threads are indispensable to fine-grained multithreading.

## 2.1.2 Stackless Threads

A stackless thread is regarded as an implementation of a lightweight thread that is suitable for finegrained parallelism. A stackless thread achieves least fork-join overheads by eliminating extra resource management and associated cost that is necessary for threading capabilities other than fork and join operations, both of which are considered to be the minimum requirements for threads. As the essence of threads is a schedulable function that can be detached from the current execution context and later invoked, understanding a mechanism of function calls is important to know fundamental overheads of fork and join operations. We first briefly overview how a function is called.

```

1

void callee(void *arg) {

2

// prologue.

3

[grow stack];

4

[save callee-saved registers];

5

// function body.

6

. . .

7

// epilogue.

8

[restore callee-saved registers];

9

[restore a stack pointer];

10

[pop the parent instruction address];

11

// return to a caller.

[jump to the original instruction address];

12

13

}

14

void caller(...) {

15

. . .

[save caller-saved registers];

16

17

[set an argument in a register/stack];

18

[push the current instruction address];

19

[set a stack pointer];

20

jump callee;

21

[restore caller-saved registers];

22

23

}

```

Figure 2.1: Flow of a function call. In reality, compiler optimizations might reorder and eliminate some of these instructions.

A function call can be executed only in sequential order, but it is the simplest way to perform a unit of work. Figure 2.1 roughly presents an assembly-level flow of a function call. In the following discussion, we use a void(\*)(void\*) function, whereby arguments can be packed and passed via a void pointer and return values can be stored in one of the arguments. Values stored in caller-saved registers are not kept after a function call, so a caller function needs to saves these values in callee-saved registers or stack if necessary (line 16). The first argument is assigned to a predetermined place, usually a specific register. After saving an instruction address and updating a stack register to point to the top of the stack,

the control jumps to a target function. The callee grows a stack by updating a stack pointer. The callee is responsible for keeping values in callee-saved registers before and after the function. In this case, a callee saves and restores callee-saved registers that are modified in the function body at lines 4 and 8. After running its body, it loads a parent stack pointer and returns to a callee using the parent instruction address. The caller restores the evicted values originally in the caller-saved registers as needed at line 21 and resumes.

A standard function call is lightweight, but its execution order is predetermined because the call site is embedded in a program. Threads need a mechanism to delay and synchronize execution. In addition to overheads of function call, minimal additional operations to implement threads are twofold: (1) a thread descriptor that stores completion status, a function pointer, and its argument and (2) a scheduling mechanism that keeps thread descriptors and runs a ready ULT, both of which are fundamental for detaching and deferring the execution of the function. The simplest and most lightweight threading method satisfies only these requirements. This technique, however, abandons all threading features that require context switching. Since this thread does not have its own stack, we call it a stackless thread. We first present the implementation of a stackless thread and describe why it does not allow context switching during execution.

```

struct thd desc t {

1

2

void (*f)(void *arg);

3

void *arg;

4

int state;

5

. . .

6

};

7

void schedule_stackless(thd_desc_t *thd) {

thd->state = STARTED;

8

9

thd->f(thd->arg);

thd->state = COMPLETED;

10

11

}

```

Figure 2.2: Pseudocode of invocation of a stackless thread.

We present an algorithm to invoke a stackless thread in Figure 2.2. A stackless thread requires only a thread descriptor that stores thread information and scheduling mechanism that is necessary to choose and invoke a stackless thread. On thread creation, a thread descriptor that holds a function pointer and its argument is allocated. A stackless thread can be invoked by simply *calling* it on top of the stack of the current thread. Compared with an immediate function call natively supported by programming languages, a stackless thread incurs overheads of thread descriptor management and scheduling mechanism, both of which are indispensable costs to detach the execution. A stackless thread has the least fork-join overheads and thus is used in several implementations such as Filaments [116] and Intel TBB [143]. A

stackless thread, however, lacks threading capabilities that require context switching because an invoked child function is called on top of a parent invoking thread and thus we cannot resume the parent thread until the child thread is completed. Consider a yield operation that returns control from a currently running stackless thread to an invoker. To restore the context of the invoking thread, values of hardware registers (including a stack pointer and an instruction address) must be reinstated. Nevertheless, the stackless thread saves none of them explicitly on invocation; thus, a threading library cannot retrieve these values although they are possibly stored somewhere in the call stack of the stackless thread as instructed by a compiler. Even if registers could be restored, because both the child and the parent threads share the same stack region, any stack growth such as a function call and an allocation of new variables in a stackless thread of threading features that require an independent invoker's context. This limitation is the largest drawback of a stackless thread.

## 2.1.3 User-Level Threads (ULTs)

A stackless thread lacks the context-switching capability because it bonds contexts of a parent thread and a child thread together. If their contexts are maintained independently, however, an invoked thread can return to schedulers at any point. A user-level thread (ULT) creates and maintains a thread context in order to support various threading capabilities that allow efficient scheduling. However, a ULT suffers from context management overheads. In implementing ULTs, lightweight context switching plays an important role to address the issue of context welding between an invoker and an invoked thread. Hence, we first explain a lightweight context-switching implementation entirely performed in the user space, which is often referred to as user-level context switch. Our implementation of user-level context switch follows that of Boost C++ Libraries [35]; similar codes are found in major threading packages, for example, in Qthreads [173], Nanos++ [120], Converse [108], and MassiveThreads [124] as well as Argobots [1].

Figure 2.3 presents the pseudocode of user-level context switch. This implementation represents a context as a single pointer to the call stack (ctx\_t\* in the figure) since all the other data are saved at the top of the stack. Since a caller of switch\_ctx() is responsible for saving and restoring *caller-saved* registers before and after calling switch\_ctx(), switch\_ctx() itself needs to manage only *callee-saved* registers (lines 3 and 9). We note that threading libraries must save and restore all callee-saved registers specified by application binary interfaces (ABIs) because, without a special compiler help, libraries are unable to obtain information about which callee-saved registers are read after calling switch\_ctx(). This routine first saves all the callee-saved registers including an instruction address on top of the stack (lines 3 and 4) and stores the current stack pointer in self\_ctx (line 5). Then, switch\_ctx() updates the stack

```

void switch_ctx(ctx_t **self_ctx, ctx_t *target_ctx) {

1

2

// save the current context.

3

[push callee-saved registers];

4

[push the parent instruction address];

5

*self_ctx = stack_pointer;

6

// restore the target context.

7

stack_pointer = target_ctx;

8

[pop the target instruction address to regA]; // regA is caller-saved.

9

[pop callee-saved registers];

10

// jump to the target context.

11

jump *regA;

12

}

```

Figure 2.3: Pseudo assembly code of user-level context switch.

```

void start_ctx(ctx_t **self_ctx, void *stack, void (*f)(void *), void *arg) {

1

2

// save the current context.

3

[push callee-saved registers];

4

[push the parent instruction address];

5

*self_ctx = stack_pointer;

6

stack_pointer = stack; // start f on top of stack.

// call the target function.

7

8

f(arg);

9

}

void end_ctx(ctx_t *target_ctx) {

10

11

// restore the target context.

12

stack_pointer = target_ctx;

[pop the target instruction address to regA]; // regA is caller-saved.

13

14

[pop callee-saved registers];

15

// jump to the target context.

16

jump *regA;

17

}

```

Figure 2.4: Pseudo assembly code to start and finish thread contexts.

pointer to the stack address pointed to by target\_ctx (line 7) and restores the instruction address and the callee-saved register values from the stack of the target in reverse order (lines 8 and 9). The target, which is suspended in switch\_ctx(), is resumed by jumping to the target instruction address (line 11). We note that all of these operations are executed in the user space.

If a scheduler's context has been saved properly, switch\_ctx() enables a ULT to save its context and resume a scheduler whenever it needs to return to a scheduler. This method, however, is inappropriate for initiating a ULT because switch\_ctx() takes target\_ctx that must have been already initialized. This routine always saves the context of the current ULT, but this action is unnecessary when a ULT finishes because that ULT will never be resumed again. To efficiently handle these cases, we split the functionality of switch\_ctx() and create two methods, start\_ctx() and end\_ctx(), to start and finish

contexts, respectively. Figure 2.4 shows the pseudocodes of these functions. Their implementations come from the first and the latter parts of  $switch_ctx()$ .  $start_ctx()$  saves the context of the current thread (lines 3–5) but freshly executes a function f() on top of stack (lines 6 and 8), while  $end_ctx()$  restores and resumes the target context (lines 12–14, 16) without saving the current context.

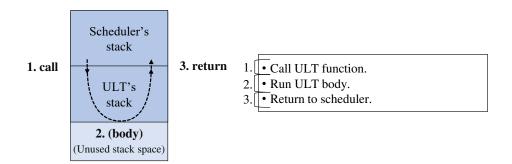

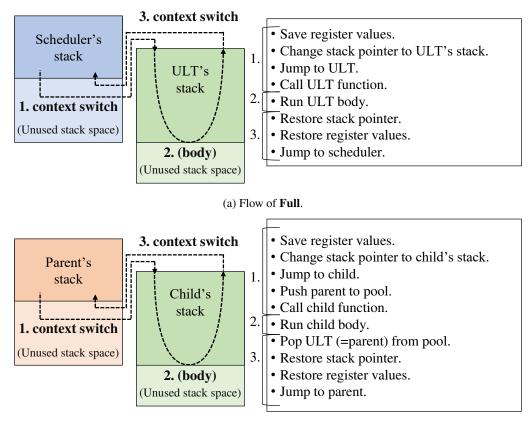

ULTs with the three context-switching functions described above address the parent-child bonding issue and enable unconstrained scheduling among threads. We explain an invocation algorithm of ULTs with switch\_ctx(), start\_ctx(), and end\_ctx(). We note that the following description assumes a typical parent-first ULT (which we call **Full** in Chapter 3) as the representative ULT implementation.

```

1

struct thd_desc_t {

2

void (*f)(void *arg);

3

void *arg;

4

int state;

5

void *stack;

ctx_t *ctx; // context of this thread.

6

7

8

}:

ctx_t *g_caller_ctx; // a global variable

9

10

void schedule_ult(thd_desc_t *thd) {

if (thd->state != STARTED) {

11

12

start_ctx(&g_caller_ctx, thd->stack, ult_wrapper, thd);

13

} else {

14

switch_ctx(&g_caller_ctx, thd->ctx);

15

}

16

}

17

void ult_wrapper(thd_desc_t *thd) {

18

thd->state = STARTED;

thd->f(thd->arg)

19

thd->state = COMPLETED;

20

21

end_ctx(g_caller_ctx);

22

}

```

Figure 2.5: Pseudocode of invocation of a ULT (Full in Chapter 3).

Figure 2.5 shows the pseudocode of a function that invokes a ULT. A given ULT is started by start\_ctx() (line 12) if thd has not been executed previously; otherwise, it resumes thd by switch\_ctx() (line 14) since its context has already been initialized. A user-given thread function is called in a wrapper function ult\_wrapper() (line 17) so that end\_ctx() is executed on completion (line 21) because a ULT invoked by start\_ctx() cannot return to the parent thread just by a standard return procedure. Since both start\_ctx() and switch\_ctx() save the caller's context in g\_caller\_ctx, the caller can be resumed by switch\_ctx() or end\_ctx() at any time.

Independent management of contexts of parent and child threads allows yielding, intermediate termination, and efficient synchronization as explained in Section 3.2. Because of rich capabilities, several

threading libraries adopt ULTs; for example, Qthreads [173], X10 [50], Task Parallel Library [114], Nanos [120], Converse [108], and MassiveThreads [124] are well-known user-level threading libraries, while some programming languages such as Python [165] and Go [145] natively support ULTs.

However, ULTs have larger fork-join overheads because of start\_ctx() and switch\_ctx() are heavier than fork and join operations of a stackless thread. The stack change increases memory footprint and pollutes caches, which lowers performance. Chapter 3 will discuss a high-performance user-level threading library, called Argobots, and explore the implementations of lightweight ULTs that have as low overheads as that of a stackless thread but are implemented without losing functionalities of ULTs.