# **Doctoral Dissertation**

# A Decentralized Implementation of Software Distributed Shared Memory (ソフトウェア分散共有メモリの非集中型実装)

# 遠藤亘

# Wataru Endo

学籍番号: 48-177403

指導教員:田浦健次朗教授

東京大学大学院 情報理工学系研究科 電子情報学専攻

Department of Information and Communication Engineering Graduate School of Information Science and Technology The University of Tokyo

# Abstract

The low application productivity of supercomputers has been a remaining problem in the history of parallel computing. Most of today's supercomputers are distributed-memory machines, which force application programmers to manually issue communication requests. Shared memory, the other memory model, is considered more productive than distributed memory, but it is widely believed that shared-memory programming is not scalable due to the model itself. In the 1990s, many researchers had developed software systems called Distributed Shared Memory (DSM) systems that realize the shared-memory model on top of distributed-memory machines. Nowadays, however, only very few researchers are investigating this idea because of the observed results of its poor performance.

The hardware environment for supercomputing has been largely improved for two or three decades. The interconnection network between nodes has also been significantly improved. The technology trends of both hardware and software have enlightened the possibility of better DSM systems than traditional DSM systems. For example, there were very few DSM systems that utilized the interconnection feature called Remote Direct Memory Access (RDMA), which appeared in the 2000s. Most of RDMA implementations can only support point-to-point communications and it is necessary to implement a decentralized coherence protocol for DSMs to utilize RDMA. Multi-core architectures have become dominant in today's processors and utilizing multi-threading in a node possibly improves the performance of DSM systems, but traditional DSM systems are not optimized for modern hardware.

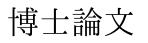

In this dissertation, we propose a decentralized approach to implement distributed shared memory based on RDMA and multi-core architecture. This approach is demonstrated as a software DSM system MENPS. To decentralize the coherence protocol of MENPS, we have introduced three novel ideas: the floating homebased method, the hybrid invalidation of logical timestamps and write notices, and the fast release. The evaluation results of MENPS show that the proposed coherence protocol can improve the performance of software distributed shared memory compared with the existing methods.

To exploit the performance of RDMA on multi-core architectures, we have developed a new communication library MECOM for MENPS. MECOM is a communication library based on a new technique to implement software communication offloading using user-level threading. The proposed software offloading technique using atomic operations improves the message rates of RDMA communications in multi-threading environments compared with the conventional locking schemes.

To accelerate the thread scheduling in MENPS, we also have implemented a user-level threading library ComposableThreads. ComposableThreads provides compile-time parametricity for different purposes in system programming. This library can be not only employed as the tasking layer for MENPS, but also customized as an efficient general-purpose threading library.

This dissertation describes the design and implementation of the DSM library MENPS. As an integrated research prototype for transparently executing shared-memory multi-threading applications, MENPS provides many interesting insights about how we can design parallel computer architecture.

# Acknowledgment

First, I would like to especially thank my supervisor Professor Kenjiro Taura for his continuous support both on my research and PhD life. This work would never be accomplished without his patience for my research activities. We had so many discussions to improve my work and I have borrowed many ideas that originate from his insights. I have been always encouraged by his strong enthusiasm for the improvement of parallel computing systems.

I would like to express my deep gratitude to Assistant Professor Shigeyuki Sato. Without his support, I would neither enter the doctoral course nor continue conducting this research. He was also the first person who really understood what my whole work is all about. His advice was always quite detailed and have significantly strengthened the presentation of my study.

All of the committee members gave me many important comments for defense preparation. I had several great discussions about the early work of this dissertation with two of the advisors Associate Professor Hidetsugu Irie and Professor Masashi Toyoda. I appreciate that both of them kindly spent their time sharing and improving my ideas. Professor Masaru Kitsuregawa, Associate Professor Ryota Shioya, and Dr. Hiroya Matsuba gave me insightful advice to clarify the strengths of my study at the pre-defense.

I am very grateful to Assistant Professor Hiroko Midorikawa for her comments about my DSM study at the workshops, pre-defense, and so on. We had several nice discussions in order to "revive" this research field. With her solid comments, I could enhance both the implementation and presentation qualities for preparing the defense.

I would like to show my gratitude to Dr. Sriram Krishnamoorthy, who kindly gave me technical advice in several offline meetings. I was really surprised by his diverse expertise in this research field. It was a very encouraging opportunity for me to discuss my ongoing work with him.

I would also like to thank Ilya Zhukov, who was our mentor during the International HPC Summer School 2018. We had great discussions on improving my work. His valuable opinions based on the performance analysis have been incorporated into my research.

I would like to thank all of our laboratory members who I have enjoyed the research with. I had a great collaboration with Takuya Fukuoka in the last two years of my doctoral course. It was an exceptional experience in my life to conduct the research together with him. I have enjoyed creating in a new wonderful logging tool with Shunpei Shiina and Tomokazu Higuchi. I would also like to appreciate Shintaro Iwasaki for discussing my rough ideas both online and offline. I appreciate all of the members who participated in the TP-PARSEC project: Dr. An Huynh, Christian Helm, and Byambajav Namsraijav. In addition, most of my work for this dissertation is based on the research conducted by Shigeki Akiyama and Jun Nakashima, who gave me much important advice until my master's course.

I had been helped many times by the former secretary of our laboratory Hiromi Takano. I remember how she was anxious about our laboratory life. I am also thankful to the current secretary Sachie Ikeya for handling lots of paperwork.

Finally, I would like to appreciate my family who has brought me up and let me take this long journey.

# Contents

| 1. | Intro | duction                                                                                   | 1 |

|----|-------|-------------------------------------------------------------------------------------------|---|

|    | 1.1.  | Background                                                                                | 1 |

|    | 1.2.  | Motivation                                                                                | 3 |

|    | 1.3.  | Contributions of this dissertation                                                        | 4 |

|    | 1.4.  | Structure of this dissertation                                                            | 5 |

| 2. | Back  | ground                                                                                    | 7 |

|    |       | ·                                                                                         | 7 |

|    |       |                                                                                           | 7 |

|    |       |                                                                                           | 8 |

|    |       |                                                                                           | 8 |

|    | 2.2.  |                                                                                           | 8 |

|    |       |                                                                                           | 8 |

|    |       | · · · · · · · · · · · · · · · · · · ·                                                     | 9 |

|    |       | 2.2.3. Partitioned Global Address Space (PGAS)                                            | 0 |

|    | 2.3.  | Interconnection networks                                                                  | 1 |

|    |       | 2.3.1. Remote Direct Memory Access (RDMA) 1                                               | 1 |

|    |       | 2.3.2. Performance modeling of communication systems                                      | 2 |

|    | 2.4.  | Memory consistency models                                                                 | 3 |

|    |       | 2.4.1. Sequential Consistency (SC)                                                        | 3 |

|    |       | 2.4.2. Data-race-free consistency models                                                  | 4 |

|    | 2.5.  | Mutex implementations                                                                     | 5 |

|    |       | 2.5.1. Characteristics of mutexes                                                         | 5 |

|    | 2.6.  | Thread scheduling                                                                         | 6 |

|    |       | 2.6.1. Kernel-level threading                                                             | 6 |

|    |       | 2.6.2. User-level threading and task parallelism                                          | 6 |

|    |       | 2.6.3. OpenMP                                                                             | 7 |

| 3. | Men   | es: A decentralized distributed shared memory library designed for modern interconnects 1 | 8 |

|    | 3.1.  | Introduction                                                                              | 8 |

|    | 3.2.  | Importance of RDMA-based design for DSM systems                                           | 9 |

|    | 3.3.  | Overview of Menps                                                                         | 0 |

|    | 3.4.  | Coherence actions of MENPS                                                                | 1 |

|    |       | 3.4.1. Existing methods for writer management                                             | 1 |

|    |       | 3.4.2. Floating home-based protocol for writer management                                 |   |

|    |       | 3.4.3. Directory-based cache invalidation methods                                         | 6 |

|    |       | 3.4.4. Directory-less cache invalidation methods                                          | 8 |

|    |       | 3.4.5. Cache invalidation method of MENPS 2                                               | 9 |

|    |       | 3.4.6. Fast release                                                                       | 0 |

|    | 3.5.  | Implementation of MENPS 3                                                                 | 2 |

|    |       | 3.5.1. Implementation overview                                                            | 2 |

|    |       | 3.5.2. Core interface of MENPS                                                            | 2 |

|    |       | 3.5.3. Implementing memory fences and barriers                                            | 2 |

|    |       |                                                                                           |   |

# Contents

|    |                                                                                                                  | 3.5.4.                                                                                                                                                                                                                                   | Write serialization and diff processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                        |

|----|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                                                                                                                  | 3.5.5.                                                                                                                                                                                                                                   | State transition mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                        |

|    | 3.6.                                                                                                             | MEOM                                                                                                                                                                                                                                     | P: OpenMP runtime on MENPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 36                                                                                                                                                                                                                                                                                                                   |

|    |                                                                                                                  | 3.6.1.                                                                                                                                                                                                                                   | OpenMP on an everything-shared DSM system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 36                                                                                                                                                                                                                                                                                                                   |

|    |                                                                                                                  | 3.6.2.                                                                                                                                                                                                                                   | Execution flow of MEOMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 37                                                                                                                                                                                                                                                                                                                   |

|    |                                                                                                                  | 3.6.3.                                                                                                                                                                                                                                   | Scheduling DSM processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 37                                                                                                                                                                                                                                                                                                                   |

|    | 3.7.                                                                                                             | Evaluat                                                                                                                                                                                                                                  | ion of Menps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 38                                                                                                                                                                                                                                                                                                                   |

|    |                                                                                                                  | 3.7.1.                                                                                                                                                                                                                                   | Application benchmark: NAS Parallel Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 38                                                                                                                                                                                                                                                                                                                   |

|    |                                                                                                                  | 3.7.2.                                                                                                                                                                                                                                   | Application benchmark: matrix multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 40                                                                                                                                                                                                                                                                                                                   |

|    |                                                                                                                  | 3.7.3.                                                                                                                                                                                                                                   | Microbenchmark: memory read on DSM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 40                                                                                                                                                                                                                                                                                                                   |

|    |                                                                                                                  | 3.7.4.                                                                                                                                                                                                                                   | Microbenchmark: false sharing benchmark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 40                                                                                                                                                                                                                                                                                                                   |

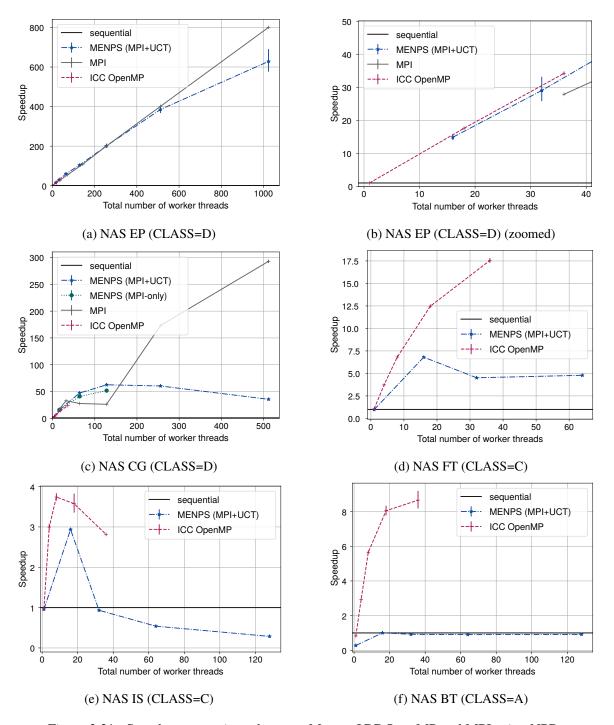

|    | 3.8.                                                                                                             | Evaluat                                                                                                                                                                                                                                  | ion Results: NAS Parallel Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 40                                                                                                                                                                                                                                                                                                                   |

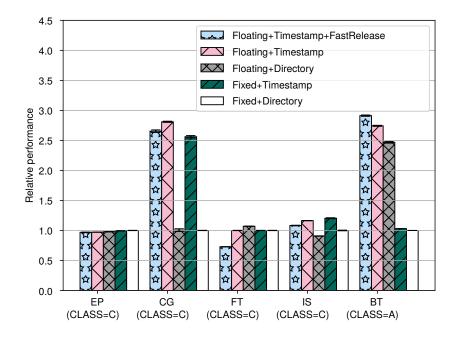

|    |                                                                                                                  | 3.8.1.                                                                                                                                                                                                                                   | Directory, Fixed Home, vs. Floating Home + Timestamp invalidation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 42                                                                                                                                                                                                                                                                                                                   |

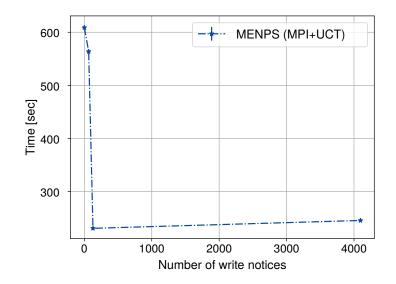

|    |                                                                                                                  | 3.8.2.                                                                                                                                                                                                                                   | Impact of Write Notices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 42                                                                                                                                                                                                                                                                                                                   |

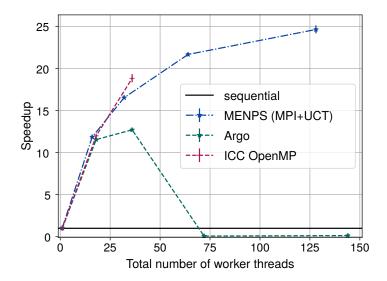

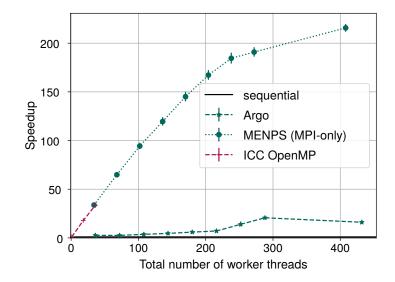

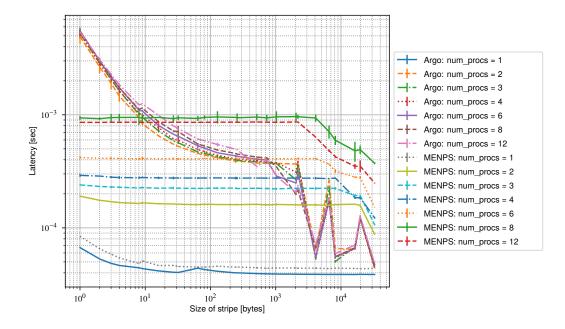

|    |                                                                                                                  | 3.8.3.                                                                                                                                                                                                                                   | MENPS vs. Argo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 43                                                                                                                                                                                                                                                                                                                   |

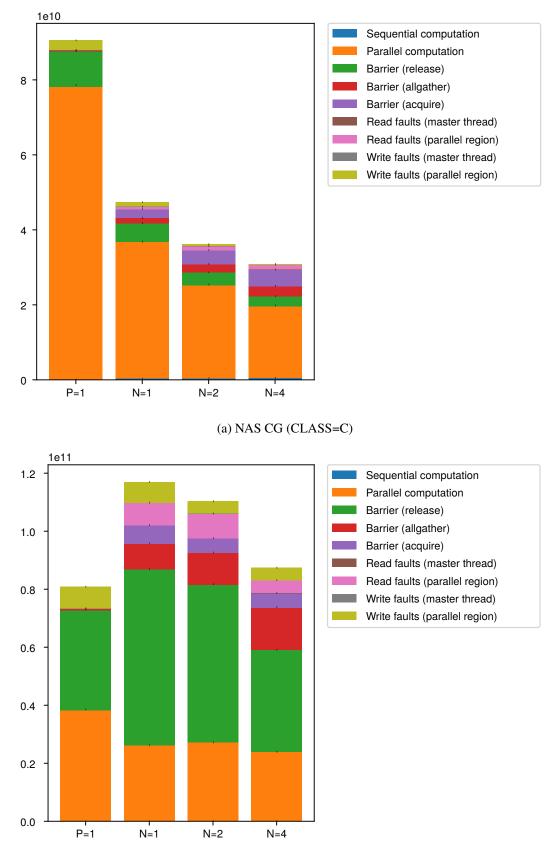

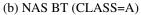

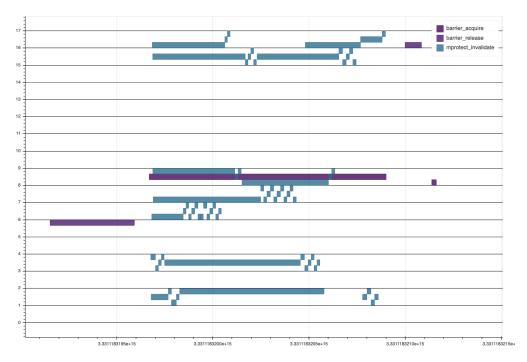

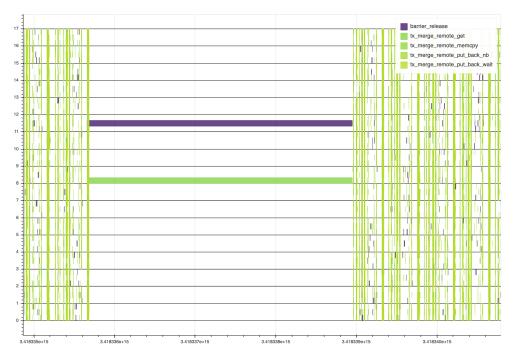

|    |                                                                                                                  | 3.8.4.                                                                                                                                                                                                                                   | Execution breakdown of NAS on MENPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 46                                                                                                                                                                                                                                                                                                                   |

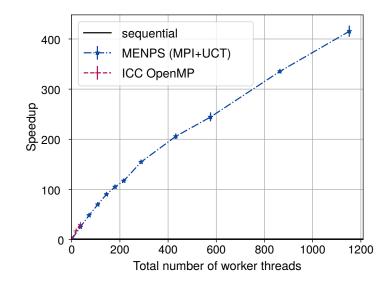

|    | 3.9.                                                                                                             | Applica                                                                                                                                                                                                                                  | tion Benchmark: matrix multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 47                                                                                                                                                                                                                                                                                                                   |

|    | 3.10.                                                                                                            | Microb                                                                                                                                                                                                                                   | enchmark results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 47                                                                                                                                                                                                                                                                                                                   |

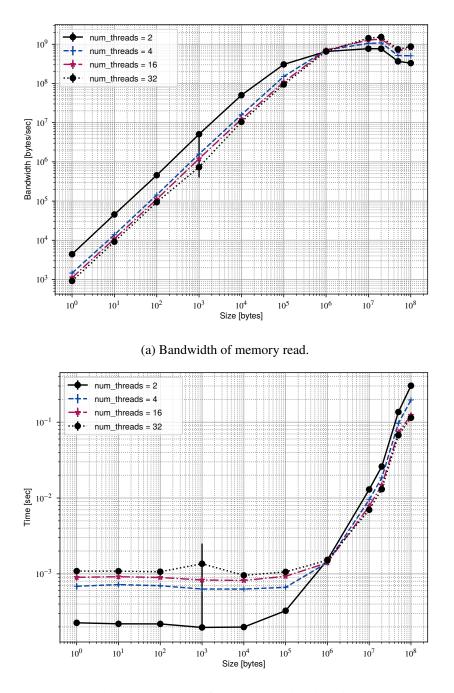

|    |                                                                                                                  | 3.10.1.                                                                                                                                                                                                                                  | Microbenchmark results: memory read benchmark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                        |

|    |                                                                                                                  | 3.10.2.                                                                                                                                                                                                                                  | Microbenchmark results: false sharing benchmark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 48                                                                                                                                                                                                                                                                                                                   |

|    | 3.11.                                                                                                            | Measur                                                                                                                                                                                                                                   | ing Productivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 50                                                                                                                                                                                                                                                                                                                   |

|    |                                                                                                                  |                                                                                                                                                                                                                                          | ry of Menps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                        |

|    |                                                                                                                  |                                                                                                                                                                                                                                          | Future work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                        |

|    |                                                                                                                  |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                        |

| 4. | MEC                                                                                                              | OM: a c                                                                                                                                                                                                                                  | ommunication library using parallelized software communication offloading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53                                                                                                                                                                                                                                                                                                                     |

|    |                                                                                                                  |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                        |

|    | 4.1.                                                                                                             | Introdu                                                                                                                                                                                                                                  | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 53                                                                                                                                                                                                                                                                                                                   |

|    | 4.1.                                                                                                             | Introdu<br>Backgro                                                                                                                                                                                                                       | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 53<br>. 54                                                                                                                                                                                                                                                                                                           |

|    | 4.1.                                                                                                             | Introdu<br>Backgro<br>4.2.1.                                                                                                                                                                                                             | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 53<br>. 54<br>. 54                                                                                                                                                                                                                                                                                                   |

|    | 4.1.                                                                                                             | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.                                                                                                                                                                                                   | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 53<br>. 54<br>. 54<br>. 55                                                                                                                                                                                                                                                                                           |

|    | 4.1.<br>4.2.                                                                                                     | Introduc<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.                                                                                                                                                                                        | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 53<br>. 54<br>. 54<br>. 55<br>. 55                                                                                                                                                                                                                                                                                   |

|    | 4.1.                                                                                                             | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECO                                                                                                                                                                                 | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 53<br>. 54<br>. 54<br>. 55<br>. 55<br>. 56                                                                                                                                                                                                                                                                           |

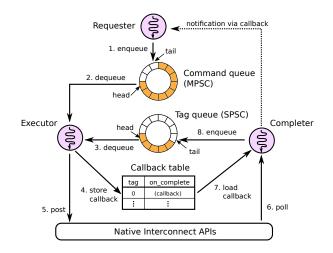

|    | 4.1.<br>4.2.                                                                                                     | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECO<br>4.3.1.                                                                                                                                                                       | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>53</li> <li>54</li> <li>54</li> <li>55</li> <li>55</li> <li>56</li> <li>56</li> </ul>                                                                                                                                                                                                                         |

|    | 4.1.<br>4.2.                                                                                                     | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECO<br>4.3.1.<br>4.3.2.                                                                                                                                                             | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 53<br>. 54<br>. 54<br>. 55<br>. 55<br>. 56<br>. 56<br>. 56                                                                                                                                                                                                                                                           |

|    | <ul><li>4.1.</li><li>4.2.</li><li>4.3.</li></ul>                                                                 | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECO<br>4.3.1.<br>4.3.2.<br>4.3.3.                                                                                                                                                   | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 53<br>. 54<br>. 54<br>. 55<br>. 55<br>. 56<br>. 56<br>. 56<br>. 57                                                                                                                                                                                                                                                   |

|    | <ul><li>4.1.</li><li>4.2.</li><li>4.3.</li></ul>                                                                 | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECO<br>4.3.1.<br>4.3.2.<br>4.3.3.<br>Microb                                                                                                                                         | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 53<br>. 54<br>. 54<br>. 55<br>. 55<br>. 56<br>. 56<br>. 56<br>. 57<br>. 60                                                                                                                                                                                                                                           |

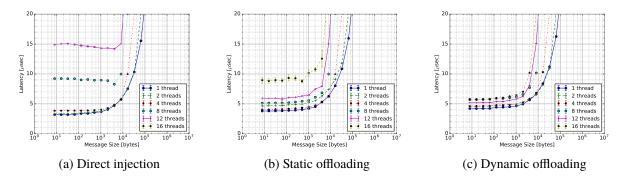

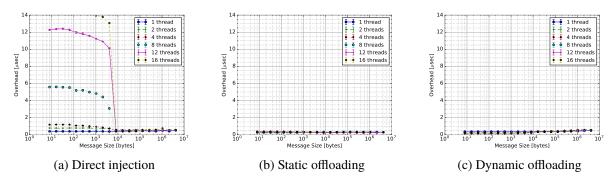

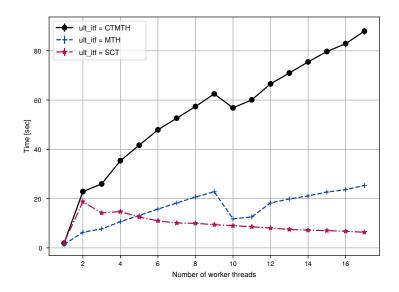

|    | <ul><li>4.1.</li><li>4.2.</li><li>4.3.</li></ul>                                                                 | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECO<br>4.3.1.<br>4.3.2.<br>4.3.3.<br>Microb<br>4.4.1.                                                                                                                               | ctionbundInfiniBand VerbsMulti-threading support in communication systemsUser-level threading for communication librariesM 1: Communication software offloading on InfiniBand VerbsAPI of MECOM 1Design of parallelized software offloadingImplementation using a circular bufferenchmark evaluation of MECOM 1Evaluation setup and benchmarks                                                                                                                                                                                                                        | . 53<br>. 54<br>. 54<br>. 55<br>. 55<br>. 56<br>. 56<br>. 56<br>. 56<br>. 57<br>. 60<br>. 60                                                                                                                                                                                                                           |

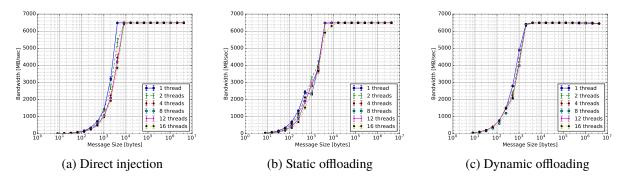

|    | <ul><li>4.1.</li><li>4.2.</li><li>4.3.</li></ul>                                                                 | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECO<br>4.3.1.<br>4.3.2.<br>4.3.3.<br>Microb<br>4.4.1.<br>4.4.2.                                                                                                                     | ctionbundInfiniBand VerbsMulti-threading support in communication systemsUser-level threading for communication librariesM 1: Communication software offloading on InfiniBand VerbsAPI of MECOM 1Design of parallelized software offloadingImplementation using a circular bufferenchmark evaluation of MECOM 1Evaluation setup and benchmarksPerformance metrics with a single QP and a CQ                                                                                                                                                                           | . 53<br>. 54<br>. 54<br>. 55<br>. 55<br>. 56<br>. 56<br>. 56<br>. 56<br>. 57<br>. 60<br>. 60<br>. 62                                                                                                                                                                                                                   |

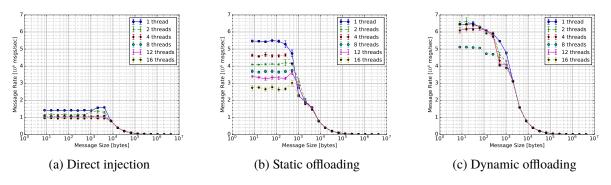

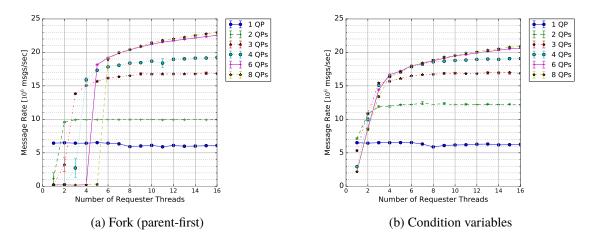

|    | <ul><li>4.1.</li><li>4.2.</li><li>4.3.</li></ul>                                                                 | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECO<br>4.3.1.<br>4.3.2.<br>4.3.3.<br>Microb<br>4.4.1.<br>4.4.2.<br>4.4.3.                                                                                                           | ctionbundInfiniBand VerbsMulti-threading support in communication systemsUser-level threading for communication librariesM 1: Communication software offloading on InfiniBand VerbsAPI of MECOM 1Design of parallelized software offloadingImplementation using a circular bufferenchmark evaluation of MECOM 1Evaluation setup and benchmarksPerformance metrics with a single QP and a CQMessage rates with multiple QPs and CQs                                                                                                                                    | . 53<br>. 54<br>. 54<br>. 55<br>. 55<br>. 56<br>. 56<br>. 56<br>. 56<br>. 57<br>. 60<br>. 60<br>. 62<br>. 64                                                                                                                                                                                                           |

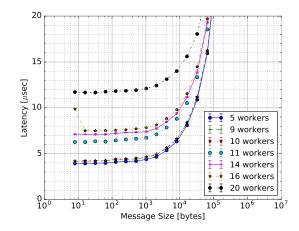

|    | <ul><li>4.1.</li><li>4.2.</li><li>4.3.</li><li>4.4.</li></ul>                                                    | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECO<br>4.3.1.<br>4.3.2.<br>4.3.3.<br>Microb<br>4.4.1.<br>4.4.2.<br>4.4.3.<br>4.4.4.                                                                                                 | ctionbundInfiniBand VerbsMulti-threading support in communication systemsUser-level threading for communication librariesM 1: Communication software offloading on InfiniBand VerbsAPI of MECOM 1Design of parallelized software offloadingImplementation using a circular bufferenchmark evaluation of MECOM 1Evaluation setup and benchmarksPerformance metrics with a single QP and a CQMessage rates with multiple QPs and CQsEffects of NUMA nodes                                                                                                               | <ul> <li>. 53</li> <li>. 54</li> <li>. 54</li> <li>. 55</li> <li>. 56</li> <li>. 56</li> <li>. 56</li> <li>. 56</li> <li>. 56</li> <li>. 56</li> <li>. 60</li> <li>. 60</li> <li>. 60</li> <li>. 62</li> <li>. 64</li> <li>. 65</li> </ul>                                                                             |

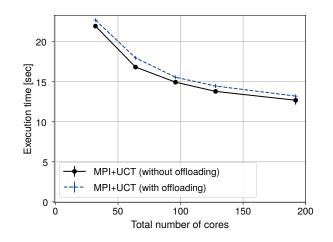

|    | <ul><li>4.1.</li><li>4.2.</li><li>4.3.</li><li>4.4.</li></ul>                                                    | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECO<br>4.3.1.<br>4.3.2.<br>4.3.3.<br>Microb<br>4.4.1.<br>4.4.2.<br>4.4.3.<br>4.4.4.<br>MECO                                                                                         | ctionbundInfiniBand VerbsMulti-threading support in communication systemsUser-level threading for communication librariesM 1: Communication software offloading on InfiniBand VerbsAPI of MECOM 1Design of parallelized software offloadingImplementation using a circular bufferenchmark evaluation of MECOM 1Evaluation setup and benchmarksPerformance metrics with a single QP and a CQMessage rates with multiple QPs and CQsEffects of NUMA nodesM 2: Communication software offloading on MPI and UCX                                                          | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                                                                                                                                                                                                                   |

|    | <ul> <li>4.1.</li> <li>4.2.</li> <li>4.3.</li> <li>4.4.</li> <li>4.5.</li> </ul>                                 | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECO<br>4.3.1.<br>4.3.2.<br>4.3.3.<br>Microb<br>4.4.1.<br>4.4.2.<br>4.4.3.<br>4.4.4.<br>MECO<br>4.5.1.                                                                               | ctionoundInfiniBand VerbsMulti-threading support in communication systemsUser-level threading for communication librariesM 1: Communication software offloading on InfiniBand VerbsAPI of MECOM 1Design of parallelized software offloadingImplementation using a circular bufferenchmark evaluation of MECOM 1Evaluation setup and benchmarksPerformance metrics with a single QP and a CQMessage rates with multiple QPs and CQsEffects of NUMA nodesM 2: Communication software offloading on MPI and UCXEvaluation of parallelized software offloading with MENPS | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                                                                                                                                                                                                                   |

|    | <ul><li>4.1.</li><li>4.2.</li><li>4.3.</li><li>4.4.</li></ul>                                                    | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECO<br>4.3.1.<br>4.3.2.<br>4.3.3.<br>Microb<br>4.4.1.<br>4.4.2.<br>4.4.3.<br>4.4.4.<br>MECO<br>4.5.1.                                                                               | ctionbundInfiniBand VerbsMulti-threading support in communication systemsUser-level threading for communication librariesM 1: Communication software offloading on InfiniBand VerbsAPI of MECOM 1Design of parallelized software offloadingImplementation using a circular bufferenchmark evaluation of MECOM 1Evaluation setup and benchmarksPerformance metrics with a single QP and a CQMessage rates with multiple QPs and CQsEffects of NUMA nodesM 2: Communication software offloading on MPI and UCX                                                          | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                                                                                                                                                                                                                   |

| 5  | <ul> <li>4.1.</li> <li>4.2.</li> <li>4.3.</li> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> </ul>                   | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECO<br>4.3.1.<br>4.3.2.<br>4.3.3.<br>Microb<br>4.4.1.<br>4.4.2.<br>4.4.3.<br>4.4.4.<br>MECO<br>4.5.1.<br>Summa                                                                      | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                                                                                                                                                                                                                   |

| 5. | <ul> <li>4.1.</li> <li>4.2.</li> <li>4.3.</li> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> <li>Com</li> </ul>      | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECOI<br>4.3.1.<br>4.3.2.<br>4.3.3.<br>Microb<br>4.4.1.<br>4.4.2.<br>4.4.3.<br>4.4.4.<br>MECOI<br>4.5.1.<br>Summa                                                                    | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>53</li> <li>54</li> <li>54</li> <li>55</li> <li>56</li> <li>56</li> <li>56</li> <li>56</li> <li>56</li> <li>56</li> <li>56</li> <li>60</li> <li>62</li> <li>64</li> <li>65</li> <li>66</li> <li>66</li> <li>67</li> </ul>                                                                                     |

| 5. | <ul> <li>4.1.</li> <li>4.2.</li> <li>4.3.</li> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> <li>Com</li> </ul>      | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECOI<br>4.3.1.<br>4.3.2.<br>4.3.3.<br>Microb<br>4.4.1.<br>4.4.2.<br>4.4.3.<br>4.4.4.<br>MECOI<br>4.5.1.<br>Summa                                                                    | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>53</li> <li>54</li> <li>54</li> <li>55</li> <li>56</li> <li>56</li> <li>56</li> <li>56</li> <li>56</li> <li>56</li> <li>56</li> <li>60</li> <li>62</li> <li>64</li> <li>65</li> <li>66</li> <li>66</li> <li>67</li> <li>68</li> <li>68</li> </ul>                                                             |

| 5. | <ul> <li>4.1.</li> <li>4.2.</li> <li>4.3.</li> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> <li>Com 5.1.</li> </ul> | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECO<br>4.3.1.<br>4.3.2.<br>4.3.3.<br>Microb<br>4.4.1.<br>4.4.2.<br>4.4.3.<br>4.4.4.<br>MECO<br>4.5.1.<br>Summa<br><b>posable</b><br>Introdu<br>5.1.1.                               | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>53</li> <li>54</li> <li>55</li> <li>56</li> <li>56</li> <li>56</li> <li>56</li> <li>56</li> <li>56</li> <li>56</li> <li>56</li> <li>60</li> <li>60</li> <li>62</li> <li>64</li> <li>65</li> <li>66</li> <li>66</li> <li>67</li> <li>68</li> <li>68</li> <li>68</li> </ul>                                     |

| 5. | <ul> <li>4.1.</li> <li>4.2.</li> <li>4.3.</li> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> <li>Com 5.1.</li> </ul> | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECOI<br>4.3.1.<br>4.3.2.<br>4.3.3.<br>Microb<br>4.4.1.<br>4.4.2.<br>4.4.3.<br>4.4.4.<br>MECOI<br>4.5.1.<br>Summa<br><b>posable</b><br>Introdu<br>5.1.1.<br>Design                   | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                                                                                                                                                                                                                   |

| 5. | <ul> <li>4.1.</li> <li>4.2.</li> <li>4.3.</li> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> <li>Com 5.1.</li> </ul> | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECOI<br>4.3.1.<br>4.3.2.<br>4.3.3.<br>Microbo<br>4.4.1.<br>4.4.2.<br>4.4.3.<br>4.4.4.<br>MECOI<br>4.5.1.<br>Summa<br><b>posable</b><br>Introdu<br>5.1.1.<br>Design<br>5.2.1.        | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>53</li> <li>54</li> <li>54</li> <li>55</li> <li>56</li> <li>56</li> <li>56</li> <li>56</li> <li>56</li> <li>56</li> <li>56</li> <li>56</li> <li>60</li> <li>62</li> <li>62</li> <li>64</li> <li>65</li> <li>66</li> <li>66</li> <li>67</li> <li>68</li> <li>68</li> <li>68</li> <li>69</li> <li>69</li> </ul> |

| 5. | <ul> <li>4.1.</li> <li>4.2.</li> <li>4.3.</li> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> <li>Com 5.1.</li> </ul> | Introdu<br>Backgro<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>MECO<br>4.3.1.<br>4.3.2.<br>4.3.3.<br>Microb<br>4.4.1.<br>4.4.2.<br>4.4.3.<br>4.4.4.<br>MECO<br>4.5.1.<br>Summa<br><b>posable</b><br>Introdu<br>5.1.1.<br>Design<br>5.2.1.<br>5.2.2. | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                   |

# Contents

|    |      |          |                                                      | 72<br>72 |

|----|------|----------|------------------------------------------------------|----------|

|    | 5 2  |          |                                                      | 72       |

|    | 5.3. |          | 1                                                    | 73       |

|    |      |          |                                                      | 73       |

|    | 5.4. |          |                                                      | 73<br>74 |

|    | 3.4. |          |                                                      | 74<br>75 |

|    |      |          |                                                      | 75<br>75 |

|    | 5 5  |          |                                                      | 75<br>75 |

|    | 5.5. | Summa    | ry of ComposableThreads                              | 15       |

| 6. | Rela | ted work | {                                                    | 77       |

|    |      |          |                                                      | 77       |

|    |      |          |                                                      | 77       |

|    |      |          |                                                      | 79       |

|    |      |          |                                                      | 80       |

|    |      |          |                                                      | 81       |

|    |      |          |                                                      | 82       |

|    |      |          |                                                      | 82       |

|    | 6.2. |          |                                                      | 83       |

|    | 6.3. |          |                                                      | 84       |

|    |      | 6.3.1.   | Self-invalidation techniques                         | 84       |

|    |      | 6.3.2.   | Reducing directory storage                           | 85       |

|    |      | 6.3.3.   | Timestamp-based invalidations                        | 86       |

|    |      |          |                                                      | 86       |

|    | 6.4. | Commu    | inication libraries for interconnects                | 86       |

|    |      | 6.4.1.   | Low-level communication libraries                    | 86       |

|    |      | 6.4.2.   | Multi-threading performance of communication systems | 87       |

|    |      | 6.4.3.   | Performance characteristics of RDMA                  | 87       |

|    | 6.5. | User-lev | vel threading and task scheduling                    | 88       |

|    |      |          |                                                      | 88       |

|    |      | 6.5.2.   | Stackful or stackless coroutines                     | 88       |

|    |      | 6.5.3.   | Work-stealing schedulers                             | 88       |

|    |      |          |                                                      | 89       |

| 7. | Cond | clusions |                                                      | 90       |

|    | 7.1. | Future v | work                                                 | 91       |

| Α. | Арре | endix    |                                                      | 93       |

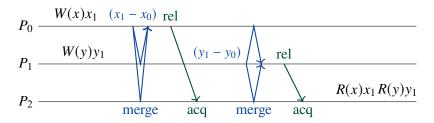

|    | A.1. | Cache in | nvalidation problem                                  | 93       |

# List of Figures

| 1.1.  | Software stack of MENPS                                                                                             | 5              |

|-------|---------------------------------------------------------------------------------------------------------------------|----------------|

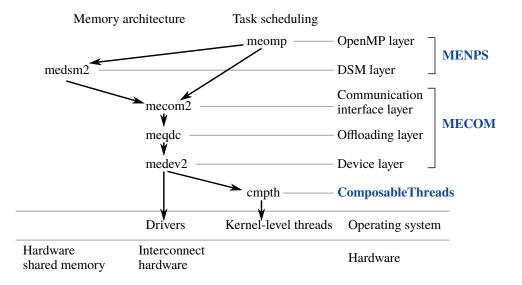

| 2.1.  | Partitioned Global Address Space (PGAS) model.                                                                      | 10             |

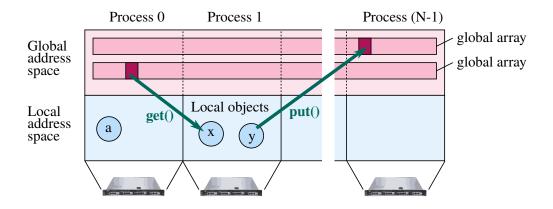

| 2.2.  | Example of global ordering in sequential consistency.                                                               | 13             |

| 2.3.  | Example of a program order in sequential consistency.                                                               | 13             |

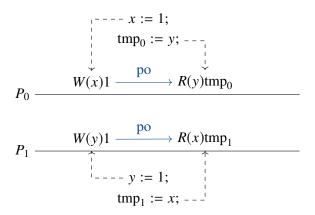

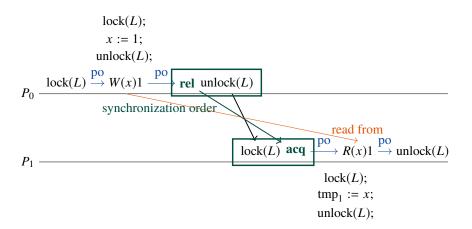

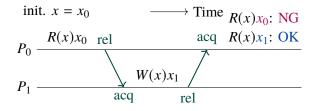

| 2.4.  | Example of a release-acquire synchronization pair based on the mutex synchronization                                | 14             |

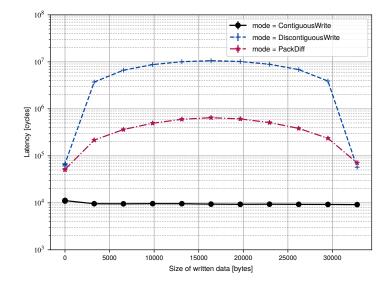

| 3.1.  | Performance comparison of three methods for remote write.                                                           | 20             |

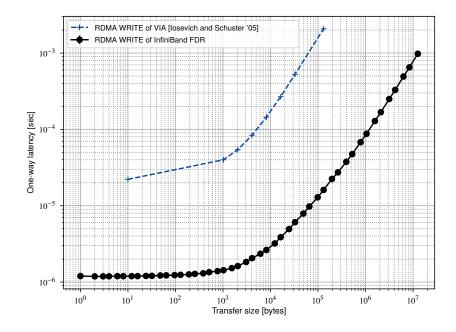

| 3.2.  | Comparison of latency of RDMA WRITE between VIA and InfiniBand FDR                                                  | 21             |

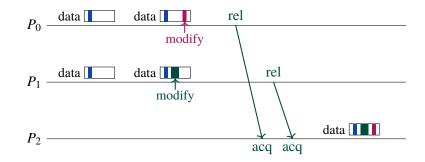

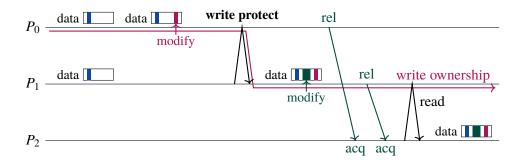

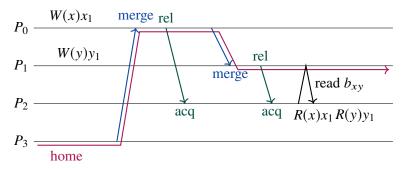

| 3.3.  | A false sharing situation in release consistency.                                                                   | 22             |

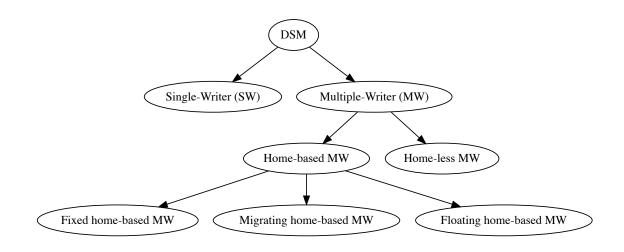

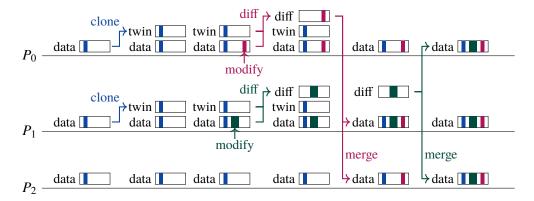

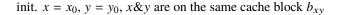

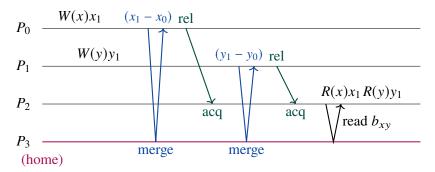

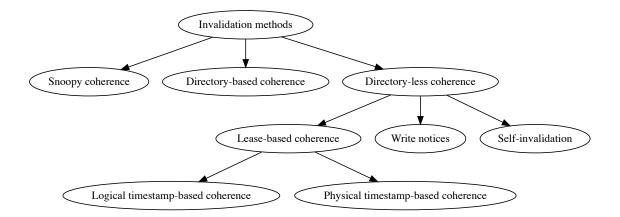

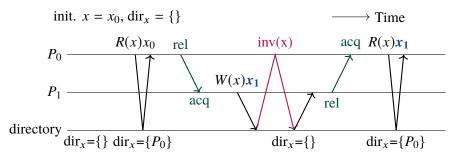

| 3.4.  | Classification of single-writer and multiple-writer protocols.                                                      | 22             |