# 東京大学 大学院新領域創成科学研究科 基盤科学研究系物質系専攻

令和2年度 修士論文

超親水性ナノすりガラス基板を用いた 高移動度極薄有機単結晶膜の作製と論理素子応用

> 2021年1月18日提出 指導教員 竹谷 純一 教授 印

> > 二宮 陽真

## 目次

| 第1章 序論                         | 3  |

|--------------------------------|----|

| 1.1. 有機電界効果トランジスタ(OFET)        | 4  |

| 1.1.1. OFET の構造と動作原理           | 4  |

| 1.1.2. OFET の移動度評価             | 6  |

| 1.1.3. 有機半導体材料                 | 9  |

| 1.2. 有機半導体膜の塗布手法               | 13 |

| 1.3. 半導体膜の転写手法                 | 15 |

| 1.3.1. 犠牲層を用いた転写手法             | 15 |

| 1.3.2. 液面から半導体膜を転写する手法         | 17 |

| 1.3.3. 超親水性塗布基板を利用した転写手法       | 17 |

| 1.4. 本研究の目的                    | 21 |

| 第2章 有機単結晶薄膜の新規転写手法             | 22 |

| 2.1. 超親水性ナノすりガラス (NGG) の開発     | 22 |

| 2.1.1. 固体表面の濡れ性                | 22 |

| 2.1.2. NGG の作製手法               | 24 |

| 2.1.3. 高温下における親水性の安定性評価        | 25 |

| 2.1.4. NGG 上への半導体膜の塗布          | 28 |

| 2.1.5. NGG を用いた半導体膜の転写         | 29 |

| 2.2. PDMS リレー基板の導入             | 31 |

| 2.2.1. NGG とリレー基板を用いた半導体膜の転写   | 31 |

| 2.2.2. XRD 測定による転写膜の結晶性評価      | 32 |

| 2.2.3. n 型 OFET の作製            | 33 |

| 2.2.4. 転写の原理                   | 35 |

| 第3章 NGG を用いたマイクロスタンプ転写パターニング   | 36 |

| 3.1. マイクロスタンプ転写パターニング (μSTP) 法 | 36 |

| 3.1.1. パターニングプロセス              | 36 |

| 3.1.2. 解像度および大面積応用             | 38 |

| 3.1.3. 半導体膜の評価                 | 39 |

| 3.2. CMOS 論理回路応用               | 41 |

| 3.2.1. CMOS 論理回路               | 41 |

| 3.2.2. CMOS 論理回路の作製            | 45 |

| 3.2.3. デバイス評価                  | 48 |

| 第4章 総括                         | 52 |

| 参考文献                           | 53 |

| 謝辞                             | 57 |

## 第1章 序論

半導体は、論理回路やセンサなどあらゆるエレクトロニクスデバイスの中で使用されており、 現代社会において不可欠なものとなっている。あらゆるモノがインターネットで繋がる IoT (Internet of Things) 社会の実現には、あらゆるモノの状態をセンサなどによってデータ化する必要 があるため莫大な量のデバイスが必要となり、例えばセンサについては毎年 1 兆個の需要が予測 されている。このような中で、次世代のエレクトロニクスデバイス基盤材料として有機半導体が 注目されている。有機半導体は分子修飾によって溶媒に可溶な分子を設計することが可能である ので、このような分子を用いることで大気下において、室温から 150℃ 以下程度の低温で塗布プ ロセスにより半導体膜を得ることが出来る。そのため、1000 ℃ 程度の高温での真空プロセスを必 要とする無機半導体デバイスに比べて安価にデバイスを作製することが可能であり、低環境負荷 であるという利点も挙げられる。また、無機半導体が原子同士の共有結合で強く結びついている のに対し、有機半導体は van der Waals 力によって集合体を形成しているという点も大きな特徴で ある。共有結合による無機半導体の結合エネルギーが数 eV 程度であるのに対して、弱い van der Waals 力で凝集した有機半導体の結合エネルギーは多くの場合 10-100 meV 程度である。そのた め、有機半導体は機械的な曲げに対する耐久性が高いという無機半導体にはない付加価値もあり、 これを活かしたフレキシブルディスプレイ[1][2][3]や、センサ付きの人工皮膚[4]などの研究も進 められている。有機半導体の移動度は、Kudo らによって有機トランジスタの駆動が初めて報告さ れた当初は 10<sup>-5</sup> cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> 程度の値にとどまっていたが[5]、近年の有機半導体材料開発と半導体 膜作製技術の進歩によって有機半導体の移動度は飛躍的に向上している。特に、分子の配向が揃 っている単結晶は結晶粒界が少ないために電気伝導特性に優れており、10 cm² V-1 s-1 を超える移 動度を示す材料も報告されている[6][7][8]。また、近年では大面積塗布技術の発展により、約 100 cm<sup>2</sup> の大面積で高移動度単結晶性薄膜を得ることが可能となっており、量産にも向いていると言 うことができる[9]。

このように有機半導体は産業分野へ応用可能なレベルまで発展してきていると言えるが、有機半導体デバイスの実用化には依然として課題が残されている。有機電界トランジスタ(Organic Field-Effect Transistor: OFET)のような積層デバイスの作製時において、溶液プロセスによる半導体の塗布は基板、絶縁膜、電極などからなる下地層の表面上で行う必要がある。ここで、下地層において有機溶剤耐性、結晶成長に十分な平坦性および熱耐性などの性能が求められることから、構成材料や構造に制約がかかってしまう問題があった。このような問題の解決策として、別基板上に作製された半導体膜を目的の基板上に移送する半導体膜の転写手法が報告されている[10]。この転写手法では、超親水性の基板上に高撥水性表面を形成する有機半導体膜を塗布し、界面に水を浸入させることで半導体膜の剥離を行っている。そのため、有機半導体の塗布後に基板の超親水性が保たれていることが重要となる。しかし、先行研究における塗布基板は UV/O3 処理による水酸基の生成によって超親水性としており、150 ℃ 程度の高温環境下においては親水性が失われてしまっていた。そのため、有機半導体材料の種類によっては依然として制約が存在していた。

本研究では、表面に微細な凹凸を形成することで、高温環境下においても構造的に安定に超親水性を保つ塗布基板を開発した。また、転写時に半導体膜にかかる応力を低減するためにエラス

トマー材料で作製したリレー基板を導入することで、低い溶解性のために高温プロセスが必要であるn型有機半導体単結晶膜を電気特性へのダメージなしに転写する手法を新たに開発した。さらに、本手法をp型有機半導体にも適用することで有機 CMOS 論理素子を作製することに成功した。本章ではまず、OFETの基本事項や半導体膜の製膜技術について述べた後、これまで研究されてきた半導体膜の転写手法について紹介し、本研究の目的とアウトラインを示す。

#### 1.1. 有機電界効果トランジスタ (OFET)

電界効果トランジスタ (FET) は、論理回路やセンサなど多くの電子デバイスの中で用いられる基本素子であり、増幅機能とスイッチング機能を持つ。IoT 社会の中で膨大な需要が見込まれているセンサでは、読み取ったアナログ信号をデジタル信号に変換し、論理回路での演算を経たデータを無線伝送するという流れでデータが送られるが、このすべての過程は FET の増幅機能とスイッチング機能を利用したものである。IoT 社会の実現に向け、センサにも様々な状況に対応できるようフレキシブル性や生体親和性などが求められ、これらのニーズに適合した次世代のエレクトロニクスデバイスとして、有機半導体を活性層に用いたトランジスタ、有機電界効果トランジスタ (OFET) が注目を集めている。以下で OFET の基本事項と、OFET の性能向上に向けた有機半導体材料と塗布プロセスの変遷について紹介する。

#### 1.1.1. OFET の構造と動作原理

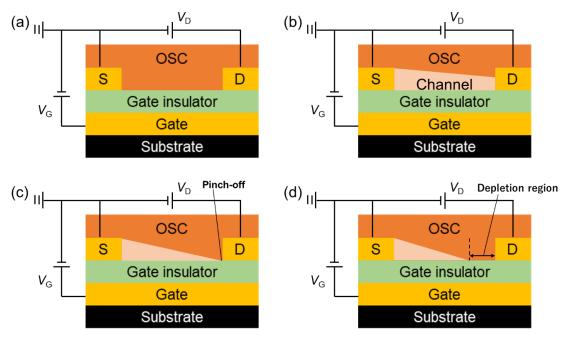

一般的な OFET は主に、有機半導体層、ゲート絶縁膜、ソース / ドレイン電極、ゲート電極および支持基板からなる。代表的な構造を図 1.1 (a-d) に示す。有機半導体層より下部にゲート電極がある構造を「ボトムゲート型」、有機半導体層より上部にゲート電極がある構造を「トップゲート型」といい、ソース / ドレイン電極が有機半導体層の上面に接する構造を「トップコンタクト

図 1.1 OFET の構造模式図。(a) ボトムゲート - トップコンタクト型 (b) ボトムゲート - ボトムコンタクト型 (c) トップゲート - トップコンタクト型 (d) トップゲート - ボトムコンタクト型

型」、ソース / ドレイン電極が有機半導体層の下面に接する構造を「ボトムコンタクト型」と呼ぶ。これらを組み合わせたボトムゲート - トップコンタクト型(図 1.1 (a))、ボトムゲート - ボトムコンタクト型(図 1.1 (b))、トップゲート - トップコンタクト型(図 1.1 (c))、トップゲート - ボトムコンタクト型(図 1.1 (d))の構造が OFET の基本構造である。このように OFET は複数の構成要素からなる積層デバイスであり、異種(ヘテロ)接合界面の制御がデバイス特性に大きな影響を与える。そのため、高性能デバイスの作製には各層の材料だけでなく、作製プロセスも大切になってくる。

続いて、OFETの動作原理をボトムゲート・ボトムコンタクト型 OFET を例に説明する。OFET の動作はゲート電極に印加する電圧 ( $V_G$ ) とドレイン電極に印加する電圧 ( $V_D$ ) で制御される。ゲ ート電極 - 絶縁膜 - 有機半導体からなる MIS (Metal-Insulator-Semiconductor) 構造のキャパシタ に対して VG を印加することによって半導体層にソース電極からキャリアを供給し、ソースード レイン電極間に VD を印加することで蓄積されたキャリアを取り出すという仕組みである。この とき、キャリアが蓄積される領域をチャネルと呼ぶ。有機半導体は基本的に真性半導体であるた め、 $V_{\rm G}$  の印加によって on/off を切り替えることができ、スイッチング素子としての役割を果た す。 $V_{

m G}=0~

m V$  のとき(図 1.2~(a))、チャネルにキャリアがほとんど蓄積されていないため、 $V_{

m D}$  を 印加しても基本的には電流はほとんど流れない。VG を大きくしていくと、チャネルにキャリアが 蓄積されていき、ソースードレイン電極間にドレイン電流 (ID) が観測されるようになる。このキ ャリア注入が始まる時の電圧を閾値電圧 ( $V_{

m th}$ ) と呼ぶ。 $\mid V_{

m G} \mid > \mid V_{

m th} \mid$  の領域で、 $\mid V_{

m D} \mid$  が  $\mid V_{

m G} - V_{

m th}$ | よりも十分小さな領域では、キャリアはチャネル中に一様に分布しておりチャネル抵抗は一定 であるとみなせる。そのため、 $V_D$  の値に比例した  $I_D$  が観測され、この領域を線形領域と呼ぶ(図  $1.2\,(b))$ 。 $|V_{\rm D}|$  を増大させていき、 $|V_{\rm D}|=|V_{\rm G}-V_{\rm th}|$  に達すると、ドレイン電極とゲート電極間の 電位差がなくなり、ドレイン電極近傍のキャリア蓄積層が消滅する。この現象をピンチオフと呼 ぶ (図 1.2 (c))。 さらに大きな  $|V_D|$  を印加すると、余剰の  $|V_D|$  はソース・ドレイン電極間のキ ャリアの存在しない空乏領域で消費されてしまい、実効的にチャネルにかかる電圧は一定となる ために  $I_D$  の値はほとんど変化しなくなる。この領域を飽和領域と呼ぶ(図 1.2 (d))。

図 1.2 (a)  $V_G = 0$  V、(b) 線形領域、(c) ピンチオフ、(d) 飽和領域での OFET 動作原理を示す模式図。

#### 1.1.2. OFET の移動度評価

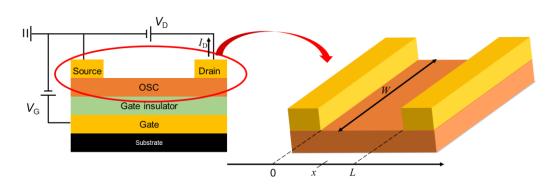

続いて、OFET の性能の指標となる、移動度の導出方法について述べる。図 1.3 の OFET の模式図に導出に用いる各値、座標を示す。ここでは、OFET の動作を簡単に定式化するために、ドレイン電圧  $V_D$  によって生じるチャネル平行方向の電界がゲート電圧  $V_G$  によって生じるチャネル垂直方向の電界に対して十分に小さいとする gradual channel 近似が成り立っていると仮定して導出を行う。

図 1.3 OFET の模式図。 $V_D$ 、 $V_G$ 、 $I_D$ 、L、W はそれぞれ、ドレイン電圧、ゲート電圧、ドレイン電流、チャネル長、チャネル幅を示す。

まず図 1.3 に示すようにチャネルに沿った方向にx 軸をとると、 $V_G$  によって誘起される位置x に蓄積される単位面積当たりのキャリア量 Q(x)は

$$Q(x) = C_{\rm i} (V_{\rm G} - V_{\rm th} - V(x))$$

$$\tag{1}$$

と書ける。 $C_i$ は単位面積当たりのキャパシタンス、V(x)は位置 x のスカラーポテンシャルをそれぞれ表す。位置 x に流れる電流  $I_D(x)$ は単位時間あたりに仮想断面を通過する電荷量であるので、

$$I_{\mathbf{D}}(x) = WQ(x)v(x) \tag{2}$$

と表される。Wはチャネル幅、v(x)は位置 x におけるキャリアのドリフト速度を表している。ここで、v(x)はキャリア移動度  $\mu$  と位置 x での電場  $\varepsilon(x)$ を用いて以下のように書き表される。

$$v(x) = \mu \varepsilon(x) \tag{3}$$

(1) および (3) 式を (2) 式に代入して整理すると位置 x におけるドレイン電流  $I_D(x)$ は

$$I_{\rm D}(x) = \mu W C_{\rm i} (V_{\rm G} - V_{\rm th} - V(x)) \varepsilon(x) \tag{4}$$

となる。ここで、 $\varepsilon(x)$ は

$$\varepsilon(x) = \frac{dV(x)}{dx} \tag{5}$$

と定義されるので、(4)と(5)式から

$$I_{\rm D}(x)dx = \mu W C_{\rm i} (V_{\rm G} - V_{\rm th} - V(x)) dV(x)$$

(6)

という関係式が得られる。 (6) 式の両辺を x について 0 から L まで積分すると、 $V_D$  の境界条件 V(0)=0、 $V(L)=V_D$  を用いて、

$$\int_{0}^{L} I_{\rm D}(x) dx = \int_{0}^{V_{\rm D}} \mu W C_{\rm i} (V_{\rm G} - V_{\rm th} - V(x)) dV(x)$$

(7)

となる。定常状態では $I_D(x)$ は位置xによらず一定となるので、これを $I_D$ とおくと (7) 式から

$$I_{\rm D} = \frac{\mu W C_{\rm i} V_{\rm D}}{L} \left( V_{\rm G} - V_{\rm th} - \frac{V_{\rm D}}{2} \right) \tag{8}$$

となる。線形領域では  $|V_{\rm D}| << |V_{\rm G} - V_{\rm th}|$  なので、(8) 式は

$$I_{\rm D} \approx \frac{\mu W C_{\rm i}}{L} V_{\rm D} (V_{\rm G} - V_{\rm th}) \tag{9}$$

と近似できる。(9) 式から  $V_G$ が一定のとき線形領域ではドレイン電流  $I_D$ は  $V_D$ に比例することがわかる。この領域で、 $V_D$ を一定にしたときに得られる  $I_{D}$ – $V_G$  曲線を線形領域の伝達曲線と呼ぶ。 gradual channel 近似が成り立つとき、 $\mu$  は  $V_G$ に依存しないので、 (9) 式の両辺を  $V_G$ で微分して整理すると線形領域の移動度  $\mu_{lin}$ に関して、

$$\mu_{\rm lin} = \frac{L}{W} \frac{1}{C_{\rm i} V_{\rm D}} \frac{\partial I_{\rm D}}{\partial V_{\rm G}} \tag{10}$$

という関係式が得られる。一方、飽和領域では余剰な電圧は空乏領域で消費されてしまうので、 実効的にチャネルにかかっている電圧は  $V_{\rm G}-V_{\rm th}$  で一定となる。したがって  $V_{\rm D}=V_{\rm G}-V_{\rm th}$ を (8) 式 に代入して整理すると

$$I_{\rm D} = \frac{\mu W C_{\rm i}}{2L} (V_{\rm G} - V_{\rm th})^2 \tag{11}$$

と表される。 (11) 式の両辺の平方根をとると、

$$\sqrt{I_{\rm D}} = \sqrt{\frac{\mu W C_{\rm i}}{2L}} (V_{\rm G} - V_{\rm th}) \tag{12}$$

という関係式が得られる。この領域で、 $V_D$ を一定にしたときに得られる $\sqrt{I_D}$   $-V_G$  曲線を飽和領域の伝達曲線と呼ぶ。線形領域の場合と同様に (12) 式の両辺を  $V_G$ で微分して整理すると飽和領域の移動度  $\mu_{\text{sat}}$  に関する以下のような関係式が得られる。

$$\mu_{\text{sat}} = 2 \frac{L}{W} \frac{1}{C_{\text{i}}} \left( \frac{\partial \sqrt{I_{\text{D}}}}{\partial V_{\text{G}}} \right)^{2}$$

(13)

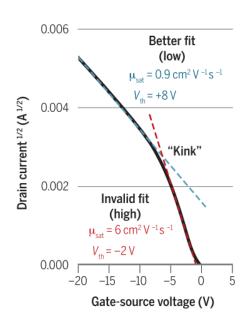

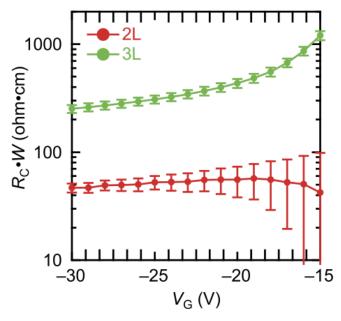

(10) 式と(13) 式から、OFET におけるキャリア移動度は伝達曲線の傾きから見積もることが でき、V<sub>th</sub>においても伝達曲線のx切片から求めることが出来ることがわかる。しかし、実際には 伝達曲線が  $V_G$ に対して線形にならない場合も多い。例えば、 $|V_G|$ を増加させていくと、ある電 圧を境に伝達曲線の傾きが緩やかになり、伝達曲線に kink-down と呼ばれるこぶのような部分が 観察される場合がある(図 1.4)[11]。この現象は gradual channel 近似においては無視されている 接触抵抗が要因であり、不自然な伝達曲線の挙動は接触抵抗の VG依存性を考えることによって説 明できることが報告されている[11][12]。接触抵抗とは、有機半導体と金属のヘテロ界面における ショットキー障壁由来の注入抵抗と、注入されたキャリアがチャネルに到達するまでの有機半導 体のバルク抵抗由来のアクセス抵抗の和である。Uemura らは、接触抵抗の  $V_G$  依存性を調べ、 | V<sub>G</sub> | が小さい領域ほどキャリアがチャネルを伝導する際の抵抗よりも接触抵抗が支配的となる ことを明らかにし、|Vg|が小さな領域の伝達曲線の傾きから移動度を見積もると、OFET本来の 移動度より高い値が得られるため移動度を過大評価してしまうことを報告している[11]。高移動度 OFET に関する論文の中にはこのような過大評価によって得られた値を報告しているものも少な くないため、注意を促すような報告も相次いでなされている[11][12][13]。また、Yamamura らは、 ボトムゲート - トップコンタクト型の OFET について、チャネルに用いている半導体膜の層数が 接触抵抗に影響を及ぼすことを報告している(図1.5)[14]。

図 1.4 kink-down のある伝達曲線の例[11]。

図 1.5 2 分子層(2L)および 3 分子層(3L)単結晶 OFET の接触抵抗の  $V_G$  依存性の比較。 3 分子層 OFET より 2 分子層 OFET の方が接触抵抗が小さいことが示されている [14]。

#### 1.1.3. 有機半導体材料

シリコン半導体が不純物ドーピングによって p 型半導体、n 型半導体を作り分けることが出来 るのに対し、有機半導体は一般に真性半導体であるため、蓄積されるキャリアが正孔(ホール) か電子かによって挙動が異なる。正孔が最高占有軌道 (HOMO) に注入されると p 型半導体、電 子が最低空軌道に注入されると n 型半導体の動作をする。電極の仕事関数とのエネルギー障壁が 大きいとキャリアは注入されにくくなるため、電極の仕事関数と有機半導体の HOMO が近い場 合、正孔の注入が起こりやすいために p型半導体に、電極の仕事関数と有機半導体の LUMO が近 い場合、電子の注入が起こりやすいために n 型半導体として動作する。そのため、キャリア注入 に用いる電極によって、OFET の挙動が変わることがあるという無機半導体にはない特徴がある。 例えば、一般にp型有機半導体として知られる pentacene (図 1.6(a)) は、HOMO が約-5.0 eV で、 LUMO が約 -3.2 eV であり、仕事関数が -5.1 eV ~ -4.9 eV の Au をソース / ドレイン電極材料 として用いると、HOMO へ正孔が注入され p 型半導体の挙動を示すが、仕事関数が -2.9 eV の Ca をソース / ドレイン電極材料として用いると、LUMO へ電子が注入され n 型半導体の挙動を することが報告されている[15]。このように p 型としても n 型としても駆動しうる材料もある が、バンドギャップの広い有機半導体では注入しやすいキャリアは片方に定まることが多い。そ のため、HOMO と RUMO の値から、p 型になりやすい、もしくは n 型になりやすい材料とい うように区別される。また、無機半導体が原子同士の共有結合で強く結びついているのに対し、 有機半導体は van der Waals 力によって集合体を形成しているという点でも大きく異なる。共有結 合を介して電気伝導が行われる無機半導体と異なり、有機半導体は分子間の π 電子雲の重なりに よって電気伝導が行われる。そのため、有機半導体分子間の軌道の重なりがキャリア伝導に大き な影響を与え、分子のパッキング構造を考慮することが大切となってくる。

本研究では低分子材料のみを扱っており、以下では低分子材料について述べる。

#### [p型半導体材料]

代表的な低分子 p 型有機半導体材料としては、複数のベンゼン環が縮合した化合物であるアセン系化合物の一つである pentacene (図 1.6 (a)) が挙げられる。前述のとおり、pentacene は用いる電極によって p 型、n 型両方の挙動をするが、HOMO 準位が約 -5.0 eV であることから、仕事関数が -5.1 eV  $\sim$  -4.9 eV の Au 電極からスムーズにキャリアとなるホールが注入されるため、真空蒸着法によって 3 cm²  $V^{-1}$  s $^{-1}$  という比較的高い移動度の多結晶膜が作製できることが報告されている[16]。同じくアセン系化合物の一種である rubrene(図 1.6 (b))は Physical Vapor Transport (PVT) 法で高品質の単結晶が作製可能であり、有機半導体の物性研究に広く用いられている。 rubrene の単結晶で有機半導体の Hall 効果が初めて観測され[17],[18]、有機半導体でもバンド伝導が行われていることが明らかとなった。また、rubrene の単結晶を用いて作製した OFET は 4 端子測定で 40 cm²  $V^{-1}$  s $^{-1}$  というこれまでに報告されている有機半導体の移動度で最も高い移動度を示したことが報告されている[19]。

キャリア伝導特性に優れた低分子単結晶の研究には前述の pentacene や rubrene が用いられて きたが、移動度の値としては実用レベルに達しているといえるものの、単結晶の作製に PVT 法な どの煩雑なプロセスが必要であることや、結晶の大きさも小さいなど、実デバイスへ応用するに はプロセス上の問題がある。そこで、6,13-bis(triisopropyl-silylethynyl) pentacene (TIPS-pentacene, 図 1.6 (c)) のような π 電子骨格に側鎖を導入することによって溶解性を向上させた有機半導体材料 が開発され、低温での溶液塗布プロセスが可能となった[20]。また、アルキル鎖を有する 2,7dioctyl[1]benzothieno[3,2- b][1]benzo-thiophene (C<sub>8</sub>-BTBT, ⊠ 1.6 (d)) ⋄ 2,9-didecyl-dinaphtho[2,3b:2',3'-f]thieno[3,2-b]thiophene (C10-DNTT, 図 1.6 (e)) も TIPS-pentacene 同様に有機溶媒に高い溶 解性を示し、C<sub>8</sub>-BTBT はダブルショットインクジェット法によって得られた単結晶で 16.4 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> [6]、C<sub>10</sub>-DNTT も 11 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> という高い移動度が報告されている[7]。溶液法は大気下で の低コストな製膜プロセスであることに加え、近年の塗布技術の発展によりキャリア伝導特性に 優れた低分子単結晶の二次元薄膜が作製可能となっており、印刷プロセスに適した材料開発が進 められていった。Mitsui らによって開発された 3,11-dinonyldinaphtho[2,3-d:2',3'-d]benzo[1,2-b:4,5b']dithiophene (C₀-DNBDT-NW, 図 1.6 (f)) は最大で約 100 cm²の面積に渡って単結晶薄膜を作製可 能であることが報告されている。また、性能面においても最高で約 12.5 cm² V-1 s-1 という高い移 動度を示すことが報告されている[9]。

(a) (b) (c)

$$A_{10} A_{10} A_$$

図 1.6 代表的な低分子 p 型有機半導体材料の構造式 (a) pentacene (b) rubrene (c) TIPS-pentacene (d) C<sub>8</sub>-BTBT (e) C<sub>10</sub>-DNTT (f) C<sub>9</sub>-DNBNT-NW

#### [n型半導体材料]

n 型半導体材料は LUMO 電位に注入された電子がキャリアとなって動作するが、電子は大気中の水や酸素でトラップされやすく、特性の劣化に繋がってしまうことがある[21]。 そのため、p型材料に比べて、大気下において安定で高移動度の n型有機半導体材料は報告例が少ない。一方、今後有機回路の発展には n型材料も不可欠である。

代表的な n 型有機半導体材料としては、fullerene ( $C_{60}$ 、図 1.7 (a)) がある。 $C_{60}$  は hot wall epitaxy という手法用いて製膜した蒸着膜で 6 cm²  $V^{-1}$  s  $^{-1}$  という高い移動度を示すことが報告されているが、大気中で不安定であることや溶解性が乏しいといった課題がある [22]。一方、hexadecafluorocopper phthalocyanine (F16CuPc、図 1.7 (b)) は、大気安定性は比較的高いが移動度が  $0.03 \text{ cm}^2 V^{-1} \text{ s}^{-1}$  程度と低い値になっている[23]。大気安定性と溶解性を兼ね備えた材料としては、 $\pi$  コアに二つのイミド基を導入した Perylene-diimide (PDI) 誘導体の一種である、N,N'-1H,1H-perfluorobutyl dicyanoperylenecarboxydi-imide (PDIF- $CN_2$ 、図 1.7 (c)) の塗布法で製膜した単結晶膜

で作製したデバイスが大気下で安定に動作し、 $1.3~\rm cm^2\,V^{-1}\,s^{-1}$  の移動度を示すことが報告されている[24]。また、同じく PDI 誘導体で、側鎖に分岐アルキル鎖を導入した N,N'-di((S)-1-methylpentyl)-1,7(6)-dicyano-perylene-3,4:9,10-bis-(dicarboxyimide) (PDI1MPCN2) (図 1.7 (d))が、溶液プロセスにより大気下で  $4~\rm cm^2\,V^{-1}\,s^{-1}$  を超える高い移動度を達成している[25]。 当研究室では、PDI の $\pi$ コア中の二つの炭化水素部位を窒素元素に置き換えることによって LUMO 準位を深めて、大気中での安定性を向上させた Benzo[de] isoquinolino[1,8-gh] quinolinetetracarboxylic diimide (BQQDI) 骨格が開発された。BQQDI 誘導体の一つである PhC2-BQQDI (図 1.7 (e))は、塗布法により製膜した単結晶膜で作製したデバイスが優れたデバイス安定性と  $3.0~\rm cm^2\,V^{-1}\,s^{-1}$  という高い移動度を示しており、Hall 効果の観測にも成功している[26][27]。

図 1.7 代表的な低分子 n 型有機半導体材料の構造式。 (a) C<sub>60</sub> (b) F16CuPc (c) PDIF-CN<sub>2</sub> (d) PDI1MPCN<sub>2</sub> (e) PhC<sub>2</sub>-BQQDI

#### 1.2. 有機半導体膜の塗布手法

有機半導体は溶媒に可溶な材料を用いることで、溶液プロセスによって大気下かつ比較的低温の環境で製膜が可能であるため、真空プロセスよりも安価に製膜が可能である。製膜された有機半導体はアモルファス、多結晶、単結晶など様々な構造をとり、この構造は塗布方法によって大きく異なる。溶液法の中ではスピンコート法が最も一般的に用いられている。スピンコート法では、半導体溶液を基板へ滴下した後に基板を高速で回転させることで、遠心力を用いて半導体膜が塗布される。スピンコート法の利点としては数分程度の短時間で比較的大面積に塗布することができることが挙げられるが、材料効率が悪いことに加え、低分子有機半導体材料では分子の配向が揃っていない薄膜が形成されてしまう場合がほとんどである。分子の配向が揃っていないと結晶粒界が多いため、電気的特性が悪くなるという問題がある。そのため、半導体材料本来の性能を最大限活かすためには分子の配向が揃った単結晶の成膜が可能な塗布方法が求められる。

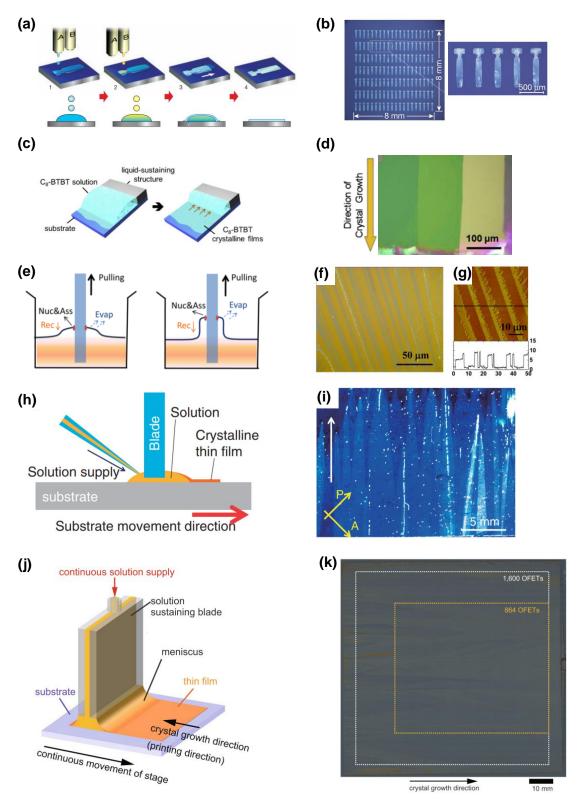

分子配向を制御しつつ溶液から単結晶性の半導体膜を作製する代表的な手法としては、ダブルショットインクジェット法(図 1.8 (a))やエッジキャスト法(図 1.8 (c))が挙げられる。ダブルショットインクジェット法では貧溶媒を滴下した後に半導体溶液を滴下し、貧溶媒と良溶媒の界面を利用して結晶成長させることで単結晶性の膜が得られる(図 1.8 (b))[6]。また、エッジキャスト法では、基板の上に半導体溶液を保持するためのガラスのブレードを置き、そこに半導体溶液を滴下することで溶液の乾燥方向をブレードに向かう方向に制御する。これにより半導体結晶の成長方向を制御し、単結晶膜を得ることができる(図 1.8 (d))[28]。

これらの方法では溶液から高品質な単結晶膜が得られる一方で、製膜可能な結晶のサイズがミリメートル以下に限られてしまうため、大面積ディスプレイや大規模集積回路といった広範囲にわたって結晶を製膜する必要があるデバイスの作製には適していない。そこで、エッジキャスト法と同様に溶液保持材と基板の間に形成されるメニスカスを利用した、大面積にわたった製膜を目指した塗布法の開発が盛んに行われていった。半導体溶液に基板を浸漬した後に基板を引き上げることで製膜する Dip-coating 法(図 1.8 (e)) [29]や、基板から少し浮かした状態で半導体溶液を保持したブレードを一方向に掃引することで製膜する Solution-shearing[30]法などが例として挙げられるが、図 1.8 (f-g) に示すような縞状の結晶が断続的に表れるような膜になるのがほとんどで、塗布エリア全面に渡って均質な単結晶膜を得ることは難しい。

当研究室で開発された連続エッジキャスト法(図 1.8 (h))は、基板から少し浮かせた高さに固定したブレードで半導体溶液を保持し、そこへシリンジから連続的に半導体溶液を供給しつつ基板を一方向に動かすことにより単結晶膜を長距離に渡って成長させる手法である(図 1.8 (i))。半導体溶液供給機構を持つために大面積の塗布が可能となっており、大面積デバイスの作製や量産プロセスにも適した手法であると言える[31]。また、溶液供給機構をシリンジからの一点供給ではなく、図 1.8 (j) に示すようにスリットにすることによって 9 cm 角の大面積で塗布エリア全面的に半導体単結晶膜の製造が可能となっている(図 1.8 (k))[9]。

図 1.8 (a) ダブルショットインクジェット法の模式図。 (b) ダブルショットインクジェット 法で製膜され  $C_8$ -BTBT 膜の顕微鏡像[6]。(c) エッジキャスト法の模式図。 (d) エッジキャスト法で製膜された  $C_8$ -BTBT 膜の偏光顕微鏡像[28]。 (e) Dip-coating 法の模式図。 (f) Dip-coating 法で製膜された TIPS-pentacene 膜の光学顕微鏡像と、(g) AFM 像 [29]。 (h) 連続エッジキャスト法の模式図。 (i) 連続エッジキャスト法で製膜した  $C_{10}$ -DNBDT-NW 膜の偏光顕微鏡像[31]。 (j) スリットから半導体溶液が供給される塗布装置の模式図。 (k) (j)に示した装置で塗布された 9 cm 角の  $C_9$ -DNBDT-NW 膜のレーザー共焦点顕微鏡像 [9]。

#### 1.3. 半導体膜の転写手法

1.2 節で述べたように有機半導体は大気下での溶液プロセスで安価に 100 cm<sup>2</sup> 程度の大面積に 単結晶膜が製膜可能になっている。しかし、1.1.1 項で示したように半導体膜は、基板、ゲート電 極、絶縁膜などからなる下地層の上に形成する必要があるために、デバイス作製において溶液プ ロセスならではの問題も起こってしまっている。例えば、溶液プロセスでは有機溶剤を用いるた めに溶剤耐性のない材料上へ塗布することはできず、フッ素系樹脂のような高撥水性材料は溶媒 を弾いてしまうため塗布できない。また、溶解度が低く、溶液プロセスで塗布するには高沸点溶 媒を用いる必要がある材料を用いる際には、100 ℃ 程度以上の環境下での塗布が必要となること がある。このとき、熱耐性の低いフィルム基板などを基板として用いることができず、フレキシ ブルデバイスに用いる基板が大幅に制限されてしまう。また、塗布膜の品質は塗布表面の状態に 大きく左右されてしまう。例えば、ゲート電極がパターンされた基板上に塗布する場合、電極の 段差を超える際に単結晶の成長が止まってしまうことがある。このような問題は、別基板上にあ らかじめ塗布した有機半導体塗布膜を目的の表面上に移送する転写手法を用いることが有効であ る。転写手法を用いると、高品質な単結晶膜を選択して目的の表面上に移送することが出来るた め、デバイスの性能や歩留まりの向上も期待できる。さらに、大面積単結晶膜を得ることや、安 定して目的の場所に単結晶膜を塗布することは難しいような半導体材料でも、転写手法を用いる ことでデバイス応用が可能になるという利点もある。

以下ではこれまでに研究されてきた転写手法について述べる。

#### 1.3.1. 犠牲層を用いた転写手法

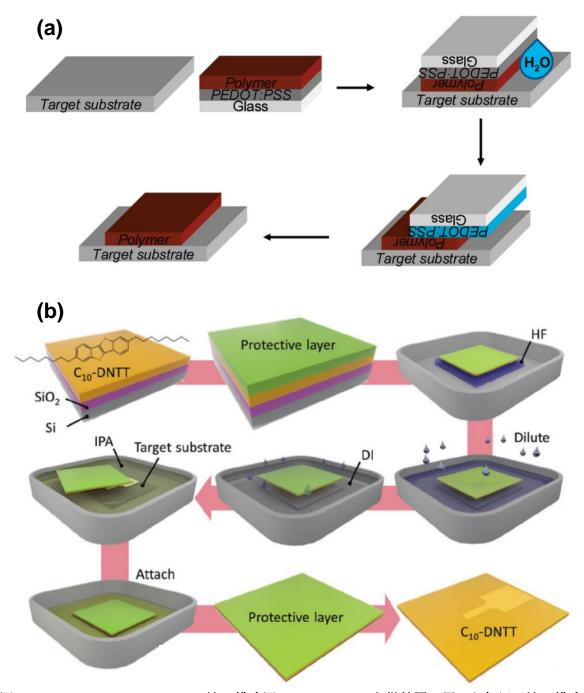

半導体膜の転写手法として、後に取り除く犠牲層を用いる方法が報告されている。Wei らによって開発された Contact Film Transfer 法は水に可溶な犠牲層を用いることで半導体膜を転写する手法である[32]。この手法では、水溶性ポリマーである PEDOT:PSS 上にポリマー有機半導体を塗布した基板を用意し、この基板をポリマー半導体膜が転写先基板に接するように置いた後に、基板の接している付近に水を滴下する。ここで犠牲層である PEDOT:PSS が溶解し、ポリマー半導体膜がターゲット基板に移るという手法である (図 1.9(a))。Peng らも犠牲層を溶解させる転写手法を開発している[33]。この手法では、p型低分子有機半導体の C10-DNTT の単結晶膜を SiO2/Si 基板上に製膜し、その上にフッ素系の保護膜を製膜する。その後、フッ酸にこれらを浸漬して SiO2 を溶解させることで水溶液上に浮かせた保護膜付きの半導体膜を、ターゲット基板を容器の底に設置した 2-propanol で満たされた容器に移す。続いて、2-propanol を蒸発させることで半導体膜と目的基板を密着させ、最後に保護膜を溶解させることで転写が完了される (図 1.9(b))。これらの手法は半導体膜に接している犠牲層を溶解するプロセスが必要であるが、界面に残る犠牲層を完全に除去することは難しく、電気的特性に影響を及ぼす可能性がある。

図 1.9 (a) Contact Film Transfer 法の模式図[32]。 (b) SiO<sub>2</sub> を犠牲層に用いた転写手法の模式 図[33]。

#### 1.3.2. 液面から半導体膜を転写する手法

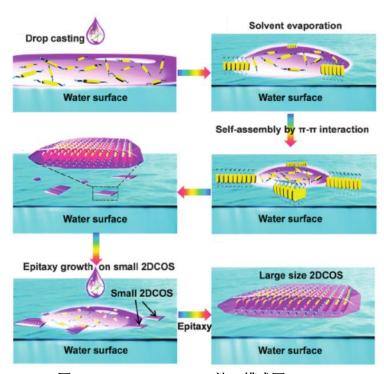

別の転写手法としては、Hu らによって開発された solution epitaxy 法が挙げられる[34]。この手法では半導体膜を水面上に形成する。水面に有機半導体溶液を滴下すると、水面に微結晶が形成される。ここにさらに溶液を供給すると水面の微結晶を核としてエピタキシャル成長し、数分子層からなる 2 次元結晶薄膜を水面上に形成することができる。最後にこの膜を転写先基板で掬い取ることで転写するという手法であるが、この手法では結晶成長が、半導体材料が水面上で自己集合していく過程に委ねられており、結晶の方位やサイズなどがコントロール出来ないため、量産に向いた手法であるとは言えない。

図 1.10 solution epitaxy 法の模式図[34]。

#### 1.3.3. 超親水性塗布基板を利用した転写手法

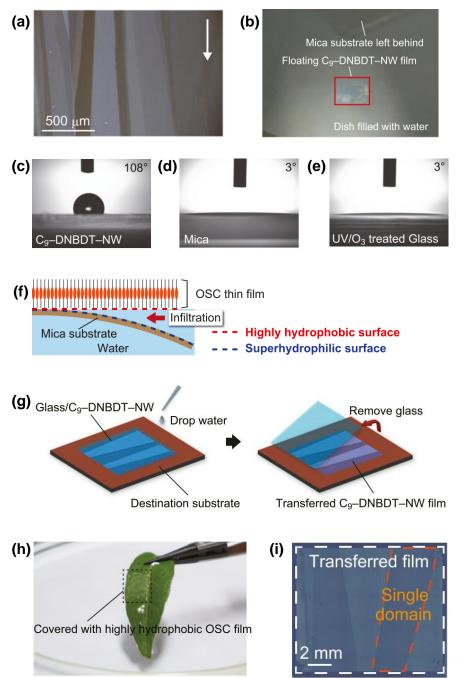

ここまで述べてきた半導体膜の転写手法は、犠牲層を完全に取り除くことが難しいこと、大面積プロセスへの応用が出来ないといった問題が残っており、産業応用可能な手法であるとは言えない。そこで当研究室では、有機半導体膜表面が高撥水性であることに着目し、超親水性の基板上に製膜した半導体膜と基板の界面に水を浸入させて半導体膜を剥離させる手法が開発された[10]。超親水性基板として天然マイカの劈開面を用い、その上に1.2項で述べた連続エッジキャスト法でC9-DNBDT-NW単結晶膜を製膜した(図1.11(a))基板を超純水で満たしたシャーレにゆっくりと浸漬することで、半導体膜をマイカ基板から剥離し、水に浮いた状態のC9-DNBDT-NW膜を得ることに成功している(図1.11(b))。このとき、半導体膜は、図1.11(f)に示すように超親水性基板と高撥水性半導体膜の間に水が侵入していき剥離が行われる。そのため、マイカと同じく超親水性を示す UV/O3 処理をしたガラス基板 (EAGLE XG® (Corning, Inc.)) を基板として用いても剥離が可能であることが確かめられている。これを利用して、UV/O3 処理をしたガラス基板上に半導体膜を製膜し、その基板を半導体膜と転写先の基板が接するように設置した後に両基板の

接点付近に水を滴下することで半導体膜を転写する手法を開発している (図 1.11 (g))。この手法 を用いることにより、半導体膜を葉の上(図 1.11 (h))や、高撥水表面を持つフッ素系高分子 CYTOP® (図 1.11 (i)) のような通常では半導体膜の塗布が困難な表面上に有機半導体単結晶膜を形成することに成功している。

図 1.11 (a) マイカ基板上に塗布した  $C_9$ -DNBDT-NW 膜の偏光顕微鏡像。 (b) マイカから剥離して水表面に浮いている  $C_9$ -DNBDT-NW 膜の写真。 (c)  $C_9$ -DNBDT-NW 膜、 (d) マイカ基板、 (e)  $UV/O_3$  処理をしたガラス基板表面の水の接触角。 (f) 水面での半導体膜剥離の模式図。 (g) 半導体膜転写手法の模式図。 (h) 表面に  $C_9$ -DNBDT-NW 膜が転写された葉の写真。 (i) CYTOP 上に転写された  $C_9$ -DNBDT-NW 膜のレーザー共焦点顕微鏡像[10]。

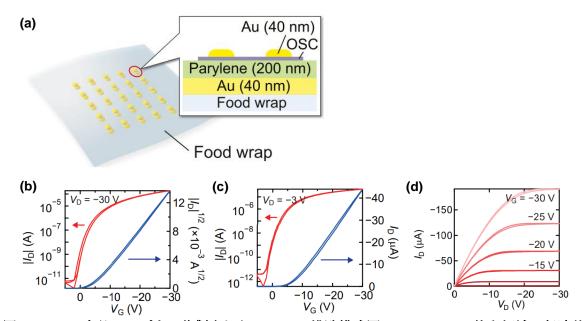

この転写手法を用いて食品ラップ上に作製された OFET は  $13~\rm{cm^2~V^{-1}~s^{-1}}$  程度の非常に高い特性を示しており、電気的特性を損なうことなく半導体単結晶膜を転写することができる手法であることが示されている(図  $1.12~\rm{(a-d)}$ )。また、本来は耐熱性や溶剤耐性の観点から食品ラップは有機半導体デバイスの支持基板としては不適であると考えられていたが、この結果に示すように高性能 OFET の作製に成功しており、本手法がフレキシブルデバイス等の有機半導体デバイスの基板選択の幅を広げる手法であることが分かる。

図 1.12 (a) 食品ラップ上に作製された OFET の構造模式図。 (b) OFET の飽和領域の伝達特性。 (c) OFET の線形領域の伝達特性。 (d) OFET の出力特性 (L/W=95 µm/335 µm)[10]。

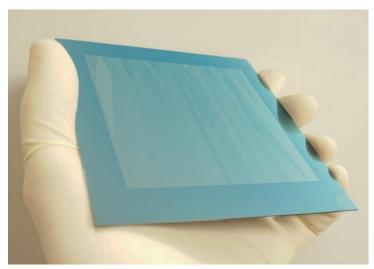

また、最近では  $8 \text{ cm} \times 8 \text{ cm}$  の大面積で  $C_9$ -DNBDT-NW 膜を転写することに成功しており、この手法は量産にも向いた産業応用可能な手法であると言える(図 1.13)。一方で、半導体膜の剥離には半導体膜塗布後に基板の超親水性が保たれていることが必要になるが、 $UV/O_3$  処理による水酸基の生成によって超親水化した基板は、 $150 \text{ }^{\circ}\text{C}$  程度の高温環境下においては親水性が失われて

図 1.13 8 cm×8 cm の大きさで転写された C<sub>9</sub>-DNBDT-NW 薄膜の写真。

しまう。そのため、有機半導体材料の種類によっては依然として制約が存在していた。例えば、高移動度を示す n 型有機半導体  $PhC_2$ –BQQDI[35]は、溶解度が低く高沸点溶媒を使用しているために 150  $^{\circ}$ C 程度の高温条件における成膜が必要となり、この転写手法を用いることは難しい。また、転写膜は、塗布膜の品質が重要であり、均一性が低い単結晶膜を転写すると、転写膜にクラックが入りやすいといった問題点も残っている。このクラックは、塗布膜が親水性基板から剥離される際に半導体膜にかかる応力が原因であると考えられるため、単結晶膜の転写では塗布膜の均一性が非常に重要なファクターであるといえる。

#### 1.4. 本研究の目的

1.3.3 節で述べた半導体膜の転写手法により、塗布法で製膜された極薄有機半導体単結晶膜をあらゆる表面に転写することが可能になり、積層デバイス作製時において半導体膜を溶液プロセスで製膜する際に発生する様々な問題を解決することが出来るようになった[10]。また、大面積での半導体膜転写も可能になっており、従来では作製しえなかった高機能デバイスの実現が期待される。しかし、この手法における塗布基板は  $UV/O_3$  処理による水酸基の生成によって超親水性としており、150  $^{\circ}$ C 程度の高温環境下においては親水性が失われてしまう。そのため、150  $^{\circ}$ C 程度以上の高温条件での塗布が必要な材料は転写することが出来ないという問題点があった。

そこで本研究では、幅広い半導体材料の利用を可能にするため、有機単結晶膜の新規転写手法の開発を目的とした。2章では、ガラス表面に微細な凹凸を形成することで構造的に超親水性を示す基板を開発し、高温環境下での安定性について調べた。さらに、エラストマー材料で作製した基板をリレー基板として新たに導入することで、転写膜に生じるクラックなどのダメージの低減を目指した。転写膜の性能を調べるために新規転写手法で得られた単結晶膜を用いて OFET を作製し、その特性を評価した。一方、半導体膜のパターニングは素子同士を電気的に分離するために、集積回路プロセスにおいて重要なプロセスのひとつである。これまでに有機半導体のパターニングにはフォトリソグラフィを用いた手法が使用されているが、エッチング時の溶媒やガスが半導体にダメージを与えてしまうといった問題が懸念されている。そこで3章では、本転写手法を応用することで、ダメージフリーのパターニング手法を開発した。さらに、本手法の有用性を確認するため、フィルム基板上において CMOS 論理回路を作製した。以上、本研究は、半導体膜の積層プロセスに付随する課題を解決するために新規転写手法を確立し、集積論理回路応用への道筋を示すものである。

### 第2章 有機単結晶薄膜の新規転写手法

1.3.3 節で述べたように、半導体膜の転写手法を用いた積層デバイス作製によって、有機半導体膜を製膜する際の下地層の制限を解決することが出来る。この転写手法においては、超親水性の基板上に撥水性の有機半導体膜を塗布し、基板/半導体膜界面に水を侵入させることで半導体膜の剥離を行う。この剥離の際には、塗布基板が超親水性であることが重要となる。しかし、先行研究における塗布基板は UV/O3 処理による水酸基の生成によって超親水性としており[10]、150 ℃程度の高温環境下においては親水性が失われてしまっていた。そのため、転写手法に用いることのできる有機半導体材料の種類は、溶液法による塗布中に基板の超親水が失われない、100 ℃程度の比較的低温で塗布することができる材料のみに限られてしまうという問題があった。そこで本章では幅広い半導体材料の利用を可能にするために開発した新規転写手法について述べる。まず、表面に微細な凹凸を形成することで、高温環境下においても構造的に安定に超親水性を保つ塗布基板、ナノすりガラス (Nano-ground glass: NGG) の開発を行った。さらに、エラストマー材料である polydimethylsiloxane (PDMS) を使用して作製したリレー基板を導入することにより転写膜のダメージ低減を目指した。本手法の確立により材料の制限がなくなり、p型だけでなくn型への利用も可能となることから、種々の論理回路デバイスへのプロセス応用が可能となる。

#### 2.1. 超親水性ナノすりガラス (NGG) の開発

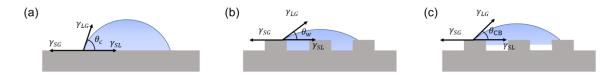

#### 2.1.1. 固体表面の濡れ性

まず、NGG の親水性の原理について述べる。固体表面の濡れ性は、材料の表面エネルギーと表面の粗さによって決定される。濡れ性の評価においては接触角の測定がよく用いられる。接触角は固体表面と、固体表面上の液滴のなす角 $\theta$ である。図 2.1 に示すように液体の気体との界面の表面張力を $\gamma_{LG}$ 、固体と気体界面の表面張力を $\gamma_{SG}$ 、固体と液体界面の表面張力を $\gamma_{SL}$ とすると、これらの間には、表面エネルギーと接触角の関係を示す Young-Dupre の (14) 式が成り立つ。

$$\gamma_{LG}\cos\theta = \gamma_{SG} - \gamma_{SL} \tag{14}$$

固体の表面エネルギーは、固体表面の官能基など化学構造によって決定される。そのため、自己組織化単分子膜(Self-Assembled Monolayer: SAM)などの表面修飾や、1.3.3 節で述べた UV/O<sub>3</sub> 処理などによって変化させることができる。しかし、これらの化学構造は基板の加熱などによって容易に変化しうる。そこで、本研究では表面の粗さが固体表面の濡れ性に及ぼす影響について注目した。

表面の粗さと濡れ性の関係を表すモデルとして、Wenzel モデル[36]と Cassie-Baxter モデル[37] が知られている。Wenzel モデルでは、全固体表面が濡れていることが前提とされており、粗面における見かけの接触角  $\theta_v$  と、平滑面における接触角  $\theta_c$  の関係式は (15) 式で表される[36]。

$$\cos \theta_W = r \cos \theta_c = r(\gamma_{SG} - \gamma_{SL}) / \gamma_{LG}$$

(15)

ここで、r は粗化率と呼ばれ、(16) 式で表される。

$$r = \frac{\text{(実効表面積)}}{\text{(見かけの表面積)}}$$

(16)

図 2.1 親水性表面における (a) 平滑面における表面の接触角、(b) Wenzel モデルでの粗面における表面の接触角、(c) Cassie-Baxter モデルでの粗面における表面の接触角。

一方、Cassie-Baxter モデルにおいては、表面の一部に空気が閉じ込められており、固体表面が不均一に濡れている場合を考慮している。Cassie-Baxter モデルにおける、全粗面における見かけの接触角  $\theta_{CB}$  と、平滑面における接触角  $\theta_{CB}$  の関係式は (17) 式で表される。

$$\cos \theta_{\rm CB} = f(r \cos \theta_c + 1) - 1 \tag{17}$$

ここで、f は液滴が固体と接している面積の割合である  $(0 < f \le 1)$ 。

これらの 2 つのモデルを比較すると、平滑面が親水性  $(0 < \theta_c < 90^\circ)$  の場合には、(15) 式と (17) 式より、

$$\cos \theta_w - \cos \theta_{CB} = (r \cos \theta_c + 1) (1 - f) \ge 0 \tag{18}$$

という関係が成り立つため、 $\cos \theta_w \ge \cos \theta_{CB}$  すなわち、 $\theta_w \le \theta_{CB}$  という関係が成り立つ。

Wenzel と Cassie-Baxter どちらのモデルの状態をとるかは材料や表面形状によっても異なる。 Miwa らは、撥水表面において、rの値が小さいときは Wenzel モデルに従いやすく、r の値が大きくなるにつれ Cassie-Baxter モデルが成り立つようになることを報告している[38]。また、液滴の形成方法によってもモデルは変わることがあり、Wenzel モデルの状態がエネルギー的に安定である場合であっても、液滴を静かにのせた場合は Cassie-Baxter 状態を取り、高い位置から落とすと Wenzel モデルをとることが報告されている[39]。

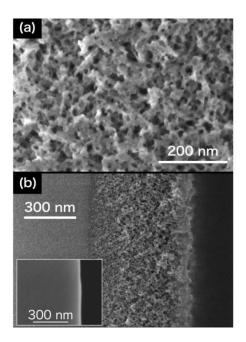

ここで、(15) 式と (17) 式は、r の値が大きくなるにつれ親水表面 ( $\theta_c$  < 90°) においては親水性が、疎水表面 ( $\theta_c$  > 90°) においては疎水性が促進されることを示している。本研究では、この親水性を促進する効果に着目した。この効果により超親水化された基板は、基板表面の粗さは表面の化学構造に比べて熱による変化が起こりにくいと考えられるため、より高温の環境下においても超親水性を保つことが期待される。実際に先行研究では、ソーダ石灰ガラスを 120 °C のNaHCO3 水溶液に浸漬させることで表面を化学的にエッチングし、階層性ナノ多孔質層 (hierarchically nanoporous layer : HNL) を形成した HNL ガラスが、同様の原理に基づいて大気下において基板表面の超親水性を 140 日以上の長期間保つことが報告されている[40]。しかし、HNL ガラスの表面には数百 nm の厚みに多孔質構造が三次元的に広がっており、有機半導体の結晶成長を阻害してしまうと考えられる。そこで本研究では、ソーダ石灰ガラスの表面を適度にエッチングすることで、超親水性の安定性と、有機半導体の単結晶成長に十分な平坦性を兼ね備えた表面を形成した NGG を作製した。

図 2.2 (a) HNL ガラス表面の SEM 像。 (b) HNL ガラスの断面 SEM 像。三次元的にスポンジ状の構造が形成されている[40]。

#### 2.1.2. NGG の作製手法

次に NGG の作製手法について述べる。まず、基板として厚さ  $0.7 \, \mathrm{mm}$  のソーダ石灰ガラスを用意し、10 分間純水で超音波洗浄して基板表面を洗浄した。その後、この基板を閉じた容器の中で  $80 \, ^{\circ}\mathrm{C}$  に加熱した NaHCO3 水溶液に 4 時間浸漬し、基板表面をエッチングした。NaHCO3 水溶液は、 $0.5 \, \mathrm{mol} \, \mathrm{L}^{-1}$  の濃度になるよう調製した。浸漬後、基板を NaHCO3 水溶液から取り出し、純水に  $10 \, \mathrm{分間浸漬}$ することで基板表面の NaHCO3 水溶液を取り除いた。その後基板を純水から取り出し、窒素でブローすることで基板上の純水を取り除き、乾燥させた。

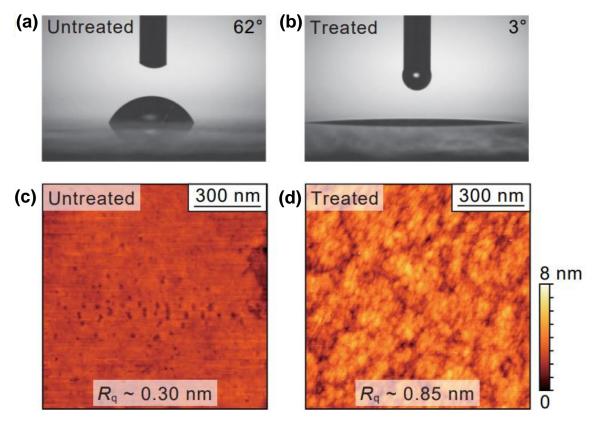

図 2.3 (a-b) に示す処理前後の基板に対する水の接触角の変化により、NaHCO3 水溶液への浸漬処理によって基板が超親水化されたことが分かる。次に、原子間力顕微鏡(Atomic Force Microscope:AFM)を用いて NGG と無処理のソーダ石灰ガラスの表面形状を比較した。AFM はエスアイアイ・ナノテクノロジー株式会社製の SPA400 を用いて、測定モードを Dynamic Force Mode (DFM) として行った。図 2.3 (c-d) に示す無処理ソーダ石灰ガラス、NGG それぞれの AFM 像より、NaHCO3 水溶液への浸漬処理により基板表面の構造が変化していることが分かる。面粗さの指標の一つである  $R_q$  の値についても、無処理のソーダ石灰ガラスが 0.30 nm、NGG が 0.85 nm となっており、NaHCO3 水溶液への浸漬処理により表面の粗さが増加したことが分かる。これにより、NGG は表面積が増加したことで超親水性になったと考えられる。本研究で用いた有機半導体材料の分子長が 1.8 nm 程度であるので、数分子層からなる有機半導体単結晶の成膜に十分な平坦性も兼ね備えていることが示唆された。ここで、ガラス表面がエッチングされる際の具体的な反応は明らかになっていないが、Fujima らはホウケイ酸ガラスを用いて、NaHCO3 水溶液への浸漬処理前後におけるガラス構成原子の含有量の変化を調べており、ケイ素、酸素原子が減少していない一方で、ホウ素、ナトリウム、カルシウム原子が減少していることを報告している[41]。ソー

ダ石灰ガラスの主成分はケイ素、酸素、ナトリウム、カルシウム原子であることから、今回の反応には、ナトリウム原子やカルシウム原子が関係していることが予想される。

図 2.3 (a) 未処理のソーダ石灰ガラス、および (b) NaHCO<sub>3</sub> 処理後のソーダ石灰ガラス表面 の水の接触角。(c) 未処理のソーダ石灰ガラス、および (b) NaHCO<sub>3</sub> 処理後のソーダ石 灰ガラス表面の AFM 像。

#### 2.1.3. 高温下における親水性の安定性評価

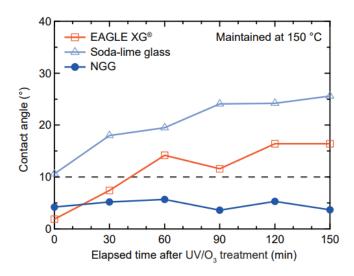

NGG 表面における超親水性の安定性を評価するため、加熱試験を行った。本研究で用いた有機半導体材料の典型的な塗布温度である 150 °C のホットプレート上で連続的に加熱し、基板の接触角の変化を測定した。まず、NGG と NaHCO3 水溶液処理を行っていないガラスを比較した。同じホットプレート上で、2.1.2 項で作製した NGG、無処理のソーダ石灰ガラス、1.3.3 項で述べた先行研究[10]における転写手法で用いられている無アルカリガラスである EAGLE XG® について、 $UV/O_3$  処理をして表面を親水化した後に加熱試験を行った。加熱試験の結果を図 2.4 に示す。図 2.4 から、 $UV/O_3$  処理ソーダ石灰ガラス、EAGLE XG® はともに 150 °C の環境下において 1 時間以内に親水性を失っており、一方で NGG は長時間超親水性を保持していることが分かる。有機半導体の塗布には 2 時間程度かかるため、NGG が超親水性塗布基板として適していることが分かる。

図 2.4 加熱試験における各基板表面の接触角の経時変化

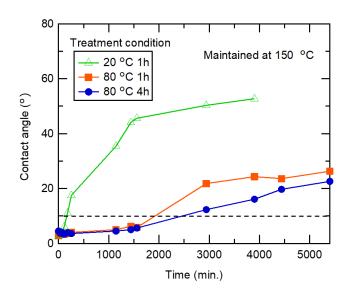

続いて、NGG の親水性の耐久性を評価した。今回は処理条件の違いによる耐久性の違いを確かめるために、NaHCO3 水溶液へ 20 °C で 1 時間、80 °C で 1 時間、80 °C で 4 時間浸漬した 3 種類のソーダ石灰ガラスを用意し、150 °C のホットプレート上で加熱試験を行った。加熱試験の結果を図 2.5 に示す。20 °C で 1 時間浸漬した基板は加熱試験開始時には超親水性を示していたものの、120 分程度経った頃に接触角が上がり始め、180 分後には 10 °以上まで上昇していた。一方、80 °C で 1 時間、80 °C で 4 時間浸漬した基板はともに少なくとも 24 時間後までは超親水性を保っており、その後接触角が上がっていっていることが分かった。

図 2.5 長時間の加熱試験における各基板表面の接触角の経時変化。

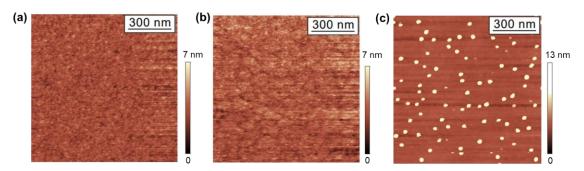

ここで、基板の接触角が上がってしまった原因を考察するために、AFM を用いて加熱試験前後の基板表面を観察した。図 2.6 に、NaHCO3 水溶液へ 20 °C で 1 時間浸漬した基板の加熱試験前の AFM 像 (a) 、 NaHCO3 水溶液へ 80 °C で 1 時間浸漬した基板の加熱試験前の AFM 像 (b) 、NaHCO3 水溶液へ 80 °C で 1 時間浸漬した基板の加熱試験後の AFM 像 (c) を示す。図 2.6 (a) と図 2.3 (c) を比較すると、20 °C での浸漬でもソーダ石灰ガラスの表面状態が変化していることが分かる。 $R_q$  の値は 0.70 nm と図 2.3 (d) で示した表面より表面粗さが小さいことが分かった。また、80 °C で 1 時間浸漬した基板表面の  $R_q$  の値は 0.76 nm となっており、浸漬条件によって表面粗さが変化することが分かった。図 2.6 (b) と図 2.6 (c) を比較すると、加熱試験により接触角が上がった基板には微小な粒が発生していることが分かる。この粒が原因で表面状態が変化し、この表面の  $R_q$  の値は 1.8 nm と増加している。表面積が増えたことによって 2.1.1 項で述べた Cassie-Baxter の寄与が大きくなり、接触角が上昇していったと考えられる。発生した粒が何によるものであるかは明らかになっておらず、今後原因の解明や除去法の開発について進めていく必要がある。

図 2.6 (a) NaHCO<sub>3</sub> 水溶液へ 20 °C で 1 時間浸漬した基板の加熱試験前の AFM 像。 (b) NaHCO<sub>3</sub> 水溶液へ 80 °C で 1 時間浸漬した基板の加熱試験前の AFM 像。 (c) NaHCO<sub>3</sub> 水溶液へ 80 °C で 1 時間浸漬した基板の加熱試験後の AFM 像。

#### 2.1.4. NGG 上への半導体膜の塗布

本研究室で開発された n 型有機半導体材料 benzo[de] isoquinolino[1,8-gh] quinoline bis(2-phenylethyl) imide (PhC2-BQQDI) は、高移動度かつ高い安定性を示すことが報告されているが[35]、 溶解性が低いことから 150 °C 程度の高温環境下での塗布が必要である。そこで、本手法の有用性を確認するため、本研究では PhC2-BQQDI を用いた。

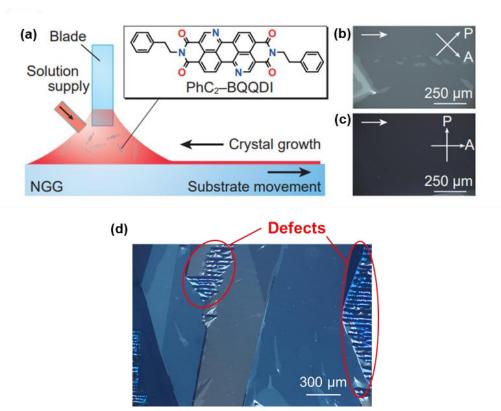

連続エッジキャスト法を用いて 2.1.2 項に述べた方法で作製した NGG 上に  $PhC_2$ –BQQDI の単結晶膜を作製した。塗布前に NGG を 10 分間  $UV/O_3$  処理し、基板表面を洗浄した。半導体溶液は  $PhC_2$ –BQQDI を 1-chloronaphthalene に 150 °C で溶解させ、0.02 wt%の濃度になるように調製した。 塗布時の基板温度は 148 °C とした。

有機単結晶膜を偏光顕微鏡によって観察した結果を図 2.7 (b), (c) に示す。結晶の成長方向がPolarizer (P) と Analyzer (A) のそれぞれと 45°の対角位にあるときには結晶の像が観察でき (図 2.7 (b))、P および A と平行もしくは直交すると一斉に消光している (図 2.7 (c)) ことから、高い配向性を有している単結晶膜が製膜できたことが分かる。これにより、NGG が有機半導体の単結晶に十分な平坦性を持ち合わせていることが示され、半導体膜転写手法のテンプレート基板としての有用性が示唆された。一方、PhC2-BQQDI は溶解度が低いことから塗布性に課題があり、塗布膜は図 2.7 (d) に示すように結晶の配列が揃っている単結晶膜の領域と、結晶の配列が揃っていない線状のアモルファスや、半導体が存在せず、ガラスがむき出しになっている欠陥の領域からなっている場合がほとんどである。このような膜は NGG に限らず、他の基板上へ塗布した際にも見られ、塗布条件を最適化することで改善されると考えられる。

図 2.7 (a) 連続エッジキャスト法による NGG 上への PhC2-BQQDI 膜の製膜模式図。(b) PhC2-BQQDI 単結晶膜の偏光顕微鏡による対角位、および (c) 消光位のときの観察写真。矢印は結晶成長方向を示す。(d) PhC2-BQQDI 膜の偏光顕微鏡による観察写真。単結晶からなる領域と欠陥からなる領域がある。

#### 2.1.5. NGG を用いた半導体膜の転写

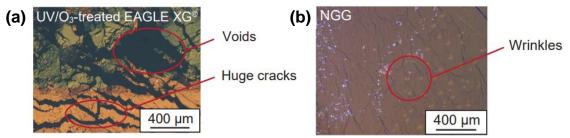

続いて、2.1.4 項で作製した NGG / 半導体膜基板を用いて半導体膜の転写を行った。NGG の効果を確認するための比較として、 $UV/O_3$  処理 EAGLE  $XG^{\$}$  ガラス上に  $PhC_2$ -BQQDI 膜を塗布した基板についても転写を行った。転写の手順は 1.3.3 項で述べたのと同様で[10]、 $UV/O_3$  処理 EAGLE  $XG^{\$}$  / 半導体膜基板もしくは NGG / 半導体膜基板を用意し、その基板を半導体膜と転写先の基板が接するように設置した後に両基板の接点付近に水を滴下することで半導体膜を転写した。図 2.8 にそれぞれ、 $UV/O_3$  処理 EAGLE  $XG^{\$}$  ガラスをテンプレート基板とした転写膜 (a) 、NGG をテンプレート基板とした転写した転写膜 (b) の偏光顕微鏡写真を示す。図 2.8 (a) の転写膜には大きなひび割れや、膜が転写されていない領域が見られる。これは図 2.4 で示した通り、塗布中にEAGLE  $XG^{\$}$  ガラスの親水性が失われてしまい、水が上手く半導体膜とガラスに入って行かず、剥離の際に膜に大きなダメージがかかってしまったためであると考えられる。一方、図 2.8 (b) からは塗布膜が全面的に転写されていることが分かり、高温下でも超親水性を保持する NGG を用いることで半導体膜とガラスの界面への水の侵入が促進されたことが示唆される。しかし、転写膜にはまだ細かいシワが多く見られ、電気的特性に悪影響を及ぼしてしまう。

ここで、このシワの原因について考察する。今回塗布に用いた半導体材料  $PhC_2$ -BQQDI は塗布性が悪く、転写に用いた  $PhC_2$ -BQQDI 膜は図 2.7 (d) に示したように結晶の配列が揃っている単

結晶膜の領域と、結晶の配列が揃っていない線状のアモルファスや、半導体が存在せず、ガラスがむき出しになっている欠陥の領域からなっている。この欠陥が原因で、単純にNGGを転写先基板の上に乗せるだけでは転写先基板との密着性が悪く、半導体膜の剥離時に膜に大きな機械的応力がかかってしまったことによりシワが発生したと考えられる。

本研究では、転写膜の膜質向上のため、エラストマー材料で作製したリレー基板を導入することで、転写時に半導体膜にかかる応力の低減を試みた。

図 2.8 (a) UV/O<sub>3</sub> 処理した EAGLE XG<sup>®</sup>ガラス、(b) NGG を用いて転写した PhC<sub>2</sub>-BQQDI 膜の偏光顕微鏡。

#### 2.2. PDMS リレー基板の導入

NGG の開発により、 $PhC_2$ -BQQDI のような 150 °C 程度の高温下での塗布が必要な半導体材料についても、基板の超親水性を保ったまま半導体膜を塗布することが可能となった。しかし、1.3.3 項で述べた転写手法[10]で NGG / 半導体膜基板から転写を行うと、半導体膜の剥離時に膜にかかる応力が原因で細かいシワが入ってしまい、電気的特性に悪影響を及ぼしてしまう。そこで本研究では、半導体膜の転写における剥離の際に膜にかかる応力が原因で発生する膜のダメージを低減するために、1.3.3 項で述べた転写手法[10]に加え、エラストマー材料のポリジメチルシロキサン (PDMS) を用いて作製したリレー基板を導入した。

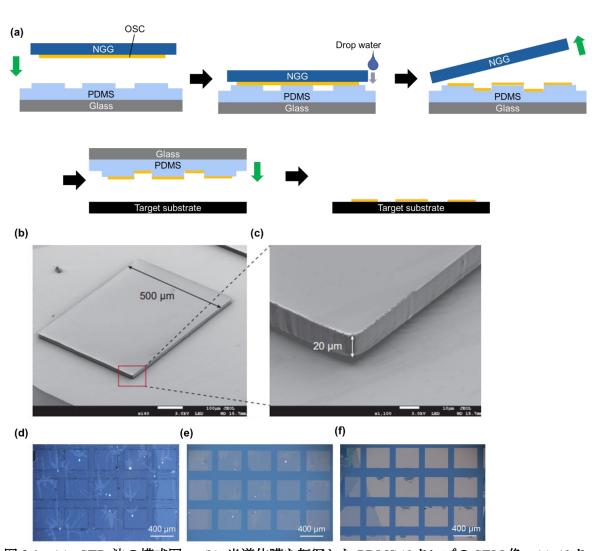

#### 2.2.1. NGG とリレー基板を用いた半導体膜の転写

まず、リレー基板を作製した。リレー基板は、厚さ  $0.7\,\mathrm{mm}$  の EAGLE  $\mathrm{XG}^{\otimes}$  ガラス上に、主剤 (SIM-360) と硬化剤 (CAT-360) (信越化学工業株式会社) を重量比で 10:1 となるように混合した PDMS 溶液を滴下し、 $150\,^{\circ}\mathrm{C}$  のホットプレート上で  $30\,$  分間加熱して硬化させて作製した。続いて、半導体膜の転写を行った。図  $2.9\,$  (a) に本手法の模式図を示す。まず、 $2.1.4\,$  項で作製した NGG/PhC2-BQQDI 基板を半導体膜が PDMS と接するようにリレー基板上に置き、上から軽く押し付けて PDMS と PhC2-BQQDI 膜を密着させた。その後、 $1.3.3\,$  項で述べた要領[10]で水を滴下することで半導体膜は NGG から剥離され、PDMS 上に転写された。その後、NGG を取り除き、リレー基板を半導体膜が転写先基板に接するように押し付けることで半導体膜を目的の基板に転写した。

次に、偏光顕微鏡を用いて転写膜を観察することにより、本手法においてリレー基板を導入することによる転写膜の変化を調べた。図 2.9 にそれぞれ、NGG をテンプレート基板とし、リレー基板を用いない手法で転写した転写膜 (b)、NGG をテンプレート基板とし、リレー基板を用いた手法で転写した転写膜 (c) の偏光顕微鏡写真を示す。図 2.9 (c) の転写膜には図 2.9 (b) に見られるような膜に生じる細かいシワは大幅に減少しており、柔らかく粘着性のある PDMS リレー基板は、ガラスからの半導体膜剥離前に半導体膜とリレー基板を密着させることで、剥離時に膜にかかる応力を減少させることができたと考えられる。

図 2.9 (a) NGG と PDMS リレー基板を用いた半導体膜転写手法の模式図。(b) NGG、(c) NGG と PDMS リレー基板を用いて転写した PhC2-BQQDI 膜の偏光顕微鏡。

#### 2.2.2. XRD 測定による転写膜の結晶性評価

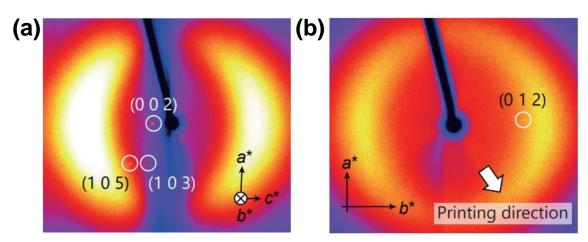

転写された半導体膜の結晶性を評価するため、XRD 測定を行った。2.1.4 項で作製した  $PhC_{2}$ -BQQDI 膜を製膜した NGG を用意し、2.2.1 項で述べた転写手法で厚さ  $30\,\mu m$  のガラス基板上に 半導体膜を転写して測定サンプルを作製した。測定は R-AXIS RAPID II(株式会社リガク)を用い、線源として  $CuK\alpha$  線( $\lambda=1.54187$  °A)を用いて室温で行った。図 2.10 ( $\alpha$ -b)にそれぞれ面内及び面外の XRD パターンを示す。 $\alpha$ -PhC2-BQQDI について報告されている、結晶のブリックワーク構造由来の回折ピーク[27]が観察されたことから、本手法は塗布膜の結晶性を損なうことなく転写が可能であることが示された。

図 2.10 転写した PhC2-BQQDI 膜の (a) 面内、(b) 面外の XRD パターン。

#### 2.2.3. n 型 OFET の作製

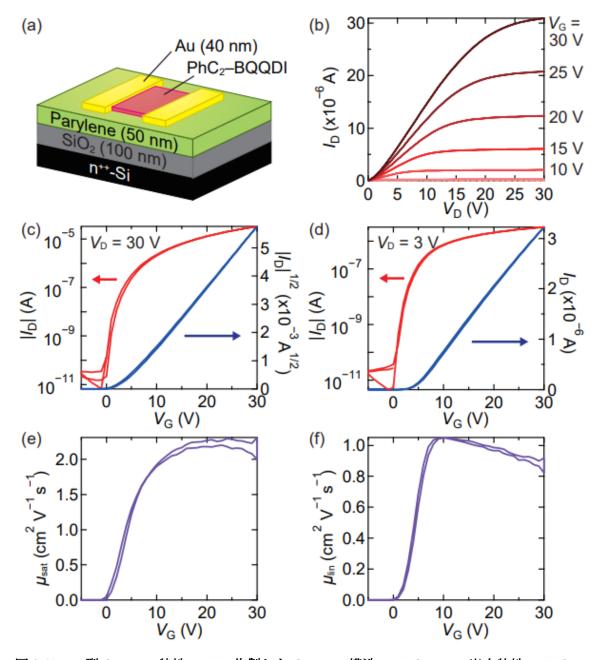

次に、転写した半導体膜が電気的特性を維持しているかを確認するために、 $PhC_2$ -BQQDI の転写膜を用いて OFET を作製した。作成手順を以下に示す。Si 基板上に熱酸化処理によって  $100\,\mathrm{nm}$  の  $SiO_2$  層を形成してある基板上を acetone、2-propanol (IPA) の順で 10 分間ずつ超音波洗浄し、 $200\,^\circ\mathrm{C}$  のホットプレート上で 10 分間加熱乾燥した。室温まで冷却した後に化学気相蒸着 (CVD) 法によって parylene (diX-SR: 第三化成株式会社) を  $SiO_2$  層上に  $50\,\mathrm{nm}$  製膜した。その上に 2.2.2 項で述べた手法を用いて  $PhC_2$ -BQQDI 膜を転写し、メタルマスクを置いたのちに Au を  $40\,\mathrm{nm}$  の厚みになるように真空蒸着してソース・ドレイン電極を形成した。電極形成後、回り込み電流を防ぐため、YAG レーザーで電極まわりの半導体をエッチングした。以上の操作により作成したボトムゲート・トップコンタクト型 OFET の構造を図 2.11 (a) に示す。 OFET の測定は Keythley4200-SCS 半導体パラメータアナライザを用いて大気下、暗室、室温で行った。移動度の算出には  $C_i$  =  $21.3\,\mathrm{nF}$  cm $^{-2}$  を用いた。

OFET の特性を図 2.11 (b-d) に示す。伝達特性はヒステリシスがほぼなく、 $V_G=0$  V 付近で立ち上がる理想的なトランジスタ特性を示し、 $10^5$  以上の良好な on/off 比が得られていることがわかる。移動度の値についても、飽和領域においては  $\mu_{\rm sat}=2.2~{\rm cm}^2~{\rm V}^{-1}~{\rm s}^{-1}$  と n 型有機半導体としては極めて高い値となっていた。この値は既報の転写をしていない  ${\rm PhC}_2$ -BQQDI の移動度と同等程度である[27]。また、この移動度の値に関しては図 2.11 (e) にみられるように、 $1.1.2~{\rm mov}$ で述べた kinkdown が見られないことから、十分に信頼できるものである[11][12][13]。線形領域における移動度は  $\mu_{\rm lin}=0.96~{\rm cm}^2~{\rm V}^{-1}~{\rm s}^{-1}$  と、飽和領域に比べて少し低下した値となっていた。これは、接触抵抗が大きいことが原因であると予想され、出力特性の  $V_D=0$  V 付近がわずかに S 字になっていることからも接触抵抗が大きいことが予想される。接触抵抗については、塗布条件を最適化して数分子層程度の単結晶膜を製膜することで低減することが可能であると考えられる[14]。これらの結果から本手法は n 型有機半導体単結晶膜が電気的特性を損なうことなく転写出来る手法であると考えられる。

図 2.11 n 型 OFET の特性。 (a) 作製した OFET の構造。 (b) OFET の出力特性。 (c) OFET の飽和領域、 (d) 線形領域の伝達特性。 ( $L/W=50~\mu m/100~\mu m$ ) (e) 飽和領域および、(f) 線形領域における移動度の  $V_G$  依存性。

#### 2.2.4. 転写の原理

ここで、本手法で用いた PDMS リレー基板から転写先基板への転写メカニズムについて考察する。PDMS を用いた転写法については様々な報告例があるが[42]、本手法は PDMS の粘着性と柔軟性に加え、表面エネルギーが低いことを利用した手法であると考えられる。表面エネルギーの値は算出方法や、評価時の条件によって異なるため一概に比較することは出来ないが、PDMS の表面エネルギーとして 19.8 mJ m<sup>-2</sup> という低い値が報告されている[43][44]。まず、NGG を PDMS に押し付ける際には、PDMS の粘着性と柔軟性を利用することで、NGG と PDMS を密着させている。これにより半導体膜を NGG から剥離する際に半導体膜にかかる応力を減少させることができ、半導体膜に大きなダメージを与えることなく PDMS への転写が可能となっていると考えられる。また、PDMS を転写先基板へ押し付けて転写する際には、PDMS の表面エネルギーが低いことを利用して半導体膜が PDMS から表面エネルギーが PDMS より高い転写先基板へ転写が出来ていると考えられる。

## 第3章 NGG を用いたマイクロスタンプ転写パターニング

第2章で述べたように、n型有機半導体においても p型有機半導体と同様に、転写手法を用いることで溶液法によって作製した単結晶膜を任意の場所に形成することが可能になった。そのため、様々な下地層をデバイス作製基板として使えるようになったが、半導体膜を実デバイスで応用する上では、各素子同士を電気的に分離するために半導体膜のパターニングが必要となる。一般的な半導体膜のパターニング手法としては、2.2.3 節で用いた YAG レーザーによるエッチングや、フォトリソグラフィにより保護パターンを形成し、不要部分の半導体膜をプラズマによるドライエッチングによって除去する手法が挙げられる[45]。これらの手法は高エネルギーのエッチングプロセスを必要とし、下地層へのダメージを考慮する必要がある。また、設備や材料のコストが高いという問題点もある。下地層へのダメージがないエッチングプロセスとしては、表面に凹凸構造を形成した PDMS スタンプと転写手法を用いて、パターニングした半導体膜を転写する手法がある[47]。この手法は物理的な破断でパターニングするため、転写することができれば、材料に関わらず用いることができる。本研究ではこの手法に NGG を用いることで、様々な材料をパターニングしつつ転写することを可能にした。続いて、この手法を用いて p型、n型の有機半導体膜を転写、かつパターニングして、有機 CMOS 論理素子への応用に成功した。

#### 3.1. マイクロスタンプ転写パターニング (µSTP) 法

#### 3.1.1. パターニングプロセス

マイクロスタンプ転写パターニング (Microstamp transfer patterning:  $\mu$ STP) 法は PDMS スタンプ表面に凹凸を形成することで半導体膜をスタンプ上へ転写した際に物理的に破断し、その後転写することで凸部のみが転写されパターニングされるという手法である。本手法の模式図を図 3.1 (a) に示す。PDMS スタンプに凹凸パターンを形成するにあたり、ネガ型の永久レジスト SU-8 3025 (日本化薬株式会社)を用いてモールドの作製を行った。EAGLE XG® ガラス基板に UV/O3 処理を施して濡れ性を向上した後、SU-8 3025 を厚さ 20  $\mu$ m となるようにスピンコートして 95  $^{\circ}$ C のホットプレート上で 10 分間プリベイクした。フォトマスク越しに露光した後、65  $^{\circ}$ C で 1 分間、95  $^{\circ}$ C で 3 分間のポストベイクを行った。その後、Propylene glycol methyl ether acetate (PGMEA)で現像し、2-propanol でリンスして乾燥させた後に、170  $^{\circ}$ C のホットプレート上で 30 分間加熱することで完全に加熱硬化させた。続いて、PDMS との剥離性を向上させるための離型層を形成してSU-8 モールドを作製した。続いて SU-8 上に PDMS の主剤 SIM-360 及び硬化剤 CAT-360 を重量比で 10:1 となるように混合した溶液を滴下して、UV/O3 処理を行った EAGLE XG® ガラス基板を被せて 4 時間以上静置した。十分に硬化させた後、PDMS / EAGLE XG® ガラス基板を SU-8 モールドから剥離し、150  $^{\circ}$ C のホットプレート上で 30 分加熱して PDMS を完全に硬化させ、PDMS スタンプを作製した。

続いて、2.1.4 項で述べた手法で、NGG 上に半導体単結晶膜を連続エッジキャスト法で製膜した。半導体膜/NGG 基板を半導体膜が PDMS スタンプに密着するよう設置し、基板の端部に水を滴下すると、半導体膜が PDMS 上に転写された。この時に転写された膜の様子を観察するため、SEM で観察した。SEM による観察は JSM-7800F Prime (日本電子株式会社) を用いて行い、 加速

本手法は水のみを用いているため半導体膜や下地層には基本的にはダメージがなく、またスタンプは繰り返し用いることが可能であるためコスト面においても有利な手法であると言える。

図 3.1 (a)  $\mu$ STP 法の模式図。 (b) 半導体膜を転写した PDMS スタンプの SEM 像。(c) スタンプ段差部の拡大図。(d) スタンプ上に転写された半導体膜の偏光顕微鏡写真。(e)  $\mu$ STP 法でパターニングされた  $C_9$ -DNBDT-NW 膜と、(f) Ph $C_2$ -BQQDI 膜。

## 3.1.2. 解像度および大面積応用

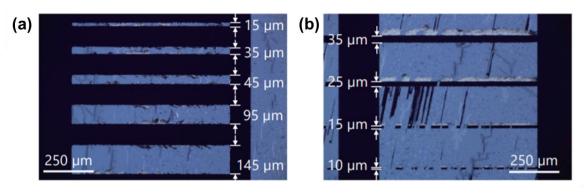

μSTP 法の半導体膜パターニング解像度を確認した。本実験では安定して大面積の単結晶膜が製膜できる  $C_9$ –DNBDT–NW を、表面を  $\beta$ -PTS 処理した  $SiO_2/Si$  基板上に  $\mu$ STP 法で転写してパターニング解像度を確認した。パターンされた  $C_9$ –DNBDT–NW 膜の偏光顕微鏡写真を図 3.2 (a-b) に示す。図 3.2 (a) から、パターニング領域端の数  $\mu$ m の領域は一部膜が剥がれている部分はあるものの、 $15\,\mu$ m のパターンも視認でき、数  $10\,\mu$ m 程度の細さのパターンまで形成可能であると考えられる。剥がれている部分に関しては、モールドやスタンプ作製の最適化や、半導体膜の押し付ける圧力等を最適化することにより、改善可能であると考えられる。一方、半導体膜同士の間隔については、図 3.2 (b) から  $35\,\mu$ m では幅  $800\,\mu$ m に対して完全に切断できており、  $25\,\mu$ m より細くなると一部切断できていない箇所があるが、こちらについても適切な設計によって、 $30\,\mu$ m 程度までのパターニング制度はあると考えられる。今後スタンプの高さや半導体膜を押し付ける圧力等のパラメータや、モールド、スタンプを適切に作製することでさらなる解像度の向上も可能であると考えられる。

現状の有機 CMOS 回路の集積度を踏まえると、本手法でのパターニング精度は現状で十分に回路応用可能であるといえる。

図 3.2 (a)、(b) µSTP 法でパターンされた C<sub>9</sub>-DNBDT-NW 膜。

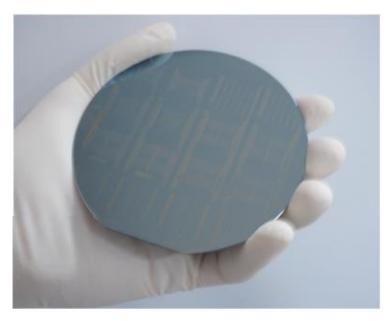

続いて、本手法を大面積へ応用できるかを確認した。NGG 上に連続エッジキャスト法で 9 cm 角の  $C_9$ –DNBDT–NW 膜を塗布し、2.2.3 項で述べた手順と同様にして parylene (diX-SR) を製膜した  $SiO_2/Si$  基板上に  $\mu$ STP 法で転写を行ったところ、4 inch ウエハ上に一度にパターニングした半導体膜を転写することに成功した(図 3.3)。また、大面積での転写は 1.3.3 項で述べたようにすでに実現されているが、2.1.5 項で述べたように転写膜の膜質は半導体膜を塗布した後の塗布基板の親水性に大きく左右される。そのため、今回は NGG を用いることで、より高品質の半導体膜の転写パターニングに成功している。これにより、本手法は量産化に有益であることが確認された。

図 3.3 4 inch のサイズのウエハ上に µSTP 法でパターンされた C9-DNBDT-NW 膜。

### 3.1.3. 半導体膜の評価

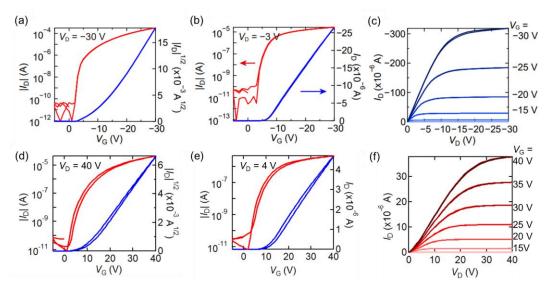

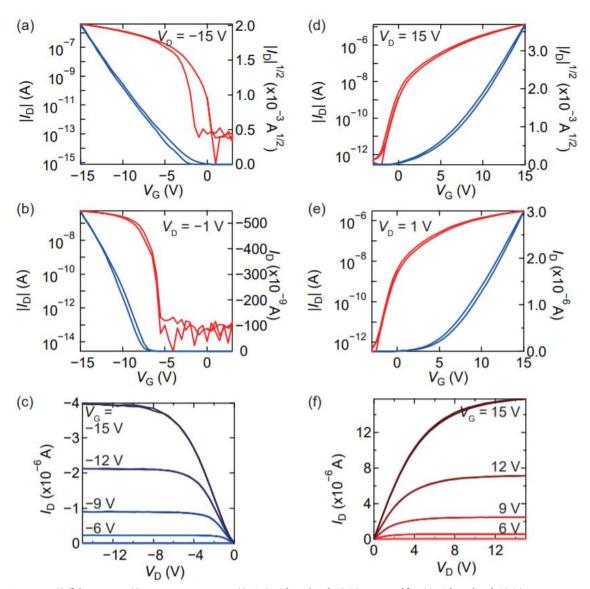

次に、 $\mu$ STP 法で転写した半導体膜が電気的特性を維持しているかを確認するために、 $C_9$ -DNBDT-NW と Ph $C_2$ -BQQDI の転写膜を用いて OFET を作製した。2.2.3 項で述べた手順と同様にして parylene (diX-SR)を製膜した SiO<sub>2</sub>/Si 基板上に $\mu$ STP 法で  $C_9$ -DNBDT-NW 膜もしくは Ph $C_2$ -BQQDI 膜を転写した。 転写後、 $80\,^{\circ}$ C の真空オーブン内で 10 時間真空乾燥を行い、メタルマスクを置いたのちに Au を  $40\,\mathrm{nm}$  の厚みになるように真空蒸着してソース・ドレイン電極を形成して OFET の作製を完了した。その後  $60\,^{\circ}$ C で 10 時間真空乾燥を行い、トランジスタ特性を測定した。OFET の測定は Keythley4200-SCS 半導体パラメータアナライザを用いて大気下、暗室、室温で行った。移動度の算出には  $C_i$ =21 nF cm $^2$  を用いた。OFET の特性を図 3.4 (a-f) に示す。 p型 OFET についてはヒステリシスが小さく、移動度も飽和領域で  $17\,\mathrm{cm}^2\,\mathrm{V}^{-1}\,\mathrm{s}^{-1}$ 、線形領域で  $13\,\mathrm{cm}^2\,\mathrm{V}^{-1}\,\mathrm{s}^{-1}$  という非常に高い値が見積もられた。また、n型 OFET の移動度については飽和領域で  $2.0\,\mathrm{cm}^2\,\mathrm{V}^{-1}\,\mathrm{s}^{-1}$ 、線形領域で  $0.86\,\mathrm{cm}^2\,\mathrm{V}^{-1}\,\mathrm{s}^{-1}$  という値が見積もられた。  $2.2.3\,\mathrm{g}$ で作製した n型 OFET と同様に線形領域の移動度が少し低いが、これは接触抵抗が大きいことが原因であると予想され、塗布条件を最適化して数分子層程度の単結晶膜を製膜することで低減することが可能であると考えられる[14]。よって、 $\mu$ STP 法は用いる材料に関わらず半導体膜や下地層にダメージを与えない手法であり、OFET 作製に適した手法であるといえる。

図 3.4  $\mu$ STP 法でパターンされた  $C_9$ -DNBDT-NW 膜で作製した OFET の (a) 線形領域の伝達特性、 (b) 飽和領域の伝達特性、 (c) 出力特性 ( $L/W=100~\mu m/400~\mu m$ )と、 $PhC_2$ -BQQDI 膜で作製した OFET の (d) 線形領域の伝達特性、 (e) 飽和領域の伝達特性、 (f) 出力特性。 ( $L/W=50~\mu m/100~\mu m$ )

## 3.2. CMOS 論理回路応用

$\mu$ STP 法は半導体膜を PDMS スタンプ上に転写し、スタンプを押し付けることにより、目的の基板に熱や溶剤の影響を与えることなく半導体膜を移送する方法であるので、基板や下地層に多くの材料を利用可能である。また、半導体材料においても、水への耐性があること、スタンプ上に転写することで半導体膜が破断可能な薄膜が製膜可能であること程度の要件しかなく、多くの半導体材料に適応可能な方法であるといえる。さらに、リソグラフィーなどの工程を必要とせずに半導体膜のパターニングが可能であることから、簡便かつ安価にデバイス作製が可能な手法であると期待される。そこで、本研究では  $\mu$ STP 法フィルム基板上での有機 CMOS 論理回路の作製に取り組んだ。

#### 3.2.1. CMOS 論理回路

CMOS (Complementary Metal Oxide Semiconductor) 論理回路は p 型と n 型のトランジスタ を相補的に組み合わせて作られる論理回路のことである。nMOS 回路および pMOS 回路は常に電流が流れてしまうのに対し、CMOS 回路はスイッチングの際以外は基本的に電流が流れないため、消費電力を低くすることが出来る。電力消費による温度上昇によって、デバイス破壊や特性劣化を起こしてしまうため、論理回路の低消費電力化は高集積化を達成するために非常に重要となってくる。CMOS 論理回路は "0" と "1" で演算を行い、これはそれぞれ電圧が低い "L" (Low) と電圧が高い "H" (High) 状態が対応している。論理回路の基本要素は NOT ゲート、NAND ゲート、NOR ゲートの3つの理論ゲートからなり、これらを組み合わせて様々な演算を表現する。以下ではそれらの動作原理について述べる。

#### 【NOT ゲート】

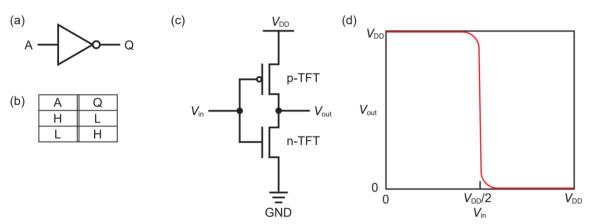

NOT ゲートはインバータとも呼ばれ、図 3.5 (a)に示す MIL 記号と呼ばれる記号で表される。図 3.5 (b) の真理値表に示すように、入力に対して反対を返す素子である。NOT ゲートの回路図を図 3.5 (c) に示す。NOT ゲートは p 型のトランジスタと n 型のトランジスターつずつで構成され、それぞれを直列に繋ぎ、その箇所が出力電圧  $V_{\rm out}$  となる。そして、p 型と n 型両方のトランジスタのゲート電極を繋ぎ、その箇所が入力電圧  $V_{\rm in}$  となる。そして p 型のソース電極に高電位側の  $V_{\rm DD}$ , n 型のソース電極はグランド (GND) に接続する。ここでは簡単のため、入力電圧に"H"を入力するときには  $V_{\rm in}$  =  $V_{\rm DD}$ 、"L"を入力するときには  $V_{\rm in}$  = 0 V (GND) とすることにし、動作原理を説明する。

まず  $V_{\rm in}$  に "L" の信号を入力したときを考える。このとき、p 型のトランジスタのソース電極電圧  $V_{\rm DD}$  はゲート電極電圧  $V_{\rm in}$  に対して高電位になっている。そのため、ホールがチャネルに注入され、p 型トランジスタは ON 状態になる。一方、n 型トランジスタのソース電極は GND に繋いであるため、n 型トランジスタのゲート電極電圧とソース電極電圧はともに 0 V となりチャネルにキャリアが注入されず、n 型トランジスタは OFF 状態となる。このとき、n 型トランジスタは非常に高抵抗な抵抗素子ととらえることができ、 $V_{\rm out}$  は  $V_{\rm DD}$  と等電位すなわち "H" を返す。

一方、 $V_{\rm in}$  に "H" の信号を入力したときを考える。このとき、p 型のトランジスタのソース電極電圧  $V_{\rm DD}$  とゲート電極電圧  $V_{\rm in}$  は等電位になっている。そのため、ホールがチャネルに注入さ

れず、p 型トランジスタは OFF 状態になる。一方、n 型トランジスタのソース電極は GND に繋いであるため 0 V、n 型トランジスタのゲート電極電圧は  $V_{\rm in}$  であるためゲート電極電圧がソース電極電圧に対して相対的に高電圧になっているためにチャネルにキャリアが蓄積され、n 型トランジスタは ON 状態となる。このとき、p 型トランジスタは非常に高抵抗な抵抗素子ととらえることができ、 $V_{\rm out}$  は GND と等電位すなわち "L" を返す。よって NOT ゲートは図 3.5 (b) の真理値表に示すように動作する。

なお、後に述べる NOR 、NAND ゲートにおいても p 型トランジスタは高電位 ( $V_{DD}$ ) 側に、n 型トランジスタは GND 側に接続されており、 $V_{in}$  に "L" が入力されたときは p 型は ON 、n 型は OFF 状態に、 $V_{in}$  に "H" が入力されたときは p 型は OFF、n 型は ON になる。

図 3.5 (d) に NOT ゲートの典型的な伝達特性を示す。p 型と n 型の抵抗値が等しくなると、この前後で  $V_{\text{out}}$  が急峻に切り替わる。この切り替わりの傾きの絶対値を  $G_{\text{ain}}$  と呼び、インバータの重要な指標である。図 3.5 (d) に示すように  $V_{\text{in}}$  が厳密に 0 あるいは  $V_{\text{DD}}$  でなくても、それぞれ  $V_{\text{DD}}$  あるいは 0 V が出力される範囲が見て取れる。よって、 $V_{\text{in}}$  が  $V_{\text{DD}}/2$  のときに  $V_{\text{out}}$  が切り替わるように回路のパターン設計の際に p 型、n 型それぞれのトランジスタのバランスを取ることでノイズに強い回路が作製可能となる。また、 $V_{\text{DD}}$  から  $G_{\text{ND}}$  に流れる電流を 貫通電流 ( $I_{\text{supply}}$ ) と呼ぶ。理想的には信号が切り替わるときにのみ貫通電流が流れる。

図 3.5 NOT ゲートの (a) MIL 記号、 (b) 真理値表、 (c) 回路図、 (d) 典型的な伝達特性。

#### 【NOR ゲート】

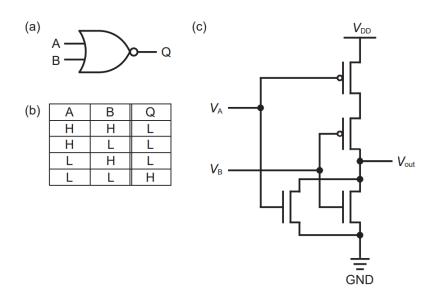

図 3.6 に 2 入力の NOR ゲートの MIL 記号 (a)、真理値表 (b)、回路図 (c) を示す。NOR ゲートは p 型 と n 型のトランジスタをそれぞれ 2 個ずつ用いて構成される。二つの p 型トランジスタは直列で n 型トランジスタは並列に接続されている。 p 型と n 型トランジスターつずつのゲート電極をそれぞれ接続し、これが二つの入力 ( $V_A$ ,  $V_B$ ) となる。直列の p 型トランジスタと並列の n 型トランジスタの直列に接続されている箇所が出力 ( $V_{out}$ ) となる。

両方の p 型トランジスタが ON つまり、 $V_A$  と  $V_B$  がともに "L" が入力されたときにのみ二 つの合成抵抗が低くなり、このとき n 型トランジスタはどちらも OFF になるため、 $V_{out}$  は  $V_{DD}$  と等電位すなわち "H" を返す。それ以外の場合にはどちらかの p 型トランジスタが OFF であ

り、n 型トランジスタは少なくとも一方は ON になるため、 $V_{out}$  は GND と等電位すなわち "L" を返す。よって NOR ゲートは図 3.6 (b) の真理値表に示すように動作する。

図 3.6 NOR ゲートの (a) MIL 記号、 (b) 真理値表、 (c) 回路図。

### 【NAND ゲート】

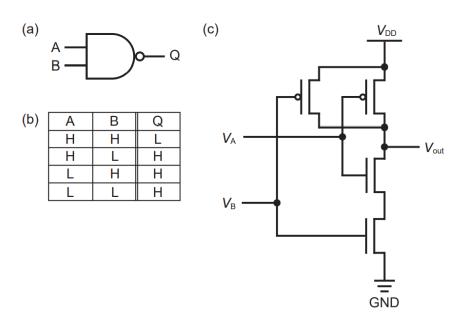

図 3.7 に 2 入力の NAND ゲートの MIL 記号 (a) 、真理値表 (b) 、回路図 (c) を示す。NAND ゲートも NOR ゲートと同様に p型 と n型のトランジスタをそれぞれ 2 個ずつ用いて構成される。二つの p型トランジスタは並列で n型トランジスタは直列に接続されている。 p型と n型トランジスターつずつのゲート電極をそれぞれ接続し、これが二つの入力 ( $V_A$ ,  $V_B$ ) となる。並列の p型トランジスタと直列の n型トランジスタの直列に接続されている箇所が出力 ( $V_{out}$ ) となる。

両方の p 型トランジスタが OFF つまり、 $V_A$  と  $V_B$  がともに "H" が入力されたときにのみ二 つの合成抵抗が高くなり、このとき n 型トランジスタはどちらも ON になるため、 $V_{out}$  は GND と等電位すなわち "L" を返す。それ以外の場合には p 型トランジスタの少なくとも一方は ON であり、n 型トランジスタは少なくとも一方は OFF になるため、 $V_{out}$  は  $V_{DD}$  と等電位すなわち "H" を返す。よって NAND ゲートは図 3.7 (b) の真理値表に示すように動作する。

図 3.7 NAND ゲートの (a) MIL 記号、 (b) 真理値表、 (c) 回路図。

### 3.2.2. CMOS 論理回路の作製

CMOS 論理回路の作製手順を以下に述べる。

# 【ゲート電極、ゲート絶縁膜の成膜】

まず、基板として厚さ 125  $\mu$ m の poly(ethylene 2,6-naphthalate) (PEN) 基板(テオネックス Q65HA:帝人デュポンフィルム株式会社)を用意した。PEN 基板は加熱によって表面にオリゴマーが発生し、絶縁層のピンホール等の原因となってしまうため、保護フィルムを剥離した後、150  $^{\circ}$ C のホットプレート上で 3 時間加熱し、acetone、2-propanol (IPA) の順で 10 分間ずつ超音波洗浄することで表面に生じるオリゴマーをあらかじめ取り除いた。続いて、30 nm の Al を PEN 基板全面に電子線蒸着によって真空蒸着した。蒸着条件は真空度  $10^{-4}$  Pa 程度,蒸着速度  $10^{-4}$  Pa 程度で行った。続いて、フォトリソグラフィでゲート電極のパターニングを行った。Al 膜の上にポジ型フォトレジストである AZ 5214 E (MicroChemicals) をスピンコート法で塗布し、 $105^{\circ}$ C のホットプレート上で 70 秒間加熱した。その後マスクレス露光機 (MLA 150 Maskless Aligner: Heidelberg Instruments) で紫外光 ( $\lambda$ =375 nm) を照射し、NMD-3 2.38%(東京応化工業株式会社)、超純水の順に浸漬することで電極を形成したい部分のフォトレジストを除去した。続いて、混酸 Al エッチング液(関東化学株式会社)に浸漬することで Al のウェットエッチングを行い、最後に AZ 100 Remover を用いてレジストを剥離した。続いて、UV/O3 処理を 5 分間することによってレジスト残渣を取り除き、CVD 法によって厚さ 120 nm の parylene (diX-SR) を製膜した。

### 【µSTP 法を用いた p型、n型半導体膜の形成】

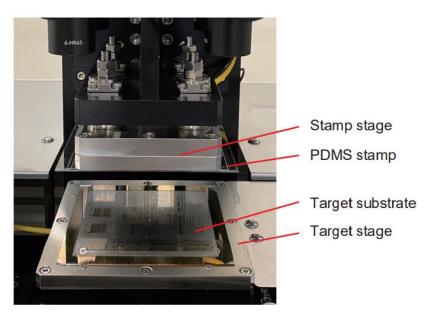

続いて、μSTP 法を用いて p 型、n 型半導体膜をゲート電極、ゲート絶縁膜を形成した PEN 基 板上に形成した。まず、3.1.1 節で述べたのと同様の方法で p 型用、n 型用それぞれのパターンの PDMS スタンプを作製した。p 型半導体は C₀-DNBDT-NW、n 型半導体は PhC₂-BQQDI を用い、 2.1.4 節で述べたのと同様の方法で、連続エッジキャスト法によって NGG 上にそれぞれの単結晶 膜の塗布を行った。それぞれの半導体膜/NGG 基板を p 型用、n 型用 PDMS スタンプ上に設置 して 30 wt% エタノール水溶液を滴下して半導体膜をスタンプ上に転写した。スタンプから目的 の基板へ転写する際には、下層に対して適切な位置に積層していくアライメントが重要となる。 本研究では、μSTP 法用に新たに設計された装置を用いて半導体膜をゲート電極に対して適切な 位置に転写できるようにした。図 3.8 に装置の写真を示す。下側にターゲット基板、上側に半導 体膜を転写した PDMS スタンプをセットする。スタンプ吸着ステージの四隅に設置してあるカ メラでゲート電極層とスタンプそれぞれに用意してあるアライメントマークを観察しながらター ゲット基板の位置を調整し、ロードセルを用いて荷重を制御しながらスタンプとターゲット基板 を密着させる。ここで、転写圧が不十分であるとスタンプからターゲット基板上に完全に半導体 膜が転写されず、過剰であると凹部も転写されてしまうため、調整する必要がある。ここで、同 じ荷重でもスタンプ凸部の面積や形状によって実際に印加される転写圧が異なるため、パターン ごとに最適な荷重を求める必要があるが、今回は p 型用 n 型用共に 10 cm 角のスタンプに対し て 300 N の荷重で押し付けたところ、凸部のみを転写することに成功した。このとき、アライメ ントは設計に対して 10-20 μm 程度ずれてしまっていたが、このズレは PDMS スタンプの厚み

が不均一性でなく設置したスタンプの凸部が厳密に水平でないために、装置のカメラで真上から見て調整した位置と、実際に押し付けた時の位置にずれが生じてしまうためであると考えられる。今後、スタンプの作製手法を最適化することで、このアライメントのずれに関しては改善することができると考えられる。p型 n型を順に転写した後、80℃の真空オーブンで 10 時間乾燥を行った。

図 3.8 µSTP 法での半導体膜転写用に開発された装置の写真。

### 【ソース、ドレイン電極の形成】

最後に、ソース・ドレイン電極を形成した。まず、ソース・ドレイン電極層とゲート電極層を 導通させるための VIA (Vertical Interconnect Access) を形成するため、YAG レーザーを用いてゲ ート絶縁膜をエッチングして、ゲート電極の一部を露出させた (VIA 開口)。この上に Au を全面 に 50 nm 真空蒸着することで、ゲート電極とソース・ドレイン電極を電気的に接続した。 続いて、 ソース/ドレイン電極のパターニングを行った。

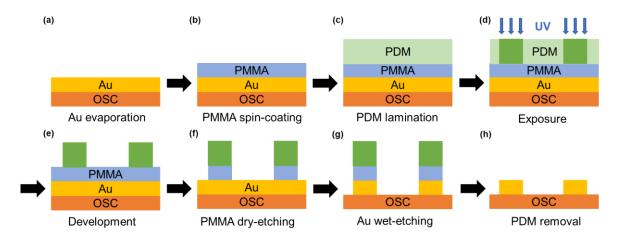

プロセスの模式図を図 3.9 (a-h) に示す. 本手法では安価な PMMA 及び厚さ 5  $\mu$ m のネガ型ドライフィルムレジスト (PDM: 太陽インキ製造株式会社) を利用した二層式のフォトリソグラフィプロセスを用いた。Au 膜上に PMMA(平均分子量 120,000、Sigma-Aldrich Co. LLC.)の 5 wt% 酢酸ブチル溶液を slope 1 秒,500 rpm で 5 秒、slope 1 秒、2000 rpm で 40 秒の条件でスピンコートし、230 nm 程度の PMMA 膜を製膜した(図 3.9 (a-b))。80  $^{\circ}$ C のホットプレート上で 10 分間乾燥させた後、真空ラミネータを用いて PDM を貼り付けた(図 3.9 (c))。基板温度は 65  $^{\circ}$ C とし、2 分程度かけて加圧しながら貼り付けた。基板を徐冷した後、レジスト上面の保護フィルムを剥離し、マスクレス露光機で紫外光( $\lambda$ =375 nm)を露光した後(図 3.9 (d))、40  $^{\circ}$ C に加温した 1 wt%の Na<sub>2</sub>CO<sub>3</sub> 水溶液に 1 分間浸漬して現像した(図 3.9 (e))。続いて、レジストで保護されていない領域の PMMA 層を反応性イオンエッチング装置(コンパクトエッチャーFA-1: サムコ株式会社)を用いて酸素プラズマを 60 秒間照射し、ドライエッチングした(図 3.9 (f))。次に、AURUM S-

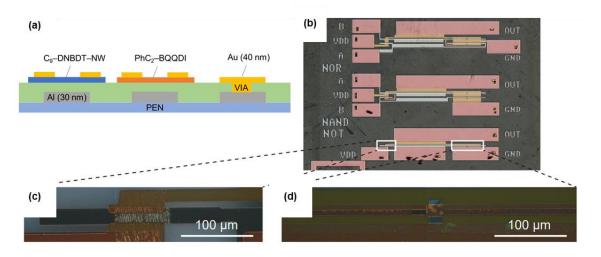

50790 (関東化学株式会社) に浸漬して Au のウェットエッチングを行い、流水に 15 分間浸してエッチング液残渣を取り除いた (図 3.9(g))。続いて、アセトニトリルに 2-3 分間程度浸漬することで PMMA 層を膨潤・溶解させ、PDM を浮かせて除去した (図 3.9(h))。最後に 80  $^{\circ}$ C のホットプレート上で 8 時間乾燥を行った。以上により作製したデバイスの構造、写真を図 3.10 に示す。

図 3.9 電極パターニング手法。 (a) 半導体膜上に Au を真空蒸着。 (b) PMMA をスピンコート。 (c) PDM を真空ラミネート。(d) 露光。(e) 現像。(f) 酸素プラズマによる PMMA のドライエッチング。 (g) AURUM による Au のウェットエッチング。 (h) アセトニトリルによる PMMA の溶解及び PDM の剥離.

図 3.10 (a) デバイス構造の模式図。 (b) デバイスの顕微鏡写真。 (c) インバータの p 型 OFET、(d) n 型 OFET の偏光顕微鏡写真。

## 3.2.3. デバイス評価

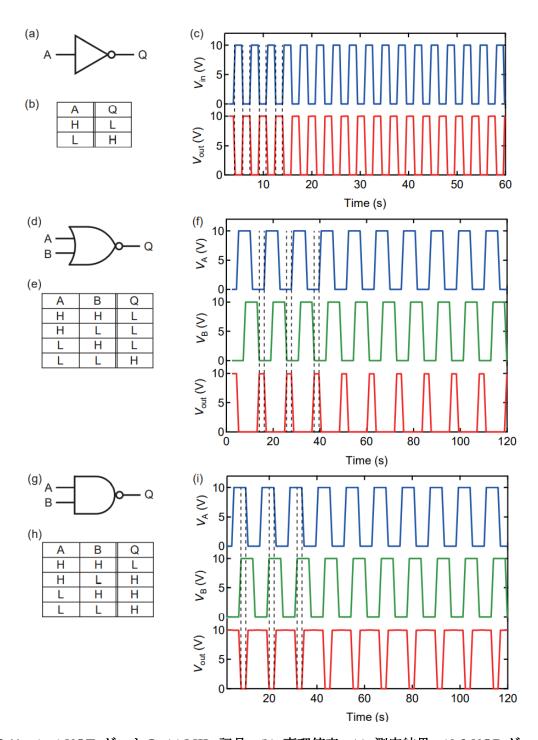

続いて、作製したデバイスの特性評価を行った。まず、3.2.1 項で説明した論理ゲート (NOT、NOR、NAND) の動作測定を行った。それぞれについて、 $V_{DD}=10\,\mathrm{V}$  として測定した。NOT ゲートに関しては、図  $3.11\,\mathrm{(c)}$  から、入力電圧  $V_{\mathrm{in}}$  に対して反転した  $V_{\mathrm{out}}$  が得られており、正しく動作していることが確かめられた。NOR ゲートについても、入力電圧  $V_{\mathrm{A}}$ 、 $V_{\mathrm{B}}$  の両方が "L" のときのみ  $V_{\mathrm{out}}$  が "H" でそれ以外のときは "L" となっており、真理値表通りの動作をしている。また NAND ゲートについても入力電圧  $V_{\mathrm{A}}$ 、 $V_{\mathrm{B}}$  の両方が "H" のときのみ  $V_{\mathrm{out}}$  が "L" でそれ以外のときは "H" となっており、真理値表通りの動作をしている。また、それぞれについて、 $V_{\mathrm{out}}$  は "H" のときには  $10\,\mathrm{V}$ 、"L" のときには  $0\,\mathrm{V}$  となっており、正常な動作をしているといえる。以上より、 $\mu\mathrm{STP}$  法を用いてフィルム基板上で基本的な論理ゲートを動作させることに成功した。

図 3.11 (a-c) NOT ゲートの (a) MIL 記号、(b) 真理値表、(c) 測定結果。(d-f) NOR ゲートの (d) MIL 記号、(e) 真理値表、(f) 測定結果。(g-i) NAND ゲートの (g) MIL 記号、(h) 真理値表、(i) 測定結果。  $V_{\rm DD}$  はいずれも  $10~\rm V$  とした。

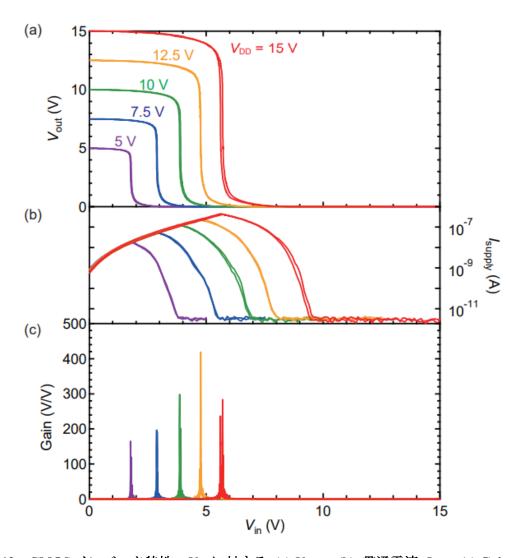

図 3.11 (c) で特性を示した CMOS インバータについて、 $V_{\rm in}$ を 0 V から 15 V の範囲で掃引して得られた特性を図 3.12 (a-c) に示す。図 3.12 (a) から、 $V_{\rm in}$  が "L" ( $V_{\rm in}$  = 0 V) のとき  $V_{\rm out}$  が "H" ( $V_{\rm out}$  = 15 V)、 $V_{\rm in}$  が "H" ( $V_{\rm in}$  = 15 V) のとき  $V_{\rm out}$  が "L" ( $V_{\rm out}$  = 0 V) となっており、インバータとして動作していることが分かる。最大の Gain としては 420 程度が得られ、塗布型 OFET のインバータとしては非常に良好な値が得られた(図 3.12 (c))。一方、それぞれの  $V_{\rm DD}$  に対して、切り替わり電圧が  $V_{\rm in}$  =  $V_{\rm DD}$  /2 よりも低電圧側に寄っている様子が見られる(図 3.12 (a))。また、図 3.12 (b) の貫通電流  $I_{\rm supply}$  を見ると、 $V_{\rm in}$  が 0 V 付近のときに完全に OFF 電流となっていない。

上記結果の原因を考察するため、インバータを構成する p 型 OFET と n 型 OFET それぞれの特性を測定した。図 3.13 に それぞれの特性を示す。いずれもトランジスタとして駆動していることが確認された。しかし、移動度の値に関しては、p 型 OFET の  $\mu_{sat}$  は  $0.34~\rm cm^2~V^{-1}~s^{-1}$  程度、n 型 OFET の  $\mu_{sat}$  は  $0.18~\rm cm^2~V^{-1}~s^{-1}$  程度となっており、3.1.3 項で作製した p 型、n 型 OFET の移動度よりも低下してしまっていた。この原因については、塗布膜の膜質や転写圧が不足してい

図 3.12 CMOS インバータ特性。  $V_{\rm in}$  に対する (a)  $V_{\rm out}$  、(b) 貫通電流  $I_{\rm supply}$  (c) Gain の値。

図 3.13 作製した p 型 OFET の (a) 飽和領域の伝達特性、(b) 線形領域の伝達特性、および (c) 出力特性。 (L/W = 12 μm/80 μm) 作製した n 型 OFET の (d) 飽和領域の伝達特性、(e) 線形領域の伝達特性、および(f) 出力特性。(L/W = 8 μm/500 μm)

たために転写膜の膜質が悪かったことや、アライメントのずれによりゲート電極とコンタクト電極の重なりが不十分であったために接触抵抗が大きく[46]、チャネル長がそれぞれ 12  $\mu$ m や 8  $\mu$ m と短いため、その影響を大きく受けていることなどが考えられる。特に p型 OFET の移動度低下が大きく、図 3.13 (c), (f) から分かるように、同じ  $|V_G|$  及び  $|V_D|$  のときに p型 OFET よりも n型 OFET の電流値が高くなってしまっている。これにより、切り替わり電圧が  $V_{in}=V_{DD}/2$  よりも低電圧側に寄ってしまったと考えられる。これについては、今後アライメント精度の向上や、それぞれの OFET の設計 (L/W) を調整することで改善されると考えられる。

また、図 3.13 (d-e) から  $V_G=0$  の状態で n 型 OFET が ON になって  $I_D$  が  $10^9$  A 程度流れてしまっていることが分かる。これにより、 $V_{in}=0$  V 付近でも  $I_{supply}$  が  $10^9$  A 程度流れたと考えられる。ON 電圧  $V_{on}$  は絶縁膜やプロセス等、さまざまな要因によってシフトするため、今後原因を究明し、最適化する必要がある。このように、CMOS 論理回路の駆動には成功したが、論理回路の動作速度や動作精度を上げていくためには設計、構造、作製プロセス等を改善する必要がある。

# 第4章 総括

本研究では、有機半導体の実デバイス応用において、溶液法を用いた半導体膜の形成に付随する問題を解決する半導体膜の転写手法を開発した。高温環境下で超親水性を安定的に保持するNGG と PDMS リレー基板を用いた新規半導体転写手法の開発により、様々な特性の半導体膜を自由に扱うことが出来るようになった。また、リレー基板に凹凸を形成することによるパターニング手法により、半導体膜の形状についても安価かつ、ダメージフリーな手法でデザインが可能となった。この手法は溶液法で作製した p型、n型単結晶膜を同一表面状に微細にパターニングできる革新的な手法であり、有機半導体の論理回路応用の可能性を大きく広げるものであるといえる。本研究で開発した転写手法とパターニング手法はいずれも半導体材料の特性によらず応用可能なものであり、これは分子設計によって様々な材料が開発される有機半導体において大きな利点である。このように、本研究で開発した手法は実デバイス作製への応用が十分に可能な手法であり、有機半導体デバイス開発を大きく加速させるものであると考えられる。

# 参考文献

- [1] T. Sekitani *et al.*, "Stretchable active-matrix organic light-emitting diode display using printable elastic conductors," *Nat. Mater.*, vol. 8, no. 6, pp. 494–499, May 2009, doi: 10.1038/nmat2459.

- [2] G. H. Gelinck *et al.*, "Flexible active-matrix displays and shift registers based on solution-processed organic transistors," *Nature Materials*, vol. 3, no. 2. Nature Publishing Group, pp. 106–110, Jan. 25, 2004, doi: 10.1038/nmat1061.

- [3] I. Yagi et al., "A flexible full-color AMOLED display driven by OTFTs," J. Soc. Inf. Disp., vol. 16, no.

1, p. 15, Jan. 2008, doi: 10.1889/1.2835023.

- [4] T. Sekitani, Y. Noguchi, K. Hata, T. Fukushima, T. Aida, and T. Someya, "A rubberlike stretchable active matrix using elastic conductors," *Science* (80-. )., vol. 321, no. 5895, pp. 1468–1472, Sep. 2008, doi: 10.1126/science.1160309.

- [5] K. Kudo, M. Yamashina, and T. Moriizumi, "Field Effect Measurement of Organic Dye Films," *Jpn. J. Appl. Phys.*, vol. 23, no. 1, p. 130, Jan. 1984, doi: 10.1143/JJAP.23.130.

- [6] H. Minemawari *et al.*, "Inkjet printing of single-crystal films," *Nature*, vol. 475, no. 7356, pp. 364–367,Jul. 2011, doi: 10.1038/nature10313.

- [7] K. Nakayama *et al.*, "Patternable solution-crystallized organic transistors with high charge carrier mobility," *Adv. Mater.*, vol. 23, no. 14, pp. 1626–1629, Apr. 2011, doi: 10.1002/adma.201004387.

- [8] C. Mitsui *et al.*, "High-performance solution-processable N-shaped organic semiconducting materials with stabilized crystal phase," *Adv. Mater.*, vol. 26, no. 26, pp. 4546–4551, Jul. 2014, doi: 10.1002/adma.201400289.

- [9] S. Kumagai *et al.*, "Scalable Fabrication of Organic Single-Crystalline Wafers for Reproducible TFT Arrays," *Sci. Rep.*, vol. 9, no. 1, pp. 1–8, Dec. 2019, doi: 10.1038/s41598-019-50294-x.

- [10] T. Makita *et al.*, "High-performance, semiconducting membrane composed of ultrathin, single-crystal organic semiconductors," *Proc. Natl. Acad. Sci.*, vol. 117, no. 1, pp. 80–85, Jan. 2020, doi: 10.1073/pnas.1909932116.

- [11] T. Uemura *et al.*, "On the Extraction of Charge Carrier Mobility in High-Mobility Organic Transistors," *Adv. Mater.*, vol. 28, no. 1, pp. 151–155, Jan. 2016, doi: 10.1002/adma.201503133.

- [12] E. G. Bittle, J. I. Basham, T. N. Jackson, O. D. Jurchescu, and D. J. Gundlach, "Mobility overestimation due to gated contacts in organic field-effect transistors," *Nat. Commun.*, vol. 7, no. 1, pp. 1–7, Mar. 2016, doi: 10.1038/ncomms10908.

- [13] I. McCulloch, A. Salleo, and M. Chabinyc, "Avoid the kinks when measuring mobility: Transistor measurements can overstate organic semiconductor charge carrier mobility," *Science*, vol. 352, no. 6293. American Association for the Advancement of Science, pp. 1521–1522, Jun. 24, 2016, doi: 10.1126/science.aaf9062.

- [14] A. Yamamura *et al.*, "Wafer-scale, layer-controlled organic single crystals for high-speed circuit operation," *Sci. Adv.*, vol. 4, no. 2, p. eaao5758, Feb. 2018, doi: 10.1126/sciadv.aao5758.

- [15] T. Yasuda, T. Goto, K. Fujita, and T. Tsutsui, "Ambipolar pentacene field-effect transistors with calcium source-drain electrodes," *Appl. Phys. Lett.*, vol. 85, no. 11, pp. 2098–2100, Sep. 2004, doi: 10.1063/1.1794375.

- [16] H. Klauk, M. Halik, U. Zschieschang, G. Schmid, W. Radlik, and W. Weber, "High-mobility polymer gate dielectric pentacene thin film transistors," *J. Appl. Phys.*, vol. 92, no. 9, pp. 5259–5263, Nov. 2002, doi: 10.1063/1.1511826.

- [17] J. Takeya, K. Tsukagoshi, Y. Aoyagi, T. Takenobu, and Y. Iwasa, "Hall effect of quasi-hole gas in organic single-crystal transistors," *Japanese J. Appl. Physics, Part 2 Lett.*, vol. 44, no. 46–49, p. 1393, Nov. 2005, doi: 10.1143/JJAP.44.L1393.

- [18] V. Podzorov, E. Menard, J. A. Rogers, and M. E. Gershenson, "Hall effect in the accumulation layers on the surface of organic semiconductors," *Phys. Rev. Lett.*, vol. 95, no. 22, Nov. 2005, doi: 10.1103/PhysRevLett.95.226601.

- [19] J. Takeya *et al.*, "Very high-mobility organic single-crystal transistors with in-crystal conduction channels," *Appl. Phys. Lett.*, vol. 90, no. 10, p. 102120, Mar. 2007, doi: 10.1063/1.2711393.

- [20] S. K. Park, T. N. Jackson, J. E. Anthony, and D. A. Mourey, "High mobility solution processed 6,13-bis(triisopropyl-silylethynyl) pentacene organic thin film transistors," *Appl. Phys. Lett.*, vol. 91, no. 6, p. 063514, Aug. 2007, doi: 10.1063/1.2768934.

- [21] B. A. Jones, A. Facchetti, M. R. Wasielewski, and T. J. Marks, "Tuning orbital energetics in arylene diimide semiconductors. Materials design for ambient stability of n-type charge transport," *J. Am. Chem. Soc.*, vol. 129, no. 49, pp. 15259–15278, Dec. 2007, doi: 10.1021/ja075242e.

- [22] T. D. Anthopoulos *et al.*, "High performance n -channel organic field-effect transistors and ring oscillators based on C60 fullerene films," *Appl. Phys. Lett.*, vol. 89, no. 21, p. 213504, Nov. 2006, doi: 10.1063/1.2387892.

- [23] Z. Bao, A. J. Lovinger, and J. Brown, "New air-stable n-channel organs thin film transistors," *J. Am. Chem. Soc.*, vol. 120, no. 1, pp. 207–208, Jan. 1998, doi: 10.1021/ja9727629.

- [24] J. Soeda *et al.*, "High electron mobility in air for N,N'-1H,1H- Perfluorobutyldicyanoperylene Carboxydi-imide Solution-Crystallized Thin-Film Transistors on Hydrophobic Surfaces," *Adv. Mater.*, vol. 23, no. 32, pp. 3681–3685, Aug. 2011, doi: 10.1002/adma.201101467.

- [25] I. Vladimirov et al., "High-Mobility, Ultrathin Organic Semiconducting Films Realized by Surface-Mediated Crystallization," Nano Lett., vol. 18, no. 1, pp. 9–14, Jan. 2018, doi: 10.1021/acs.nanolett.7b03789.

- [26] S. Kumagai et al., "Coherent Electron Transport in Air-Stable, Printed Single-Crystal Organic Semiconductor and Application to Megahertz Transistors," Adv. Mater., vol. 32, no. 50, p. 2003245, Dec. 2020, doi: 10.1002/adma.202003245.

- [27] T. Okamoto *et al.*, "Robust, high-performance n-type organic semiconductors," 2020. Accessed: Jul. 09, 2020. [Online]. Available: http://advances.sciencemag.org/.

- [28] T. Uemura, Y. Hirose, M. Uno, K. Takimiya, and J. Takeya, "Very high mobility in solution-processed organic thin-film transistors of highly ordered [1]benzothieno[32-b]benzothiophene derivatives," *Appl. Phys. Express*, vol. 2, no. 11, p. 111501, Nov. 2009, doi: 10.1143/APEX.2.111501.

- [29] K. Wu *et al.*, "Controlled Growth of Ultrathin Film of Organic Semiconductors by Balancing the Competitive Processes in Dip-Coating for Organic Transistors," 2016, doi: 10.1021/acs.langmuir.6b01083.

- [30] G. Giri *et al.*, "Tuning charge transport in solution-sheared organic semiconductors using lattice strain," *Nature*, vol. 480, no. 7378, pp. 504–508, Dec. 2011, doi: 10.1038/nature10683.

- [31] J. Soeda, T. Uemura, T. Okamoto, C. Mitsui, M. Yamagishi, and J. Takeya, "Inch-size solution-processed single-crystalline films of high-mobility organic semiconductors," *Appl. Phys. Express*, vol. 6, no. 7, p. 076503, Jul. 2013, doi: 10.7567/APEX.6.076503.

- [32] Q. Wei, S. Miyanishi, K. Tajima, and K. Hashimoto, "Enhanced charge transport in polymer thin-film transistors prepared by contact film transfer method," *ACS Appl. Mater. Interfaces*, vol. 1, no. 11, pp. 2660–2666, Nov. 2009, doi: 10.1021/am9005572.

- [33] B. Peng *et al.*, "A Transfer Method for High-Mobility, Bias-Stable, and Flexible Organic Field-Effect Transistors," *Adv. Mater. Technol.*, vol. 5, no. 5, p. 2000169, May 2020, doi: 10.1002/admt.202000169.

- [34] C. Xu *et al.*, "A General Method for Growing Two-Dimensional Crystals of Organic Semiconductors by 'Solution Epitaxy," *Angew. Chemie Int. Ed.*, vol. 55, no. 33, pp. 9519–9523, Aug. 2016, doi: 10.1002/anie.201602781.

- [35] T. Okamoto *et al.*, "Robust, high-performance n-type organic semiconductors," *Sci. Adv.*, vol. 6, no. 18, p. eaaz0632, Apr. 2020, doi: 10.1126/sciadv.aaz0632.

- [36] R. N. Wenzel, "Resistance of solid surfaces to wetting by water," *Ind. Eng. Chem.*, vol. 28, no. 8, pp. 988–994, Aug. 1936, doi: 10.1021/ie50320a024.

- [37] A. B. D. Cassie and S. Baxter, "Wettability of porous surfaces," *Trans. Faraday Soc.*, vol. 40, no. 0, pp. 546–551, Jan. 1944, doi: 10.1039/tf9444000546.

- [38] M. Miwa, A. Nakajima, A. Fujishima, K. Hashimoto, and T. Watanabe, "Effects of the surface roughness on sliding angles of water droplets on superhydrophobic surfaces," *Langmuir*, vol. 16, no. 13, pp. 5754–5760, Jun. 2000, doi: 10.1021/la991660o.

- [39] B. He, N. A. Patankar, and J. Lee, "Multiple equilibrium droplet shapes and design criterion for rough hydrophobic surfaces," *Langmuir*, vol. 19, no. 12, pp. 4999–5003, Jun. 2003, doi: 10.1021/la0268348.

- [40] T. Fujima, E. Futakuchi, T. Tomita, Y. Orai, and T. Sunaoshi, "Hierarchical nanoporous glass with antireflectivity and superhydrophilicity by one-pot etching," *Langmuir*, vol. 30, no. 48, pp. 14494–14497, Dec. 2014, doi: 10.1021/la502873d.

- [41] T. Ito, E. Tabata, Y. Ushioda, and T. Fujima, "Effect of boron in a hierarchical nanoporous layer formation on silicate glass," *Materials (Basel)*., vol. 13, no. 8, p. 1817, Apr. 2020, doi: 10.3390/MA13081817.

- [42] A. Carlson, A. M. Bowen, Y. Huang, R. G. Nuzzo, and J. A. Rogers, "Transfer printing techniques for materials assembly and micro/nanodevice fabrication," *Advanced Materials*, vol. 24, no. 39. John Wiley & Sons, Ltd, pp. 5284–5318, Oct. 09, 2012, doi: 10.1002/adma.201201386.

- [43] D. W. VAN KREVELEN, "POLYMER PROPERTIES," in *Properties of Polymers*, Elsevier, 1997, pp. 3–5.

- [44] S. H. Hur, D. Y. Khang, C. Kocabas, and J. A. Rogers, "Nanotransfer printing by use of noncovalent surface forces: Applications to thin-film transistors that use single-walled carbon nanotube networks and semiconducting polymers," *Appl. Phys. Lett.*, vol. 85, no. 23, pp. 5730–5732, Dec. 2004, doi: 10.1063/1.1829774.

- [45] K. Nakayama *et al.*, "High-Mobility Organic Transistors with Wet-Etch-Patterned Top Electrodes: A Novel Patterning Method for Fine-Pitch Integration of Organic Devices," *Adv. Mater. Interfaces*, vol. 1, no. 5, p. 1300124, Aug. 2014, doi: 10.1002/admi.201300124.

- [46] T. Sawada *et al.*, "Correlation between the static and dynamic responses of organic single-crystal field-effect transistors," *Nat. Commun.*, vol. 11, no. 1, pp. 1–8, Dec. 2020, doi: 10.1038/s41467-020-18616-0.

- [47] 辻村 秀太. ヘテロ界面制御による有機半導体単結晶微細パターニング手法. 東京大学応用 化学科卒業論文 (2014)

# 謝辞

本論文は、筆者が東京大学新領域創成科学研究科 竹谷・岡本・渡邉研究室で行った研究成果を まとめたものです。竹谷純一教授には、本研究の遂行にあたり、この上なく充実した実験設備を 用意していただき、円滑に研究を進めることが出来ました。また、日ごろから研究方針から論文 執筆に至るまで終始ご指導ご鞭撻いただきました。心より感謝申し上げます。岡本敏宏准教授に は、特に化学の観点から研究に対する貴重なアドバイスをいただきました。深く感謝申し上げま す。 渡邉峻一郎准教授には、日頃から研究計画について様々なアドバイスをいただきました。ま た、研究環境を整えていただき、円滑に研究を進めることができました。心より感謝いたします。 佐々木真理助教には、日頃の研究計画から本論文の執筆に至るまで、懇切丁寧なご指導をいただ きました。深く感謝いたします。黒澤忠法助教には、常日頃から親身にお声がけいただきました。 深く感謝いたします。熊谷翔平特任助教には、有機半導体や絶縁膜材料についての様々なご指導 をいただきました。また、XRD 測定について多くのサポートをいただきました。心より感謝申し 上げます。本研究室に在籍されていた物質・材料研究機構の山下侑博士には、親身に研究の相談 に乗っていただきました。深く感謝いたします。牧田龍幸氏には、日頃から様々な装置の使い方 についてご指導頂き、研究方針や論文執筆、発表資料等についても多くのアドバイスをいただき ました。心より感謝申し上げます。有機半導体の塗布についてパイクリスタル株式会社脇本貴裕 氏、大貫敬子氏に多くのアドバイスをいただきました。深く感謝いたします。日頃から親身にお 声がけいただき、研究方針についてアドバイスいただいた渡辺和誉博士に感謝いたします。2 年 間ともに励ましあった同期の澤田大輝氏、越路直也氏、工藤翔氏、王晏氏に深く感謝いたします。 その他研究室の皆様、卒業生の皆様にも大変お世話になりました。深く感謝いたします。最後に、 日ごろの研究生活を支えてくれた家族に心から感謝します。

> 令和 3 年 1 月 18 日 二宮 陽真