# 博士論文

# Operation Mechanisms and Intrinsic Performances of Non-volatile Memory Devices

### Based on Two-dimensional van der Waals Heterostructures

(二次元ファンデルワールスヘテロ構造からなる

不揮発性メモリデバイスの動作機構と本質的なデバイス性能に関する研究)

佐々木 太郎

### Abstract

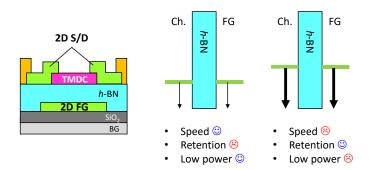

It is no doubt that our society has been strongly supported by the remarkable progress of Si-based electronic devices. On the contrary, the emergence of new kinds of applications such as neuromorphic computing, and the predicted arrival of geometrical and economical limit of the device scaling have required the alternative strategy for future fertile society. In this context, two-dimensional (2D) materials have been increasing their prominence as a candidate for next-generation electronic material. As well as its field-effect-transistor (FET) applications, its non-volatile memory (NVM) applications have been aggressively studied. With the help of dry transfer technique, NVM devices based on 2D van der Waals heterostructures (2D heterostructured NVM devices) have been realized, and considered as promising candidates of next-generation NVM, since its dangling-bond free interfaces have potential to realize the interface trapped charge free NVM devices. In 2D heterostructured NVM devices, typically, transition metal dichalcogenides (TMDCs) are often used as channel materials, while hexagonal boron nitride (h-BN) and graphite or graphene are used as a tunneling barrier and floating gate (FG), respectively. In addition, because of the increasing attention of 2D materials-based FETs, future material compatibility can also be expected for 2D heterostructured NVM device. However, even though a lot of progress has been achieved from graphene channel device with non-2D materials to 2D heterostructured device, it has not been sufficiently supported by the understandings of their operation mechanisms, preventing further improvement and control of their performances as desired. The lack of understandings also leads to the invalid evaluation of their performances, that is, *intrinsic* performances of them are still unclear. Therefore, the objective of this study is to reveal the comprehensive operation mechanisms and their intrinsic performances. The study is conducted in bottom-up approach as follows.

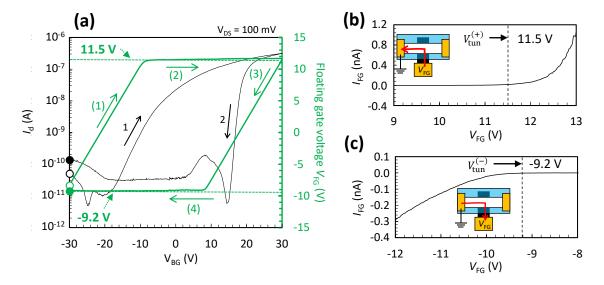

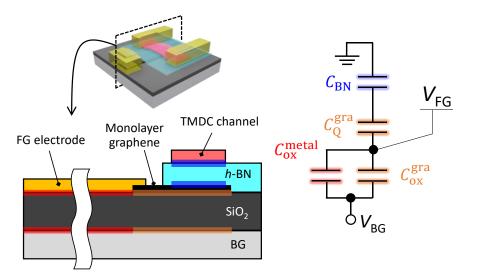

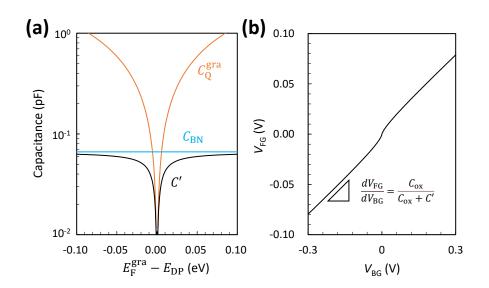

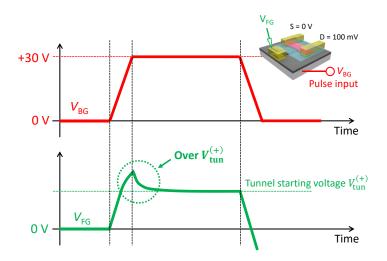

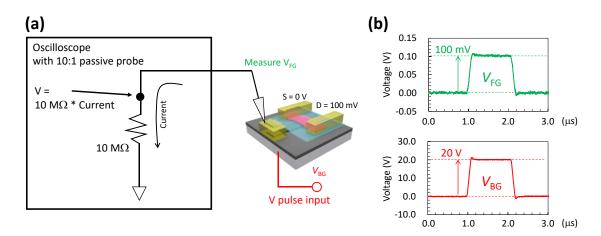

First of all, new measurement technique called *floating gate voltage* ( $V_{FG}$ ) *measurement* is proposed, for unveiling the operation mechanisms behind standard

current–voltage (I-V) round sweep curves. Since  $V_{FG}$  measurement can be performed by just adding another electrode onto the FG, it is applicable to any 2D heterostructured NVM devices. Measured  $V_{FG}$  during I-V round sweep called  $V_{FG}$  trajectory can be explained by two regions, which are capacitive coupling region with tilted  $V_{FG}$  and feedback region with pinned  $V_{FG}$ . The principle has been confirmed by experimental results.

Next, for reasonable performance evaluation, the validity of memory window extraction method is investigated since there are two different extraction methods which strongly depend on the research field. While I-V round sweep is widely used in 2D research field, I-V single sweep after program and erase (P/E) operation is used in Si research field. Consequently,  $V_{FG}$  trajectory-based analysis has revealed that the memory window extracted by I-V round sweep is often overestimated. The criterion for the overestimation by I-V round sweep is also derived, and it is found that the criterion is easy to be satisfied. Therefore, as well as Si research field, I-V single sweep should be used for the extraction of memory window even in 2D research field.

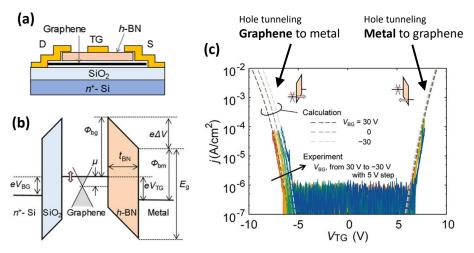

Then, the  $V_{FG}$  measurement is applied for three kinds of 2D heterostructured NVM devices. Since bandgap of 2D channel material and metal/2D interface are considered as the keys of device operation, three different materials (MoS<sub>2</sub>, WSe<sub>2</sub>, MoTe<sub>2</sub>) are used as the channels. On the other hand, all three devices have *h*-BN tunneling barrier and graphite FG. Interestingly, each device has inherent  $V_{FG}$  trajectory while their *I–V* round sweep curves are very similar as well as previous studies. By analyzing the trajectories, comprehensive understandings of their operation mechanism can be revealed, in terms of three tunneling current limiting paths. Moreover, the validity of understandings is confirmed by experimental controls of  $V_{FG}$  trajectory where the temperature, device structure, and sweeping rate are varied. Tunneling between source/drain (S/D) metal electrode and FG are experimentally proved for the first time, while previous studies have claimed that the 2D heterostructure was tunneling path.

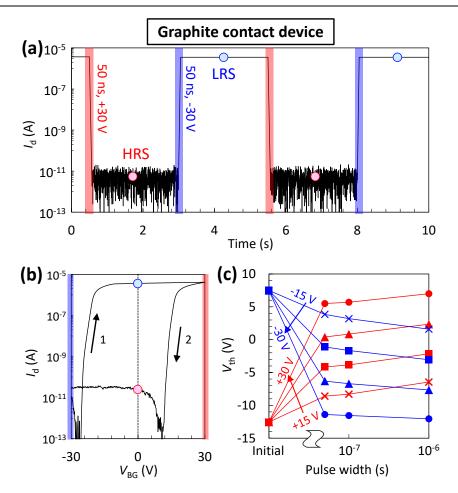

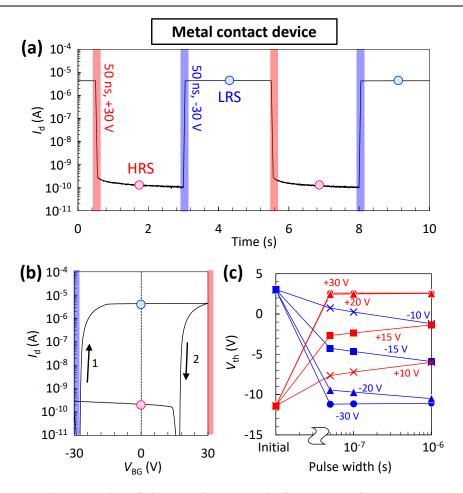

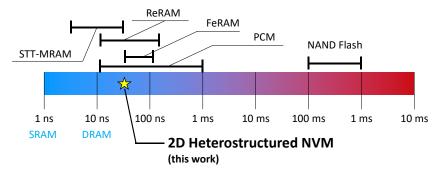

Finally, intrinsic performances of 2D heterostructured NVM device is reasonably investigated as mainly focused on the P/E speed. Remarkably, 50 ns ultra-fast P/E

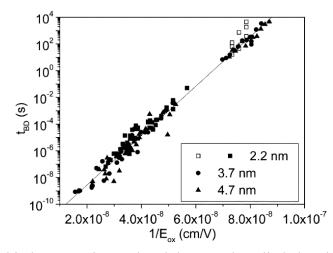

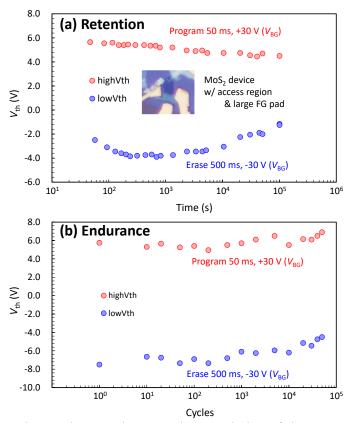

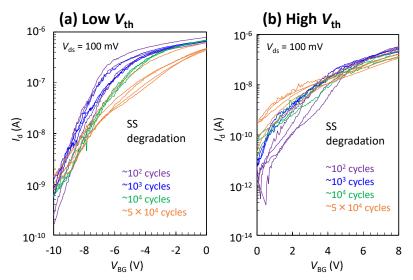

operation can be achieved by appropriately designed devices. To minimize the size of FG pad is the key for preventing the large tunneling current during fast P/E operation, which leads the *h*-BN breakdown. Although the superior 2D/2D interface seems to be the key, the controlled experiment revealed it is not the key. On the other hand, as compared with conventional SiO<sub>2</sub>, *h*-BN possesses stronger breakdown strength under high-speed voltage pulse stress, suggesting that the larger tunneling current can be allowed for *h*-BN. Importantly, the ultra-fast nature of 2D heterostructured NVM device is in the range of storage class memory, which is now strongly desired. Retention and endurance characteristics are also investigated, and 10<sup>5</sup> s retention and  $5 \times 10^4$  P/E cycles endurance can be achieved for the MoS<sub>2</sub> device with access region. Since the MoS<sub>2</sub> device has large FG pad for  $V_{\text{FG}}$  and tunneling current measurements, *h*-BN may be severely degraded due to large tunneling current as well as the speed test, suggesting that further improvement can be expected by the device with appropriately designed FG pad.

As the conclusion of this study, 2D heterostructured NVM device with graphite contact is proposed as a promising device structure. Although 2D/2D interface is not the key for the ultra-fast operation, it will be the key of great reliability.

Thesis supervisor: Kosuke Nagashio Title: Professor of Materials Engineering

### Acknowledgements

First of all, I would like to express my gratitude to my supervisor, Prof. Kosuke Nagashio for the exciting discussions and clear guidance throughout my doctoral course. The greatest fortunate in my doctoral course is that, Nagashio-sensei treated my curious result,  $V_{FG}$ *trajectory* as an interesting and meaningful one. Without this encouragement, the comprehensive understandings of operation mechanism had never been seen in the world. In addition, all of discussions with Nagashio-sensei are very exciting. Even if I was disappointed due to my poor results, Nagashio-sensei always gave me an alternative perspective which re-activates my motivation. These experiences must be a guideline of my future carrier.

I would like to express my gratitude to Prof. Ken Uchida, Prof. Koji Kita, Prof. Tomoki Machida, and Prof. Masaharu Kobayashi, for insightful comments on my doctoral dissertation committee. By their help, I can gain important perspectives and drastically improved the discussions in this thesis.

I would also like to thank Dr. Tomonori Nishimura for his help of my experiments and a lot of significant comments. Whenever I encountered the trouble in my experiments, Nishimura-san kindly helped me by not only trouble shootings, but also suggestions of alternatives. At the weekly meeting, Nishimura-san precisely pointed out the quite important things which I missed until finishing the presentation, which drastically improved my experiments and discussions.

I would also like to offer my thanks to Prof. Keiji Ueno (Saitama Univ.) for providing us high-quality TMDC crystals, Dr. Takashi Taniguchi and Dr. Kenji Watanabe (NIMS) for providing us high-quality *h*-BN crystals, and Dr. Yukinori Morita and Dr. Yongxun Liu (AIST) for meaningful suggestions at the early stage of this study. I would like to offer my special thanks to Masaaki Niwa, Senior Fellow (UTokyo), for his kind attention throughout my doctoral course. In Nagashio lab., I would also like to thank Mrs. Kyoko Ogawa for her support of our daily life in the lab. I would also like to thank Drs. Nan Fang, Teerayut Uwanno, and Naoki Higashitarumizu for their fruitful help and suggestions in my experiments. I would also like to thank Dr. Haruki Uchiyama for giving me his new and interesting insights. I really thank Yih-Ren Chang, Supawan Ngamprapawat, Satoshi Toyoda, Kohei Maruyama, Keigo Nakamura, Hayami Kawamoto, Masaya Umeda, Yuichiro Sato, Masahiro Kobayashi, Shuhong Li, Roichi Kato, Wataru Nishiyama, Tomohiro Fukui, Ryuichi Nakajima, Hiryu Kozaki, and Ryo Nanae for significant discussions and fun memories. Thanks to all of the members, my doctoral course at the University of Tokyo become very enjoyable.

I would also like to thank the administrative staffs in the department of materials engineering for their support on my daily life in the department. I would like to extend my gratitude to my friends for their personal support, which makes my life fertile.

Finally, I want to give sincere thanks to my parents and family for their long support of my education. Thanks to the support, I can finally come this far.

### **Citations to Previously Published Works**

Chapter 2, 3, and 4 in this thesis are based on the following publications:

- <u>Sasaki, T.</u>; Ueno, K.; Taniguchi, T.; Watanabe, K.; Nishimura, T.; Nagashio, K. Understanding the Memory Window Overestimation of 2D Materials Based Floating Gate Type Memory Devices by Measuring Floating Gate Voltage. *Small* 2020, *16* (47), 2004907. (https://doi.org/10.1002/smll.202004907)

- (2) <u>Sasaki, T.</u>; Ueno, K.; Taniguchi, T.; Watanabe, K.; Nishimura, T.; Nagashio, K.

Material and Device Structure Designs for 2D Memory Devices Based on the Floating Gate Voltage Trajectory. *ACS Nano* 2021, *15* (4), 6658–6668.

(https://doi.org/10.1021/acsnano.0c10005)

# Contents

| Abstract                                                      | i    |

|---------------------------------------------------------------|------|

| List of Figures                                               | X    |

| List of Tables                                                | xvii |

| Chapter 1 Introduction                                        | 1    |

| 1.1 Non-volatile Memory Technology                            | 1    |

| 1.2 Si-based Flash Memory                                     |      |

| 1.2.1 Planer Cell                                             | 8    |

| 1.2.2 Scaling Limit of Planer Cell                            | 12   |

| 1.2.3 Three-dimensional Cell                                  | 14   |

| 1.2.4 Challenges in Three-dimensional Cell                    | 16   |

| 1.3 2D Materials                                              |      |

| 1.3.1 Graphene                                                | 19   |

| 1.3.2 <i>h</i> -BN                                            |      |

| 1.3.3 Transition Metal Dichalcogenides                        |      |

| 1.3.4 2D Heterostructures                                     |      |

| 1.3.5 Defects in 2D Materials                                 |      |

| 1.4 2D Materials-based Flash Memory                           |      |

| 1.4.1 Graphene Channel Devices with Non-2D Materials          |      |

| 1.4.2 Semiconducting 2D Channel Devices with Non-2D Materials |      |

| 1.4.3 2D Heterostructured Devices                             |      |

| 1.4.4 Advanced Functional Devices                             |      |

| 1.5 Objectives and Organizations of the Thesis                | 50   |

### Chapter 2 $V_{FG}$ Measurement for 2D Materials-based Flash Memory...52

| 2.1 Device Fabrication and Characterization            | . 53 |

|--------------------------------------------------------|------|

| 2.1.1 Device Structure                                 | 53   |

| 2.1.2 Fabrication Procedure                            | 55   |

| 2.1.3 Characterization by Raman Spectroscopy           | 57   |

| 2.1.4 Characterization by AFM and TEM                  | 59   |

| 2.2 Principle of V <sub>FG</sub> Measurement           | . 60 |

| 2.2.1 Measurement Setup                                | 60   |

| 2.2.2 Expected V <sub>FG</sub> Trajectory              | 61   |

| 2.3 Experimental Result of V <sub>FG</sub> Measurement | . 64 |

| 2.4 Effect of Quantum Capacitance of Graphene FG       | . 65 |

| 2.4.1 Capacitive Coupling Region   | 65 |

|------------------------------------|----|

| 2.4.2 Feedback by Tunneling Region |    |

| 2.5 Summary                        | 69 |

| Chapter 3 Memory Window Overestimation                                 | 70 |

|------------------------------------------------------------------------|----|

| 3.1 Memory Window as a Fundamental Metric                              | 71 |

| 3.2 Memory Window Extraction Methods                                   | 73 |

| 3.2.1 <i>I–V</i> Round Sweep in 2D Research Field                      | 73 |

| 3.2.2 <i>I–V</i> Single Sweep in Si Research Field                     | 74 |

| 3.3 Analysis by V <sub>FG</sub> Trajectory                             | 75 |

| 3.3.1 Extracted Memory Windows of the MoTe <sub>2</sub> Channel Device | 75 |

| 3.3.2 <i>I</i> – <i>V</i> Round Sweep Case                             | 77 |

| 3.3.3 <i>I</i> – <i>V</i> Single Sweep Case                            | 80 |

| 3.3.4 Memory Window Overestimation by <i>I–V</i> Round Sweep           | 81 |

| 3.4 Criterion for Memory Window Overestimation                         | 83 |

| 3.5 Summary                                                            | 85 |

| Chapter 4 Operation Mechanisms                                     | 86  |

|--------------------------------------------------------------------|-----|

| 4.1 Limited Information from <i>I–V</i> Transfer Curves            | 89  |

| 4.2 Inherent V <sub>FG</sub> Trajectories                          | 89  |

| 4.3 Three Current Limiting Paths                                   |     |

| 4.3.1 Path 1: FN Tunneling across <i>h</i> -BN                     |     |

| 4.3.2 Path 2: Communication between Access Region and FG Region    |     |

| 4.3.3 Path 3: Carrier Injection from Metal Electrode to 2D Channel |     |

| 4.4 V <sub>FG</sub> Trajectory Control                             | 107 |

| 4.4.1 Region B Control by Temperature                              |     |

| 4.4.2 Region C Control by Device Structure                         |     |

| 4.5 Temperature Dependence of V <sub>FG</sub> Trajectories         | 110 |

| 4.5.1 Positive Sweep                                               |     |

| 4.5.2 Negative Sweep                                               |     |

| 4.6 The Origin of <i>I</i> <sub>d</sub> Plateau                    | 114 |

| 4.7 Summary                                                        | 115 |

| Chapter 5 Performances                       | 116 |

|----------------------------------------------|-----|

| 5.1 Program and Erase Speed                  | 116 |

| 5.1.1 Preparation for High-speed Measurement |     |

| 5.1.2 P/E Speed of the Devices with Access Region             |  |

|---------------------------------------------------------------|--|

| 5.1.3 Device Design for High-speed and Robust P/E Operation   |  |

| 5.1.4 Fifty Nanoseconds P/E Operation and Its Possible Origin |  |

| 5.2 Retention and Endurance                                   |  |

| 5.3 Summary                                                   |  |

|                                                               |  |

| Chapter 6 Summary and Outlook |  |

|-------------------------------|--|

| 6.1 Summary                   |  |

| 6.2 Outlook                   |  |

| Appendix 1 List of Symbols            | 148 |

|---------------------------------------|-----|

| Appendix 2 Abbreviations and Acronyms | 151 |

| Appendix 3 Fowler-Nordheim Formula    | 155 |

| References                            | 161 |

| Publications                          | 177 |

| Award                                 |     |

# **List of Figures**

| <b>Fig. 1-1</b> Exponential expansion of global data <sup>1</sup> 1                                               |

|-------------------------------------------------------------------------------------------------------------------|

| Fig. 1-2 Schematic of a flash memory cell.    2                                                                   |

| <b>Fig. 1-3</b> NOR and NAND array configuration of flash memory cells <sup>4</sup> 2                             |

| Fig. 1-4 Memory hierarchy in computing system at early stage of ICT era and current. $\cdot\cdot$ 3               |

| Fig. 1-5 Schematic of typical neural network and its hardware implementation by using                             |

| non-volatile memory devices <sup>14</sup> 6                                                                       |

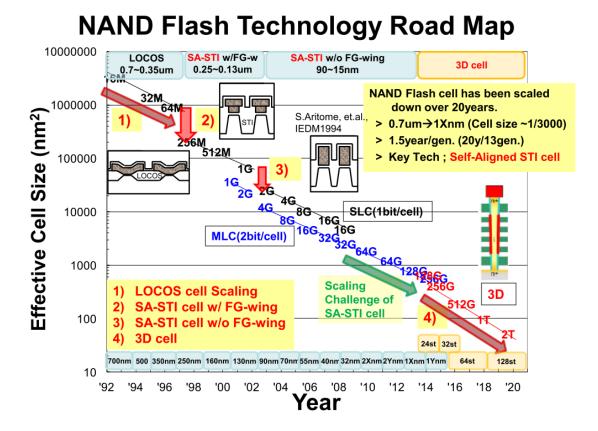

| <b>Fig. 1-6</b> Comprehensive roadmap of NAND flash technology <sup>5</sup> 8                                     |

| Fig. 1-7 Typical planer cell structure and its equivalent circuit9                                                |

| Fig. 1-8 Cross-sectional views of SA-STI cell with and without FG wing <sup>5</sup> 10                            |

| <b>Fig. 1-9</b> One example of $V_{\text{th}}$ distribution of multilevel cell <sup>18</sup> 11                   |

| <b>Fig. 1-10</b> Scaling limitations of planer cell <sup>16</sup> 12                                              |

| Fig. 1-11 Endurance and ECC bits trends <sup>22</sup> and conceptual illustration of severe effect by             |

| the interface trapped charges in a scaled cell                                                                    |

| Fig. 1-12 Schematic, cross-sectional SEM image, and equivalent circuit of the 3D flash                            |

| memory <sup>23</sup>                                                                                              |

| <b>Fig. 1-13</b> Performance comparison between planer NAND cell and 3D NAND cell <sup>24</sup> 15                |

| Fig. 1-14 Cross-sectional images of CT type and FG type 3D NAND flash memory <sup>27</sup> . $\cdot$ 15           |

| <b>Fig. 1-15</b> Simulation study of charge spreading in CT type 3D NAND flash memory <sup>30</sup> . 16          |

| Fig. 1-16 Brief summary of efforts and issues for Si-based flash memories                                         |

| Fig. 1-17 Atomic structure of graphene.    19                                                                     |

| <b>Fig. 1-18</b> Band structure for $\pi$ electrons in graphene <sup>34,35</sup>                                  |

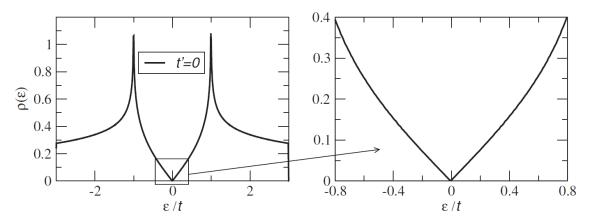

| <b>Fig. 1-19</b> Density of states of graphene as a function of energy of electron <sup>35</sup> 20               |

| <b>Fig. 1-20</b> Atomic structure of <i>h</i> -BN                                                                 |

| <b>Fig. 1-21</b> Height and charge density profile of graphene on <i>h</i> -BN and on SiO <sub>2</sub> $^{47}$ 22 |

| <b>Fig. 1-22</b> Representative three phases of TMDC crystal <sup>51</sup> 23                                     |

| Fig. 1-23 Calculated electronic band structure of monolayer, bilayer, and bulk MoS <sub>2</sub> ,                     |

|-----------------------------------------------------------------------------------------------------------------------|

| MoSe <sub>2</sub> , WS <sub>2</sub> and WSe <sub>2</sub> <sup>53</sup>                                                |

| <b>Fig. 1-24</b> Calculated bandgaps of bulk and monolayer TMDCs <sup>54</sup> 25                                     |

| <b>Fig. 1-25</b> Atomic structure of MoS <sub>2</sub>                                                                 |

| Fig. 1-26 Brillouin zone of MoS <sub>2</sub> , and its bandgaps and position of band edge as a function               |

| of the number of layers <sup>56</sup>                                                                                 |

| Fig. 1-27 Schematic, TEM image, and transfer characteristics of 1D2D-FET <sup>58</sup>                                |

| <b>Fig. 1-28</b> Demonstration of typical MoS <sub>2</sub> SB-FET <sup>59</sup>                                       |

| <b>Fig. 1-29</b> Demonstration of $MoS_2 ACCU$ -FET <sup>62</sup> 29                                                  |

| <b>Fig. 1-30</b> Bandgap fluctuation in monolayer MoS <sub>2</sub> <sup>67</sup> 31                                   |

| <b>Fig. 1-31</b> Conceptual illustration of 2D heterostructure <sup>68</sup>                                          |

| Fig. 1-32 Evolution of fabrication technique and corresponding electrical characteristics                             |

| of graphene FET <sup>73</sup>                                                                                         |

| <b>Fig. 1-33</b> Sketch of the $\Delta G$ and its first and second term as a function of <i>n</i>                     |

| Fig. 1-34 Calculated defect formation energies in bulk MoS <sub>2</sub> as functions of chemical                      |

| potential of sulfur and Fermi level <sup>78</sup>                                                                     |

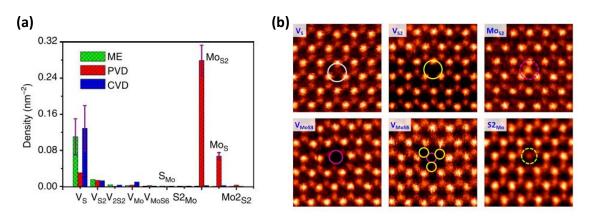

| Fig. 1-35 Histogram of various point defects in MoS <sub>2</sub> monolayers <sup>79</sup> , and STEM-ADF              |

| image of various point defects in CVD grown monolayer MoS <sub>2</sub> <sup>81</sup>                                  |

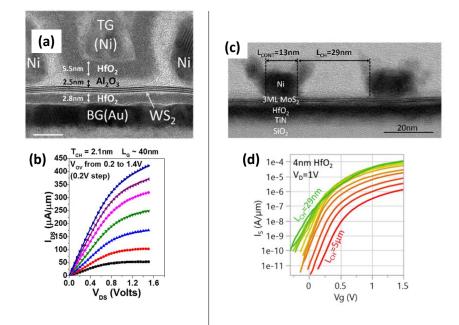

| Fig. 1-36 Recent demonstrations of ultra-scaled 2D materials-based MOSFETs <sup>86,87</sup> 38                        |

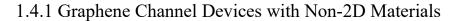

| <b>Fig. 1-37</b> Schematic of typical graphene channel device and its results <sup>90</sup> 40                        |

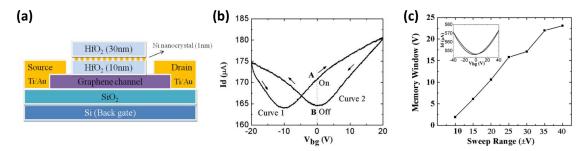

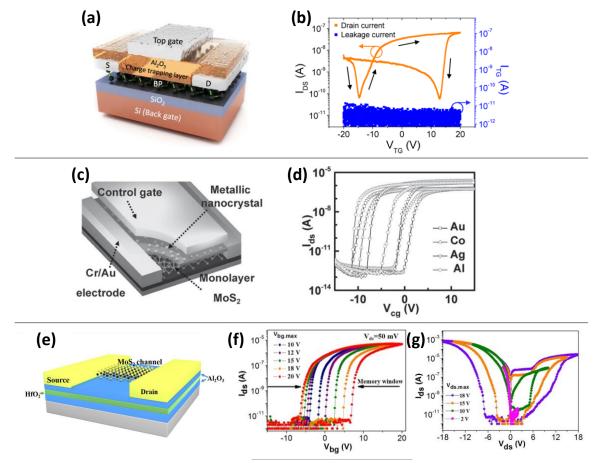

| Fig. 1-38 Schematics of typical semiconducting 2D channel devices and their results <sup>93-</sup>                    |

| <sup>95</sup>                                                                                                         |

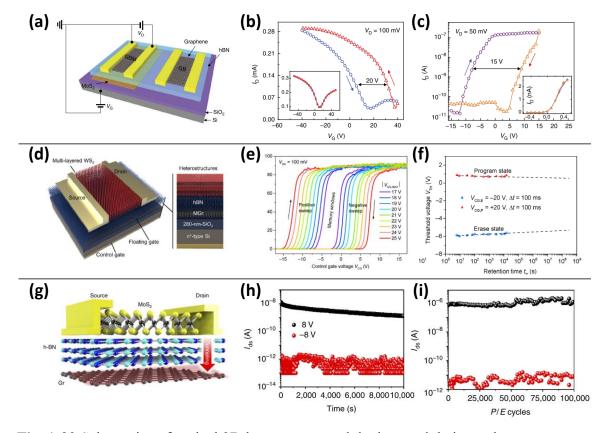

| <b>Fig. 1-39</b> Schematics of typical 2D heterostructured devices and their results <sup>41-43</sup> 43              |

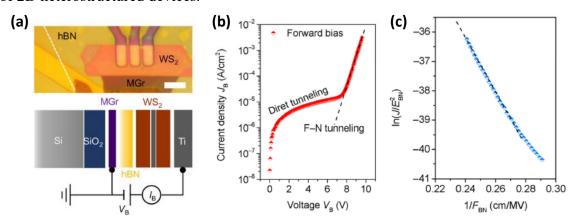

| <b>Fig. 1-40</b> Tunneling current in WS <sub>2</sub> / $h$ -BN/multi-layer graphene heterostructure <sup>42</sup> 44 |

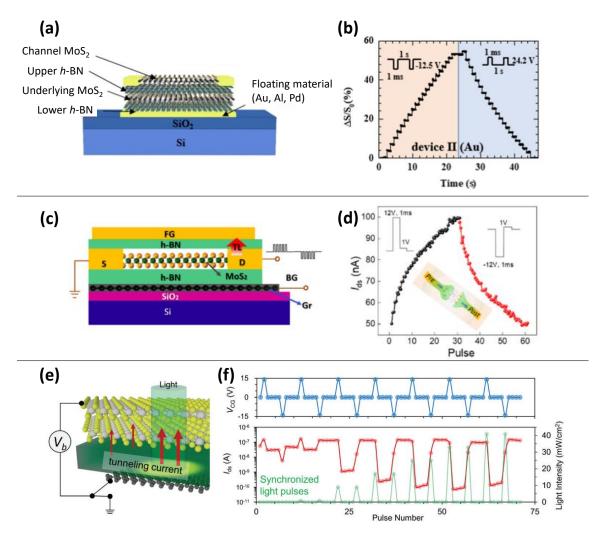

| Fig. 1-41 Schematics of typical advanced functional devices and their results <sup>100-102</sup> . ···· 45            |

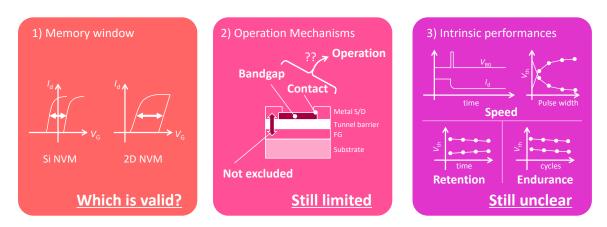

| Fig. 1-42 Three issues to be solved for recent 2D heterostructured NVM devices 47                                     |

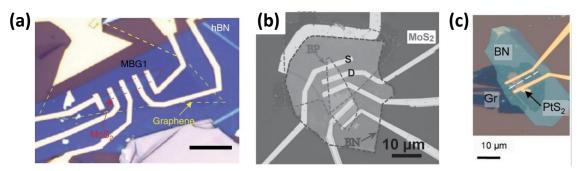

| <b>Fig. 1-43</b> Examples of S/D electrodes overlapping on the $FG^{41,102,104}$                                      |

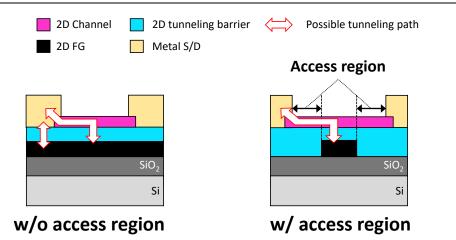

| Fig. 1-44 Possible tunneling paths in the device with and without access region                                       |

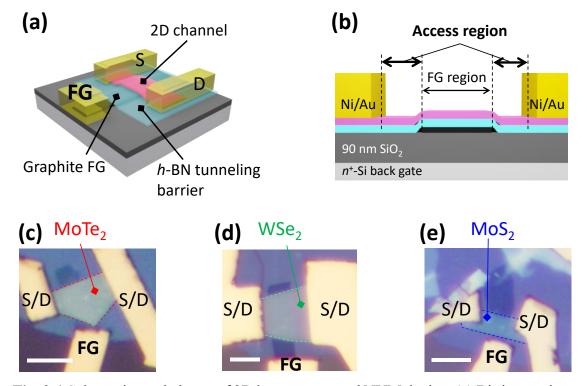

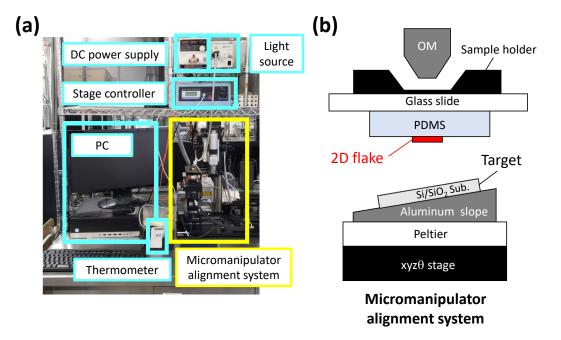

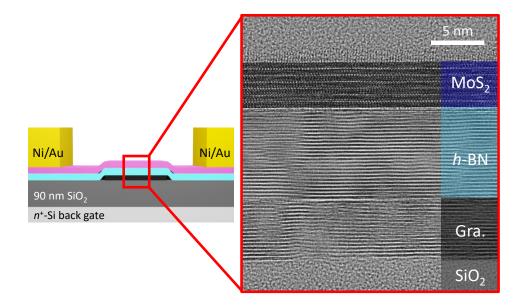

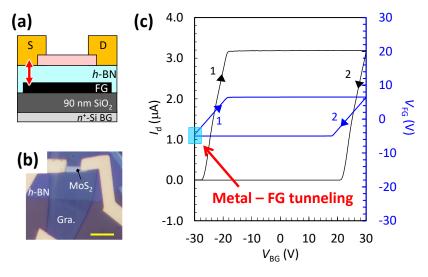

| Fig. 2-1 Schematics and photos of 2D heterostructured NVM device                                               |

|----------------------------------------------------------------------------------------------------------------|

| <b>Fig. 2-2</b> Photo and schematic of the dry transfer system <sup>70</sup> 55                                |

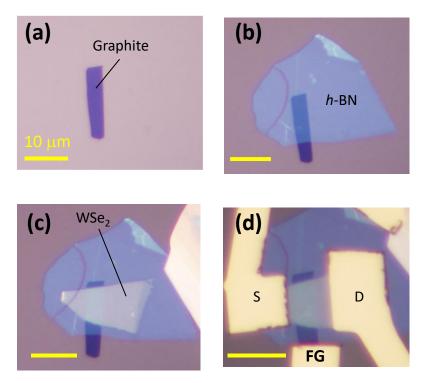

| <b>Fig. 2-3</b> Photos after each device fabrication process                                                   |

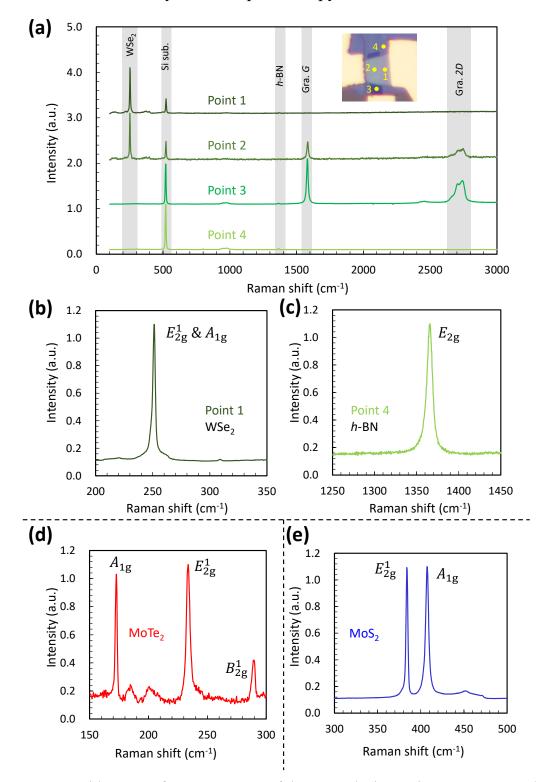

| Fig. 2-4 Raman spectra of fabricated devices.    57                                                            |

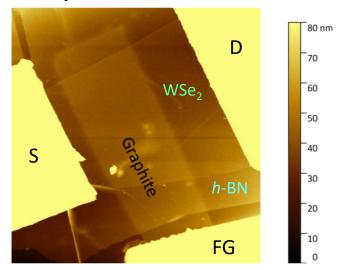

| Fig. 2-5 AFM image of the WSe <sub>2</sub> device 59                                                           |

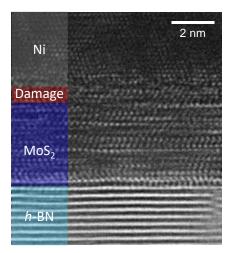

| Fig. 2-6 Cross-sectional TEM image of typical MoS <sub>2</sub> / <i>h</i> -BN/graphite heterostructure on      |

| $SiO_2/n^+$ -Si substrate fabricated by the dry transfer technique                                             |

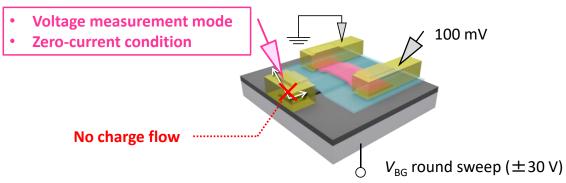

| <b>Fig. 2-7</b> Schematic of the setup for $V_{\rm FG}$ measurement                                            |

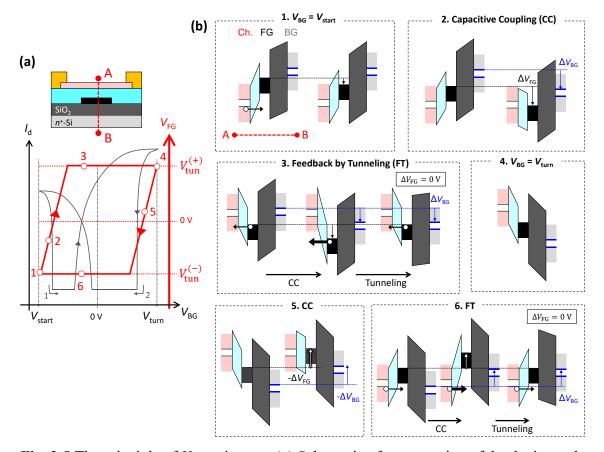

| <b>Fig. 2-8</b> The principle of $V_{\text{FG}}$ trajectory                                                    |

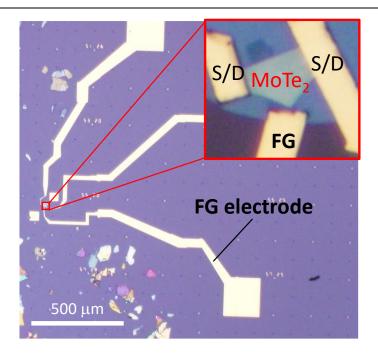

| Fig. 2-9 Photo of typical huge FG electrode.    62                                                             |

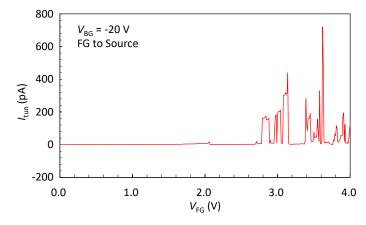

| Fig. 2-10 Measured $V_{FG}$ trajectory of MoTe <sub>2</sub> device and measured tunneling current              |

| between the FG and channel64                                                                                   |

| <b>Fig. 2-11</b> $I_d - V_{BG}$ transfer curves with and without $V_{FG}$ measurement                          |

| Fig. 2-12 Cross-sectional view of the device with monolayer graphene FG and its                                |

| equivalent circuit                                                                                             |

| <b>Fig. 2-13</b> Calculated capacitances and $V_{\text{FG}}$ as a function of $V_{\text{BG}}$ in CC region     |

| Fig. 2-14 Tunneling current in metal/ <i>h</i> -BN/graphene heterostructure fabricated on SiO <sub>2</sub> /Si |

| substrate <sup>120</sup>                                                                                       |

| Fig. 2-15 Comparison of the expected $V_{FG}$ trajectory between bulk graphite FG case and                     |

| monolayer graphene FG case                                                                                     |

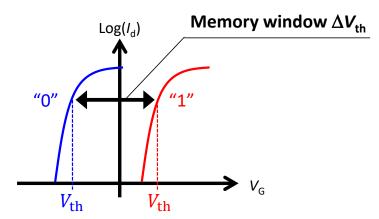

| Fig. 3-1The definition of memory window.71                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------|

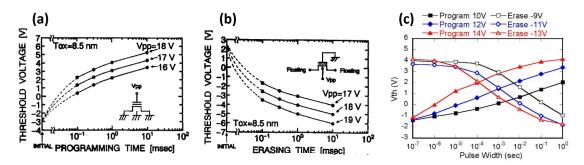

| <b>Fig. 3-2</b> Typical program and erase characteristics of NAND flash memory <sup>23,122</sup> 71                                   |

| <b>Fig. 3-3</b> Typical endurance and retention characteristics of planer NAND flash memory <sup>20</sup> .                           |

|                                                                                                                                       |

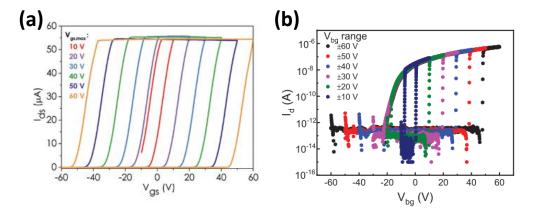

| <b>Fig. 3-4</b> Typical $I_d - V_g$ round sweep curves of 2D heterostructured NVM devices <sup>106,109</sup> . 73                     |

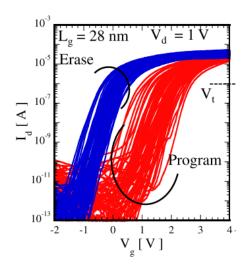

| Fig. 3-5 Typical $I_d-V_g$ singe sweep curves of Si based-flash memory cell after P/E                                                 |

| operation <sup>123</sup> 74                                                                                                           |

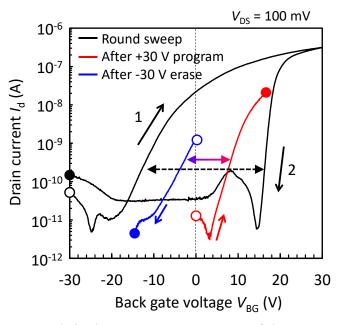

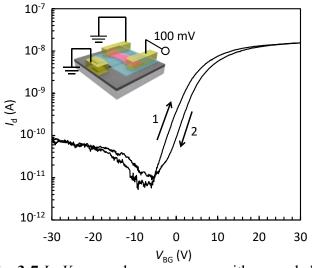

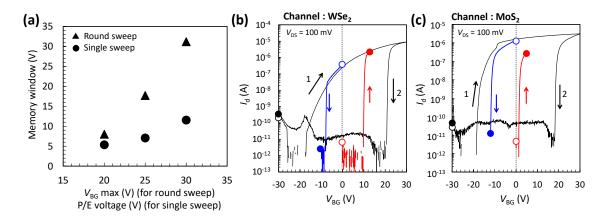

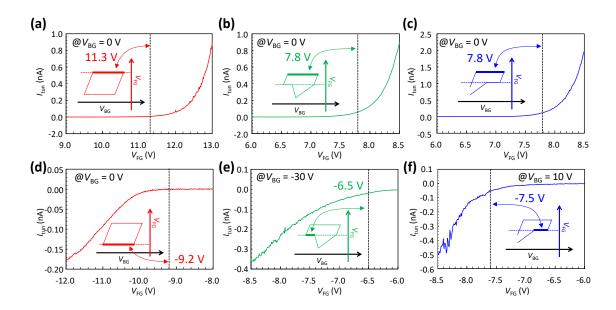

| <b>Fig. 3-6</b> Round sweep and single sweep $I_d - V_{BG}$ curves of the MoTe <sub>2</sub> device75                                  |

| <b>Fig. 3-7</b> $I_d - V_{BG}$ round sweep curves with grounded FG                                                                    |

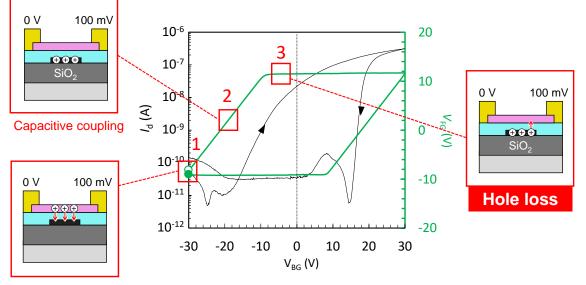

| <b>Fig. 3-8</b> Hole loss during $I_d - V_{BG}$ round sweep                                                                           |

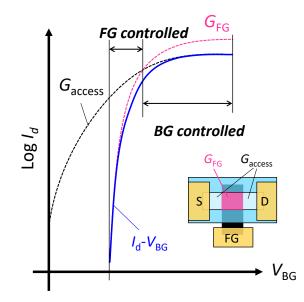

| Fig. 3-9 Schematic of FG controlled mode and BG controlled mode                                                                       |

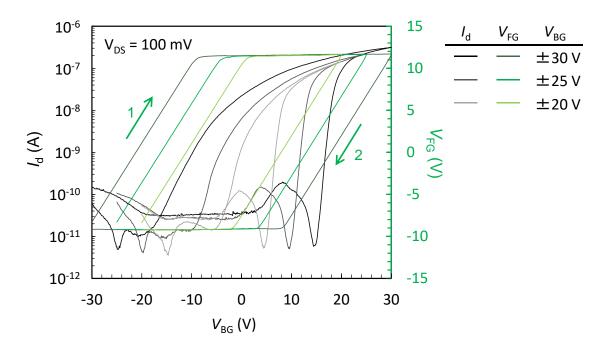

| Fig. 3-10 $V_{\rm FG}$ trajectories with various $V_{\rm BG}$ sweeping range superimposed on                                          |

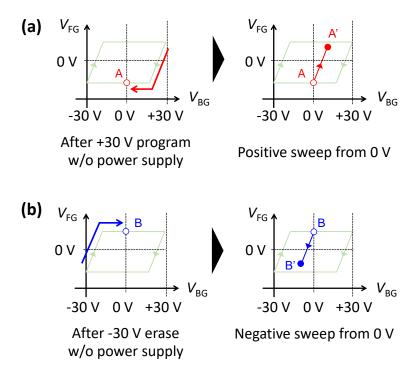

| corresponding $I_{\rm d}$ – $V_{\rm BG}$ round sweep curves                                                                           |

| Fig. 3-11 Expected $V_{\text{FG}}$ trajectories which correspond to $I_{\text{d}}$ - $V_{\text{BG}}$ single sweep curves. $\cdots$ 80 |

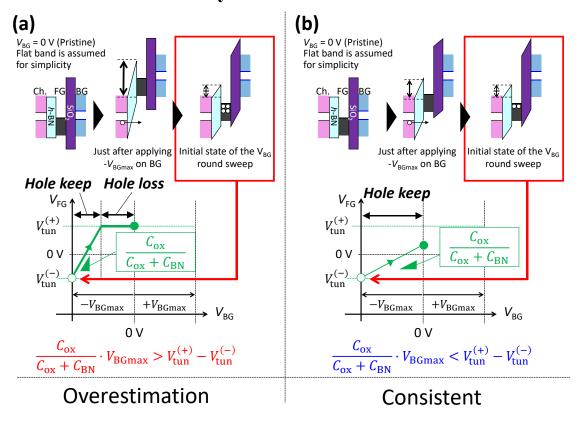

| Fig. 3-12 The generality of memory window overestimation                                                                              |

| Fig. 3-13 Schematics of generalized overestimation case and consistent case                                                           |

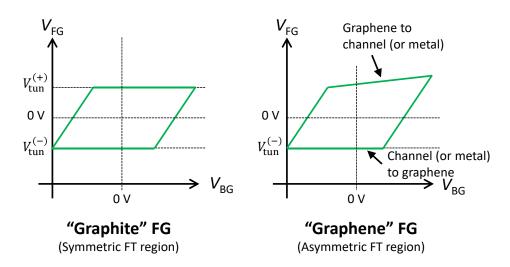

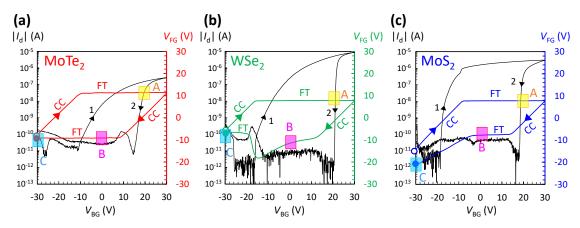

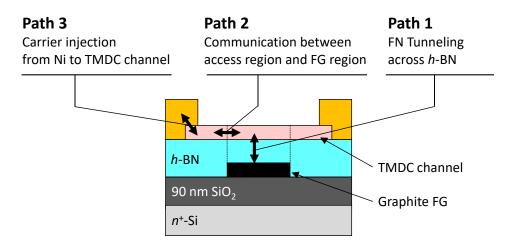

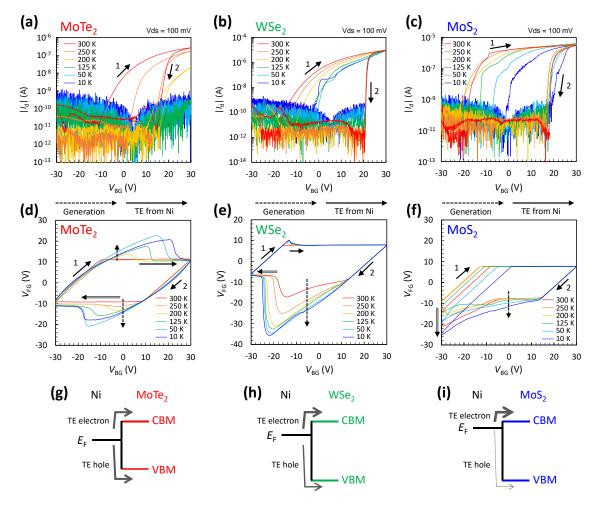

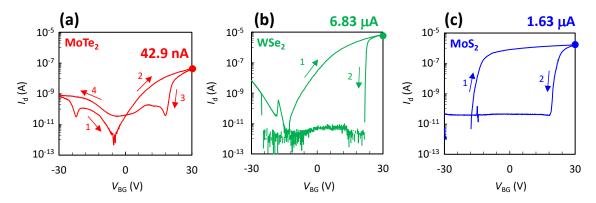

| Fig. 4-1 Measured $V_{FG}$ trajectories superimposed on $I_d-V_{BG}$ round sweep transfer                         |

|-------------------------------------------------------------------------------------------------------------------|

| curves 89                                                                                                         |

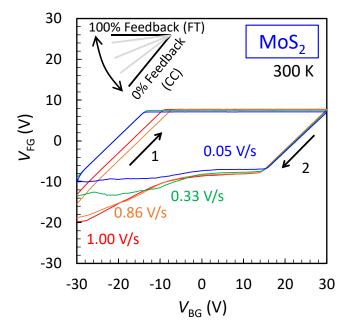

| <b>Fig. 4-2</b> $V_{\rm FG}$ trajectories of the MoS <sub>2</sub> device with various $V_{\rm BG}$ sweeping rates |

| Fig. 4-3 The correspondence of the $V_{FGS}$ in FT region and measured tunnel starting voltages.                  |

|                                                                                                                   |

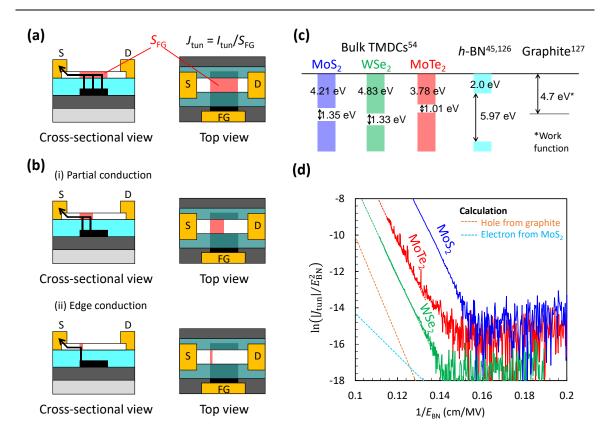

| Fig. 4-4 Three tunneling paths in 2D heterostructured NVM device with access region. 92                           |

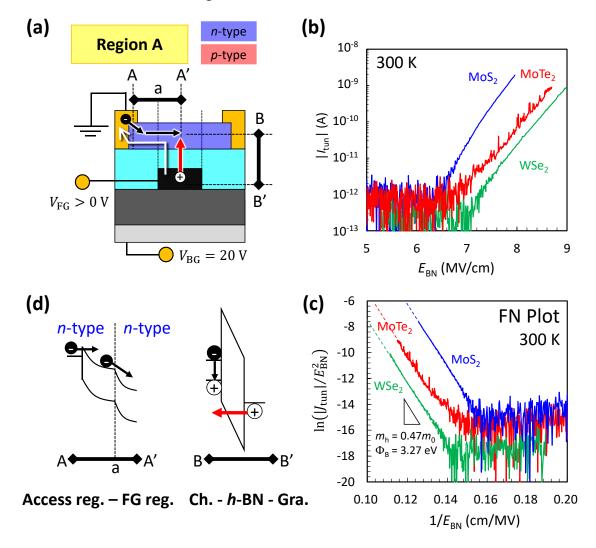

| Fig. 4-5 Schematics of operation mechanism and important results in region A                                      |

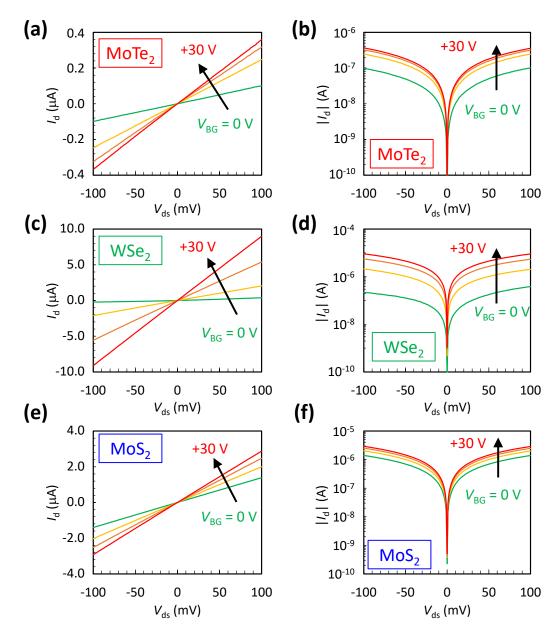

| Fig. 4-6 The ohmic conduction of each device. 94                                                                  |

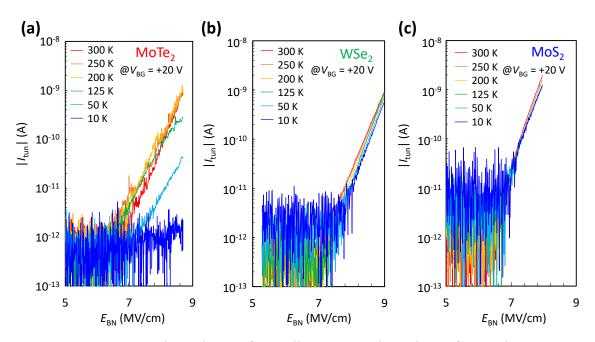

| Fig. 4-7 Temperature dependence of tunneling currents in region A                             |

|-----------------------------------------------------------------------------------------------|

| Fig. 4-8 The discussions for the validity of the calculations for FN plot. Band alignment of  |

| the 2D materials <sup>45,54,126,127</sup> is also shown                                       |

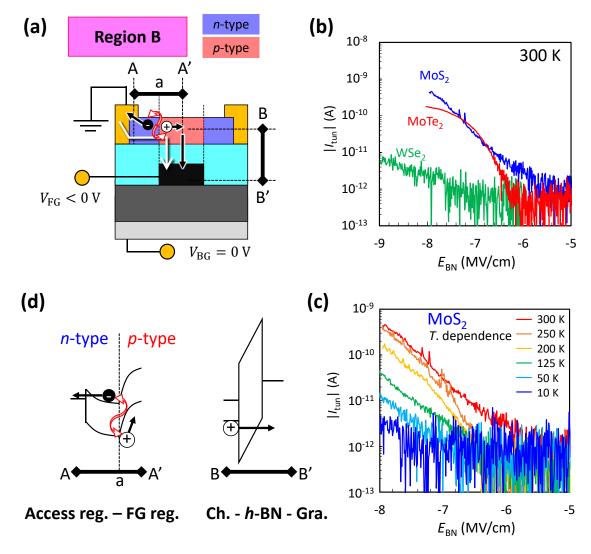

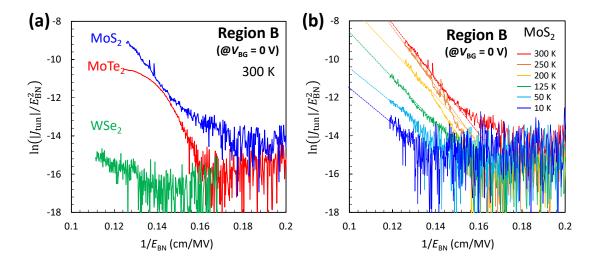

| Fig. 4-9 Schematics of operation mechanism and important results in region B                  |

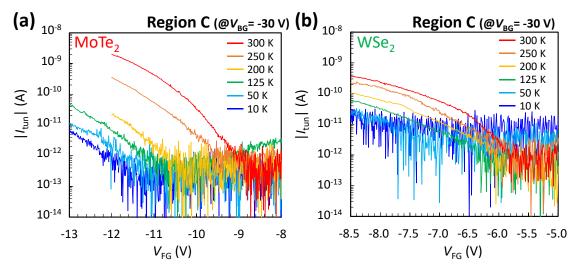

| Fig. 4-10 Temperature dependence of tunneling current in region B101                          |

| <b>Fig. 4-11</b> FN plots of <b>Fig. 4-9(b)</b> and <b>(c)</b> 101                            |

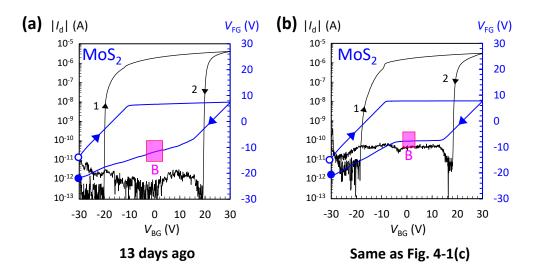

| Fig. 4-12 The $V_{FG}$ trajectories of MoS <sub>2</sub> device measured in different days103  |

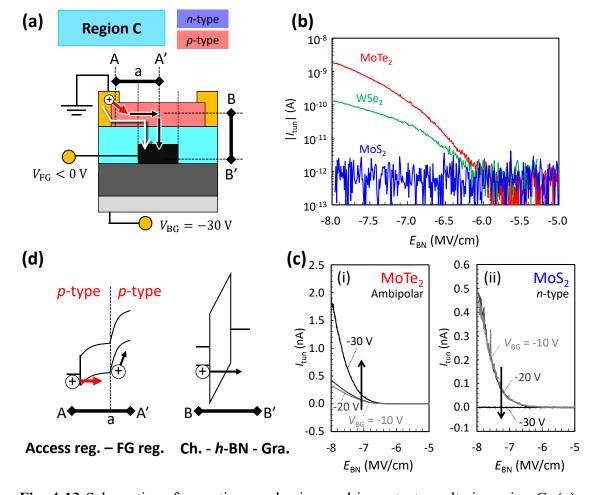

| Fig. 4-13 Schematics of operation mechanism and important results in region C104              |

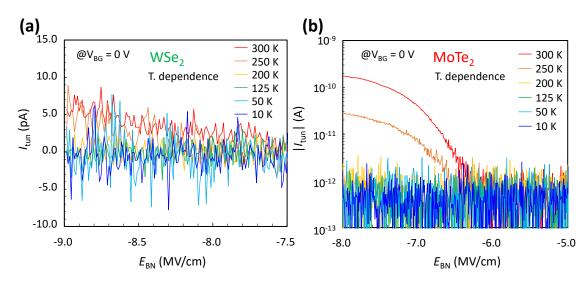

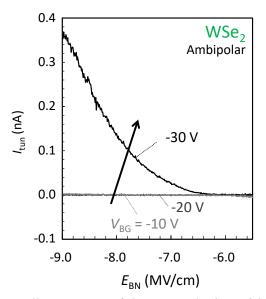

| <b>Fig. 4-14</b> Tunneling current of the WSe <sub>2</sub> device with various $V_{BG}$ 105   |

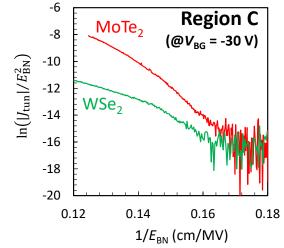

| Fig. 4-15 FN plot of the tunneling currents in region C106                                    |

| Fig. 4-16 Temperature dependence of tunneling currents in region C106                         |

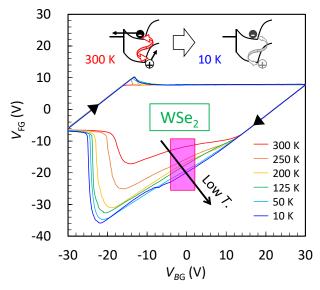

| Fig. 4-17 Temperature dependence of $V_{FG}$ trajectory of the WSe <sub>2</sub> device107     |

| Fig. 4-18 Metal-FG tunneling in the device without access region108                           |

| Fig. 4-19 Temperature dependence of $I_d$ - $V_{BG}$ round sweep transfer curves and $V_{FG}$ |

| trajectories for the MoTe <sub>2</sub> , WSe <sub>2</sub> , and MoS <sub>2</sub> devices110   |

| <b>Fig. 4-20</b> The origin of $I_d$ plateau. 114                                             |

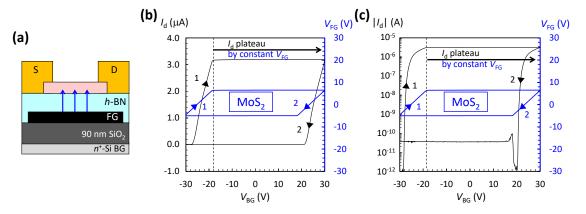

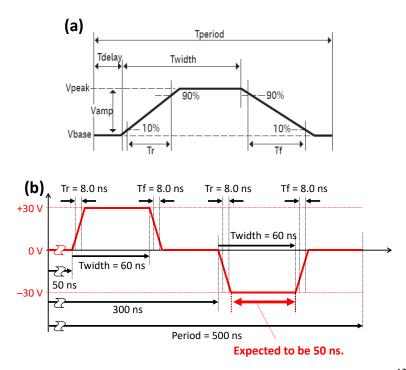

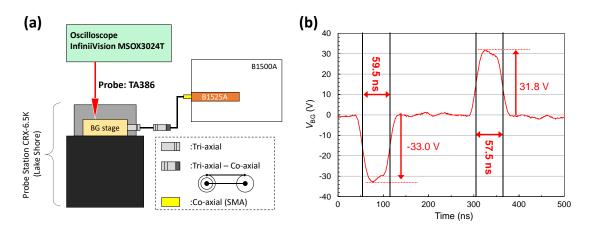

| Fig. 5-1 Definition of each parameter which constructs the output pulse <sup>129</sup> , and illustration                         |

|-----------------------------------------------------------------------------------------------------------------------------------|

| of the designed pulse, which is the fastest pulse for P/E operation in this study117                                              |

| Fig. 5-2 Measurement setup for high-speed voltage pulse and measured $V_{BG}$                                                     |

| waveform119                                                                                                                       |

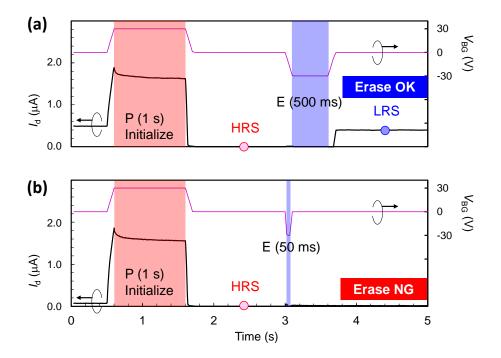

| Fig. 5-3 Operation waveforms of the MoS <sub>2</sub> device without access region120                                              |

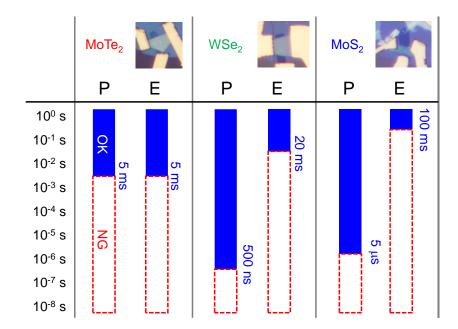

| Fig. 5-4 Measured P/E speed of the MoTe <sub>2</sub> , WSe <sub>2</sub> and MoS <sub>2</sub> devices without access region.       |

|                                                                                                                                   |

| <b>Fig. 5-5</b> $I_d$ – $V_{BG}$ round sweep curves just before the speed test for the MoTe <sub>2</sub> , WSe <sub>2</sub> , and |

| MoS <sub>2</sub> devices                                                                                                          |

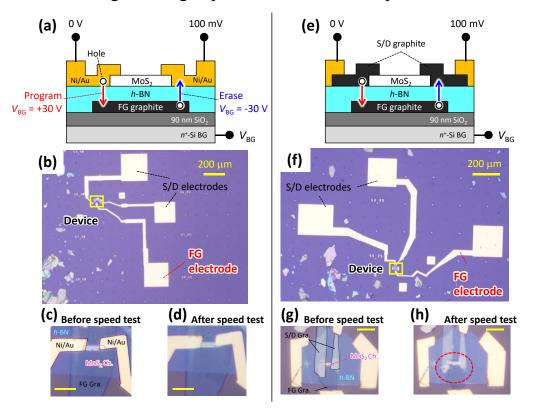

| Fig. 5-6 Schematics and photos of the devices with huge FG electrode124                                       |

|---------------------------------------------------------------------------------------------------------------|

| Fig. 5-7 Typical TEM image of 2D heterostructure underneath the thermally evaporated                          |

| Ni125                                                                                                         |

| Fig. 5-8 Typical tunneling current characteristic after the degradation of <i>h</i> -BN for the metal         |

| contact device126                                                                                             |

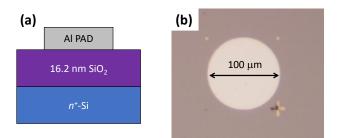

| Fig. 5-9 Schematic and photo of fabricated MIS capacitor                                                      |

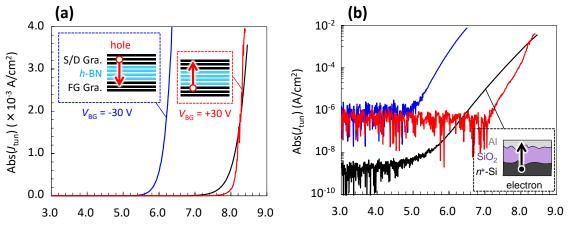

| Fig. 5-10 The comparison of tunneling current in 2D system and 3D system                                      |

| Fig. 5-11 Possible origin of the difference of tunnel starting fields for tunneling currents in               |

| 2D system                                                                                                     |

| Fig. 5-12 The design of coupling ratio of the device                                                          |

| Fig. 5-13 Schematics and photos of the device with small FG pad131                                            |

| Fig. 5-14 Speed test results of the graphite contact device                                                   |

| Fig. 5-15 Speed test results of the metal contact device                                                      |

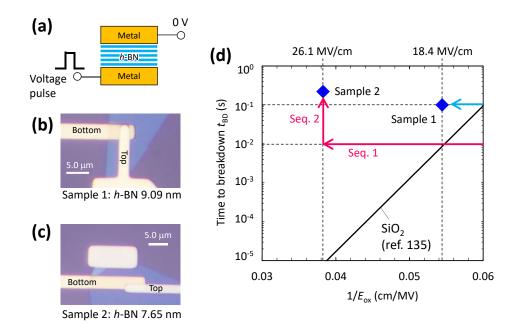

| Fig. 5-16 Relationship between time to breakdown and applied electric field of ultra-thin                     |

| SiO <sub>2</sub> <sup>135</sup> 135                                                                           |

| Fig. 5-17 Illustration of expected $V_{FG}$ response in ultra-fast time scale136                              |

| Fig. 5-18 Unmeasurable $V_{FG}$ response due to low internal resistance of an                                 |

| oscilloscope136                                                                                               |

| Fig. 5-19 Breakdown strength of <i>h</i> -BN under fast voltage pulse stress137                               |

| <b>Fig. 5-20</b> Comparison of the achievement in this work and other memory technologies <sup>12,139</sup> . |

|                                                                                                               |

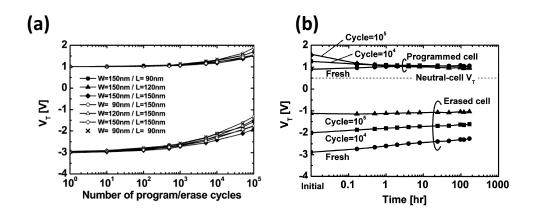

| Fig. 5-21 Retention and endurance characteristics of the $MoS_2$ device with access region                    |

| and huge FG electrode140                                                                                      |

| Fig. 5-22 Transition of $I_d$ - $V_{BG}$ transfer curves during endurance test141                             |

| Fig. 6-1 Band alignment of various TMDCs, elemental contact metals and metal/buffer |

|-------------------------------------------------------------------------------------|

| contacts <sup>142</sup> 147                                                         |

| Fig. 6-2 Barrier height engineering for 4th generation device147                    |

# Appendix

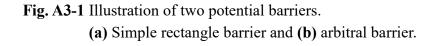

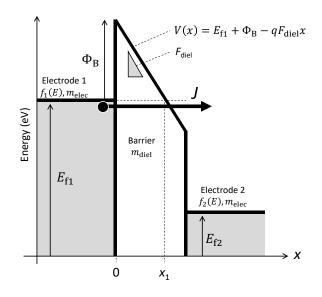

| Fig. A3-1 Illustration of two potential barriers       |                  |

|--------------------------------------------------------|------------------|

| Fig. A3-2 Illustration of triangle barrier and FN tunn | eling current158 |

## **List of Tables**

| Table 1-1. Typical FoM values and market readiness for established and emerging memory                   |

|----------------------------------------------------------------------------------------------------------|

| technologies <sup>12</sup> 5                                                                             |

| Table 1-2. Evolution of 2D materials-based flash memory devices.    39                                   |

| <b>Table 1-3.</b> Summary of the previous studies. Materials, structure and characteristics. $\cdots$ 49 |

|                                                                                                          |

**Table 2-1.** Thickness of each 2D material measured by AFM.54**Table 2-2.** Important properties of TMDCs used for the channel<sup>54</sup>.55

**Table 4-1.** Summary of the previous studies. Materials, structure and characteristics. ... 88**Table 4-2.** Three mechanisms related to electron-hole pair generation in region B.....102

| Table 5-1. Comparison of capabilities between WGFMU and HV-SPGU <sup>129</sup> 117 |

|------------------------------------------------------------------------------------|

| Table 5-2. Pulse range and pulse parameter of HV-SPGU <sup>129</sup> .         118 |

| Table 5-3. Experimental procedure in Fig. 5-19(d) for sample 1                     |

| Table 5-4. Experimental procedure in Fig. 5-19(d) for sample 2                     |

Table 6-1. The 4th generation device as the conclusion of this study.

145

# Chapter 1 Introduction

### 1.1 Non-volatile Memory Technology

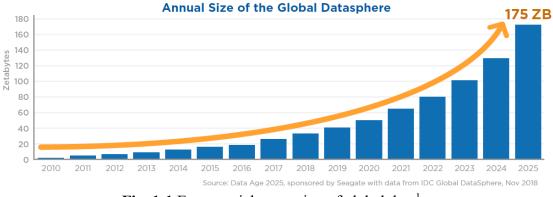

Non-volatile memory (NVM) is one of the most important technologies in our society. Today, people use a smartphone, personal computer (PC), tablet *etc.* in their daily life. These computing systems must employ a non-volatile memory to store the huge amount of data without power supply. Thanks to its non-volatility, we can save the data and shut down our PC whenever we want, and we do not have to worry about our smartphone running out of battery with data loss. In addition, the popularization of internet and great progress of hardware technologies have resulted in the data driven society. As shown in **Fig. 1-1**, International Data Corporation reported the exponential expansion of global data in 2018<sup>1</sup>. This means that, the importance of NVM technology will continue to increase in the future.

Fig. 1-1 Exponential expansion of global data<sup>1</sup>.

At the beginning of information and communication technology (ICT) era, hard disk drive (HDD) had played an important role. Due to its huge capacity, HDD is often treated as a *storage* rather than a *memory*. In case of an HDD, ferromagnetic materials are significant to store the binary data "0" and "1" which correspond to poles of magnet. Magnetization of these materials can be electrically controlled<sup>2</sup>, and has an immunity against an environment, resulting in non-volatility of HDD. In other words, *spin* of electron (a) Control gate (CG) (b) Floating gate (FG) electron  $n^+$   $n^+$   $n^+$ p-well p-well

is a key property for non-volatility.

Fig. 1-2 Schematic of a flash memory cell with (a) empty FG and (b) filled FG.

Fig. 1-3 NOR and NAND array configuration of flash memory cells<sup>4</sup>.

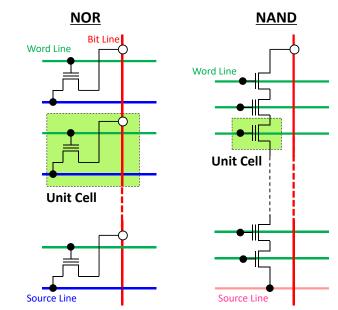

In 1984, F. Masuoka et al. has developed epoch-making non-volatile memory device called *flash memory*<sup>3</sup>. Schematic of flash memory is shown in **Fig. 1-2**. Charge trapping layer called floating gate (FG) is inserted between a control gate (CG) and channel. By applying the large positive (negative) voltage to the CG, electrons can be injected to (ejected from) the FG. Depending on a state of FG, that is, whether filled by electrons or empty, the device has two threshold voltages, corresponding to binary "0" and "1", respectively. In addition, NAND type array configuration has realized the large-capacity semiconductor non-volatile memory, whereas NOR type array configuration has been used as an instruction storage memory for a processing unit. Both array configurations are

illustrated in **Fig. 1-3**<sup>4</sup>. Thanks to the large capacity of NAND flash memory, it has created new market such as USB drive and MP3 player instead of tape media<sup>5</sup>. Over the past 40 years, NAND flash memory technology has been drastically updated. The details of these improvement and challenges are presented in next section. For the flash memory technology, *charge* of electron is a key property for non-volatility.

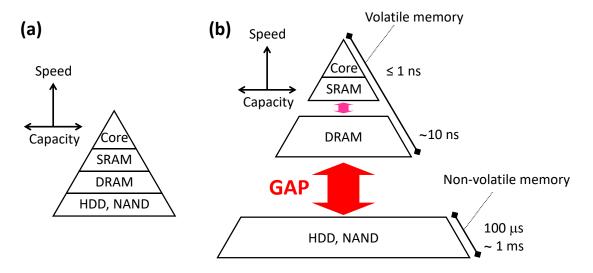

Fig. 1-4 Memory hierarchy in computing system at (a) early stage of ICT era, and (b) current.

Of course, volatile memories such as static random access memory (SRAM) and dynamic RAM (DRAM) have also played an important role in computing system. Since the volatile memories have lower capacity but higher speed than HDD and flash memory, these are used as a cache memory or working memory. At the early stage of ICT era, as illustrated in **Fig. 1-4**, non-volatile memories (NAND flash, HDD) and volatile memories (SRAM, DRAM) had well cooperated for an efficient computing. However, drastic improvements of each technology have resulted in the huge speed and capacity gap between memories. In addition, scaling of the metal-oxide-semiconductor field effect transistor (MOSFET) have led unexpected performance degradations called short channel effects (SCEs)<sup>6</sup>. One of SCEs is the increase of leakage current of MOSFET, which increases static power of SRAM and DRAM since MOSFET is a key component of them. For the purpose of filling the gap and achieving energy efficient computing, novel non-volatile memory technologies have been emerged recently. At this stage, not only *spin* and

*charge* of electron, but also any physics can be a key component of non-volatility. For example, phase change RAM (PCRAM) utilizes the *phase change* between amorphous phase and crystal phase of the material<sup>7</sup>, and resistive RAM (ReRAM) often utilizes the *soft breakdown* of the metal-insulator-metal structure which can be controlled by applying voltage<sup>8</sup>. Especially, the ReRAM whose filament is formed by metal ion is often referred to as conductive bridge RAM (CBRAM). Whereas spin-transfer-torque magnetic RAM (STT-MRAM) utilizes the *spin* of electron as a key physics as well as HDD, it is manipulated in a different way. The new storage device called magnetic tunnel junction (MTJ) is employed, and spin-transfer-torque by spin polarized current changes the state of MTJ<sup>9,10</sup>. In addition, ferroelectric RAM utilize the *ferroelectricity* of the material<sup>11</sup>. Typical performances of them are summarized in **Table 1-1**<sup>12</sup>. Although some of emerging memories are in the market, flash memory still maintains its dominant position as solid-state drives (SSDs) or embedded storage in mobile applications<sup>4</sup>. Important point is that, to fill the gap with non-volatility. We can take any option to achieve it. No one knows what will be an essential non-volatile technology.

| Table                       | ter. Typical Fo         | oM values and n               | narket readiness               | Table 1-1.       Typical FoM values and market readiness for established and emerging memory technologies <sup>12</sup> . | d emerging men           | oory technologies        | 5 <sup>12</sup> .        |

|-----------------------------|-------------------------|-------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|

| FoM                         | SRAM                    | DRAM                          | Flash NAND<br>(planer)         | ReRAM                                                                                                                     | FeRAM                    | PCM                      | STT-MRAM                 |

| Density [bytes per chip]    | $\approx 10 \text{ MB}$ | 1-10 GB                       | $\approx 10~{ m GB}$           | ≈1 GB                                                                                                                     | $\approx 1 \text{ MB}$   | 1-10 GB                  | 10–100 MB                |

| Cell size [F <sup>2</sup> ] | >100                    | 6-10                          | 45                             | 6–20                                                                                                                      | 15-40                    | 6-20                     | 35-40                    |

| Write time                  | <10 ns                  | $\approx \! 10 \ \mathrm{ns}$ | $\approx \! 100 \ \mathrm{ms}$ | 10–100 ns                                                                                                                 | $\approx 100 \text{ ns}$ | 10-100 ns                | $\approx 10 \text{ ns}$  |

| Program energy per bit      | 1-10 pJ                 | 1-10 pJ                       | $pprox 10  \mathrm{nJ}$        | $\approx 10 \text{ pJ}$                                                                                                   | 1 pJ                     | 0.1–1 nJ                 | <1 pJ                    |

| Retention                   | Volatile                | Volatile<br>10–100 ms         | Nonvolatile<br>>10 years       | Nonvolatile<br>>10 years                                                                                                  | Nonvolatile<br>>10 years | Nonvolatile<br>>10 years | Nonvolatile<br>>10 years |

| Endurance                   | >10 <sup>15</sup>       | >10 <sup>15</sup>             | $10^{2}-10^{5}$                | $10^{6} - 10^{9}$                                                                                                         | >10 <sup>15</sup>        | $10^{6}-10^{9}$          | >10 <sup>15</sup>        |

| Maturity                    | Product                 | Product                       | Product                        | Early product                                                                                                             | Product                  | Early product            | Early product            |

| Market price [\$ per GB]    | 10–100 k                | $\approx\!10$                 | ≈1                             | ≈1 k                                                                                                                      | 10–100 k                 | 10-100                   | 1-10 k                   |

Chapter 1. Introduction

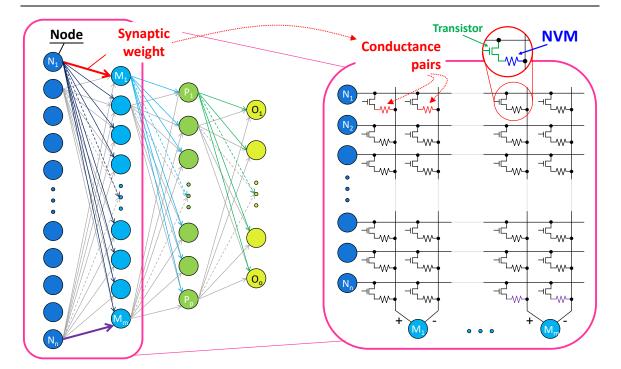

**Fig. 1-5** Schematic of typical neural network and its hardware implementation by using non-volatile memory devices<sup>14</sup>.

For the future, expansion of the territory of non-volatile memory is easy to be predicted, since many exciting applications have been emerged beyond the classical PCs. One interesting application is the neuromorphic computing. In 2012, great success of deep learning was announced in terms of object recognition<sup>13</sup>, which had been strongly supported by the progresses of hardware including memory devices, and the popularization of internet. Deep learning utilizes the neural network which mimic the human brain. Typical neural network and its conceptual hardware implantation is illustrated in **Fig. 1-** $5^{14}$  where a neuron corresponds to a node, and synapse which is a connection point between neurons, corresponds to the weighted edge. As shown in the figure, NVM devices are required to store the weight. The purpose of their non-volatility is to save energy in neuromorphic computing. Here, each node performs the product-sum calculation as follows:

$$y_i = w_1 x_1 + w_2 x_2 + \dots + w_n x_n, \tag{1.1}$$

where,  $y_i$  is a calculated result of *i*-th node in current layer,  $x_n$  represents the input from *n*-

th node in previous layer, and  $w_n$  represents the synaptic weight. Therefore, neural network can be implemented by the NVM array since it can perform following calculation:

$$I_i = G_1 V_1 + G_2 V_2 + \dots + G_n V_n, \tag{1.2}$$

where,  $I_i$  is current as a calculated result of *i*-th node,  $G_n$  represents the conductance of each NVM device as a synaptic weight, and  $V_n$  represents the voltage as a input from previous layer. Since machine learning technique including deep learning has versatility, it has been utilized everywhere, and its application will be further expanded, requiring the further improvement of non-volatile memory devices.

### 1.2 Si-based Flash Memory

In this section, Si-based flash memory technology is overviewed by focusing on a memory cell. Flash memory, which is most popular semiconductor non-volatile memory, has changed the world as mentioned above. Tremendous efforts had been devoted to miniaturize the planer cell for realizing a low bit cost memory chip. Although planer cell finally reached the scaling limit, three dimensional (3D) NAND array which pave the alternative way for lowering the bit cost was proposed<sup>15</sup>. Although 3D NAND is in the mainstream of the recent market, its several challenges have been pointed out<sup>16</sup>.

#### 1.2.1 Planer Cell

Fig. 1-6 Comprehensive roadmap of NAND flash technology<sup>5</sup>.

Since NAND flash memory was on the market in 1992, planer cell had been utilized as a memory cell for a long time. Comprehensive scaling roadmap of NAND flash memory technology by S. Aritome is shown in **Fig. 1-6**<sup>5</sup>. According to the figure, planer cell

technology had been used until the middle of 2010s. In this excellent miniaturization for low bit cost, there are two important requirements. One is the isolation between neighboring cells, and the other is to ensure the capacitive coupling ratio between FG and CG.

Since flash memory cell is operated in a memory array, isolation between neighboring cells is very important. Whereas local oxidation of silicon (LOCOS) was used for isolation at the early stage of production (LOCOS cell in **Fig. 1-6**), shallow trench isolation (STI) replaced the role of LOCOS at the end of 1990s (SA-STI cell in **Fig. 1-6** where SA stands for *self-aligned*).

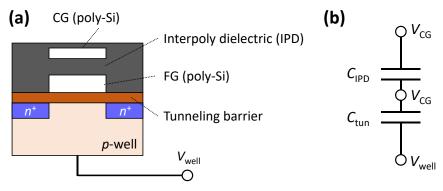

Fig. 1-7 (a) Typical planer cell structure and (b) its equivalent circuit.

Capacitive coupling ratio is related to the program and erase (P/E) operation. As schematically shown in **Fig. 1-7(a)**, typical planer cell has FG FET structure, where poly-Si is usually used as CG and FG. Here, insulator between FG and channel is called tunneling barrier or tunneling oxide, while the insulator between CG and FG is usually called interpoly dielectric (IPD). Therefore, as shown in **Fig. 1-7(b)**, gate stack of planer cell equivalently represented by the serial connection of these capacitances, where  $C_{IPD}$  and  $C_{tun}$  are the capacitance of IPD and tunneling barrier, respectively. When  $V_{CG}$  is applied to the CG and *p*-well is grounded ( $V_{well} = 0$  V), potential of FG ( $V_{FG}$ ) can be determined by following equation:

$$V_{\rm FG} = \frac{C_{\rm IPD}}{C_{\rm IPD} + C_{\rm tun}} V_{\rm CG}.$$

(1.3)

Since large  $V_{FG}$  is required for tunneling between the FG and channel, large capacitive

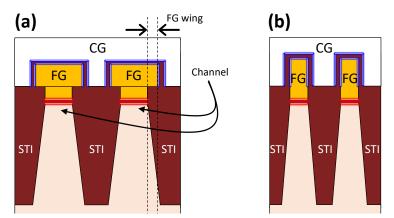

coupling ratio is helpful for low voltage operation. Its typical value is  $0.6^{17}$ . For this purpose, as shown in **Fig. 1-8(a)**, FG is capped by IPD and CG for SA-STI cell with FG-wing. Due to the requirement for further miniaturization, it was updated to SA-STI cell without FG-wing as shown in **Fig. 1-8(b)**. The active area of  $C_{poly}$ , highlighted by blue is larger than that of  $C_{tun}$ , highlighted by red, to ensure the coupling ratio.

Fig. 1-8 Cross-sectional view of SA-STI cell (a) with and (b) without FG wing<sup>5</sup>.

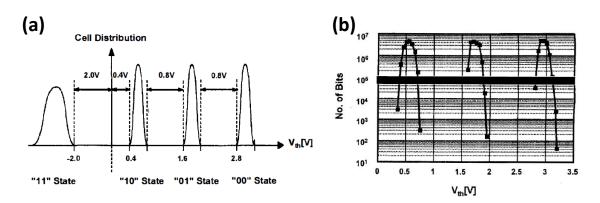

Although low bit cost is a first priority of memory, single cell-level performance should also be focused on. One important metric is a memory window defined by the difference of threshold voltages. For the further reduction of bit cost, multi-level cell (MLC) technology, i.e., more than one bit are represented by one cell, has been developed. Actually, the word *multi-level cell* often represents the 2 bits/cell, while triple-level cell (TLC), quad-level cell (QLC), and penta-level cell (PLC) represent 3 bits/cell, 4 bits/cell and 5 bits/cell, respectively. **Fig. 1-9** shows one example of  $V_{th}$  distributions of multi-level cell<sup>18</sup>. It is clear that the large memory window is required for multi-level cell technology to ensure the appropriate margin between the states.

Fig. 1-9 One example of  $V_{\rm th}$  distribution of multilevel cell. (a) Designed and (b) measured<sup>18</sup>.

P/E speed is also important because it determines the range of applications. Since NAND flash memory has a large capacity while its speed is low (100  $\mu$ s ~ 1 ms), it is used as a storage rather than working memory. Retention and endurance are related to the reliability of flash memory cell. Retention characteristic represents how robust the  $V_{th}$ s of the device against time. Generally, non-volatile memory is required to keep the data for 10 years without power supply. Since 10 years are too long to test, thermal accelerated test is often used for the evaluation<sup>19,20</sup>. Endurance characteristic represents how robust the  $V_{th}$ s of the device against P/E cycles. According to the **Table 1-1**, typical value is 10<sup>2</sup>~10<sup>5</sup> cycles<sup>12</sup> while it strongly depends on the product.

#### 1.2.2 Scaling Limit of Planer Cell

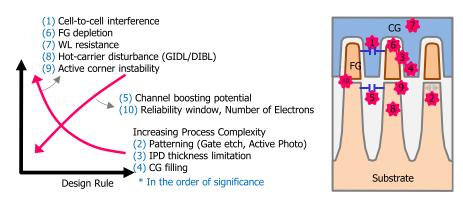

**Fig. 1-10** Scaling limitations in planer cell. The number indicates the seriousness. Smaller value means more serious<sup>16</sup>.

As well as MOSFET, there are various scaling limitations for planer cell as shown in **Fig. 1-10**<sup>16</sup>. According to the literature, most important issue is that cell-to-cell interference (CTCI). Since the distance between cells is shortened with scaling, neighboring FGs are coupled via parasitic capacitance. Thus, when the FG potential of selected cell is changed by electron injection or ejection, that of neighboring cell is also changed undesirably. As long as the capacitive coupling ratio can be ensured, reducing the FG thickness is one simple solution for  $CTCI^{21}$ .

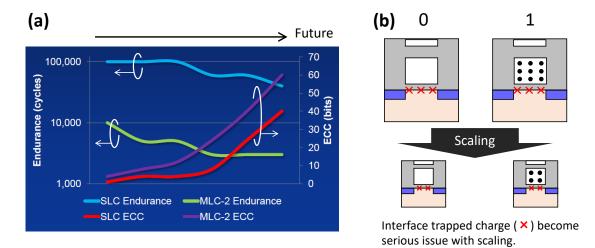

**Fig. 1-11 (a)** Endurance and ECC bits trends<sup>22</sup>. Corresponding to the degradation of endurance, more ECC bits are required. **(b)** Conceptual illustration of severe effect by the interface trapped charges in a scaled cell.

On the contrary, cell-level reliability issue should also be focused on. As shown in Fig. 1-11(a)<sup>22</sup>, endurance is predicted to be degraded with scaling. The degradation is more severe for multi-level cell. In addition, as shown in Fig. 1-11(b), the effect of single trapped charge on the Vth distribution become severe with the scaling, since the number of charges stored in the FG is decreased. Roughly speaking, the FG is scaled threedimensionally while the interface is scaled two-dimensionally, resulting in the severe condition for the scaled device. Due to this, "0" and "1" may no longer be distinguished. These *cell-level* reliability issues have been masked with advanced *system-level* techniques such as an error correction by error correction code (ECC) bits and a wear leveling, which is a technique to average the P/E cycles of each cell. Probably, in order to increase the presence of their product on the market, some cell-level reliability issues have been sacrificed instead of lowering bit cost. Although the severe reliability issues shown in Fig. 1-11(a) is well known, multi-level scheme is often accepted. Needless to say, however, if the cell-level reliability issues are overcome, the system-level technique can be much simpler. Alternatively, if the system-level techniques are remained, more advanced cell such as TLC, QLC, and PLC cell can be realized.

In case of planer cell, the conflict between the scaling and performance degradation finally reached the insurmountable phase.

### 1.2.3 Three-dimensional Cell

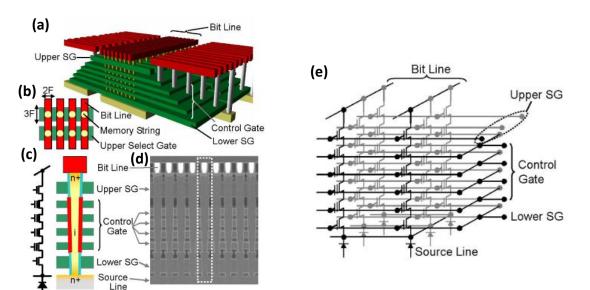

**Fig. 1-12 (a)** Birds-eye view and **(b)** top-down view of the 3D flash memory. **(c)** Enlarged view of the memory string, and **(d)** cross-sectional SEM image of the 3D flash memory array. **(e)** Equivalent circuit of the 3D flash memory<sup>23</sup>.

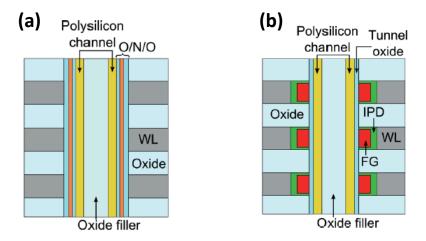

Paradigm shift was occurred in 2007 by 3D NAND cell array<sup>15,23</sup> shown in **Fig. 1-12**. In 3D NAND flash memory, its capacity can be increased by stacking cell layers, that is, the density of cells can be increased free from lateral scaling. Therefore, design rule can be relaxed, and the space between neighboring cells is easy to be assured. Consequently, various scaling penalty of planer cell could be overcome. One example shown in **Fig. 1-13** which is reported at 2017 IEEE International Memory Workshop (IMW)<sup>24</sup>. In addition, charge trap (CT) type cell<sup>25</sup> is coming into use instead of FG type cell<sup>26</sup>, since vertical CT type cells are easy to be fabricated as compared with vertical FG type cell. Typical crosssectional views of them are shown in **Fig. 1-14**<sup>27</sup>. Nowadays, 3D NAND is in the mainstream, and whether to use CT type or FG type strongly depends on the strategy of each company.

Fig. 1-13 Performance comparison between planer NAND cell and 3D NAND cell<sup>24</sup>.

**Fig. 1-14** Cross-sectional images of (a) CT type and (b) FG type 3D NAND flash memory<sup>27</sup>. CT type is sometimes employed for 3D NAND due to its structural simplicity.

#### 1.2.4 Challenges in Three-dimensional Cell

Although some issues which planer cell encountered was temporally overcome, the glory of 3D cell will not last forever. The number of stacking layers has been increased<sup>28</sup>, and at present, it has reached 176 layers<sup>29</sup>. However, it must have a limitation. In addition, while lateral scaling (× 1/ $\alpha$ ) could increase the density within a fixed area by the square (×  $\alpha^2$ ), vertical stacking (×  $\beta$ ) could increase the density only by the same amount of the multiplication (×  $\beta$ ), where  $\alpha$  and  $\beta$  are the constants larger than one.

One possible solution is that the scaling of layer thickness. However, decreasing thickness of each layer makes neighboring cells closer, that is, same scaling limitations in planer cell shown in **Figs. 1-10** and **1-11** reappear. If the charge trap layer is cylindrically covered the channel pillar, charge spreading become a serious issue as shown in **Fig. 1-15**<sup>30</sup>. Moreover, poly-Si channel of 3D NAND is often problematic due to its grain boundary. For example, instability of read current has been reported due to the grain boundary<sup>31,32</sup>.

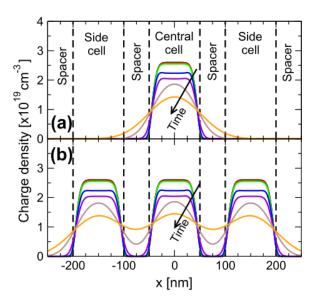

**Fig. 1-15** Simulation study of charge spreading in CT type 3D NAND flash memory for (a) neutral side cells and (b) programmed side cells<sup>30</sup>.

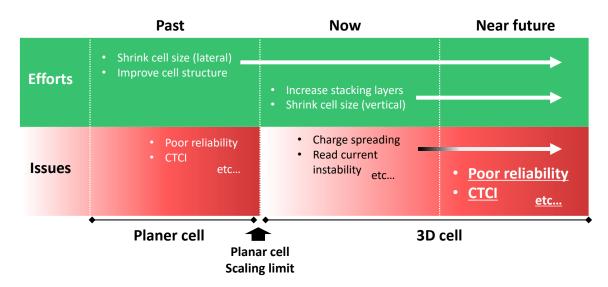

**Fig. 1-16** Brief summary of efforts and issues for Si-based flash memories. Although breakthrough was achieved by 3D NAND technology, the glory will not last forever.

Above discussions are summarized in **Fig. 1-16**. Previously, planer cell was in a mainstream of NAND flash memory product. For achieving low bit cost, tremendous efforts, including the change of cell structure, had been devoted to shrink the cell size in lateral dimension. However, many issues including poor reliability (cell-level) and CTCI (array-level) became severe issues with the scaling, and finally reached the scaling limit. Currently, even though the appearance of 3D NAND technology could solve the issues related to the lateral scaling, temporally, other issues resulted from its 3D structure and poly-Si channel have appeared. In addition, other efforts related to vertical direction have been required. In near future, consequently, same problems will be emerged again. Therefore, beyond the conventional Si technology, alternative strategy such as other material systems should be considered.

#### **1.3 2D Materials**

2D materials are composed of atomic layers which are bonded by weak van der Waals (vdW) force. Within each layer, strong covalent bonds are formed between neighboring atoms. In 2004, K. S. Novoselov and A. K. Geim et al. reported the experimental characterization of atomically thin graphene flake<sup>33</sup>. The innovative point is that they showed that atomically thin graphene can easily be isolated from bulk crystal by using scotch tape. For this achievement, they won the Nobel Prize in Physics in 2010, being the trigger for the abundant studies of 2D materials. Around 2010 is also a period when the limitation of planer technology was seriously claimed, and new strategy was aggressively explored. Therefore, it is quite natural that the graphene, which has ultra-high carrier mobility (e.g., ~15,000 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> at room temperature for multilayer graphene<sup>33</sup>), was started to be studied as a promising candidate of next generation electronic devices. Although graphene as a channel for MOSFETs has lost researcher's attention due to its zero-bandgap nature, 2D materials such as insulating hexagonal boron nitride (h-BN) and semiconducting transition metal dichalcogenides (TMDCs) have attracted much attention as candidates for new electronic/optical devices, since they have unique properties which are not limited to high mobility. Of course, graphene does not lose its importance as a 2D material. There are lots of researches for its novel properties and applications.

In this section, before discussing the 2D materials-based flash memory devices, basic properties and applications of 2D materials are overviewed. In addition, its heterostructure is also discussed.

### 1.3.1 Graphene

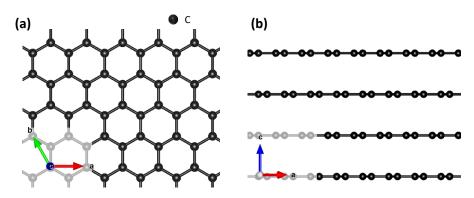

Fig. 1-17 Atomic structure of graphene. (a) Top view and (b) side view.

**Graphene** is the most popular 2D materials in the world. As shown in **Fig. 1-17**, monolayer graphene shows a honeycomb structure. 2s,  $2p_x$  and  $2p_y$  orbitals of each carbon atom are hybridized to form three  $sp^2$  orbitals, resulting in strong interatomic bonds called  $\sigma$  bond, while remained  $2p_z$  orbitals result in weak interatomic bonds called  $\pi$  bond. Since electrons in the  $2p_z$  orbitals ( $\pi$  electrons) does not contribute to the covalent  $\sigma$  bond, it can contribute to the electrical conductivity of graphene. Based on the tight-binding approach, the electronic band structure for  $\pi$  electrons in graphene is derived as follows<sup>34</sup>:

$$E(k_x, k_y) = \pm \gamma_0 \sqrt{1 + 4\cos\left(\frac{ak_x}{2}\right)\cos\left(\frac{\sqrt{3}ak_y}{2}\right) + 4\cos^2\left(\frac{ak_x}{2}\right)}, \qquad (1.4)$$

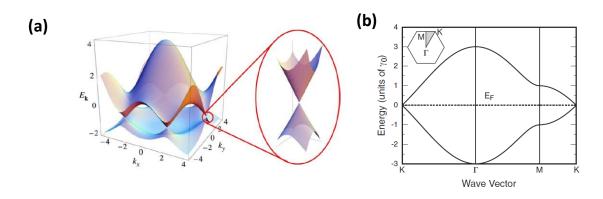

where, E,  $\gamma_0$ , and a are the energy of  $\pi$  electrons, transfer integral between nearestneighbor carbon atoms, and lattice constant of graphene (0.246 nm), respectively. In addition,  $\mathbf{k} = (k_x, k_y)$  is the wave vector. The band structure is illustrated in **Fig. 1-18**<sup>34,35</sup>. Here, the point where two cones face each other is called Dirac point. Since Fermi level  $(E_F)$  of graphene is located at Dirac point, linear *E-k* dispersion and corresponding density of states (DOS) shown in **Fig. 1-19**<sup>35</sup> play an important role for possessing many interesting properties.

**Fig. 1-18** Band structure for  $\pi$  electrons in graphene. (a) Three-dimensional view in k-space<sup>35</sup> and (b) 2D view along the lines with high-symmetry k-points<sup>34</sup>.

Fig. 1-19 Density of states of graphene as a function of energy of electron when next nearest-neighbor hopping is not considered (t' = 0). Energy term is normalized by nearest-neighbor hopping energy *t*. The details are in the litelature<sup>35</sup>.

In terms of FET applications, quantum capacitance ( $C_Q$ ) is one example of unique property of graphene. Strictly speaking, since  $C_Q$  is resulted from low DOS of 2D materials, it is not limited for the graphene but for any 2D materials. When graphene is on the gate stack such as an SiO<sub>2</sub>/ $n^+$ -Si substrate, the conductivity of graphene can be modulated via the  $n^+$ -Si back gate (BG). However, in contrast to 3D materials, graphene cannot screen the electric field from the BG completely due to its low DOS. At this time,  $E_F$  of graphene is further modulated to serve sufficient charges in the graphene for screening the electric field, that is, the voltage is dropped across SiO<sub>2</sub> and graphene itself. This can be modeled as the serial connection of two capacitances,  $C_{ox}$  for the SiO<sub>2</sub> and  $C_Q$  for the graphene.  $C_Q$ of graphene has been experimentally investigated<sup>36,37</sup>. At the early stage of 2D research, graphene was treated as a channel material for next generation transistor due to its ultra-high carrier mobility<sup>33,38</sup>. However, since graphene has no bandgap, ON/OFF ratio is not large enough for the channel material. Although the role of graphene was superseded by semiconducting TMDCs as explained below, graphene and graphite are still attracted much attention from many viewpoints such as Cu diffusion barrier<sup>39</sup>, vdW contact to TMDC FETs<sup>40</sup>, charge trapping layer of memory devices<sup>41-44</sup>, and so on.

1.3.2 *h*-BN

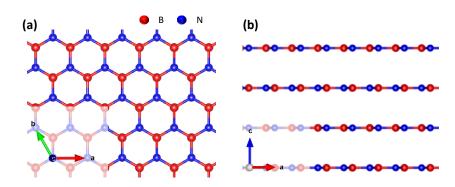

Fig. 1-20 Atomic structure of *h*-BN. (a) Top view and (b) side view.

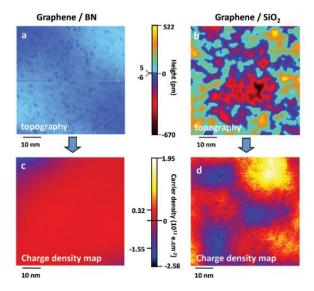

*h*-BN is the most popular 2D insulator with 5.97 eV of band gap<sup>45</sup>. High-quality *h*-BN has been grown by a temperature-gradient method under a high-pressure and high-temperature atmosphere<sup>45</sup>. Crystal structure is very similar to that of the graphene, that is honeycomb structure as shown in **Fig. 1-20**. Because the strong B-N bonding, *h*-BN has a great thermal tolerance up to  $850^{\circ}C^{46}$ . This stable property of *h*-BN allows to be used as an atomically flat substrate<sup>47</sup> and/or passivation film<sup>48</sup>. For example, **Fig. 1-21** clearly shows that the ultimate flatness of *h*-BN results in the uniform charge distribution of graphene<sup>47</sup>. More importantly, since *h*-BN has a SiO<sub>2</sub> comparable dielectric breakdown strength (~12 MV/cm, parallel to c-axis<sup>49</sup>), it is used as a gate dielectric with 2 ~ 4 of relative permittivity<sup>50</sup> for 2D heterostructured electronic devices.

Fig. 1-21 Height and charge density profile of graphene on h-BN and on SiO<sub>2</sub><sup>47</sup>.

#### 1.3.3 Transition Metal Dichalcogenides

**TMDCs** are the famous semiconducting 2D materials. Its generic formula is  $MX_2$ , where M represents a transition metal such as molybdenum (Mo) and tungsten (W), and X represents a chalcogen such as sulfur (S), selenium (Se), and tellurium (Te).

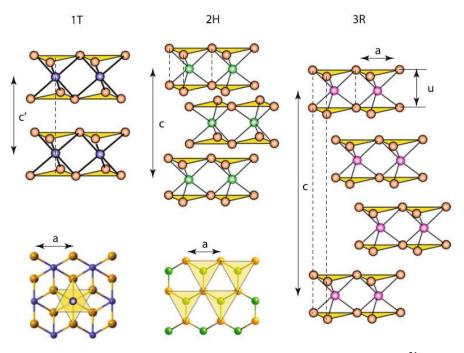

Fig. 1-22 Representative three phases of TMDC crystal<sup>51</sup>.

In TMDC crystal, each transition metal atom is covalently bonded with six chalcogen atoms. Representative three phases of TMDC crystal are shown in **Fig. 1-22**<sup>51</sup>, where 2H phase is generally used as a semiconductor with 1~2 eV of bandgap<sup>52</sup>. Here, *s*, *p*, *d*-orbitals of transition metal are hybridized to from six-fold coordinate, and each  $sp^3$  hybridized orbital of chalcogen is bonded to them. Interestingly, lone-pair electrons of chalcogen atom plays an important role in the bonding. Although standard covalent bond is formed when two atoms provide one electron per bond, for the covalent bond in TMDC crystals, vacant hybrid orbital of a transition metal is filled by lone-pair electrons in  $sp^3$  hybridized orbital of chalcogen. Hereinafter, compositional formulas such as MoS<sub>2</sub> or WSe<sub>2</sub> represents the 2H phase of them for simplicity.

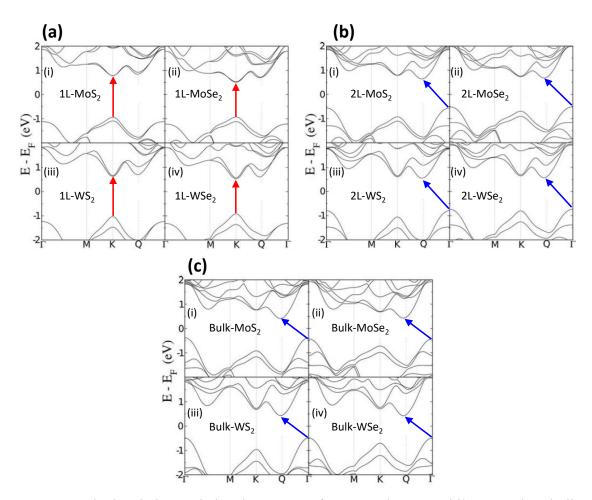

Fig. 1-23 Calculated electronic band structure of (a) monolayer, (b) bilayer, and (c) bulk  $MoS_2$ ,  $MoSe_2$ ,  $WS_2$  and  $WSe_2$ <sup>53</sup>.

One interesting property of TMDCs is that, layer number dependent electronic band structure. **Fig. 1-23** shows the calculated band structures in first Brillouin zone of MoS<sub>2</sub>, MoSe<sub>2</sub>, WS<sub>2</sub>, and WSe<sub>2</sub><sup>53</sup>. As indicated by red arrows in **Fig. 1-23(a)**, monolayer of them show the direct bandgap, while bilayer and bulk of them show the indirect bandgap as indicated by blue arrows in **Figs. 1-23(b)** and **(c)**. Interlayer interaction is decreased with decreasing the layer number, resulting in the transition. This is sometimes referred as indirect-to-direct gap transition<sup>51</sup>.

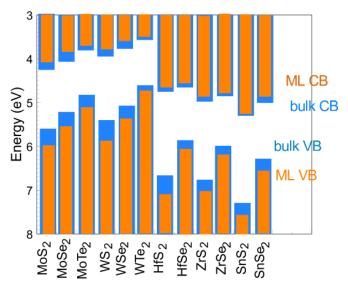

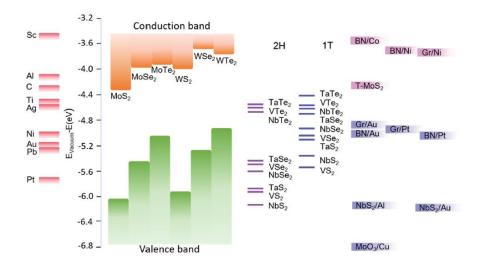

Fig. 1-24 Calculated bandgaps of bulk and monolayer (ML) TMDCs <sup>54</sup>.

**Fig. 1-24** summarizes the calculated bandgaps of TMDCs<sup>54</sup>. A wide variety of TMDCs provides us the tunability of bandgap by changing the material or layer number. This is one of the advantages of 2D material system which Si technology does not have. In addition, some high-quality TMDC crystals can be grown by a chemical vapor transport (CVT) technique or a physical vapor transport (PVT) technique<sup>55</sup>. These growth techniques enable the experimental study of various TMDCs.

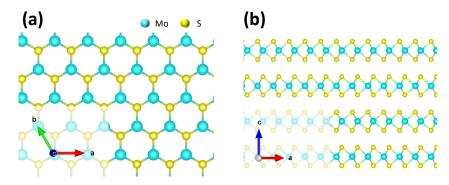

Fig. 1-25 Atomic structure of MoS<sub>2</sub>. (a) Top view and (b) side view.

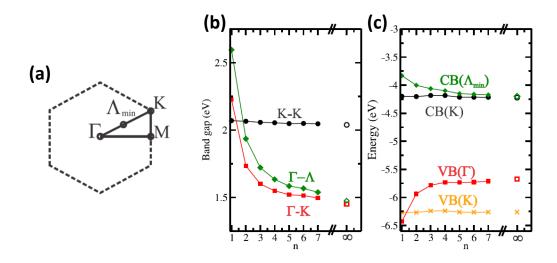

Among TMDCs, MoS<sub>2</sub> illustrated in Fig. 1-25 is a popular semiconducting material due to its air stability. Its Brillouin zone is shown in Fig. 1-26(a), and calculated bandgaps and position of the band edge as a function of the number of layers are shown in Figs. 1-26(b) and (c), respectively<sup>56</sup>. Here,  $\Lambda_{min}$  point in Fig. 1-26 is same as Q point in

Fig. 1-26 (a) Brillouin zone of  $MoS_2$  with high-symmetry *k*-points. (b) Bandgaps and (c) position of band edge as a function of the number of layers. Energy value is indicated with respect to the vacuum level<sup>56</sup>.

**Fig. 1-23**. As well as other TMDCs, the bandgap of MoS<sub>2</sub> is increased with decreasing the number of layers. As shown in **Fig. 1-26(c)**, conduction band (CB) edge at K point (CB(K)) and valence band (VB) edge at K point (VB(K)) are insensitive against the number of layers, while CB edge at  $\Lambda_{min}$  point (CB( $\Lambda_{min}$ )) and VB edge at  $\Gamma$  point (VB( $\Gamma$ )) are sensitive, resulting in different evolutions of bandgap shown in **Fig. 1-26(b)**. This can be explained by different contribution from orbitals of the atoms. Roughly speaking, layer number insensitive edges (CB(K) and VB(K)) are mainly composed of in-plane orbitals of S and Mo atoms, whereas layer number sensitive edges (CB( $\Lambda_{min}$ ) and VB( $\Gamma$ )) are mainly composed of out-of-plane orbitals of S and Mo atoms. Especially, according to their calculations, VB( $\Gamma$ ) is mainly composed of  $p_z$  of S and  $d_{z^2}$  of Mo, which are insensitive to the interlayer interaction, while VB(K) is mainly composed of  $p_x$  and  $p_y$  of S, and  $d_{xy}$  and  $d_{x^2-y^2}$  of Mo, which are insensitive to the interlayer interaction. As a result, valence band maximum point is changed from VB(K) to VB( $\Gamma$ ). More detailed calculation can be found in the reference<sup>56</sup>. It is noted that, as shown in the reference<sup>56</sup>, the difference of the layer number sensitivity cannot be fully understood by above explanations.

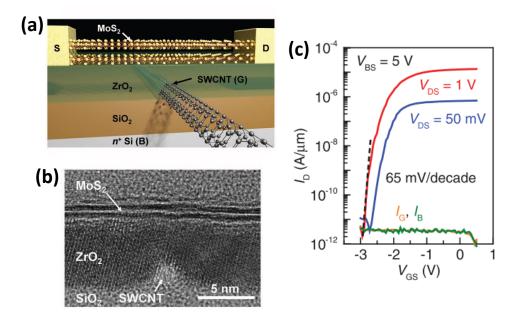

Fig. 1-27 (a) Schematic, (b) cross-sectional TEM image, and (c) transfer characteristics of 1D2D-FET<sup>58</sup>.

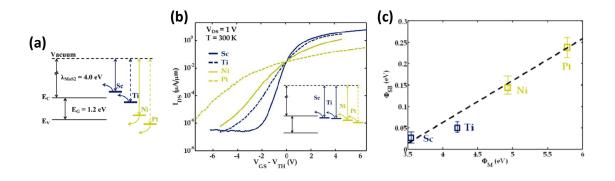

In terms of FET application, MoS<sub>2</sub> has been considered as one of promising candidate for channel material<sup>57</sup> due to its strong immunity for the short channel effects. One surprising demonstration in 2016 from Ali Javey group (UC Berkley in US) is shown in **Fig. 1-27**<sup>58</sup>. They have demonstrated the 1D2D-FET schematically illustrated in **Fig. 1-27(a)**, which composed of MoS<sub>2</sub> channel and single-walled carbon nanotube (SWCNT) gate with ZrO<sub>2</sub> gate insulator. Although the gate length is only one nanometer (**Fig. 1-27(b**)), as shown in **Fig. 1-27(c)**, 65 mV/decade of subthreshold swing and ~10<sup>6</sup> of on/off ratio can be achieved with ~10<sup>-12</sup> A/µm of off current. It should be noted that the effective channel length is about 3.9 nm, based on their simulations. Generally, operation mechanism of 2D FET is understood based of the Schottky barrier FET (SB-FET) model which well describes the ambipolar nature of 2D FET. Representative works for the MoS<sub>2</sub> FET by J. Appenzeller group (Purdue Univ. in US) is shown in **Fig. 1-28**<sup>(a)</sup>, suggesting that electron injection seems to be dominant for Sc or Ti contact while hole injection seems to be dominant for Ni or Pt contact. However, as shown in **Fig. 1-**

Fig. 1-28 Demonstration of SB-FET. (a) Band alignment between MoS<sub>2</sub> and metals when they are isolated. (b) Experimental transfer curves. Inset shows the sketch of actual band alignment. (c) Extracted Schottky barrier height ( $\Phi_{SB}$ ) as a function of metal work function ( $\Phi_M$ ). Poor slope suggests the strong Fermi level pinning at the MoS<sub>2</sub>/metal interface<sup>59</sup>.

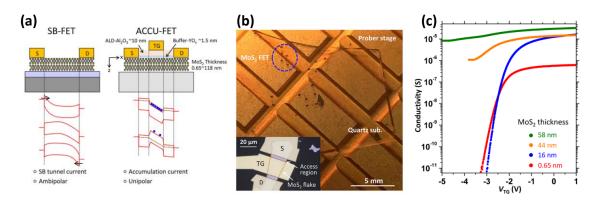

**28(b)**, *n*-type behavior of MoS<sub>2</sub> FET was obtained for all metals. According to their discussions, it is due to strong Fermi level pinning (FLP) at the metal/MoS<sub>2</sub> interface. **Fig. 1-28(c)** shows the relationship between Schottky barrier height at the interface ( $\Phi_{SB}$ ) as a function of work function of the metal ( $\Phi_M$ ). The slope  $d\Phi_{SB}/d\Phi_M$  is around 0.1, indicating that the situation is far from Schottky-Mott limit (slope = 1). Similarly, other TMDC FETs such as WSe<sub>2</sub> FET<sup>60</sup> and MoTe<sub>2</sub> FET<sup>61</sup> have been investigated based on the SB-FET model. On the contrary, N. Fang et al. have demonstrated the accumulation mode 2D FET (ACCU-FET), where partial top gate (TG) can effectively modulate the conductance of 2D channel (**Fig. 1-29**)<sup>62</sup>. ACCU-FET model was originally proposed for silicon-on-insulator MOSFET<sup>63,64</sup>, where accumulated carriers (majority carriers) contribute the current flow. This is different from MOSFET in which inversion carriers (minority carriers) do so. Based on the fact, the operation mechanism of 2D FET should be understood by the combination of SB-FET and ACCU-FET model.

Fig. 1-29 Demonstration of ACCU-FET. (a) Conceptual illustration of ACCU-FET model as compared with SB-FET. (b) Photo of fabricated device. The margin between TG and S/D electrodes is called access region. (c) Transfer curves of  $MoS_2$  FETs. Partial TG effectively modulates the conductivity especially below 16 nm of thickness<sup>62</sup>.

#### 1.3.4 2D Heterostructures

Although interesting properties of 2D materials have been predicted and demonstrated as mentioned above, for unveiling the intrinsic property of them, it was necessary to wait for the emergence and development of 2D hetero-stacking technique. In other words, *gate stack* for 2D FETs is the key to access their intrinsic properties.

In conventional 3D material system, Si/SiO<sub>2</sub> is a popular gate stack. Generally, the Si/SiO<sub>2</sub> system is fabricated by thermal oxidation of Si<sup>65</sup>, and the improvement of Si/SiO<sub>2</sub> interface quality is one driving force of development of integrated circuits (ICs), since channel of MOSFET is formed underneath the SiO<sub>2</sub>. However, volume expansion occurs during the oxidation, resulting in dangling bonds and strained region at the interface<sup>66</sup>. This is the origin of interface states in the bandgap of Si, which degrades the FET performances such as subthreshold swing (SS).

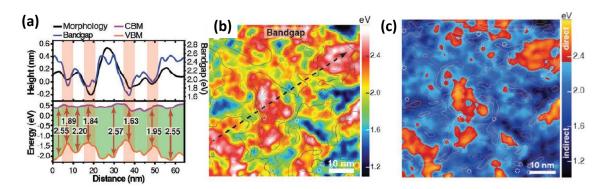

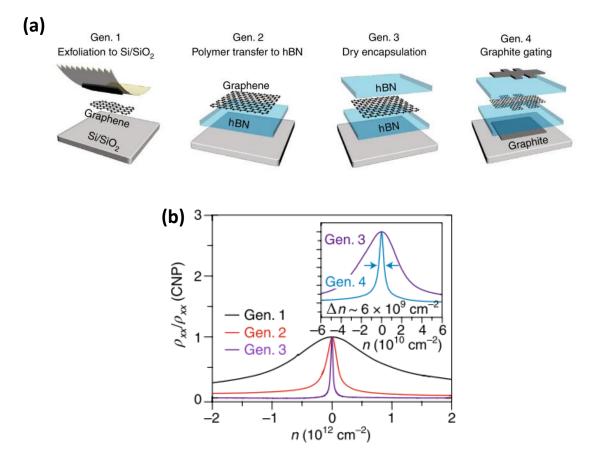

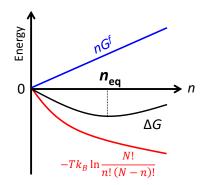

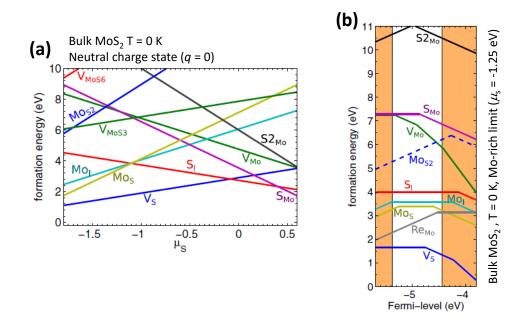

In this context, 2D materials have been attracted much attention since they are ideally free from dangling bonds on their surface. However, since the 2D FET had been fabricated on conventional 3D gate stack such as Si/SiO<sub>2</sub>, they were suffered from surface morphology and charged impurity in the 3D insulator, still preventing us to access their intrinsic properties. For example, according to the theoretical study of graphene, DOS and carrier density must be zero at the Dirac point, while current flow has been observed in graphene FET fabricated on a SiO<sub>2</sub>/Si substrate. The carrier density which contribute the current flow at the Dirac point is referred as residual carrier density ( $n^*$ ). At the early stage of graphene research, residual carrier density had been studied, and the origin has been considered to be the charged impurities on/in SiO<sub>2</sub> <sup>36</sup>. For TMDCs, situation is same. Y. H. Lee group (SKKU in Korea) reported the bandgap fluctuation of monolayer MoS<sub>2</sub> as shown in **Fig. 1-30**<sup>67</sup>. Since 2D materials can partially follow the surface morphology due to its strong strain tolerance, local strain causes the local change of band structure, resulting in the fluctuation.

30

Fig. 1-30 Bandgap fluctuation in monolayer  $MoS_2$ . (a) Line profiles along the dotted arrow in (b) where the value of bandgap is mapped. (c) Map of direct and indirect bandgaps in same region of (b)<sup>67</sup>.

Therefore, it is inevitable that 2D hetero-stacking technique would emerge to obtain dangling bond free and atomically sharp interface in the gate stack. One of the advantages of 2D materials is that, the heterostructure is free from lattice mismatch issue due to their layered nature. Moreover, fortunately, there is a stable insulating 2D material, h-BN, which can act as an atomically flat substrate by masking the surface morphology and the effect from charged impurity on/in 3D insulators.

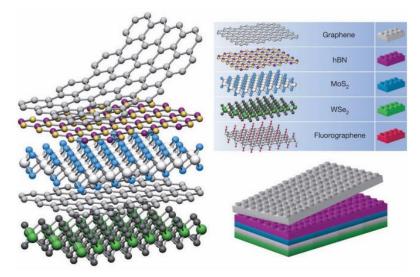

Fig. 1-31 Conceptual illustration of 2D heterostructure<sup>68</sup>.

The conceptual illustration of 2D heterostructure is shown in **Fig. 1-31**<sup>68</sup>. To realize the heterostructure, polymer assisted dry transfer technique has been developed<sup>69–72</sup>. As expected, the gate stack with 2D/2D interface(s) enables us to access their intrinsic