UDC 621, 374, 3

# MOS 形 FET を用いた A-D 変換器

An A-D Converter using MOS Field Effect Transistors

森脇 義雄\*・高羽 禎雄\*・西森 武弘\* Yoshio MORIWAKI, Sadao TAKABA and Takehiro NISHIMORI

# 1. 緒 言

筆者らはこれまで、MOS 形 FET (電界効果トランジスタ)が、増幅素子としては入力抵抗がきわめて高く、スイッチ素子としてはオン・オフの抵抗比が大でオフセット電圧、漏えい電流がないなどの特徴を有していることに着目して、各種のアナログ・パルス回路に応用することを検討し、良好な結果を得た10~40. また、同時にこれらの回路を構成するにあたっては、集積回路化に際して有利となるように、回路の全 MOS-FET 化をすすめてきた.

ここでは、通信、計測等の諸分野において、ディジタル技術を導入する際に必要不可欠な A-D(アナログ・ディジタル)変換器の集積回路化をはかることをねらいとして、前記の各種のペルス回路の組み合わせにより逐次比較方式、2進8けたの A-D 変換器を試作し、各回路の諸特性ならびに総合特性の検討を行なったので、その結果をご報告する.

### 2. 試作装置の概要

試作装置の設計条件としては、表1に掲げた事項を考慮した.

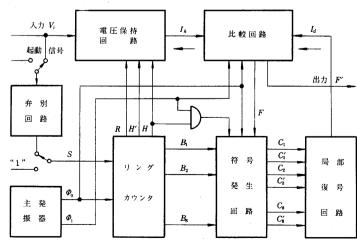

試作装置の構成の概要を図1に示す。A-D 変換方式 としては通常の逐次比較方式をとっている。ここで,主 発振器は周波数 500 kHz, 2 相の主クロック・パルス  $\Phi_0$ ,  $\Phi_1$  を,リング・カウンタはリセット・パルス R, ホー

図 1 試作装置の構成

#### 表 1 試作装置の設計条件

入力信号電圧 連続波または正パルス 0~5V 出力符号 直列または並列2進8けた  $0V\rightarrow00000000$ ,  $5V\rightarrow11111111$ 変換の正確さ ±0.1% (量子化誤差を除く) 変換時間  $20 \mu \text{ sec}$ 論理電圧 負論理 "1"=0V \"0"=6V 電源電圧 ±6V, ±12V, ±24V 周囲温度 10°C~40°C

ルド・パルスH、ビット・パルス $B_1 \sim B_8$  などを発生し、 A-D 変換動作を制御する. 符号発生回路は A-D 変換の 過程で必要な2進8けたのディジタル符号  $C_1 \sim C_8$  を発 生する. 局部復号回路はこのディジタル符号を局部復号 電流 Ia に変換する. 一方, 電圧保持回路は A-D 変換中, 入力信号  $V_i$  を蓄積し、これに対応した保持電流  $I_k$  を比 較回路から吸収する. これらの電流値は、 $V_i=0$  V のと き  $I_h=1$  mA,  $V_i=5$ V のとき  $I_h=0$  mA, また  $C_1\sim C_8$ =0 のとき  $I_d=1$  mA,  $C_1\sim C_8=1$ のとき  $I_d=0$  mA と選 ばれている. 比較回路ではこの  $I_a$  と  $I_b$  の大小を判定し て、その結果を符号Fとして符号発生回路に帰還する. 弁別回路は外部起動信号あるいは入力パルス信号じたい によって A-D 変換の起動信号 S を発生する. また、常 時 S=1 とするときには連続的、周期的に A-D 変換を 行なう. 以上の諸回路のうち, 電圧保持回路, 局部復号 回路、比較回路などのアナログ信号を扱う回路は、前記

のように全 MOS-FET 化された回路を主体として構成している。またリング・カウンタ,符号発生回路などのディジタル回路は、ダイオード・ゲートおよび混成超小形構造の J-K フリップ・フロップによって構成している。

試作装置の動作は従来の逐次比較形 A-D 変換器と同様であって,その各部波形の 1 例を図 2 に示す.変換開始前の状態では R = 1, H,  $B_1 \sim B_8 = 0$  となり, $C_1 \sim C_8$  は前回の変換結果を示している.入力信号の到来に従って起動信号 S が発生すると, $2 \mu s$  だけ遅れて,R = 0, H = 1 となり,入力信号電圧を電圧保持回路に蓄積し,さらに

\* 東京大学生産技術研究所第3部

図 2 試作装置各部の波形

パルス  $H\Phi_1$  によって符号発生回路のフリップ・フロッ プを初期状態 ( $C_1=1$ ,  $C_2\sim C_8=0$ ) にセットする. 第1 ビット $C_1$ のあたいを定めるために、これより $2\mu$ s だけ 遅れて  $I_a$  と  $I_h$  の大小判定が行なわれ、 $I_a < I_h$  であれ ば帰還信号を F=1 とし、さらに  $1\mu$ s のちに  $C_1$  を 0にリセットし、これと同時に  $C_2=1$  にセットする.  $I_d$  $>I_{4}$  であるときには F=0 とし、 $C_{1}$  は 1 のまま残され る、第2ビット $C_2$ の判定は $C_2=1$ にセットされたのち  $1 \mu s$  たって行なわれ、さらに  $1 \mu s$  たって  $C_2=1$  あるい は0 にセットされる. 以下, 同様に第8 ビット Cs まで 判定が行なわれたのち、リングカウンタは変換開始前の 状態にもどる. このとき, 出力ディジタル符号は符号発生 回路の出力  $C_1 \sim C_8$  に並列信号として得られ、また変換 の過程で比較回路から直列信号 F' としても得られる.

## 3. 回路構成

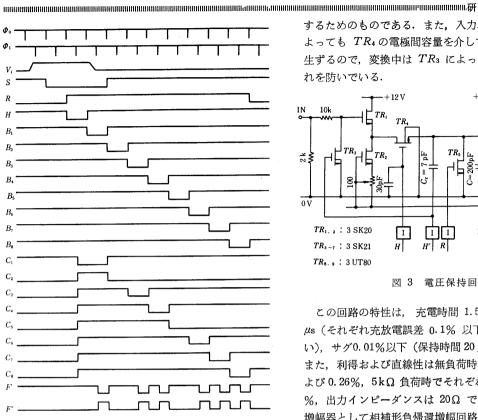

電圧保持回路を図3に示す. これは MOS-FET, TR4.5 を充放電用スイッチとして保持容量Cに入力電圧を保持 する回路 $^{1)}$  であって、前置増幅器として  $TR_{1,2}$  よりな る直列差動形増幅回路2)を,後置増幅器として TR6-9 よ りなる相補形負帰還増幅回路3)を用いている. 容量C。は 充電パルス H の後縁で TR4 の電極間容量を介して発 生するスパイクを、逆極性のパルス H' を利用して補償

するためのものである. また, 入力パルス信号の後縁に よっても TR4の電極間容量を介して保持電圧の変化を 生ずるので、変換中は  $TR_3$  によって入力を短絡し、こ れを防いでいる.

図 3 電圧保持回路

**この回路の特性は、 充電時間 1.5 μs, 放電時間 0.6** μs (それぞれ充放電誤差 0.1% 以下となるまでのあた い)、サグ0.01%以下(保持時間20 µs のとき)である. また、利得および直線性は無負荷時でそれぞれ 0.978 お よび 0.26%, 5kΩ 負荷時でそれぞれ 0.973 および 0.28 %, 出力インピーダンスは  $20\Omega$  であって、とくに後置 増幅器として相補形負帰還増幅回路を用い, 出力インピ ーダンスの減少をはかったことにより、負荷時の利得お よび直線性が改善されている. ドリフトは測定時間 30 分間で ±1.2 mV 程度であり、これはディジタル値1単 位の約 1/16 に相当する.

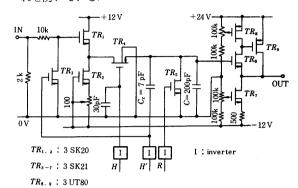

局部復号回路40を図4に示す. この回路は8組のMOS-FET スイッチ対を用いており、入力符号  $C_i=0$  のとき  $TR_i$  を on,  $TR_i$ ' を off として加重抵抗  $2^{i-1}R$  を流 れる電流を出力側に生ぜしめ、 $C_i=1$  のときには  $TR_i$

図 4 局部復号回路

ものである. 加重抵抗としては  $40\,\mathrm{k}\Omega$  ないし  $5.12\mathrm{M}\Omega$ の金属被膜抵抗(精度 0.05~0.1%, 温度係数 50 ppm/℃) を用いている. この回路の特性は, 直流的な変換誤差の 最大値 約0.07%,変換誤差0.1%以下となるまでのス

研 究 イッチ時間は  $C_1 \sim C_8 = 1$  のとき約  $0.9 \,\mu s$ .  $C_1 \sim C_8 = 0$ のとき約 0.6 μs である. ドリフトは測定時間 45 分間で ディジタル値1単位の約1/7程度である.

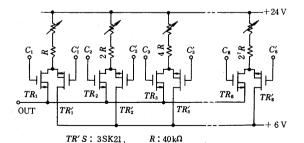

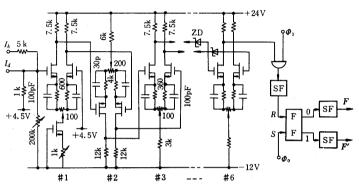

比較回路を図5に示す. この回路は MOS-FET 差動 増幅回路 6 段を用い、その出力を主クロック・パルス  $\Phi_1$ でサンプルしてフリップ・フロップをトリガし、帰還信 号 F を発生するものである. 差動増幅器の初段ないし3 段は相補形 FET による直結回路であり、4段ないし6 段は同一の回路で、ツエナー・ダイオードによるレベル シフトを行なっている. 増幅回路全体の電圧利得は 72dB 周波数帯域幅は0ないし 1.2 MHz である。ディジタル

TR'S in #2 : 3UT80 ZD'S:RD9A

other TR'S : 3SK21 SF : source follower

図 5 比較回路

値1単位の変化に相当する増幅回路初段入力電圧は最小  $3.05 \,\mathrm{mV^{40}}$  であり、フリップ・フロップのトリガ感度は 1 V 以下の入力パルス振幅の差を弁別しうるから、符号 判定のあいまいさはディジタル値1単位の 1/10 以下と なる. 増幅回路の応答時間の実測値は想定される最大入 力電圧変化 ±0.204V に対して最大約 1.0 µs である. ま た、ドリフトは各増幅段の FET に Idss の温度変化の 等しい対を選び、とくに初段の素子に注意を払った結果, ディジタル値1単位の約1/12以下となっている.

# 4. 総合特性

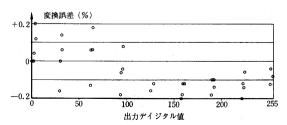

変換時間 20 μs のときの A-D 変換特性を, 直流入力 電圧を加えて測定した結果を図6に示す。同図では、量 子化誤差を除いた変換誤差をディジタル 出力 の変 化点

図 6 試作装置の A-D 変換特性 (変換時間 20 µs)

(いわゆる mid-riser) に対して求め、最大入力振幅 5V に対する相対値で示してある. 電圧保持回路における直 線性からのずれがその他の回路の特性によって相殺され ている一方,変換誤差の微細構造は局部復号回路の直流 特性かとはある程度異なっている.

表2は A-D 変換時間を変えた場合の特性の概要を示 したもので、変換時間を 40 µs 程度とすることによっ て、誤差をほぼ  $\pm 0.1\%$  の範囲となしうる。また、変 換時間が 20 μs を下回ると誤差が急激に大きくなる. こ の傾向は前記の各回路の所要動作時間の測定結果からも 説明できる.

表 2 試作装置の A-D 変換時間と変換精度

| 変換時間    | (# <b>s)</b> | 60    | 40    | 20    | 15    |

|---------|--------------|-------|-------|-------|-------|

| 変換誤差(%) | 上限           | +0.22 | +0.16 | +0.20 | +0.30 |

|         | 下限           | -0.16 | -0.06 | -0.20 | -0.34 |

# 5. 結

MOS 形 FET を用いて A-D 変換器の 集積回路化をはかることをねらいとして, 変換時間 20 µs, 2 進8 けたの逐次比較形 A-D 変換器を試作し、設計目標にほぼ近 い特性を得てその実現可能性を確かめると とができた.

アナログ回路の全 MOS-FET 化は可能 であって、とくに電圧保持回路、局部復号

回路では従来のバイポーラ・トランジスタを用いるもの に比べて、簡単で、しかも良好な特性のものが得られ た.

これらの回路の集積化を具体的に検討することが今後 の課題であるとともに、ディジタル回路にも、現在すで に開発されている MOS 集積回路を利用することが、信 号電圧レベルの整合の観点から望ましいと考えられる.

(1968年8月26日受理)

#### 文

- 1) 森脇, 高羽, 木下: 生産研究, 18, 8 (1966-8)

- 2) 森脇, 高羽, 西森: 昭和 41 年度電気通信学会全国大会, 658, (1966-11)

- 3) 森脇, 高羽, 西森: 生産研究, 20, 4 (1968-4)

- 4) 森脇, 高羽, 西森: 生産研究, 19, 10 (1967-10)

- 5) 森脇, 高羽, 西森: 電子通信学会創立50周年記念全国大会 908 (1967-10)