THE 弈 谏

UDC 621 382 323 012

# MOS 形 FET の静特性に対する バルクバイアスの影響

Effect of Bulk Bias Voltage on the Static Characteristics of MOSFET

# 安達芳夫・上村幸守

Yoshio ADACHI · Yukimori UEMURA

#### 1. 序

現在、集積同路分野を中心に広く使用され始めている MOS 形 FET (Metal-Oxide-Semiconductor Type Field Effect Transistor) の静特性の研究は、すでに Hofstein・ Sah など<sup>1)-7)</sup>、いろいろな人によってなされているが, これらの研究はすべてソースとバルクとを同電圧に保っ た場合のみを考察し, バルクバイアスの効果を全然考え ていない. われわれはバルクバイアス電圧をも考慮に入 れた理論式を導き出し、測定結果と比較したところ、非 常によい結果を得たのでここに報告する.

#### 2. 理

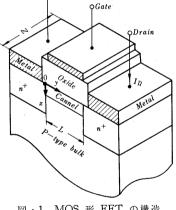

n-チャンネル MOS 形 FET の内部構造は図・1 のよ

Source

うであるが, この 場合のドレイン電 流  $I_D$  は次式で表 わされる<sup>6)</sup>.

$I_D = q \mu_n Z N_{(y)}$

$dV_{(y)}$ (1)

ここに μη: チ ャンネル中の 電子の移動度 (ここでは一

定と考える.)

$Z \colon \mathcal{F}$ 図・1 MOS 形 FET の構造 (各部分の大きさの比は正確でない)

$N_{(y)}, V_{(y)}: ソースからチャンネルにそって距離 y の$ 点での、単位表面積当たりの電子密度・ および電位

ところで $N_{(y)}$ はSi-SiO<sub>2</sub>界面での電気的中性条件から,  $qN_{(y)} = qN_{SS} + C_0[V_{G1} - \psi_{S(y)}] - Q_{b(y)}$

ここに Nss: 単位表面積当たりの有効表面準位密度 (一定と仮定する.)

Co: ゲート酸化膜の単位面積当たりの容量

$\phi_s$ : 表面準位( $=V_{(y)}+2\phi_F$ )

φ<sub>ε</sub>: エネルギギャップの中央から測った P形 バルク内部のフェルミ電位

ここで問題になるのが  $Q_{b}$  であるが, バルクバイアス 電圧  $V_{G2}$  を加えた場合の  $Q_{b}$  は近似的に次式で与えら れる。(ここで  $V_{G2}$  は、ソースに対してバルクに逆バイ アスを加えたとき、正の値を取ってある.)

$$Q_b = \sqrt{2\varepsilon_q N_A} (V_{(y)} + V_{G2} + 2\phi_F)^{1/2} \tag{3}$$

ここに  $N_A$ : バルク中のアクセプタ密度

ε: バルクの誘電率

(1) 式に(2)・(3) 式を代入して, 境界条件 V(y=L)  $=V_D$  のもとで積分すると,

$$\begin{split} I_D &= (Z\mu_n C_0 / L) [V_{G'} \cdot V_D - 1/2 \{ (V_D + 2\phi_F)^2 \\ &- (2\phi_F)^2 \} - 2/3 (2\varepsilon q N_A / C_0^2)^{1/2} \\ &+ \{ (V_D + V_{G2} + 2\phi_F)^{3/2} - (V_{G2} + 2\phi_F)^{3/2} \} ] \\ &\sim V_{G'} = V_{G1} + (qN_{ss}/C_0) \end{split} \tag{4}$$

したがって、 $V_D=0$  における出力コンダクタンス  $\frac{\partial ID}{\partial V_D} = g_{d0}$  は次式であらわせる.

$$g_{d0} = (Z\mu_n C_0/L) (V_{G'} - 2\phi_F - (2\varepsilon q N_A/C_0^2)^{1/2}$$

$$(V_{G2} + 2\phi_F)^{1/2})$$

(5)

また、飽和電圧  $V_{DS}$ ・飽和電流  $I_{DS}$  はピンチ・オフ条件  $N_{(y=L)}=0$  より、それぞれ (6)・(7) 式で与えられる.

$$V_{DS} = V_{G'} - 2\phi_F - (\varepsilon_q N_A / C_0^2) \left[ \left\{ 1 + (2C_0^2 / \varepsilon_q N_A) \right\} \right]$$

$$(V_{G'} + V_{G2}) \left\{ 1/2 - 1 \right\}$$

(6)

$$I_{DS} = (Z\mu_{\pi}C_0/6L) \left(V_{DS}'^2 + 2V_{G}'V_{DS}' - 4\left(V_{G}' - V_{DS}'\right)\right)$$

$$V_{G2} - 12\phi_F \left(V_{G}' - \phi_F\right) + 4(2\varepsilon_q N_A/C_0^2)^{1/2}$$

$$\left(V_{G2} + 2\phi_F\right)^{3/2}$$

$$(7)$$

$V_{DS}' = V_{DS} + 2\phi_F$ ててに

#### 3. 実験結果と検討

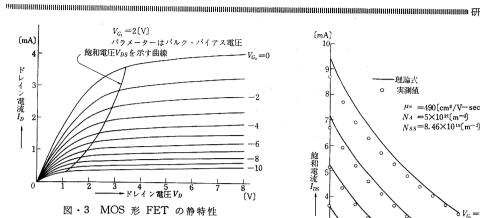

図・2 の結線で測定した MOS 形 FET の代表的な静特

次に素子のパ ラメーターのう ちの移動度μηや 表面準位密度 Nss を決定す るために、 $V_D=$

性を図・3に示す

図・2 MOS 形 FET 静特性測定回路 0 における出力 コンダクタンス gao を測定した. (図・4 に示す.)この  $V_{G1}-g_{d0}$  曲線は  $V_{G1}$  が 4V 以下ではほぼ直線と考えら れるから、この傾きから  $\mu_n=490 \text{ [cm}^2/V\text{-sec]}$  が求め られる、さらに、 $V_{G1}=V_{G2}=0$  の場合の実験値と理論値 を比較することによって、Nss=8.46×10-11(cm-2) が得られる. ここに示した試料のほか3個の被測定

MOSFET 07 れもほぼこれに 近い値が得られ た。

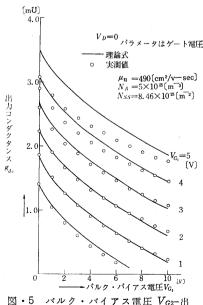

この二つの値 を(5)式の µn・ Nss に代入して  $V_{G1} \cdot V_{G2}$ の関数 として gao を計 算すると 図・5 の実線になる. これと実験値 (○印)とを比較 すると V<sub>G1</sub>≤4 で非常によく一 致することがわ

図・4 ゲート電圧  $V_{GI}$ -出力コン ダクタンス Qdo 特性

バルク・バイアス電圧 VG2-出 カコンダクタンス gao 特性

かるように 直線性が失 われてくる ために, μ,  $=490 \, \text{cm}^2$ V-sec)  $\geq \cup$ たことが不 適当となり 実験値と一 致しなくな る. 次に、飽 和領域にお ける理論値 と実験値を

かる. ただ

$\cup$ ,  $V_{G1}>4$

になると図

・4 でもわ

V<sub>G2</sub>-飽和電流特性

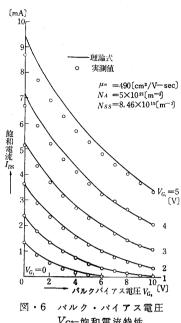

速 報 架 比較するために (6)式から飽和 電圧  $V_{DS}$  を求 め、それをもと にして飽和電流 IDS を式(7)か ら計算して図示 したのが図・6 (実線) である. 実験値(○印)は 図・3(および,記 載してない同様 なグラフ) から Vosに対する電 流値を読み出し たもので, この 場合も実験値と 理論値とがよく

一致している.

## 4. 結

MOS 形 FET のバルクとソース間にバイアス電圧を加 えることによって、半導体表面の空間電荷領域が広がる ために、バルクの電荷密度 $Q_{\mathbf{k}}$ は増加する $^{8)}$ . この効果を 考慮に入れた(3)式を用いると、ドレイン電流・出力 コンダクタンス・飽和電圧・飽和電流表示式として、そ れぞれ、(4)~(7) 式が得られるが、これらは以上に述 べたように実験とよく一致する. このように MOS 形 FET のバルクバイアス効果は従来の理論式の簡単な修 正によって表現できることがわかった.

謝辞 本研究に対して、試料を提供していただいた日 本電気 KK 半導体技術部の藤江明雄氏、および安達研究 室の方々に深く感謝する. (1966年10月3日受理)

### 参考文献

- C. T. Sah; "Characteristics of the Metal-Oxide-

- Semiconductors" IEEE. Trans. ED-11 (1964-7). Hofstein and Heiman; "The Silicon Insulated-Gate-Field-Effect Transistor" Proc. IEEE, 51 (1963.9).

- Root and Vadasz; "Design Calculation for MOS. FET" IEEE. Trans. ED-11 (1964-6).

- Hofstein and Warfield; "Carrier Mobility and Current Saturation in the MOS Transistor" IEEE. Trans. ED-12 (1965.3).

- 吉村; "MOSFET の飽和特性"昭和 41 年 電気学会連 合大会予稿, p. 1265.

- Reddi and Sah; "Source to Drain Resistance Beyond Pinch-off in MOS Transistors" IEEE. Trans. ED-12 (1965•3).

- 後川・藤田; "MOS トランジスタのピンチ・オフと飽 機構"トランジスタ研究会資料 (1966・2).

- A. Many, Y. Goldstein and N. B. Grover [Semiconductor Surface Noth-Holland Rublishing Company Amsterdam (1965).