UDC 681, 327, 66

# 磁性薄膜を用いた非破壊読出し高速記憶装置

渡 辺 勝・荒 木 宏

情報処理機器に使われる記憶裝置の高速化を達成するために,磁性薄膜素子の非破壊方式による高速記憶裝置を製作したので,その周辺回路ならびに動作結果を発表する.この結果は記憶裝置の非破壊方式による高速化の指針となるものである.

#### 1. はじめに

最近の情報処理機器の発展はまことにめざましく,特に高速化への要望が強まっている。その情報処理機器の主流をなす電子計算機や電子交換機の高速化の方法として,演算回路や記憶回路を高速化するには

- 1) 使用素子自体を高速化し、また回路方式を改良して高速化する手段.

- 2) 方式全体を改良して等価的に高速化する手段. の二つの方法が考えられる. ところが近年, 半導体素子の飛躍的な改善と回路技術の進歩により, 数値などの計算を行なう演算・制御装置の性能は著しく向上したため記憶回路が遅すぎる感があった.

そこで、記憶回路の高速化を達成するためには、再書 込みによる遅延時間を短縮する必要がある. この点から 見て非破壊方式は高速化へきわめて有望であり、また記 憶装置の論理構成を一部簡単化できる.

ここでは、円筒型磁性薄膜素子を用いて、非破壊読出し方式による読出し、書込みくり返し時間 200 nsec を目標にした高速記憶装置を試作し、実験したので、その周辺回路ならびに動作結果を記す.

# 2. 磁性薄膜記憶素子

磁性薄膜の高速記憶素子としては平板型磁性薄膜,円筒型磁性薄膜そして  $BICORE^{1}$  などがあり, これらはいずれも 1)高速スイッチング,2)高密度化,3)一括 製造( $Batch\ Fabrication$ )が可能であることが必要条件である.

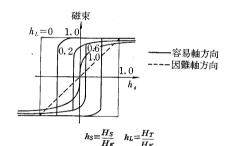

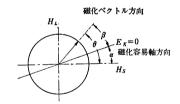

磁性薄膜は  $10\sim50$  Oe の磁界の影響下で Ni-Fe (80-20) 材を厚さ  $1000\sim2000$  Å の薄膜状に形成すると、その方向に磁化容易軸 (easy direction) ができ、その B-H 特性は図・1 の矩形ヒステリシス曲線で示される。またそれに垂直な方向は磁化困難軸 (hard direction) となり、その B-H 特性は図中破線で示した直線となる.  $^{20}$

以上の磁性薄膜の特性を利用して情報の記憶を行なう 場合,その薄膜素子の製造方法から分けると,

- 1) 真空蒸着による方法.

- 2) 電気メッキによる方法. がそのおもなものである.

- (1) その構造と動作原理

真空蒸着法は普通 0.2 mm 程度のガラス板上にパーマロイの薄膜を形成させるもので、これを平板型と呼び、電気メッキ法は円筒形の導線の上に薄膜を形成させる方法であり、これを円筒型と呼ぶ.

円筒型磁性薄膜は直径  $0.2\,\mathrm{mm}$  程度の導体線 (Cu) に電流を流しながらパーマロイ (80-20) を電気メッキすると、その円周方向に磁化容易軸ができ、またそれと垂直な線方向は磁化困難軸となる。それらの B-H 特性は図・1 に示したものである。

H<sub>K</sub>

H<sub>K</sub>

H<sub>S</sub>: 容易軸方向磁界, H<sub>T</sub>: 困難軸方向磁界

図・1

薄膜のヒステリシス特性

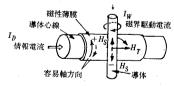

このメッキされた導線を情報線とし、同時に記憶情報の読取り線とする. 語駆動線はこのメッキ線と直交するように織り上げられている. そこで、原理的な構造は図・2 に示すように磁性薄膜線とその表面に沿うように直交した語駆動線で構成される.

HT: 磁化困難軸

Hs: 磁化容易軸

図・2

円筒型磁性薄膜記憶素子の原理

この磁性薄膜の単軸異方性は芯線導体の円周方向へ処理されているので、1ビットの記憶状態はその交点における磁性薄膜の磁化状態、すなわち磁化容易軸の方向を右巻きにするか左巻きにするかによって決まる.

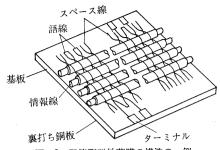

円筒型磁性薄膜は特にわが国で優秀な素子が開発されたもので、その原理、動作および製造方法についてはすでに詳細に報告されている<sup>3)</sup>が、図・3 にその構造の一例を示す (表紙写真を参照さたい).

図・3 円筒型磁性薄膜の構造の一例

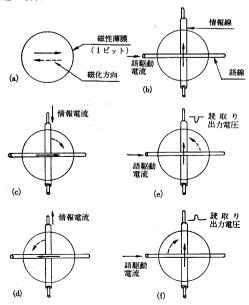

磁性薄膜の動作状態を模型的に順をおって説明すると 図・4(a)で円形に示したのは磁性薄膜素子で、矢印は 磁化方向を示す.素子の磁化方向は図に実線で示した方 向かまたは破線で示した方向のみ安定で、その他の方向 には外部磁界により無理に引き止められた時以外には向 かない. 外部磁界を取り除くと, 磁化方向は実線か破線 のいずれか近い向きに急速に戻る. 図・4(b) に示すよ うに、語線と情報線の交点を1ビットとし、語線に電流 を流すと、薄膜素子の磁化方向は図示のようになる. と こで語駆動電流を切ると、磁化方向は(a)図の実線か 破線のいずれになるか迷う. そこで(c) 図のように情 報線に電流を流しながら語駆動電流を切ると, 磁化方向 は必ず右向きに安定する.一方(d)図に示すように逆 向きの情報電流を流しながら語駆動電流を切ると磁化方 向は左向きに安定する. このように情報電流は素子の磁 化方向を決めることができるので書込み時に用いられ る.

次に図・4(e)に示すように右向きに安定している磁化方向に対し,語駆動電流を流すと,磁化方向が破線の如く回転して読取り線には負電圧が発生する.(f)は(e)の逆の場合で,読取り線には正電圧が発生する.よって

図・4 磁性薄膜の動作原理の模型による説明

読取り線に発生する出力電圧の極性により、語駆動電流 を流す前の磁化方向の状態を知ることができる.

# (2) 非破壊読出し方式

記憶内容を読取ると、その内容がいったん消されてしまう方式を DRO\*1 方式といい、読取るたびにもう一度情報を書き直す必要があるのに対し、NDRD\*2 方式では読取り後も記憶内容を保存することができる方式である。

DRO 記憶方式用として作られた磁性薄膜素子を ND-RO 記憶として動作させることは 可能 であるが、特に NDRO 方式に適した構造や磁気特性を 有する素子を使用すると、信頼性の高い動作が可能である.

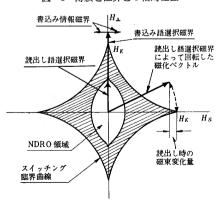

磁性薄膜を NDRO 記憶で使う原理は,直交駆動モードにおいて,語選択駆動パルスを異方性磁界  $H_K$  を超えない範囲で加えるものである.すなわち磁化容易軸方向と磁化ベクトルとのなす角を  $\beta$  とすれば単軸異方性によるエネルギは  $E_K=K_L\sin^2\beta$  である.ただし, $K_L$  は異方性定数である.いま,単一磁区の薄膜を図・5 に示すように相対位置におき,膜面に平行でお互に直交する磁界  $H_S$ ,  $H_L$  を加えると,磁化回転モデルによる薄膜のエネルギ  $E^{40}$  は

$E=K_{u}\cdot\sin^{2}(\theta-\alpha)-H_{s}N\cos\theta-H_{\perp}M\sin\theta$  (1) 磁化が飛躍的,非可逆的な回転を行なう臨界磁界の値は(1)式の変曲点を求めることにより, $\alpha=0$  ならば

$H_S^{2/3} + H_{\perp}^{2/3} = (2K_u/M)^{2/3} = H_K^{2/3}$

が得られる.  $H_K$  は異方性磁界と呼ばれるもので、磁化回転による反転現象を取り扱う場合に基準となる重要な量である. (2) 式を  $H_S$ - $H_1$  平面上に描くと図・6 の

図・5 薄膜と磁界との相対位置

図・6 スイッチング臨界曲線内の可逆磁化回転を 利用する NDRO 記憶

- \*1 DRO: Destructive Read out, 破壊読出し.

- \*2 NDRO: Nondestructive Read out, 非破壊読出し.

星茫形の曲線となる。すなわち図・4 において、読取りのさいの駆動電流を小さくして、駆動電流がなくなると必ず元の磁化方向へ戻り、磁化ベクトルは記憶情報を保存するように復帰するものである。

#### 3. NDRO による高速化

#### (1) サイクル時間という考え

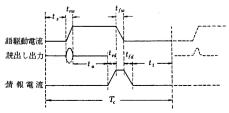

DRO では語選択駆動磁界は磁化回転によるスイッチングの臨界値である異方性磁界を超えて、磁化ベクトルを困難軸方向へ飽和にまで駆動することにより、いままで記憶されていた内容は壊れてしまうので、情報を一度読出すたびに必ず再書込みをしなければならない。このような形の記憶では、ひき続いて記憶情報を利用することができる速度は、読出し、書込みの1サイクルを終了するに要するサイクル時間できまる。

DRO 記憶のサイクル時間を図・7 で説明すると

- t,: 情報を分解して目的の番地を選択するに要する時間

- $t_a$ : 読出し出力パルスを増幅し、これを判別して再書 込み情報電流パルスが送られるまでの時間

- t<sub>1</sub>: 再書込み情報電流パルスの過渡状態における非常 に大きな雑音がおさまり、次の読出しに移れるまで の待ち時間

以上がサイクル時間の大部分であり、その他、選択された番地に加えられる語駆動電流パルスの立上り、立下り時間。この駆動パルスの前縁によって読出される出力パルスの基底幅はほぼ  $t_{rw}$  に等しい。これは磁性薄膜の固有スイッチング時間は 1 nsec 程度であって、一般にこれより数十倍大きい  $t_{rw}$  をもつ語駆動磁界の変化に、磁化ベクトルが遅れなくついていくことができるとみなすことができるからである。

情報パルスの立上り、立下り時間を  $t_{rd}$ 、 $t_{fd}$  とする. 情報パルスは少なくとも語駆動パルスの終了の前後にわたって存在しなければならない (図・4) から、全サイクル時間  $T_c$  は、図・7 より

# $T_c = t_s + t_{rw} + t_a + t_{rd} + t_{fw} + t_{fd} + t_t$

を必要とする。そこで  $T_c$  の短縮には、それぞれの遅延時間の合理的な配分と短縮が必要となる。しかし  $T_c$  のうち実際には  $t_s$ ,  $t_a$  と  $t_s$  がかなりな割合を占有していて、これが薄膜記憶のより一層の高速化をはばんでいる。

したがって、非破壊読出し記憶によって再書込みの必

図・7 DRO 記憶のサイクル時間

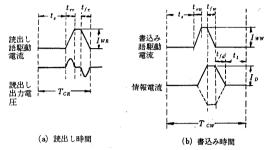

要性が除かれると、サイクル時間の短縮が可能になる. この場合再書込みというサイクルを繰り返す必要がないので、サイクル時間という考えは存在せず、書込み時間と読出し時間とに分れることになる.

図・8 に NDRO 記憶の読出し時間と書込み時間のダイヤグラムを示す. なおこの場合語駆動電流パルスの定常部分は必ずしも必要でない.

図・8 NDRO 記憶の読出しおよび書込み時間

## (2) NDRO 記憶の利点

NDRO 記憶により、情報を再書込みする必要性がなくなれば、高速化できることはいうまでもなく、情報をより速く処理できることであるが、NDRO 記憶による高速性の増大は一度記憶した情報の利用度が高いほど、すなわち読出し回数が多いほど著しい、したがってDRO記憶のサイクル時間に比べて NDRO 記憶の読出し時間が短いほど高速性の増大率が大きい、頻繁に使用される制御情報やデータ、サブルーチンなどには有効である。

もう一つの利点は、記憶レジスタに読出した情報を、再書込みのために情報パルス駆動回路へ帰す必要がないので、通常この帰還回路に挿入されている Exclusive-OR 回路などを省くことができて、経済化できる。さらに書込み時に選択されない番地やビットに加わる妨害雑音の回数が少なくなるので、クリーピングによる記憶情報破壊に対して安定性が増すことである。

#### 4. 機構の概要

円筒型磁性薄膜記憶素子を電子計算機やディジタル装置の内部記憶装置 (internal memory) として使用することを考え、記憶装置をより一層高速化する方法の一つとして NDRO 方式を採用し、以下に記すような内容で試作を行なった。

記憶方式: 語選択, 非破壊読出し方式

読出し繰り返し時間: 200 nsec 記憶容量: 64 語**\*16** ビット

使用メモリ・プレーン: MODEL MX-W 32 D 64-

2 GN

規準駆動電流

書込み時: 語駆動電流 (*I<sub>ww</sub>*) 400 mA 情報電流 (*I<sub>D</sub>*) 40 mA

読出し時: 語駆動電流 (*Iwr*) 200 mA 情報電流 不要

なお、この装置に使用した基本回についてはすでに報告されている $^{5}$ .

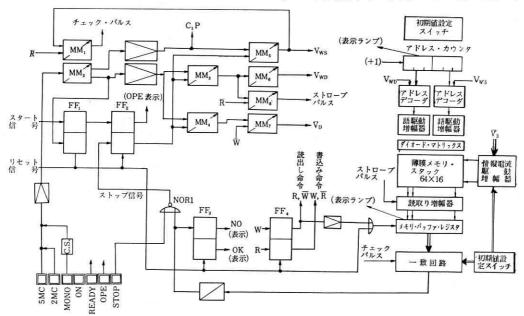

# (1) 記憶装置の論理設計

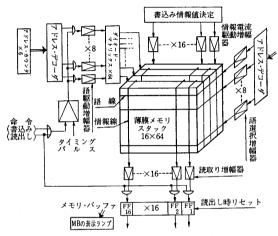

記憶装置は円筒型磁性薄膜メモリ・プレーンを64語\*16 ビットで構成したスタックとして、その駆動周辺回路を開発し、それを制御駆動することによって情報の書込みおよび読出しを行なう。それら周辺回路の構成のブロック線図を図・9 に示す。

図・9 NDRO 記憶装置のブロック線図

アドレス・カウンタで指定された番地はアドレス・デコーダ回路によって8回路の語駆動増幅器と8回路の語 選択増幅器に分配される。各語選択増幅器には8回路の語駆動増幅器が接続されているので、その出力はダイオード・マトリックスによって、64 語中の1語が選ばれる、すなわち語選択方式である。

書込みを行なうとき,選ばれた1語にはタイミング・パルス回路から図・8(b)の時間関係にある  $V_W$ ,  $V_D$ パルスが導入され, $V_W$  はアドレス・デコーダ回路によって指定された語駆動増幅器で十分な電流パルス  $I_{WW}$ となって語線に送られる.一方,メモリ・プレーンの各情報線 (digit line) にはそれぞれ情報電流駆動増幅器があり,これに情報に応じたオーダ・パルス  $V_D$  が導入され, $I_D$ (正または負)となって1語の各ビットへ並列に送られ, $I_{WW}$ と  $I_D$  が一致した点に,前記の原理によって情報("1"または"0")が記憶される.

一方内容の読出しは語駆動パルス  $I_{WR}$  で駆動させる. この場合は"読出し命令"によりメモリ・バッファ・レジスタが読出し準備され、同時にストローブ・パルスが 発生され、読取り増幅器が動作して、情報に応じた信号 によりメモリ・バッファ・レジスタを駆動する.

読出された内容はチェック回路において、書込んだ情報と読出された内容とが等しいか否かを判断される。

#### (2) 記憶装置に必要なテスト

磁性薄膜素子を使用して、ある語数の記憶装置として 使用するとき、当然のことではあるが記憶装置に要求されることは、与えられた情報を確実に書込み、これを読出した場合にそれが失なわれていないことである。しかし実際には以上の動作を確認する上において、記憶動作の最も困難な場合、あるいは誤動作を生じやすい状態が予想される。そこで当記憶装置では予想される困難な状態を人為的に作り出し、これを繰り返しテストして確かめる必要がある。

記憶情報を減少または破壊する電気的擾乱のおもな原因としては,外部磁界その他の特殊なものを除けば,一般には

- 1) 前に書込まれた情報の影響

- 2) 隣接記憶点の読み,書きの影響

- 3) 情報線に沿う遠隔記憶点の読み,書きの影響などがある.1) は磁化状態の履歴および膜厚に起因する現象で,たとえば書込み時の電流が小さ過ぎるような場合に生ずる.2) は通常 interference と呼ばれるもので,情報線上の隣接記憶点間で互に逆の情報の読み,書きを行なうと語線電流による鎖交磁束および磁壁移動などによって電気的干渉を生ずる現象である.3) は disturbance と呼ばれるもので,別の番地に書込むための情報電流によって生ずる磁気的 creeping に関係するものである.

これらのチェックを行なうために、次のような操作が 行なえるように装置を設計した.

- ① 記憶装置の任意の番地が指定できるように、手動操作が行なえるようにした.

- ② 指定された番地に指定したパターン(1語)を書込む、この際隣接ビットには逆パターンの書込みができること.

- ③ 一度書込みが終了すると、次は読出しを実行する。 その繰り返し時間は 200 nsec としてテストを行なう。

- ④ 読出された内容と書込んだ内容を比較して、誤り のある場合はこれを表示し、動作はストップする.

以上の動作テストが行なえるようにする.

#### 5. 記憶装置の構成

最近の電子計算機のほとんどに使用されている強磁性コア記憶装置や磁気ドラム記憶装置と同様に、磁性薄膜記憶装置は、いわゆる情報を記憶する部分(ここではメモリ・スタックと呼ぶ)とそれを駆動する周辺回路から構成される。しかし高速記憶装置では、その周辺回路がしばしば問題になる。まず雑音の問題がある。信号レベルに比してはるかに大きい雑音はしばしば読取り増幅器を不能にし、繰り返し時間の短縮をはばんでいる。したがって雑音の発生を防ぐための技術、発生した雑音を除

去するための技術が必要である.

当記憶装置はメモリ・スタックを中心に、その配線が 最短距離になるように配置され、標準ラックに組み込ま れている。そして装置の動作はすべて操作盤上に表示ラ ンプで示される。なお、この種の NDRO 方式は書込み 語駆動電流と読出し語駆動電流の二種類を必要とするた め駆動回路が多少複雑になる。

## (1) メモリ・スタック

ある語数の記憶装置として使用できる形に組み立てた ものをメモリ・スタックと呼ぶ. 磁性薄膜の NDRO 方 式では,磁化ベクトルを飽和にまで駆動させないため読 取り電圧レベルが小さい. したがってスタック内部で誘 起する雑音,接続線間において外部から受ける擾乱が信 号伝播にとって大きな妨害となり,信号対雑音比を低下 させる原因となる.

#### 情報線・読取り線の接続<sup>6)</sup>

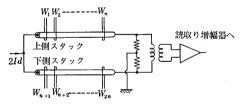

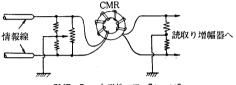

情報線と語線との1交点を1ビットとして用いることは可能であり $^{7}$ 、その方がビット密度を高くし得る。しかし信号は非平衡伝播となり。S/N比が悪くなる。そこで、図・11に示すように、情報線2本を用いてブリッジ形に構成する。すなわち2記憶点を1ビットとして用いるので、ビット密度は半減するが、読取り出力は normal 信号となって倍加し、common mode 形の雑音は相殺される。この原理を応用した実際の結線図を図・12に示す。

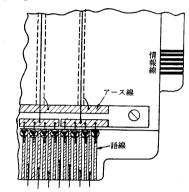

## 2) スタックの構造

2枚のメモリ・プレーンを銅板をはさんで背中合せに

図・10 1記憶点1ビットの結線の一例

図・11 ブリッジ形結線

図・12 情報線・読取り線の結線図

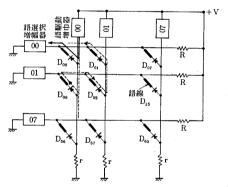

取り付け、この銅板を外枠に固定させると同時にアース 板として使用する. 語線には語選択用のダイオードがプレーンの両側に直接取り付けてあり、その模様を図・13 に示す. このダイオードは図・14 に示すようにマトリックスに構成されていて、指定した1番地が選択できるようになっている. また情報線は図・12 に示す方式で結線し、図・12 中にある部品はすべてプレーン上に固定されている.

図・13 語選択用ダイオードの取付け

図・14 ダイオード・マトリックス

#### 3) 雑音に対する考慮

記憶素子からの読出し出力電圧レベルが微小であるので, 雑音の発生を防ぐための技術, 発生した雑音を除去するための技術が必要であることは前に述べた.

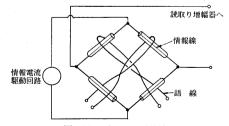

それぞれの語線と情報線の交点に存在する静電容量を媒介にして、語駆動電流の過渡状態において、語線から各情報線へ並列に誘起する雑音は common mode である。それを図・15 に示す。そこで、図・12 に用いた CMR $^{899}$  (Common Mode Rejector) は common mode 入力信号に対して高いインピーダンスを呈し、normal mode 信号に対してはインピーダンスはほとんど0となるから、1 ビットの交さ点に誘起した雑音は CMR $_{1}$  (CMR $_{2}$ )、CMR $_{3}$  においていずれも common mode であり、したがって雑音の伝播は阻止される。一方、駆動電流により読出された出力信号は normal mode 信号であり、CMR は低インピーダンスを呈し、信号伝播には何ら影響をおよばさない。

図・15 語選択駆動時の雑音の発生

CMR: 7 mmø 磁性コア 7 turn×2図・16 コモン・モード・チョーク

次に図・14 に示すダイオード・マトリックスの構成において、たとえば今、 $WD_{00}$  と  $WS_{00}$  が動作して  $D_{00}$  が選択された時、語電流は  $WD_{00}$  から  $D_{00}$  を通って  $WS_{00}$  へ流れる。この際同図中に破線で示したような回り込み電流を防ぐ、よって逆抵抗の高いダイオードがよく、一方選択番地には語電流が流れるからそれを妨たげないために順方向抵抗の小さいダイオードが望まれる。

また選択用ダイオードを語線を境いにして語駆動増幅 器側に接続するか、語選択増幅器側に接続するかにおい

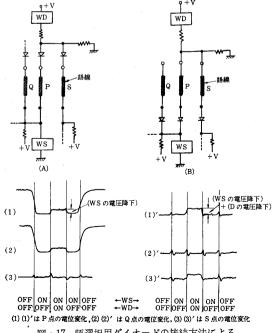

図・17 語選択用ダイオードの接続方法による 語線の電位変化

て機能的に違いはない. しかしその接続個所により,語線から情報線へ誘起する雑音には差があることが認められた. これら二通りの接続方法について,雑音を考慮して検討すると, $図 \cdot 17$ (A),(B) に示す如くである.

図・17(A) において

- ① WS の OFF↔ON 時に P, Q 点において電位変 化が大きく, その際語線から情報線へ雑音が誘起するが 記憶素子からの読出し信号にはさほど影響しない.

- ② WD の OFF↔ON 時には読出し駆動電流 Iwr が流れた時の WS による電圧降下だけ電位変化を生ずる。 次に図・17 (B) において

- ③ P, Q, S 各点とも WS の OFF→ON による電位 変化は小さく、情報線への影響はほとんどない。

- ④ WD の OFF $\leftrightarrow$ ON によって、読出し駆動電流  $I_{WR}$  が流れると、P 点の電位変化は WS の電圧降下と 選択ダイオードの電圧降下の和だけ生ずる、この電位変化は②のものより大きく、したがって情報線へ発生する 雑音も大きいことが認められた・

以上検討した結果から、語選択用ダイオードはWD側に接続するようにした.

また図・14 において非選択番地のダイオードを常にカットオフの状態に保つために抵抗 R を通じて正電圧が加えられ、抵抗 r は選択番地が動作中に貯えた電荷を、動作後速やかに放電させる役目をする.

# (2) 周辺装置

#### 1) アドレス・カウンタ

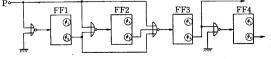

メモリの番地を指定するカウンタで、入力を受けるごとに"1"づつ count-up してゆく、方式は並列 Up-Counter と直列 Up-Counter を組み合せ、FF と NOR 回路を用いた論理構成である。

たとえば、N 番目の FF の入力ゲートの一般式は

$$n = (\overline{N}_1 + \overline{N}_2 + \dots + \overline{N}_{n-1} + P)$$

$$= N_1 \cdot N_2 \cdot \dots \cdot N_{n-1} \cdot \overline{P}$$

$$\overline{n} = (\overline{N}_1 + \overline{N}_2 + \dots + \overline{N}_{n-1} + P)$$

$$= \overline{N}_1 \cdot \overline{N}_2 \cdot \dots \cdot \overline{N}_{n-1} \cdot \overline{P}$$

ただし $\bar{n}$  は N 番目の FF の入力,  $N_1$ ,  $N_2$ , … $N_{n-1}$  はカウンタの各段のセット出力,  $\bar{N}_1$ ,  $\bar{N}_2$ , … $\bar{N}_{n-1}$  はそのリセット出力である. その回路を図・18 に, 実負荷における動作波形を図・19 に示す. 実際には FF 6回路を使用した6段のカウンタである.

図・18 アドレス・カウンタの構成

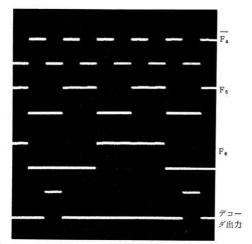

#### 2) アドレス・デコーダ回路

NOR 回路を使用して, 64 語を 8 \* 8 に分割してマトリックス回路の入力となるものである. NOR 回路に

(a) アドレス・カウンタおよびデコーダの動作波形 2 μs/div 5 V/div (SS-5502 シンクロスコープ使用)

(b) 使用パッケージ (GF-504 4回路/パッケージ) 図・19

よる AND 論理は De-Morgan の定理により  $f=\overline{FF_1+FF_2+FF_3}=FF_1 \cdot FF_2 \cdot FF_3$

で計算される. その動作波形を写真 (a) に示す.

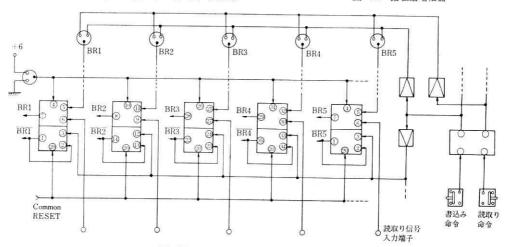

#### 3) メモリ・バッファ・レジスタ

メモリからの読取り出力を受け、それを1時蓄積し、 読取り情報を外部の回路へ渡したり、また外部から情報 を受けたりする、その回路構成の1部を図・20に示す.

次に、初期の書込み情報値とバッファ・レジスタに読出された内容とが同じものであるか否かをチェックする 一致回路がある.

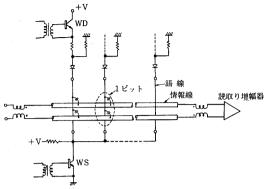

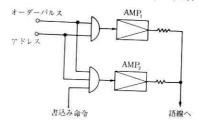

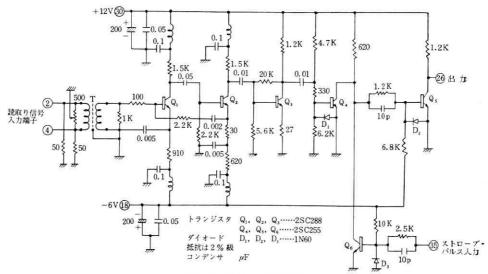

# 5) 語駆動増幅器と語選択増幅器

語駆動増幅器 (WD) は語線を駆動する電流パルスを供給する増幅器で、8台の WD と 8台の WS (語選択増幅器)から成り、それぞれ1台の WD に8台の WS が接続される.

NDRO 記憶では2種類の駆動電流  $(I_{WW}, I_{WR})$  を必要とするため,以下に記す方法でそれを実現された.

すなわち. 図・21 (b) に示す回路を2 回路並列に接続させ、図・21 (a) のようにする. 一方の回路の入力ゲートには書込み命令を入れておく. したがって書込み時は  $AMP_1$  と  $AMP_2$  が並列に動作し、読出し時は  $AMP_1$  のみを動作させることにより2 種類の駆動電流を

(a): WD の書込み、読出し切換方式

(b): WD の基本回路 図・21 語駆動増幅器

図・20 メモリ・バッファ・レジスタ回路

#### 作りだした.

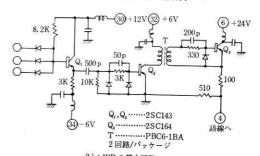

また語選択増幅器も同じような方法で作り、その回路を図・22 に示す。

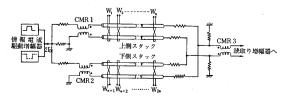

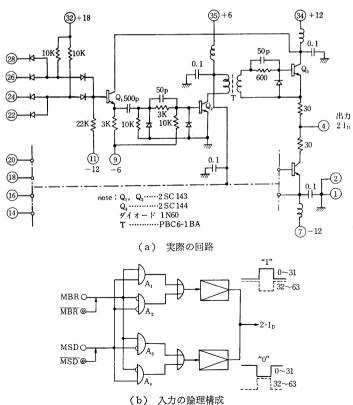

# 6) 情報駆動增幅器

情報線に情報電流  $I_D$  を流す回路である。情報電流による妨害を除くため、メモリ・スタックを upper stack と lower stack に 2 分割して、ブリッジ構成としているため、 $I_D$  は  $2I_D$  を必要とすること、また 2 組のおのおののスタックに書込む情報の"1"、"0"を逆にして扱わなければならないので、その入力側で情報の"1"と"0"を切換えるように論理構成した。

そこで、実際にはメモリの番地を前半(0~31)と後半

(32~63) に分け"1"と"0"を制御する.

A1=MBR • MSD,  $A2=\overline{MBR} • \overline{MSD}$

$A3=MBR \cdot \overline{MSD}$ ,  $A4=\overline{MBR} \cdot MSD$

ここでA1, A2,  $\cdots$  A4 は各ゲートの出力, MBR はメモリ・バッファ・レジスタの出力, MSD はアドレス・カウンタの最上位桁の情報である。実際の回路と入力論理構成を図・23 の (a),(b) に示す。上記の論理式より  $0\sim$ 31 番地までは A1 と A4 が動作し、バッファ・レジスタの内容によって"1"または"0"のパルス  $(2I_D)$  が出力に現われる。すなわち"1"の場合は A1 が動作して図中実線の電流が流れる。

"0" の場合は A4 が動作して負電流が流れる. 後半の 32~63 番地までは A2 と A3 が動作して, 前述の条件と逆の電流パルスが出力端に現われる.

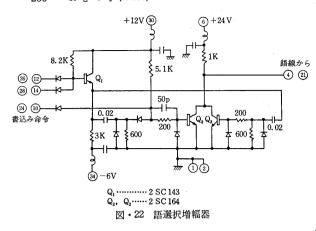

# 7) 読取り増幅器 (SA)<sup>10)</sup>

メモリからの読出し出力を十分なロジック・レベルまで増幅し、バッファ・レジスタに送る回路である. 読出し出力が微小であるため、浮遊容量による雑音や外部擾乱を避けるため、入力端までの信号経路にはシールド線を用い、またこの回路は CMR 比を向上させるために入力側に平衡トランスを使用し、可変抵抗を調節することによりインピーダンスの整合を取るようにした. 平衡トランスは1次と2次間をシールドして平衡度の向上につとめてある. この増幅器の利得は約 70 dB である.

図・23 情報駆動増幅器

図・24 読取り増幅器

# 6. 記憶装置の動作および結果

周辺装置の個々の回路および動作は前章で説明したので、ここでは装置全体の構成ならびにその動作を理解するために図・26 に装置のブロック線図を示す。記憶装

図・25 操作盤

置の動作状態はすべて操作盤(図・25)上にランプ表示 される.

## (1) 動作

まず, 記憶装置を駆動させる前に

- 1) メモリの何番地に書込みを行なうかをアドレス・カウンタにセットする.

- 2) 「読み,書き」命令を書込みにセットする.

- 3) 書込む情報パターンをバッファ・レジスタにパネル盤上よりスイッチによりセットする.

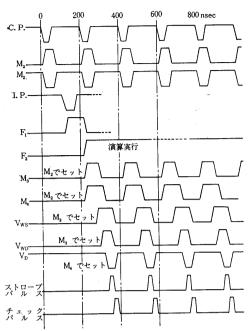

以上の条件を各レジスタにセットし、次に「OPE」ボタンを押すと  $FF_2$  がセットされ、 装置は動作状態となり、図・27 に示すタイムチャートに従って $MM_5$ ,  $MM_5$  と  $MM_7$  が動作する。したがって  $V_{WS}$ ,  $V_{WD}$ ,  $\overline{V}_D$  の各

図・26 記憶装置のブロック線図

図・27 タイミング発生回路のタイム・チャート

パルスが発生し、これは周辺回路のそれぞれの入力へ導かれ、そこで書込みに必要な電流パルスに増幅されて、 メモリの指定された番地に送られて情報の書込み動作が 実行される.

次に、先きに記憶した内容の読出し周期を実行する場合には

- 1) 動作をいったんストップさせる

- 2) 「読み、書き」命令を読出しに切換える、この時 バッファ・レジスタは自動的にリセットされる

- 3) 再び「START」ボタンを押す

と、読取り増幅器を動作させるストローブ・パルスと読出された内容をチェックするためのチェック・パルスが $MM_8$ と  $MM_1$  から発生される、読出しに必要な語駆動電流が指定番地に送りこまれ、装置は読出し動作が実行される

メモリから読出された内容は SA で増幅され、ストローブドされた出力は、読取り内容に従ってバッファ・レジスタをセットする. その状態はランプ表示される.

次に一致回路において、メモリへ書込んだ情報パターンと読出された内容とが同じものであるか否かをチェックする。内容が正しく読出されているならば、読出し周期をくり返す。一方、もし内容が誤って読出された場合には、 $FF_3$ をセットして $\Gamma NO$ 」表示され、さらに  $NOR_1$ を通過して  $FF_2$  をリセットして装置の動作はただちにストップする。以上の動作は自動的に行なわれる。

# (2) 波形の測定

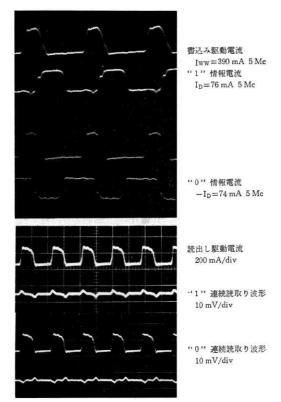

記憶装置を前節に記した順序にしたがって動作させる に当り、まず ready して装置全体を clear する. そして

- ① 記憶装置の各番地ごとにパターン"1010…10"を 書込み,直後これを読出す.次に,この補数パターン "0101…01"を書込み,読出す.

- ② ある番地にパターン"1010…10"を書込み、続いて両隣接番地には補数パターン"0101…01"を連続して書込む、その後、先きの番地へもどして読出し、チェックする。

以上のテスト操作を任意の番地について,数回くり返 し行なう.

1) 読み, 書きサイクル時間 0.5 μs による記憶装置のテスト

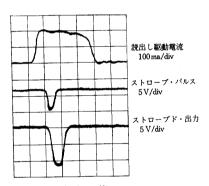

読み,書きサイクル時間  $0.5 \mu s$  のときの IwR と出力 波形とその時間関係を図・28 に示す.同図 (a) は当記 憶装置による NDRO 方式の動作波形であり,(b) は DRO 方式 $^{11}$ の動作波形である. 両者を比較参照された

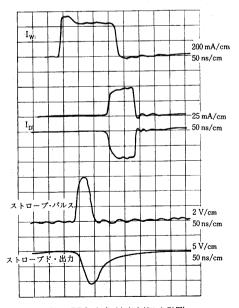

# 2) 周期 0.2 µs における動作

(a): NDRO 方式 50 n sec/div (SS-5502 シンクロスコープ使用)

(b): DRO 方式(参考文献より引用)図・28 読み,書きサイクル 500 ns における波形と DRO 方式との比較

図・29 周期 200 nsec における NDRO 記憶装置の 動作波形 (SS-5502 シンクロスコープ使用)

周期  $0.2 \mu s$  のときの書込み動作 および連続読出し動作波形を図・29 に示す。 これにより NDRO 方式による連続読出しが可能であり、speed-up できることが実証される。

また interference や disturbance テストに対しても安定であった.

## 7. 検 討

円筒型磁性薄膜素子を用いた非破壊読出し記憶装置の 試作は、初期の目標であった書込み、読出し周期 200 nsec を達成し得た. なお、この装置は現在の状態で 150 nsec までは speed up できる見込みである.

今回の記憶装置は小容量 (1024 bits) であったので, とりわけ高度な技術は要求されなかったが,今後,大容 量化,より一層の高速化を達成するためには,当然予測 される問題点がある.

- 1) 微小信号に対する雑音対策の問題

- 2) メモリ・プレーン内で生じる信号遅延の問題

- 3) 周辺回路の改良

などである. 1) については今回の報告に記したようにかなり注意した点である. 2) については、たとえば読取り線、駆動線を伝わる信号の伝播時間が無視できなくなると、それぞれの伝送線を特性 impedance で終端する. とかあるいはスタックをいくつかに分割して信号の遅延を軽減させるなどの配慮が必要である. 3) ではいく通りかの方法が考えられた. 特に語駆動増幅器では定電流. 回路を用いて、それを制御駆動させるなどである. 以上の点に留意し、解決しなければならない問題である.

当装置の非破壊方式は異方性磁界内で駆動させる方法 であったが、別な方法として磁性薄膜パルス応答の角度 ヒステリシス<sup>12)</sup>を利用する非破壊方式も考えられる.

おわりに本記憶装置の試作に当り、終始有益なご助言をいただいた渡部弘之氏(日本 I.B.M.)、試作に協力されたアイ電子測器 K.K. へお礼申し上げる.

(1966年6月22日受理)

# 参考文献

- R. J. Petschauer: A Nondestructive readout film memory, PROC.-FALL JOINT COMPUTER CONF., p. 411 (1964).

- 2) E.E. Bittmann: Intermag Conf. 9-1 (1963).

- 大島信太郎他: 注目される ワイヤ・メモリマトリック スの開発,電子科学, Sept. (1963).

- 4) 神山,菅田:磁性体薄膜,薄膜工学ハンドブック,Ⅲ61~,5月(1964)

- 渡辺, 荒木: 東大生産技研電気談話会報告, VOL. 16.

No. 8, Jun, (1966)

- "An Improved Union of Digit-Select Lines and Sense Lines in Word Select Ferrite-Core Memory Systems", Proc. of the IEEE, p. 432, April (1964).

- 7), 11) 渡部,松下:円筒形織成薄膜素子を用いた高速記 憶装置,生産研究,17,8 (1965).

- C. L. Ruthroff: Some Broad-Band Transformers, Proc. of the IRE, p. 1337, August (1959).

- 9), 12) 石立 喬: 最近の高速記憶素子と周辺回路技術, エレクトロニクス, 4月 (1965).

- C. F. Chong etc: High-Speed Read Amp. for Thim Films, ELECTRONIC DESIGN, August 3 (1964)