# Soft-Error Tolerant Cache Architectures

(耐ソフト・エラーのキャッシュ・アーキテクチャ)

Supervisor: Professor Shuichi Sakai

# Luong Dinh Hung

Department of Information Science and Technology, The University of Tokyo

December 2006

# Abstract

The problem of soft errors caused by radiation events are expected to get worse with technology scaling. This thesis focuses on mitigation of soft errors to improve the reliability of memory caches. We survey existing mitigation techniques and discuss their issues. We then propose 1) a technique that can mitigate soft errors in caches with lower costs than the widely-used Error Correcting Code (ECC), 2) a technique to mitigate soft errors in Content Addressable Memories, and 3) a cost-effective cache architecture achieving both variation-induced defect and soft-error tolerance.

ECC is widely used to detect and correct soft errors in memory caches. Maintaining ECC on a per-word basis, which is preferred for caches with word-based access, is expensive. Chapter 3 proposes **Zigzag-HVP**, a cost-effective technique to detect and correct soft errors for such caches. Zigzag-HVP utilizes horizontal-vertical parity (HVP). Basic HVP can detect and correct a single bit error (SBE), but not a multi-bit error (MBE). By dividing the data array into multiple HVP domains and interleaving different domains, a spatial MBE can be converted to multiple SBEs, each of which can be detected and corrected by the corresponding parity domain. Vertical parity update and error recovery in Zigzag-HVP can be performed efficiently by modifications to the cache data paths, write-buffer, and Built-In Self Test. Evaluation results indicate that the area and power overheads of Zigzag-HVP caches are lower than those of ECC-based ones.

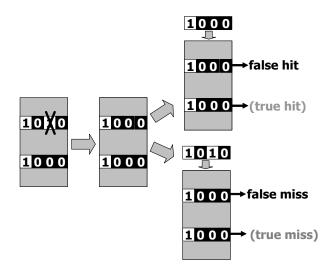

Chapter 4 proposes **STCAM**, a soft-error tolerant Content-Addressable Memory (CAM). Soft-error mitigation in a CAM is difficult due to the unavailability of data outside the cell array in a CAM access. Since CAMs are used in several components of a processor, making those CAMs being resilient against soft errors is required to attain high processor's reliability. STCAM can successfully detect and correct false hits and false misses caused by soft errors in a CAM. This is achieved through subdividing a CAM and providing backup checking for cases the input tag is partially matched in the CAM. An original encoding scheme is proposed to reduce the frequency of backup checking. Modifications to support STCAM do not increase access latency. Performance degradation incurred by backup checking is very low.

Chapter 5 presents **SEVA**, a soft-error- and variation-aware cache architecture. As memory devices are scaled down, the number of variation-induced defective cells increases rapidly. Combination of ECC, particularly Single-Error Correction Double-Error Detection (SECDED), with a redundancy technique can effectively tolerate a high number of defects. While SECDED can repair a defective cell in a hardware block, the block becomes vulnerable to soft errors. SEVA exploits SECDED to tolerate variation-induced defects while preserving high resilience against soft errors. Information about the defectiveness and data dirtiness is maintained for each SECDED block. SEVA allows only the clean data to be stored in the defective blocks. An error occurring in a defective block can be detected and the correct data can be obtained from the lower level of the memory hierarchy. SEVA improves both yield and reliability with low overheads.

Having memory caches to be tolerable from soft errors is essential for attaining high processor's reliability. Incurring low area and power overheads, **Zigzag-HVP** allows support for soft-error tolerance to be more affordable and therefore pervasive. **STCAM** increases in the coverage of soft error protection in a processor. Finally, **SEVA** shows that soft-error tolerance for reliability and defect tolerance for yield can be achievable with reasonable costs, paving the way for successful SRAM designs in future process technology.

# Acknowledgment

First of all, I would like to express my gratitude to my advisor, Professor Shuichi Sakai, for his continuous guidance, support, and encourage given to me throughout the six years I has spent in his laboratory. I fully appreciate his earnest effort to provide the students with the best-equipped research environments and the highest opportunity to pursuit their own research.

I address thanks to Associate Professor Masahiro Goshima for his invaluable technical comments and suggestions on my research. He also gave me helpful advice on how to improve presentation skill.

I am also grateful for the referee members of this thesis: Professor Masaru Kitsuregawa, Professor Tohru Asami, Professor Hitoshi Aida, and Associate Professor Kenjiro Taura for their invaluable comments and suggestions to the thesis.

I'm also deeply gratitude to Professor Hidehiko Tanaka, now at Institute of Information Security, for supervising me during my master course. I admire his great leadership at the laboratory previously as well as at the CREST project that my research has been involved.

I thank the rest of laboratory members for all the support and invaluable discussions, both technical and non-technical ones. I thank Dr. Hidetsugu Irie for leading and taking care of the research project. I am especially indebted to those who spent a lot of their time for maintaining the network and computers in the laboratory, particularly Hiroyuki Kurita, Kazuto Shimizu, Ryota Shioya, Hironori Ichibayashi, and Kenichi Watanabe. Special thanks go to Mrs. Harumi Yagihara, Ms. Miwa Tsukimura, and Ms. Anzu Uchida for their dedications to make administration affairs run smoothly. I also thank former members, especially Dr. Niko Demus Barli and Ms. Chitaka Iwama, for assisting me a lot when I started my research at the laboratory.

I also express my thanks to Kansai Paint Scholarship and Tokyo Marine Kagami Memorial Foundation. Without their generous financial support, I would have not been able to fully dedicate myself to the research.

Luong Dinh Hung The University of Tokyo, Japan December 2006

# Contents

| 1        | Intr |                                                           | 15 |

|----------|------|-----------------------------------------------------------|----|

|          | 1.1  | Background                                                | 15 |

|          |      |                                                           | 15 |

|          |      | 1.1.2 Soft-Error Tolerance in Memory Caches               | 20 |

|          | 1.2  | Research Contributions                                    | 22 |

|          | 1.3  | Thesis Organization                                       | 23 |

| <b>2</b> | Exi  | sting Work on Soft-Error Tolerance in Memory Caches       | 25 |

|          | 2.1  | Process- and Technology-Level Hardening Techniques        | 25 |

|          | 2.2  | Circuit- and System-Level Hardening Techniques            | 27 |

|          | 2.3  | Architectural Level Hardening Techniques                  | 29 |

|          | 2.4  | Room for Improvements                                     | 31 |

|          |      | 2.4.1 Overhead Reduction                                  | 31 |

|          |      | 2.4.2 Soft Error Mitigation in Content-Addressable Memory | 32 |

|          |      | 2.4.3 Pursuit of Soft-Error- and Defect Tolerance         | 32 |

| 3        | Zig  | zag-HVP: Soft-Error Mitigation in Caches with Word-       |    |

|          | -    |                                                           | 33 |

|          | 3.1  | Introduction                                              | 33 |

|          | 3.2  |                                                           | 35 |

|          | 3.3  |                                                           | 36 |

|          |      | *                                                         | 36 |

|          |      |                                                           | 37 |

|          |      |                                                           | 38 |

|          | 3.4  | Zigzag-HVP                                                | 39 |

|          |      | 0 0                                                       | 39 |

|          |      |                                                           | 42 |

|          |      |                                                           | 43 |

### CONTENTS

|   | 25           |                                                               | 4.4        |

|---|--------------|---------------------------------------------------------------|------------|

|   | 3.5          | Applications of Zigzag-HVP                                    | 44         |

|   |              | 3.5.1 L1 Write-back Caches                                    | 44         |

|   | 9 C          | 3.5.2 L2 Caches with Write-through L1 Caches                  | 44         |

|   | 3.6          | Evaluation                                                    | 49         |

|   |              | 3.6.1 Evaluation Methodology                                  | 49         |

|   |              | 3.6.2 Physical Configurations of L2 caches                    | 51         |

|   |              | 3.6.3 Area Overhead                                           | 51<br>50   |

|   |              | 3.6.4 Power Overhead                                          | 52         |

|   | 0.7          | 3.6.5 Unrecoverable Soft Error Rate                           | 53         |

|   | 3.7          | Summary                                                       | 55         |

| 4 | STO          | CAM: Soft-Error Tolerant Content-Addressable Memory           | 57         |

|   | 4.1          | Random Access Memory and Content Addressable Memory.          | 57         |

|   | 4.2          | CAM-RAM Caches                                                | 59         |

|   | 4.3          | False Hits and False Misses                                   | 61         |

|   | 4.4          | STCAM Architecture                                            | 63         |

|   |              | 4.4.1 Mitigation of False Hits                                | 63         |

|   |              | 4.4.2 Mitigation of False Misses                              | 63         |

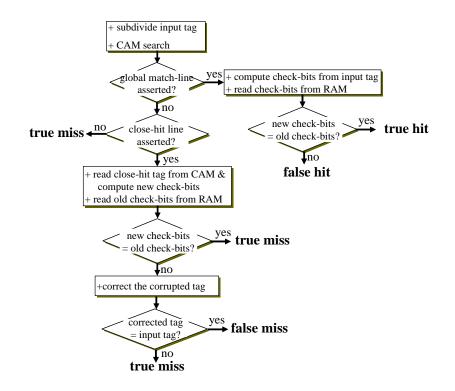

|   |              | 4.4.3 Cache Access Algorithm                                  | 65         |

|   | 4.5          | Close Hit Rate and Tag Encoding Scheme                        | 67         |

|   |              | 4.5.1 Close Hit Rate                                          | 67         |

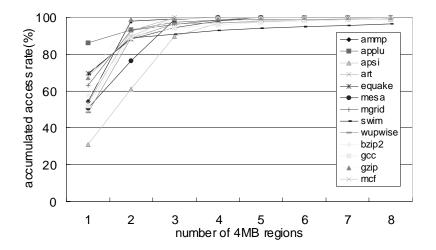

|   |              | 4.5.2 Distribution of Access Addresses                        | 68         |

|   |              | 4.5.3 Tag Encoding Scheme                                     | 69         |

|   | 4.6          | Overheads of STCAM                                            | 71         |

|   |              | 4.6.1 Cache Access Latency                                    | 71         |

|   |              | 4.6.2 Processor Performance                                   | 73         |

|   | 4.7          | Summary                                                       | 74         |

| 5 | SE7          | A: Soft-Error- and Variation-Aware Cache Architecture         | 75         |

| Э | 5.1          | Introduction                                                  | 7 <b>5</b> |

|   | $5.1 \\ 5.2$ | Variation-induced Defects and Defect Tolerance                | 73<br>77   |

|   | 0.2          | 5.2.1 Variation-induced Defects                               | 77         |

|   |              | 5.2.2 Defect Tolerance Techniques                             | 79         |

|   | 5.3          |                                                               | 79<br>80   |

|   | $5.3 \\ 5.4$ | Limitation of Existing Techniques                             | 80<br>81   |

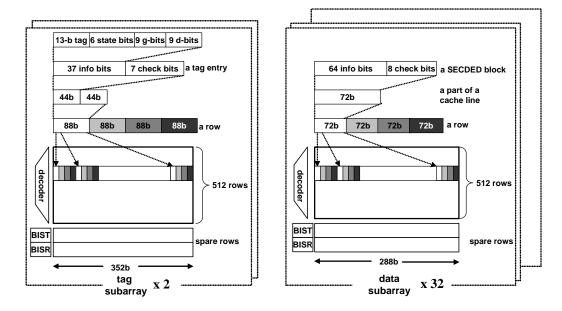

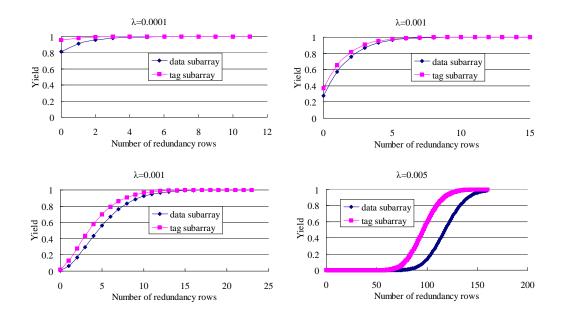

|   | 0.4          | 5.4.1 Cache Structure and Block Classification                | 81         |

|   |              | 5.4.2 Inclusion Properties in Multi-level Cache Hierarchies . | 83         |

|   |              | 5.4.3 Assurance Update                                        | 84         |

|   |              | J.4.J Assurance Update                                        | 04         |

8

|    |       | 5.4.4   | Assurance Update Reduction        | . 84  |

|----|-------|---------|-----------------------------------|-------|

|    |       | 5.4.5   | Example SEVA Cache                | . 89  |

|    | 5.5   | Defect  | t and Yield Analysis              | . 90  |

|    |       | 5.5.1   | Results                           |       |

|    |       | 5.5.2   | Discussion                        | . 93  |

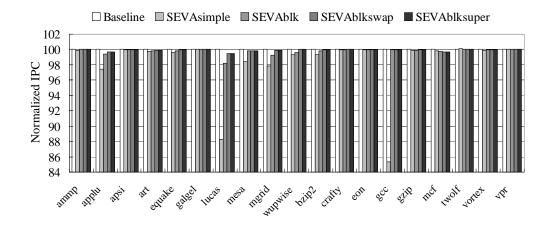

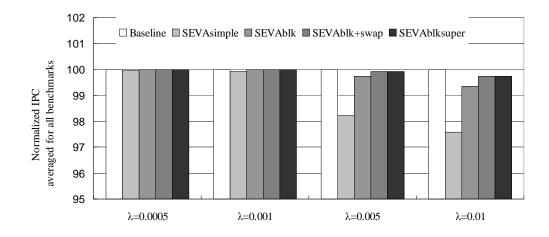

|    | 5.6   | Perfor  | rmance and Reliability Evaluation | . 93  |

|    |       | 5.6.1   | Evaluation Methodology            | . 93  |

|    |       | 5.6.2   | Evaluation Results                | . 95  |

|    | 5.7   | Summ    | hary                              | . 99  |

| 6  | Cor   | ıclusio | ns                                | 101   |

|    | 6.1   | Concl   | usions                            | . 101 |

|    | 6.2   | Sugge   | stions for Future Work            | . 103 |

| Ρı | ıblic | ations  |                                   | 105   |

### 9

CONTENTS

# List of Figures

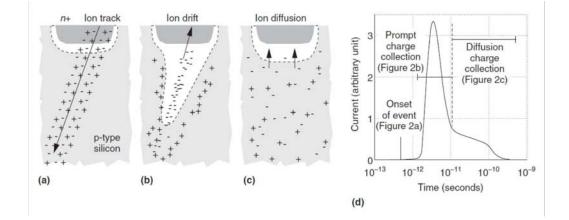

| 1.1  | Charge generation and collection in a reverse-biased junction. | 16 |

|------|----------------------------------------------------------------|----|

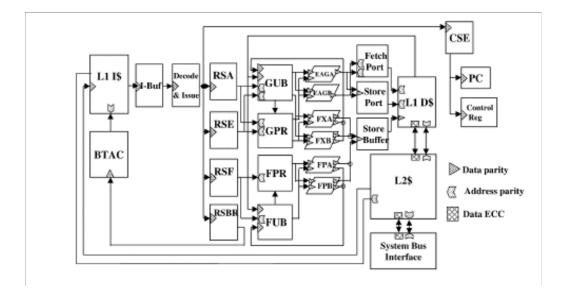

| 1.2  | Error check diagram in SPARC64 processor                       | 21 |

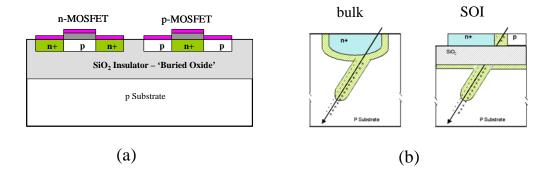

| 2.1  | Structure and ionized charge collection of SOI                 | 26 |

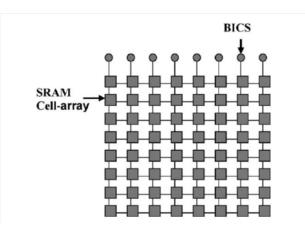

| 2.2  | Memory protection using BICS                                   | 29 |

| 2.3  | Principle of logic design hardened storage cell                | 30 |

| 3.1  | Horizontal-vertical parity                                     | 37 |

| 3.2  | Examples of multi-bit errors                                   | 38 |

| 3.3  | Interleaving schemes to deal with MBEs                         | 41 |

| 3.4  | Distribution of partially- and fully-modified ECC codewords    | 46 |

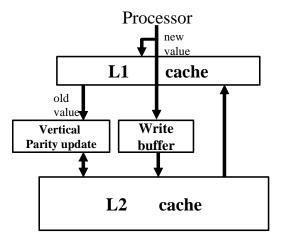

| 3.5  | Modified data path of L2 cache with write-through L1 cache     | 47 |

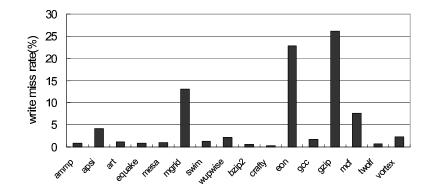

| 3.6  | Write miss rate of L1 data cache.                              | 48 |

| 3.7  | An entry of write buffer.                                      | 48 |

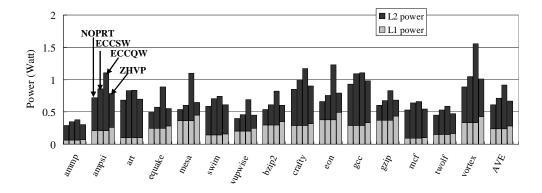

| 3.8  | Breakdown of power consumption                                 | 53 |

| 3.9  | Illustration of unrecoverable error                            | 54 |

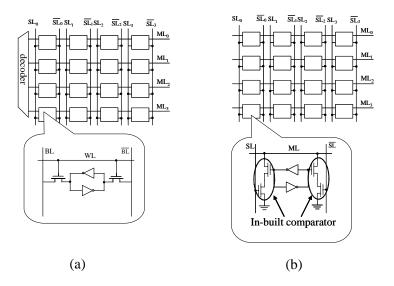

| 4.1  | Structures of RAM and CAM                                      | 58 |

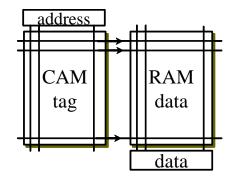

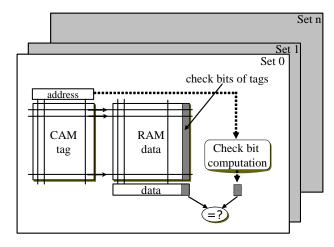

| 4.2  | A CAM-RAM structure.                                           | 59 |

| 4.3  | Structure of highly associative CAM-RAM cache.                 | 60 |

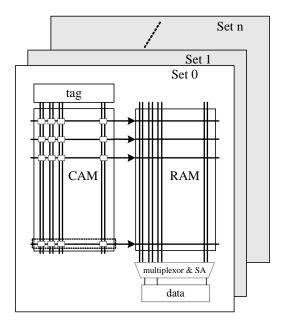

| 4.4  | Examples of false hits and false misses                        | 62 |

| 4.5  | Mechanism for mitigating false hits.                           | 64 |

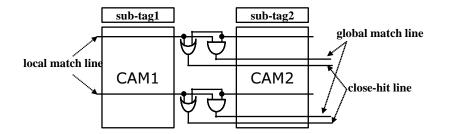

| 4.6  | Modified CAM tag for mitigating false misses                   | 65 |

| 4.7  | Access algorithm of a STCAM cache                              | 66 |

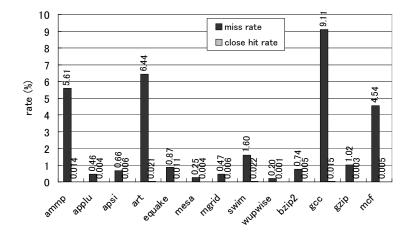

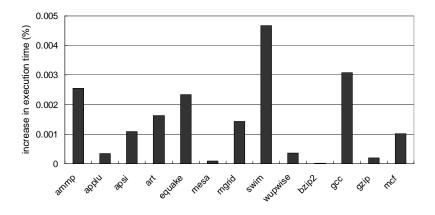

| 4.8  | Cache miss rate and close hit rate.                            | 68 |

| 4.9  | Distribution of the target addresses of accesses.              | 69 |

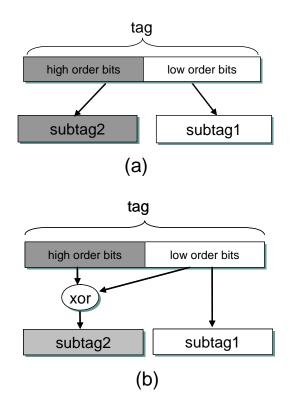

| 4.10 | Tag encoding schemes.                                          | 70 |

| 4.11 | Miss and close-hit rates with proposed tag encoding            | 71 |

| 4.12 | Performance of processor using STCAM.                          | 73 |

### LIST OF FIGURES

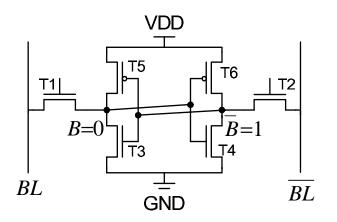

| 5.1  | Schematic of a SRAM cell                                        | 78 |

|------|-----------------------------------------------------------------|----|

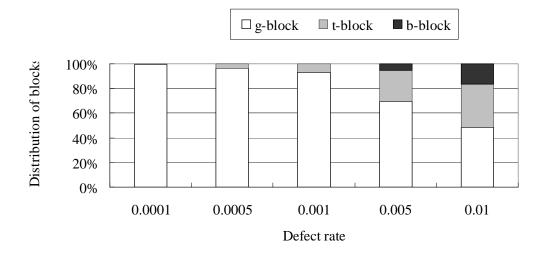

| 5.2  | Distribution of blocks at different defect rates                | 82 |

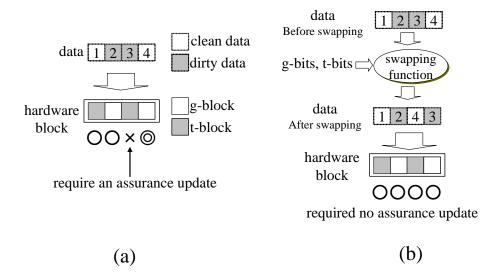

| 5.3  | Example of data swapping                                        | 86 |

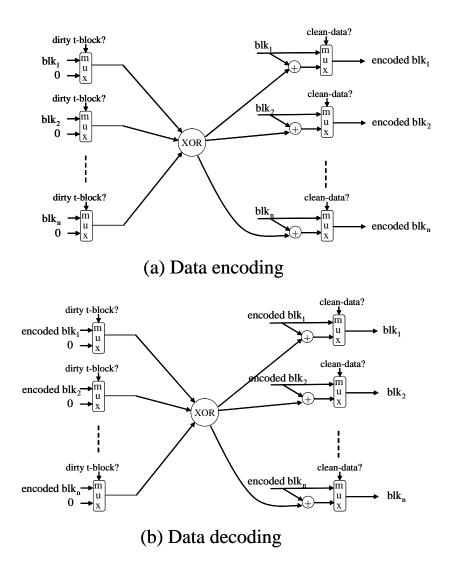

| 5.4  | Encoding and decoding in data superimposition                   | 87 |

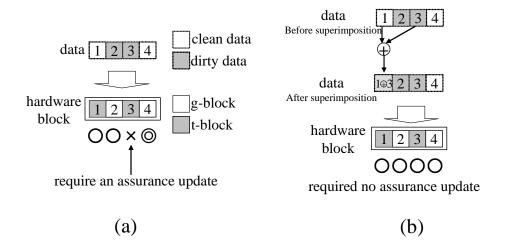

| 5.5  | Example of data superimposition                                 | 88 |

| 5.6  | Example structure of a SEVA cache                               | 89 |

| 5.7  | Yields of tag and data subarrays.                               | 92 |

| 5.8  | Normalized performance when defect rate is equal to $0.005.$ .  | 96 |

| 5.9  | Normalized performance as defect rate is varied                 | 96 |

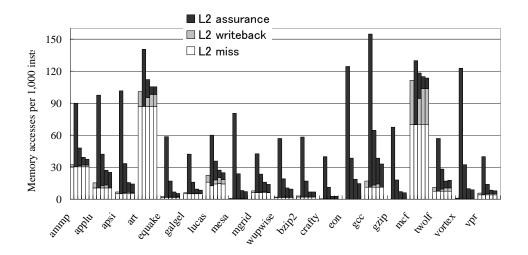

| 5.10 | Breakdown of accesses from L2 cache to memory per 1,000         |    |

|      | instructions when $\lambda$ is equal to 0.005                   | 97 |

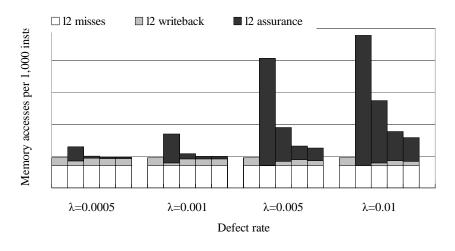

| 5.11 | Breakdown of accesses from L2 cache to memory per 1,000         |    |

|      | instructions when $\lambda$ is varied                           | 98 |

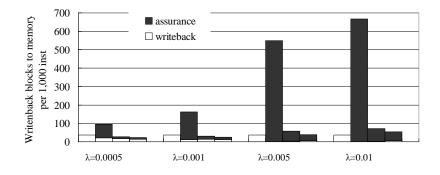

| 5.12 | Number of written-back blocks to memory per 1,000 instructions. | 98 |

12

# List of Tables

| 3.1 | Number of SECDED check bits for various data unit size             | 34 |

|-----|--------------------------------------------------------------------|----|

| 3.2 | Parameters of Simulated Architecture.                              | 50 |

| 3.3 | Area overheads of protection schemes                               | 52 |

| 3.4 | Unrecoverable Soft Error Rate                                      | 55 |

| 5.1 | Variation of $V_{th}$ over process generations                     | 77 |

| 5.2 | Probability of failure cell versus $\sigma V_{th}$ in 45nm process | 79 |

| 5.3 | Number of check bits required for different information-bit        |    |

|     | lengths                                                            | 80 |

| 5.4 | Yields and overheads of subarrays and cache                        | 92 |

| 5.5 | Parameters of Simulated Architecture                               | 94 |

| 5.6 | Uncorrectable error rate of L2 caches                              | 99 |

LIST OF TABLES

14

# Chapter 1 Introduction

Computer systems with very high dependability are required as the society becomes increasingly dependent on the computation and communication capability provided by them. *Dependable computing* has been emerging as an important and active research field, covering aspects including reliability, availability, safety, and security of computer systems [1].

Radiation-induced soft errors are expected to have serious impacts on the reliability of semiconductor devices, particularly as scaling trend continues. This thesis focuses on mitigation of soft errors to improve the reliability of memory caches and, as a result, to enhance the dependability of processors. In this chapter, we explain the problem of soft errors, and briefly review existing mitigation techniques in memory caches. We then describe the research contributions. At the end of the chapter, we describe the organization of this thesis.

## 1.1 Background

#### 1.1.1 Soft Error Problem

Soft errors, also called Single Event Upsets (SEUs), in a semiconductor device refer to intermittent or transient failures caused by radiation events [2]. Soft errors cause loss of of data but do not bring about permanent damage to the device. The problem of soft errors are early recognized in 1950s [3]. Since then, extensive work has been done to investigate the mechanisms of soft errors, their impacts on the reliability of semiconductor devices, as well as to

Figure 1.1: Charge generation and collection in a reverse-biased junction. Formation of a cylindrical track of electron-hole pairs in (a), funnel shape extending high field depletion region deeper into substrate in (b), diffusion beginning to dominate collection process in (c), and the resultant current pulse caused by the passage of a high-energy ion in (d) [4].

develop techniques to mitigate them.

#### Soft Error Mechanisms

The reverse-biased P/N junction node (i.e., drain node of a transistor) is the most charge-sensitive part of circuits, particularly if the junction is floating or weakly driven and consequently most susceptible to soft errors. As ionizing radiation passes through a node, electrons and holes are generated along the track of ionizing particles, as shown in Figure 1.1-a. Depending on the type and amount of energy of the incident particles, the generated charges are produced by either *direct ionization* by the incident particle, or *indirect ionization* of secondary particle produced by nuclear reaction between the incident particle and the target material [5]. When the resultant ionization track traverses or comes close to the depletion region, the electric field rapidly collects carriers, creating a current/voltage glitch at that node. Charge collection is greatly enhanced by *funneling effect* [4]. Funneling is caused by distortion of the potential into a funnel shape extending deeply into the substrate, as shown in Figure 1.1-b. Excess charges produced by a radiation track inside this funneling region are collected very rapidly. This collection phase completes within tens of picoseconds. Then another phase follows in which diffusion begins to dominate the process. Figure 1.1-c shows the resultant current pulse.

#### **Radiation Sources**

There are several sources of high-energy particles that can cause soft errors [2]. Soft errors may be caused by alpha particles emitted from radioactive decay of contaminants in the metal, passivation layers, and package materials. Soft errors may also be caused by cosmic rays (mainly neutrons and protons) that are the by-products of interactions between high energy (tens of MeV/nucleus) galactic cosmic ray with oxygen and nitrogen in the atmosphere. The third source of soft errors comes from alpha particles released from interaction of low-energy cosmic neutrons with the isotope boron-10 (<sup>10</sup>B) present in borophosphosilicate glass (BPSG), which is a common semiconductor dopant and dielectric component in IC materials [6]. In advanced processes that use highly purified chip and packaging materials with extremely low levels of uranium and thorium impurities, and where a dielectric material free of <sup>10</sup>B has replaced BPSG layers, high-energy cosmic neutrons are responsible for the majority of soft errors observed [4].

Soft errors can cause bit-upsets in dynamic and static memory elements (e.g., DRAMs, SRAMs, latches, flip-flops). Memory caches have been the main targets of soft error mitigation. The problem of soft errors in logic circuits has received attention in recent years.

#### Soft Error Rate and Impacts of Scaling

The amount of charges collected by a gate after a radiation event depends on many factors including the substrate structure, device doping and biasing of circuit nodes, the substrate structure, device doping, the type of ion, where the ion occurs within the devices, and the device's state [5]. The collection slop  $Q_s$  is a measure of the charge collection efficiency of a device measured in fC and it is heavily dependent on the process technology [7]. Previous work has showed that  $Q_s$  will become smaller as technology scales down [8].

The collection efficiency of a device, however, is not the only factor that determines if a soft error occurs. The sensitivity of the device to the excess charges must also be considered.  $Q_{crit}$  is the critical amount of charges that

has to be deposited to a circuit node for a soft error to occur.  $Q_{crit}$  depends on many factors including the nodal capacitance, operating voltage, circuit topology [4]. Circuit simulators can be used to calculate the critical charge of a circuit [9]. The scaling trend towards lower supply voltage and smaller device dimensions has decreased  $Q_{crit}$  [4].

For simple isolated junction (e.g., DRAM cells), a soft error will be induced when a radiation event occurs close enough to a sensitive node such that the collected charge represented by  $Q_s$  is greater than  $Q_{crit}$ . Conversely, if the event produces a  $Q_s$  less than  $Q_{crit}$ , the circuit will survive the event and no soft error will occur. In SRAM or other logic circuit having active feedback, there is an additional component of  $Q_{crit}$  related to the magnitude of the compensating current and the switching time of the device. Increasing the strength of the feedback circuit and the time to switch the device will in effect increase  $Q_{crit}$ .

A widely used empirical model relating the soft error rate (SER) to  $Q_s$  and  $Q_{crit}$  is indicated by Equation 1.1 [8]. F in the equation is the particle flux which is the number of particles per unit area per second (particles/ $(cm^2s)$ ). A is the area of the circuit that is sensitive to particle strikes  $(cm^2)$ .

$$SER \propto F \times A \times e^{-\frac{Q_{crit}}{Q_S}}$$

(1.1)

DRAM's per-bit SER was high when manufacturers used planar capacitor cells that store charges in two-dimensional, large-area junctions. These cells were very efficient at collecting radiation-induced charges. DRAM manufacturer since then adopted three-dimensional capacitor designs that significantly increase  $Q_{crit}$  while greatly reducing junction collection efficiency by eliminating the large storage junctions. DRAM's per-bit SER has been shrinking about 4x to 5x per generation. The increased memory density (bits per system) almost as fast as the SER reduction that technology scaling provided. DRAM's system SER has remained essentially unchanged over generations [4].

A SRAM is more susceptible to soft errors than a DRAM. Designers have deliberately minimized the SRAM junction area to reduce capacitance, leakage, and cell area while aggressively scaling down SRAM's operating voltage to minimize power consumption. Which each successive SRAM generation, a reduction in operating voltage and node capacitance has cancelled out the reduction in cell collection efficiency caused by shrinking cell depletion volume. Initially, SRAM's per-bit SER was increasing with each successive generation.

#### 1.1. BACKGROUND

More recently, as feature sizes have size have shrunk into the deep-submicron range, SRAM's per-bit SER has reached saturation and might even be decreasing. This saturation is primarily due to the saturation in voltage scaling, reduction in junction collection efficiency, and increased charge sharing caused by short-channel effects with neighboring nodes. SRAM's per-chip SER is expected to increase at most linearly with decreasing feature size [8].

A transient pulse caused by ionizing event can propagate through logic gates and finally be latched by a sequential element, resulting in an incorrect output. Whether an erroneous pulse in a logic circuit resulting in an incorrect output depends on three masking effects: logical masking, electrical masking and latch window masking. Logical masking happens when one of inputs of a gate is in controlling state (e.g., 0 for a NAND gate) so that then transient pulse at another input is blocked. Electrical masking happens when pulse is attenuated by subsequent logic gates because of the electrical property of the logic gate. Latch window masking means the arrival transient pulse is outside of the latching window for the sequential elements. The impacts of these masking effects on SER of logic circuit have been studied [10] [7] [11]. SER of logic circuits is expected to increase rapidly and contribute a significant fraction of system SER [7].

The commonly used unit of measure for the soft error rate (SER) and other hard-reliability mechanisms is the FIT (failure in time). A FIT is equivalent to one failure in  $10^9$  device hours. Soft errors have become a huge concern in advanced computer chips because, uncorrected, they produce a failure rate exceeding that of all other reliability mechanisms combined. For example, a typical failure rate of a hard-reliability mechanism (e.g., gateoxide breakdown, metal electro-migration) is about 5 to 150 FITs. However, without mitigation, SER can easily exceed 50,000 FITs per chip [4].

#### Necessity of Soft Error Tolerance

Traditionally, soft errors were regarded as a major concern only for space and avionics electronics. Since the flux of radiation particles increases with high altitude, electronics working in high altitude environments are exposed to a much higher SER than those on ground. Specifically, the sea-level flux is several hundred times smaller than the fluxes seen at aircraft altitudes [12]. The necessity of employing measures against soft errors in space and avionics electronics also stems from the fact that these applications are extremely mission-critical such that even a small SER is unacceptable. Until recently, the problem of soft errors was largely ignored in commodity electronics. Commodity electronics are highly cost-sensitive so that any measure against soft errors that imposes a relatively high cost was commonly considered unacceptable by users. Moreover, SER was low enough so that the costs and design efforts spent to implement the measures were unjustified. However, the situation has been increasingly changing. The problem of soft errors in commodity electronics cannot be negligible any more. Device scaling enables large scale integration. System-level SER therefore grows rapidly. Customers become more aware of, and demand stringent tolerance requirements for soft-error problem. These factors make soft error mitigation indispensable not only for space and avionics electronics, but also for commodity electronics.

Soft-error induced failures in commodity electronics have been reported. SUN servers crashed due to lack of soft error tolerance in the designs of UltraSparc II processor and its internal cache [13]. Cisco's 12000 line-card router reset after SEU failures, requiring two or three minutes to recover [14]. FPGA-based Q Cluster and System X, which were the second and third fastest supercomputers on the November 2003 Top 500 Supercomputer Sites list, experienced fatal failures caused by soft errors [15]. The Q cluster, for example, experienced 26.1 CPU failures a week [15]. Such failures had unavoidably led to customer's dissatisfaction, damaged reputation of companies. Advanced processor designs have put a great emphasis on soft error tolerance. Figure 1.2 shows the diagram of SPARC64 processor [16] [17]. Memory caches, data paths, and 83% of latches in the processor are protected from soft errors, either by parity or Error Correcting Code (ECC).

#### 1.1.2 Soft-Error Tolerance in Memory Caches

Memory speeds are increasing at a much slower rate than processor speeds [18]. So even though processors are becoming faster, the overall performance declines because of the slower memory. The processor will spend increasing portion of execution time waiting for data to be brought from memory. To bridge the gap between memory speed and processor speed, an advanced processor usually devotes a majority of hardware resources for its memory caches. For instance, Itanimum 2 processor devotes 86% of the transistors for its L3 cache [19]. Moreover, memory caches are usually SRAMs that are highly vulnerable to SEUs. Having memory caches to be resilient against soft errors is indispensable for attaining high processor's reliability.

Figure 1.2: Error check diagram in SPARC64 processor. Caches and data paths are protected by either parity or ECC.

Soft errors in memory caches can be mitigated at multiple levels. At process and technology level, by using purified materials or employing shielding, soft errors caused by alpha particles can be mostly eliminated [20] [21]. Charge collection efficiency can be reduced in processes with extra doping layers [22] [23] [24] [25], or silicon-on-insulator (SOI) [26]. While techniques at this level can provide an error-hardened substrate for all circuits built on it, combinations of them with techniques at higher levels are usually required for achieving a low SER, particularly as neutron-induced soft errors are increasingly become a major concern.

Coding techniques (e.g., parity and ECC) are very effective in protecting memory caches, thanks to the high regularity of memory arrays. The overheads of coding techniques are reasonable and acceptable in most cases. Single-Error Correction Double-Error Detection Hamming code (SECDED) is the most widely used ECC in practice. As we point out later, SECDED can incur a high area overhead for some cases. Multi-bit errors can be tolerated by combining SECDED with *interleaving* [27] [28], or *scrubbing* [29] [30].

Circuitry of individual memory cells can be modified to make them more robust against soft errors [31] [32] [33]. However, since a hardened cell typically requires a significant larger area than a typical cell, these techniques are not suitable for cost-sensitive applications.

By exploiting architectural properties such as dirtiness or access frequency of data, error protection can be selectively performed on those data having high impacts on the cache's SER [34] [35] [36]. While such an approach requires less area overhead than the approach treating all data equally, its effectiveness is dependent on the amount of locality of data access in execution programs.

## **1.2** Research Contributions

This research focuses on mitigating soft errors in memory caches. We make the following contributions.

- We proposes **Zigzag-HVP**, a cost-effective technique to detect and correct soft errors for such caches. While ECC is widely used for SEU mitigation in VLSI caches, we show that ECC is expensive for being implemented in caches with word-based access. Zigzag-HVP utilizes the concept of horizontal-vertical parity (HVP). HVP maintains parity of a data array in two-dimensional directions: horizontal and vertical. While requiring fewer check bits than ECC, a basic HVP scheme can detect and correct only a single bit error (SBE), but not a multi-bit error (MBE). By dividing the data array into multiple HVP domains and interleaving the bits of different domains, a spatial MBE can be converted to multiple SBEs, each of which can be detected and corrected by the corresponding parity domain. Vertical parity update and error recovery in Zigzag-HVP can be performed efficiently by modifications to the cache data paths, write-buffer, and Built-In Self Test. Evaluation results indicate that the area and power overheads of Zigzag-HVP caches are lower than those of ECC-based ones.

- We proposes **STCAM**, a soft-error tolerant Content-Addressable Memory (CAM) architecture. Due to differences in circuit structure and access nature, mitigation of soft errors in a CAM is more difficult than in a RAM. STCAM can detect and correct false hits and false misses caused by soft errors in a CAM. The technique involves subdividing a CAM and providing backup checking for cases the input is partially matched in a CAM search. An original encoding scheme is proposed to

reduce the frequency of backup checking. Our evaluation results show that modifications to support STCAM do not increase access latency. Performance degradation incurred for false miss checking is very low.

• We propose SEVA, a cost-effective soft-error- and variation-aware cache architecture. As devices are scaled down, the number of variation-induced defective memory cells increases rapidly. The proposed SEVA combines SECDED with a redundancy technique to effectively tolerate such a high number of defects. While SECDED can repair a defective cell in a block, the block becomes vulnerable to soft errors. To remedy the problem, SEVA allows only clean data to be stored in the defective (but repairable) blocks. Such constraint is enforced through a mechanism called *assurance update*. An error occurring in a defective block can be detected and the correct data can be obtained from the lower level of the memory hierarchy. We also propose techniques to reduce the frequency of assurance update.

## 1.3 Thesis Organization

The remaining of this thesis is organized as follows. Chapter 2 provides a detail survey on existing soft-error mitigation techniques in memory caches. Chapter 3 presents **Zigzag-HVP**. Chapter 4 presents **STCAM**. Chapter 5 presents **SEVA**. Finally, Chapter 6 makes conclusion.

# Chapter 2

# Existing Work on Soft-Error Tolerance in Memory Caches

This chapter surveys existing techniques for mitigating soft errors in memory caches. The problem of soft errors can be addressed at multiple levels. The techniques presented here are classified based on at which level they are implemented. We then identify those areas that require improvements. Following chapters will propose techniques dealing with them.

# 2.1 Process- and Technology-Level Hardening Techniques

The most obvious way to eliminate soft errors is to remove the radiation sources that cause them. To mitigate the dominant SER cause by low-energy neutrons and  ${}^{10}B$ , manufacturers have removed BPSG from virtually all advanced technology [4]. To reduce alpha particle emissions, semiconductor manufacturers use extremely high purity material and processes, production screening all materials having low background alpha emission measurements. Purified interconnect metal is used to reduce the natural alpha emission [20]. Coating the chip surface with a thick polyimide layer before packaging, can block alpha particles with energies up to approximately 9 MeV [21]. This would shield the active silicon from the particles being emitted from the ceramic packaging. Although large SER reductions are possible either by removing the sources of or shielding the  ${}^{10}B$  reaction products and alpha particles, a large portion of the high-energy cosmic neutrons will always reach

Figure 2.1: Structure and ionized charge collection of SOI. MOSFET is formed over a buried oxide layer in (a). The charge volume in SOI is significantly reduced thank to isolation by buried oxide layer, as compared with a bulk device in (b).

the devices and cause soft errors. Ultimately, high-energy cosmic neutron radiation defines the SER limit.

Modern methods for technology hardening of memories against SEU rely on reducing charge collection at sensitive nodes. Introducing extra doping layer as a novel p-well protection barrier can restrict substrate charge collection [22]. Triple-well [23] or quadruple-well [24] structures can improve resistivity against soft errors. Built-in junctions in these structure increase the recombination of charges far away from the active region. Epitaxial substrates reduce charge collection by funneling and provide some benefits in SEU reduction [25].

In addition to offering high-speed and low-power, silicon-on-insulator (SOI) is also renown for their resilience again SEUs [26]. Figure 2.1-a show the cross-section of SOI CMOS structure. MOSFET is formed on a thin SOI layer over a buried oxide layer, and the entire MOSFET is enclosed in a silicon oxide layer. The device is fabricated in a thin silicon layer that is isolated from the substrate by a buried oxide layer that acts as a dielectric. After an ionized strike, the charges deposited in the silicon substrate below the buried oxide cannot be collected at the drain because of the isolating dielectric between the drain and the substrate. The charge volume is significantly reduced in SOI, as compared with bulk device, as shown in 2.1-b. The charge collection depth thereby reduces from as much as a few microns in

bulk-Si devices to 100 to 300nm in SOI devices. Moreover, the buried oxide results in the absence of junction depletion region below the source and the drain. Thus, the P/N junction area is considerably reduced as compared to bulk CMOS processes, resulting in increased soft error immunity.

The abovementioned process- and technology-level hardening techniques can provide a significant improvement in SER reduction. Nevertheless, these techniques are not silver bullets that can provide a total solution to the softerror problem. Combinations with hardening techniques at other levels are required in order to achieve a high degree of soft error tolerance.

# 2.2 Circuit- and System-Level Hardening Techniques

Parity and error-correcting code (ECC) are widely employed in practice to protect memory caches from soft errors. In a parity scheme, a parity generator computes the parity bit of the memory word to be written into a cache. The parity bit are also stored in the cache. If a particle strike inverts one bit of a memory word, the error can be discovered by checking the parity code when the memory word is read. The area overhead of a parity scheme is very low. However, the drawback is that the scheme can detect but *cannot* correct the error. Parity scheme is sufficient for a cache storing only clean data (e.g., an instruction cache or a write-through data cache). Since all the data in the cache can also be found in memory, error recovery is simply a matter of discarding corrupted data and fetching correct data from memory. However, parity scheme is not sufficient for a cache holding dirty data (e.g., a write-back cache). Corruption of dirty data in the cache can leave the system into unrecoverable state if the data are referenced later. Error correcting capability provided by ECC is required for such a cache.

While numerous error correcting codes exist, the incurred area and speed penalty for implementing them can be excessive, especially for the ones that enable correction of multiple errors. Single-Error Correction Double-Error Detection Hamming code (SECDED) is the most widely-used ECC in practice. As implied by its name, SECDED can detect and correct a single-bit error, or detect a double-bit error in a codeword. The overheads incurred by SECDED is moderate and acceptable in most cases. The encoding/decoding circuitry of SECDED can be constructed as XOR trees and is quite fast. A multi-bit error (MBE) in a codeword may be left undetectable, or be detectable but uncorrectable by SECDED. An MBE may result from the error bits accumulated from multiple particle strikes over time, or the error bits caused by a single particle strike. We call the former case a *temporal* MBE, and the latter case a *spatial* MBE. The scaling trend toward smaller device dimensions and lower supply voltages has increased the probability that a strike will result in a spatial MBE [37] [38]. Interleaving different codewords in the same row can disperse the error bits of a spatial MBE into multiple codewords so that each error bit can be detected and corrected by SECDED [27] [28].

The probability of a temporal MBE can be negligible for a small, frequentlyaccessed memory cache [29]. However, for a very large cache or cache that may be idle for a long period while still holding data, the probability of a temporal MBE may not be insignificant. The probability of a temporal MBE can be reduced by *scrubbing* [30]. Scrubbing consists of periodically reading out the data from a memory cache, correcting any latent error, recomputing ECC, and writing the bits back. If scrubbing interval is short enough, the opportunity for a temporal MBE to arise is practically eliminated.

Nicolaidis et al. proposed the use of current sensors to protect memory from SEUs [39] [40]. A memory cell being in the steady state drives a very small current. But when its state is reversed due to the impact of an ionized particle, an abnormal current flows through the Vdd and Gnd lines of the cell. It is then possible to detect the occurrence of a SEU by implementing one current sensor (BICS) on each vertical power line of the cell array, as shown in Figure 2.2. Because BICSs monitor the vertical power lines of the memory, the detection of a SEU also indicates the position of the affected bit. Since memory cells on the same column can share a censor, the area overhead of BICS is lower than that of ECC. However, implementing BICS significantly increases the design complexity. Moreover, the efficacy of this technique relies on the capability of a sensor to capture a small current. Properly capturing the current will become more difficult due to larger variations in scaled process technologies.

Techniques to make the static storage cells to be radiation-hardened have been proposed. Those cells preserve their states even if the electrical states of some of their nodes is altered by an ionizing particle strike. Resistance elements can be added to the gate or drain terminals of transistors of the cross-coupled inverters in a SRAM cell [31] [32]. Those resistance elements will form RC low-pass filters filtering out the high-frequency components

Figure 2.2: Memory protection using BICS. A current sensor (BICS) added to each column of a cell array can detect the abnormal current accompanied by ionized particle striking on that row.

of a SEU spike. The main disadvantages of these techniques are that they increase the cell's size, and possibly degrade the write time and sense time of a memory cell.

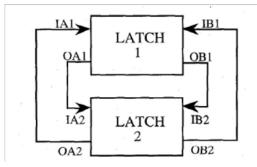

Dual interlocked storage cell (DICE) employs logic redundancy into a memory cell [33]. Figure 2.3 shows the principle of DICE. The two latches L1 and L2 store the same data, with the data in the uncorrupted latch providing state-preserving feedback to the corrupted latch. The differential outputs OA, OB of each latch section are connected to the differential feedback input IA, IB of the opposite, dual latch section. The basic drawback of DICE cells is their hardware cost, which is generally close to duplication.

## 2.3 Architectural Level Hardening Techniques

Conventional ECC is implemented in a *uniform* manner. That is every unit of data is protected by a check code of the chosen capability. Such an implementation treats data equally. However, cache lines stored in a memory cache can have different access frequency. Most frequently used (MFU) cache lines are most error-prone and errors in those blocks easily propagate unless checked. Kim et.al., proposed the concept of *parity caching* in which a small cache is allocated to store check bits of recently used data [34]. Parity caching

Figure 2.3: Principle of logic design hardened storage cell.

can obtain a high reliability with lower area overhead as compared with a uniformly-implemented ECC. They also proposed *shadow checking* in which the copies of MFU blocks are stored in a shadow cache [34]. The underlying idea is the same as parity caching, but the shadow cache performs error checking by means of comparison using the copies of data rather than check codes. The goal of shadow checking is to obtain a high reliability enhancement even in the presence of multi-bit errors with smaller chip area overhead. *Replication cache* enhances shadow checking concept by using a small fullyassociative cache to store the replica of every write to the L1 cache [35]. ICR cache uses these cache lines that are predicted to be "dead" as replicas of "hot" dirty data [36]. While these techniques offer lower area overheads than a uniform ECC, a large portion of the dirty data still remains unprotected if the locality of the data is low. The level of dependability achieved by these techniques is obviously not acceptable for applications demanding a very high reliability. In addition, while shadow checking and replication cache may be applicable to small L1 caches, application of them to large L2 caches is impractical [35].

The use of *early writeback* to improve cache reliability has been proposed [41]. Conventionally, a cache line stays in a cache until a cache miss occurs and the cache line is chosen as an eviction candidate. If a dirty cache line in a cache has a long lifetime, the possibility that the cache line being corrupted by SEU and causing an unrecoverable error can be high. By early writing back dirty blocks to a lower-level cache, the lifetime of the dirty blocks can be reduced. Instead of using ECC that incurs a high area overhead, simple parity can be sufficient to protect a cache employing early writeback. When

a clean cache line is verified to be corrupted by parity, the correct data can be obtained from the lower-level cache. Interestingly, early writeback may also have a favorable side-effect on processor performance. If a program makes frequently data updates, the writeback buffer may be full requiring the processor to stall its pipeline for the buffer to write back its old entries. Early writeback can improve performance by reducing those stall cycles caused by a full writeback buffer [42]. Periodically refreshing a cache with data from the lower-level cache is proposed in [43]. While these techniques improve the reliability of a cache with low area overheads, they increase the access activity to a lower-level cache and consequently its power consumption.

When hardware ECC is not available, software-implemented ECC can be used to protect memory caches [44] [45]. Given the address and size of the data block that needs to be protected, ECC software requests the operating system to allocate another block. Then, it calculates the check bits and stores them in the allocated block. Any modification to the data block requires its check bits to be recomputed by the means of software. Software-based ECC may be applicable to a code section or a less-frequently updated data section. However, for a data section receiving frequent updates, softwarebased ECC is impractical since the performance overhead of recomputing check bits is excessive in this case. Given that hardware-based approach is transparent to user's software and ECC support has increasingly being the norm in modern memory designs, the benefit of software-based ECC has become less appealing.

## 2.4 Room for Improvements

#### 2.4.1 Overhead Reduction

Error-correcting code (ECC) is an effective technique to protect data from soft errors. ECC may incur a moderate area cost that is acceptable for most cases. However, for some designs, the area penalty incurred by ECC may be undesirable. In order to keep area overhead low, a large codeword is preferred. However, in caches where data are accessed on a per-word basis, maintaining ECC on a per-word basis is preferred. Otherwise, if large codewords consisting of multiple data words is used for such caches, partial updates to the large codeword will frequently occur, incurring expensive *read-modify-write* operations that read the entire codeword, recompute the check bits, and write back the codewords. However, the cost of maintaining ECC on a per-word basis is high. For instance, a 32-bit word requires seven SECDED check bits and incurs a 22% area overhead. The proposed Zigzag-HVP described in Chapter 3 will provide cost-effective technique mitigate soft errors in caches with word-based access.

## 2.4.2 Soft Error Mitigation in Content-Addressable Memory

Memories can be classified into two types based on their access mechanisms: Random Access Memories (RAMs) and Content Addressable Memories (CAMs). Due to the difference in access mechanism, RAM and CAM require different mechanisms for mitigating soft errors. Coding techniques such parity or ECC have proved to be very effective in mitigating soft errors in RAMs. However, those techniques are not immediately applicable to CAMs because they depend on processing the full contents of the memory word outside the array, which is not possible in a normal CAM access. Mitigation of soft errors in CAMs is more challenging than in RAMs and has received little attention so far. However, since several components in a processor are built as CAMs, having those components to be resilience against soft errors necessary to increase the coverage of error protection in a processor. The proposed STCAM in Chapter 4 can deal with soft-error problem in CAMs.

#### 2.4.3 Pursuit of Soft-Error- and Defect Tolerance

Variation-induced defects become severe in scaled processes [46] [47]. Previous work has shown that ECC is effective in tolerating a high number of random defects in memory caches [48] [49]. It would be cost-effective if the same ECC resource can be used for both soft error tolerance for reliability and defect tolerance for yield. However, while a defective cell present in a block can be repaired by ECC, the block becomes vulnerable to soft errors. An error occurring in the block may be detectable but *uncorrectable*. This can get the processor system into an unrecoverable state, particularly when the corrupted data are dirty data that have no backup elsewhere in the memory hierarchy. The proposed SEVA in Chapter 5 can deal with this problem.

# Chapter 3

# Zigzag-HVP: Soft-Error Mitigation in Caches with Word-based Access

## **3.1** Introduction

Error Correction Code (ECC)—specifically Single Error Correcting and Double Error Detecting Hamming Code (SECDED)—is widely used to detect and correct soft errors in caches. For a SECDED codeword consisting of k information bits and c check bits, the relation between k and c is given by Equation 3.1.

$$2^c \ge k + c + 1 \tag{3.1}$$

Table 3.1 shows the number of check bits, and overhead of SECDED when the codeword size varies. The number of check bits just increases linearly as the codeword size increases exponential. Therefore, in order to keep the overhead low, a large codeword is preferred. However, this is not true for caches with word-based access where data are accessed on a per-word basis. Exemplified caches with word-based access are L1 data caches or L2 caches with write-through L1 caches. The later are commonly found in the memory hierarchy of multiprocessor systems because maintaining cache coherency at L2 cache is simpler if the accompanied L1 cache is write-through. For these caches with word-based access, maintaining ECC on a per-word basis is preferred [50] [51]. Otherwise, if large SECDED codewords consisting of

Table 3.1: Number of SECDED check bits for various data unit sizes. Doubling the size of data unit increases the number of check bits by one. Large data unit is preferred to keep the overhead low

| Data unit size (bits) | 16   | 32   | 64   | 128 | 256 |

|-----------------------|------|------|------|-----|-----|

| Number of check bits  | 6    | 7    | 8    | 9   | 10  |

| Overhead (%)          | 37.5 | 21.9 | 12.5 | 7.0 | 3.9 |

multiple words is used, partial updates to the large codeword will frequently occur, incurring expensive *read-modify-write* operations that read the entire codeword, recompute the check bits, and write back the codewords. However, the cost of maintaining SECDED on a per-word basis is high. For instance, a 32-bit word requires seven check bits and incurs a 22% area overhead.

This chapter describes **Zigzag-HVP**—a low-cost technique to detect and correct soft errors for these word-based accessed caches. The technique makes use of horizontal-vertical parity (HVP) [52]. HVP maintains the parity of the data array both horizontally and vertically. Basic HVP can detect and correct a single bit error (SBE), but not a multi-bit error (MBE). The probability that multiple errors will be accumulated from multiple particle strikes is very low in frequently accessed caches. Instead, MBE is mostly caused by a single particle strike that corrupts multiple bits at once [38]. Therefore, the corrupted bits are located close to one another. By dividing the data array into multiple HVP domains and interleaving bits of different domains, a spatial MBE is converted into multiple SBEs, each of which can be detected and corrected by the corresponding domain.

An error recovery routine is executed when an error is detected by horizontal parity. By sequentially reading the data words belonging to the parity domain, vertical parity can be recomputed to locate the error bit. The Built-In Self Test (BIST) [53] [54] is enhanced to include such a recovery function. We also modify the cache data path and write buffer to efficiently accommodate vertical parity updates. The evaluation results indicate that the area and power overheads of Zigzag-HVP caches are lower than those of the ECC-based ones.

The remainder of this chapter is organized as follows. Section 3.2 discusses related work. Section 3.3 explains the basic concept of HVP and its limitations. Section 3.4 describes Zigzag-HVP. Section 3.5 discusses the ap-

plication of Zigzag-HVP. Section 3.6 presents the evaluation results. Finally, Section 3.7 summarizes this chapter.

## 3.2 Related Work

The use of a small cache to store check bits or replicas of recently used data has been proposed [34]. Replication cache [35] enhances this concept by using a small fully associative cache to store the replica of every write to the L1 cache. ICR cache [36] uses these cache blocks that are predicted to be "dead" as replicas of "hot" dirty data. While these techniques offer lower overheads than ECC, a large portion of the dirty data still remains unprotected if the locality of the data is low. The portion of unprotected data for some benchmarks has been as high as 40% [34], 30% [36], or 5% [35]. The level of dependability achieved by these techniques is obviously not acceptable for applications demanding extremely high reliability. In addition, while a replication cache [35] may be suitable for small L1 caches, its application to large L2 caches is impractical. Zigzag-HVP can reduce the error rate by many orders of magnitude and can be applied to both L1 and L2 caches.

Cross-parity [55] can deal with MBEs by maintaining parity in the diagonal parity, in addition to the horizontal and vertical. However, an examination of the horizontal parity alone cannot expose the existence of some MBEs (e.g., MBEs where the number of error bits in the same row is even). Recomputation and checking of vertical or diagonal parity are required to detect such MBEs. However, these operations are expensive and it is impractical to execute them on every data access. By relying on interleaving to disperse the error bits, the existence of spatial MBEs in Zigzag-HVP can be detected by only examining the horizontal parity and the vertical parity only needs to be recomputed after the errors have been detected.

Nicolaidis et al. propose the use of current sensors that are built into the vertical power lines of a data array to detect the abnormal current dissipation accompanied with a particle strike [39] [40]. Memory cells on the same column can share a censor, resulting in a lower area overhead than ECC. However, the efficacy of this technique relies on the capability of the sensors to capture the small current; capturing the current more difficult due to larger variations in scaled process technologies. Zigzag-HVP is more scalable since it is not affected by process variations, and the degree of interleaving can be easily increased to deal with a higher probability of MBEs in scaled

process technologies.

The concept of interleaving has been used to combat burst errors (e.g., in data communications, compact disks, magnetic storages, hologram memories, and two-dimension barcodes). Existing interleaving schemes usually require intensive computation to be able to detect and correct the errors. However, on-chip caches are latency-critical, making these complex interleaving schemes unacceptable. Simple interleaving of ECC datawords in the same row to tolerate MBEs has been used in caches or memories [27] [28]. Zigzag-HVP interleaves the data in two dimensions and its practicality is explained in this chapter.

## 3.3 Horizontal-Vertical Parity and Its Limitations

Since our proposed Zizag-HVP is based on horizontal-vertical parity (HVP), this section first describes the concept of a basic HVP. We then explains the limitations of the basic HVP, namely HVP is unable to detecting and/or correcting multi-bit errors (MBEs). We then describes the characteristics of MBEs and the impacts of process technology having on the trends of MBEs. How such limitations of basic HVP are overcome by Zigzag-HVP is described in the next section.

#### 3.3.1 HVP Concept

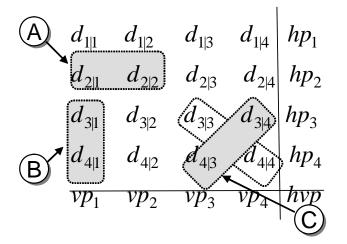

Figure 3.1 shows the concept of HVP [52]. The parity of the  $m \times n$  cell array is maintained both horizontally and vertically.  $d_{i|j}$  denotes a data bit in the *i*-th row and *j*-th column of the array.  $hp_i$  are  $vp_j$  are respectively the parity bits of the *i*-th row and *j*-th column. hvp is the sum parity of the vertical parity bits and this is also equal to the sum parity of the horizontal parity bits.

HVP can detect and correct single-bit errors (SBEs). Assume that the bit  $d_{i|j}$  is corrupted. When row *i* is accessed, the parity of the row is recomputed and compared to  $hp_i$ . A mismatch indicates the existence of an error in the row. The vertical parity is recomputed by sequentially reading all rows of the array. The resultant vertical parity are compared to those previously stored in the array. A mismatch in column *j* of the vertical parity indicates the position of the error bit in the victim row.

36

Figure 3.1: Horizontal-vertical parity. The parity is maintained both horizontally and vertically.

For an  $m \times n$  data array, HVP requires m+n check bits or an  $(m+n)/(m \times n)$  area overhead. The overhead is small when m and n are sufficiently large.

## 3.3.2 Limitations with Basic HVP

While the basic HVP scheme previously described can detect and correct an single-bit error (SBE), it may be unable to detect and correct a multi-bit error (MBE). Figure 3.2 shows several cases of MBEs in a  $4 \times 4$  cell array. In case A, since the corruption of both  $d_{2|1}$  and  $d_{2|2}$  leaves the parity of row 2 unchanged, horizontal parity is unable to detect the existence of the errors. Examining vertical parity can show the existence of the error. However, recomputation of vertical parity is an expensive operation which requires all the rows to be read from an array. Examining vertical parity on every cache access is therefore impractical. In case B, while the existence of errors in row 3 and row 4 can be detected by  $hp_3$  and  $hp_4$ , the exact positions of the errors in the rows cannot be revealed by vertical parity since the vertical parity of column 1 remains unchanged. In case C, while horizontal parity reveals the existence of errors in rows 3 and 4, HVP still cannot determine which one of the two pairs ( $d_{3|4}, d_{4|3}$ ) or ( $d_{3|3}, d_{4|4}$ ) has been corrupted.

Figure 3.2: **Examples of multi-bit errors.** Multi-bit errors may be undetectable by horizontal parity (case A), or detectable but uncorrectable (case B and C).

#### 3.3.3 Multi-Bit Errors and Characteristics

An MBE results from the error bits accumulated from multiple particle strikes, or the error bits caused by a single particle strike. We call the former case a *temporal* multi-bit error, and the latter case a *spatial* multi-bit error.

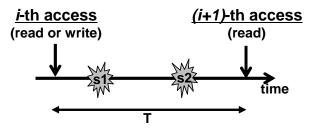

In a temporal MBE, a particle strike occurs and corrupts a single bit. Another strike occurs and corrupts a different bit before the erroneous data are accessed through which the error could have been detected and corrected. The error bits in a temporal MBE are *randomly* located in the data array. Temporal MBE can occur in very large memories where the data might not be accessed for a long time and the probability that undetected errors will accumulate cannot be ignored.

A spatial MBE is resulted from a single strike corrupting multiple bits at once. In contrast to a temporal MBE, the error bits in a spatial MBE are *closely* located. The scaling trend toward smaller device dimensions and lower supply voltages has increased the probability that a strike will result in a spatial MBE [37] [38]. Experiments have confirmed the existence of up to four-bit spatial MBEs for SRAM fabricated in a 90 nm process [38].

## 3.4 Zigzag-HVP

Since on-chip caches usually have a high access frequency, an error generated by a strike is likely be detected and corrected before the next strike occurs. The results in Section 3.6 confirm that probability for a temporal MBE to occur in an on-chip cache is very low. We therefore focus on measures against spatial MBEs.

Zigzag-HVP enhances the basic HVP to effectively deal with spatial MBEs. Zigzag-HVP exploits the property that the error bits in a spatial MBE are closely located. Zigzag-HVP groups the data bits of a cache into multiple *parity domains*. Each parity domain consists of several data words and is protected by HVP. By interleaving different parity domains, the spatial error bits in a spatial MBE are converted to multiple SBEs. Each SBE belongs to a parity domain that can be successfully detected and corrected. The bit interleaving scheme, parity update mechanism, error detection, and recovery mechanism are described in this section.

Let us define some terminology. A cache can be expressed as a data array with  $N_R$  rows. Each row contains  $N_L$  cache lines, each line contains  $N_W$ words, and each word contains  $N_B$  bits. Cache size is  $N_R \times N_L \times N_W \times N_B$ bits. The cache size,  $N_W$ , and  $N_B$  are usually specified in advance in a cache design. Given the predetermined architectural parameters (e.g., cache size,  $N_W$ ,  $N_B$ , cache associativity), tools like Cacti [56] can automatically calculate  $N_R$ ,  $N_L$  that yield good trade-offs between access time and power efficiency.

#### 3.4.1 Bit Interleaving Schemes

A spatial MBE can have multiple error bits in the same row, or the same column [38]. We will now describe the interleaving schemes to deal with these patterns of error bits.

#### Dealing with Horizontal MBEs

Interleaving layout of words converts adjacent error bits on the same row into SBEs in different words. ECC-protected caches have used this technique to effectively reduce MBEs on the same ECC unit [27] [28]. We use the same technique in Zigzag-HVP to deal with horizontal MBE. The words interleaved in a row belong to different parity domains. Figure 3.3-a illustrates a simple

example; two words are interleaved in each row and up to two bit errors can be tolerated  $(b_i^j \text{ indicates the } j\text{-th bit of the } i\text{-th word in a row}).$

To tolerate up to d bit errors, we must interleave at least d different words. Upon data access, only one bit is multiplexed for every d consecutive bits. We have two possible options in choosing how to interleave words horizontally: 1)interleaving words from different cache lines or 2) interleaving words from the same cache line. If the the number of cache lines in each row  $N_L$  is larger than or equal to d, we should interleave words from different cache lines. In this case, the words belonging to a cache line can be accessed at once, which is preferred for line-based cache operations such as line replacements or cache refills. If  $N_L$  is smaller than d (possible in small caches), the interleaved word could be selected from the same line. In this case, reading a whole cache line requires several cache accesses since an access can only read a subset of words of the cache line.

The number of horizontal parity bits is equal to the number of cache words  $(N_R \times N_L \times N_W)$  and is independent of how the words are interleaved.

#### Dealing with Vertical MBEs

Vertical MBE can also be dealt with by using the same interleaving concept as in the case of horizontal MBE. Consecutive bits in the same column are protected by different vertical parity bits. In Figure 3.3-b, bits in the even and odd rows are protected by a different vertical parity and up to two bit errors can be tolerated in this example. In order to tolerate up to d bit errors, this scheme requires d vertical parity bits in each column, or  $d \times (N_L \times N_W \times N_B)$ bits in total. Since the vertical parity bits are frequently updated, they should be implemented as flipflops or latches which consume larger areas than normal SRAM cells. The overheads for vertical parity increase with a large d and may offset the benefit of HVP.

We instead propose an original scheme for encoding vertical parity. The HVP domain is constructed so that a vertical bit is calculated from bits located in a *zig-zag* path, rather than from bits in the same column. The physical locations of any two bits in the same zig-zag path are separated by a sufficient distance so that both cannot be corrupted by a particle strike. The number of vertical parity bits in this scheme is equal to the number of columns and is *independent* of d.

To formalize the scheme, the expression  $w_{ijk}$   $(0 \le i < N_W, 0 \le j < N_L, 0 \le k < N_R)$  is used to refer to the *i*-th word of the *j*-th cache line of the

Figure 3.3: Interleaving schemes to deal with MBEs. Bits are interleaved to tolerate horizontal MBEs in (a). Scheme in (b) tolerates horizontal & vertical MBEs but requires many vertical parity bits. Scheme in (c) can tolerate horizontal & vertical MBEs with fewer vertical parity bits.

k-th row. A parity domain  $\mathcal{PD}_{mn}$   $(0 \leq m < N_W, 0 \leq n < N_L)$  is a set of words that can be expressed by Equation 3.2.

$$\mathcal{PD}_{mn} = \{ w_{inj} | (i-j) \equiv m \pmod{N_W} \}$$

(3.2)

Figure 3.3-c illustrates a simple example. The data array has four rows, each row contains two cache lines, and each cache line has two two-bit words.  $b_{ijk}^{l}$  indicates the *l*-th bit of word  $w_{ijk}$ . The two cache lines in each row are interleaved to tolerate horizontal MBEs. Two zigzag paths which consist of bits belonging to the same parity domain ( $\mathcal{PD}_{00}$ ) are shown in the figure. The parity domain consists of four words:  $w_{000}$ ,  $w_{101}$ ,  $w_{002}$ , and  $w_{103}$ . MBEs having up to two bits can be tolerated in this example.

The proposed scheme can tolerate up to an  $N_W$ -bit vertical MBE. Given that a cache line typically consists of  $8\sim32$  words and an SS-MBE contains no more than four bits in current processes [38], our zigzag scheme can effectively deal with vertical MBEs.

#### Other MBEs

If the interleaving scheme in Section 3.4.1 tolerates up to  $d_1$  consecutive error bits in a row and the interleaving scheme in Section 3.4.1 tolerates up to  $d_2$ consecutive error bits in a column, then any MBE in which the error bits are confined to a  $d_2 \times d_1$  array can be successfully detected and corrected.

### 3.4.2 Parity Update Mechanism

Any update of a word (e.g., in processor writes or cache line replacements) requires the parity of the corresponding domain to be updated. From Equation 3.2, the parity domain that a word belongs to can easily be determined from the values of the bits used to index the row, and the values of the bits used to index the row.

Updating of horizontal parity is simple: The parity bit is newly calculated from the updated word value and stored together with the word. Updating of the vertical parity follows Equation 3.3.

$$\mathcal{VP}_{new} = \mathcal{VP}_{old} \oplus w_{old} \oplus w_{new} \tag{3.3}$$

The new vertical parity of the domain  $(\mathcal{VP}_{new})$  is the exclusive-OR of the old vertical parity  $(\mathcal{VP}_{old})$ , old and new values of the data word  $(w_{old}$  and  $w_{new})$ . The horizontal parity bits are included in the  $w_{old}$  and  $w_{new}$ .

The update the vertical parity requires the old value of the word. Section 3.5 discusses how caches can be modified to effectively supply the old words.

A Vertical parity update can be done in parallel with writing the data word into data array. Therefore, the access latency of a Zigzag-HVP cache is comparable to that of a cache protected by a simple parity.

#### 3.4.3 Error Recovery

When a word is read, the horizontal parity bit is recomputed and compared with the pre-stored value. A mismatch indicates the existence of a bit error in the word. A dedicated error recovery routine is then triggered. Since there is a possibility that bit error(s) may also be present in other word(s), the routine examines not only the parity domain containing the identified erroneous word but also all the parity domains. For each domain, the routine sequentially reads all the words belonging to that domain. The horizontal parity of each word and the vertical parity of the domain are recomputed, and compared with the old ones. If an SBE is present in the domain, its location can be determined.

Modern caches are typically equipped with a Built-In Self Test (BIST) [53]. The BIST accesses data in particular access patterns, also called *marching patterns*, to locate potential manufacturing defects. Modern BISTs are programmable and support various marching patterns [54]. The capability of sequentially reading the words belonging to a parity domain can be supported by extending the existing BIST hardware. The address patterns of those data words belonging to the same parity domain are derived from Equation 3.2. By accommodating such patterns into the BIST, an error recovery routine can be achieved at modest hardware cost.

Recovering from errors requires the cache to be fully scanned. Nevertheless, the overhead for error recovery is small since soft errors occurs very infrequently, For instance, let us consider a 512KB cache. Assuming a perword access throughput of 512M-word/sec, a full scan of all parity domains in the cache requires 269  $\mu$ sec. Such an overhead is incurred once every 17 years and is therefore negligible (refer to Section 3.6.5 for the cache error rate).

## 3.5 Applications of Zigzag-HVP

Two possible candidates for Zigzag-HVP are 1) L1 write-back caches and 2) L2 caches with write-through L1 caches. These two candidates share unique properties: They receive frequent word-based updates from processors, and they may hold dirty data so that not only detection but also correction capabilities are required to be able to fully tolerate soft errors. This section focuses on how the data paths of these caches can be modified so that the vertical parity update of Zigzag-HVP can be efficiently executed.

#### 3.5.1 L1 Write-back Caches

Zigzag-HVP requires the old value of the modified word for vertical parity update. Before writing a word, the L1 cache needs to probe its tag to determine whether it is holding the word or not. The L1 cache is adapted so that data access occurs in parallel the tag probing. If the line is found in the L1 cache, the old value of the data word is accessible after the tag probe phase. The cache then proceeds to write the new value while the old value is passed to the vertical parity update unit. Such a modification is easily accomplished since, in practice, L1 caches already perform a tag probe and data access in parallel to achieve minimum latency.

Write-back caches usually employ a *write-allocate* policy [57]: A write miss fetches the missed line from the lower level cache and allocates the location for storing the line. In the case of a write miss, the vertical parity update unit will receive the old value of the modified word when the line is retrieved from the lower level cache.

### 3.5.2 L2 Caches with Write-through L1 Caches

Many processors adopt a cache hierarchy in which the L1 data cache is writethrough and is backed by a large L2 write-back cache [58] [50] [59]. Making the L1 data cache a write-through cache simplifies the task of maintaining cache coherency in multiprocessor systems [60]. Maintaining simple parity for the detection of errors is sufficient for write-through L1 caches since correct data can be obtained from the L2 caches. The application of Zigzag-HVP to L2 caches is discussed hereafter.

#### Write Buffer and Its Implication:

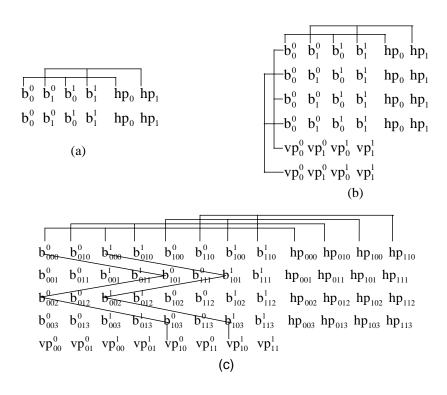

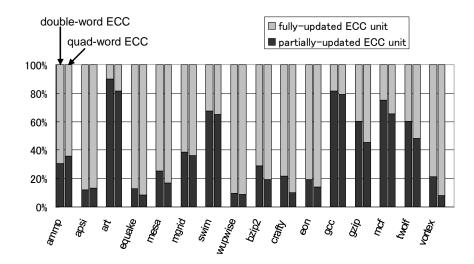

A processor with a write-through L1 cache usually includes a write buffer. The write buffer has two essential functions: 1)absorbing processor writes at a rate faster than the L2 cache could, thereby preventing processor stalls and 2) coalescing writes to the same cache block, thereby reducing the traffic to the L2 cache. The reduction of word-based updates to the L2 cache by the write buffer has an implication in the implementation of ECC in the L2 cache. One could maintain ECC in large data units (e.g., double-word (64-bit) [61], or per quad-word (128-bit) [62]) to reduce the hardware overheads, and rely on the write buffer to merge updates to consecutive words into a single update of a large ECC word so that the read-modify-write operations could be reduced.

To evaluate the capability of the write buffers to coalesce modified words into a large ECC data unit, we model a superscalar processor with a write buffer of eight entries, where each entry is of 32 byte (equal to the size of L1 cache line). The L1 data cache is a four-way, 16KB, non-write-allocate, writethrough cache. The details of the configurations of the processor are indicated in Table 3.6.1. The write buffer attempts to retire the oldest entry whenever more than six entries are occupied (*retire-at-6* policy [63]). Two ECC unit sizes are evaluated: double-word and quad-word. For each ECC unit size, we measure the amounts of partially-modified and fully-modified ECC units retired from the write buffer to the L2 cache for SPEC2000 benchmarks. The results are shown in Figure 3.4. A majority of ECC codewords are partially modified. These partially-modified ECC codewords require expensive readmodify-write operations and unavoidably incur significant overheads.

Per-word ECC incurs a large hardware cost, while a larger ECC unit incurs frequent read-modify-write operations even with the presence of the write buffer. Zigzag-HVP can deal with such shortcomings with ECC schemes.

#### Support for Efficient Vertical Parity Updates

The old values of the modified words, which are required for vertical parity update in Zigzag-HVP, can be supplied directly by the L2 cache. However, since the L2 cache is large, reading the old values from L2 caches incurs a large power overhead. Moreover, while tag access and data access are performed in parallel in L1 caches, the tag access and data access in L2 cache are done sequentially for low-power consumption. Therefore, the latency of reading

Figure 3.4: Distribution of partially- and fully-modified ECC codewords. Applications such as *art*, *swim*, *gcc*, *gzip*, *mcf*, *twolf* have large fractions of partially-modified codewords that require expensive read-afterwrite operations.

the old values from the L2 cache cannot be hidden.