# 高性能光通信用受信回路の 設計に関する研究

1998年 佐野栄一

## 目 次

| 第1章 | 序論                              | 1  |

|-----|---------------------------------|----|

| 1.1 | 研究の背景                           | 1  |

| 1.2 | 受信回路研究の歴史                       | 4  |

| 1.3 | 研究の目的と課題                        | 10 |

| 1.4 | 本論文の構成                          | 11 |

| 第2章 | 受光デバイスの高速化設計                    | 14 |

| 2.1 | はじめに                            | 15 |

| 2.2 | 基本方程式                           | 16 |

|     | 2.2.1 電磁界の挙動                    | 16 |

|     | 2.2.2 キャリアの挙動                   | 17 |

| 2.3 | 流体モデルを用いたGaAs MSM-PDの基本動作解析     | 19 |

| 2.4 | 粒子モデルを用いたMSM-PDの高速化設計           | 22 |

|     | 2.4.1 GaAs MSM-PDの設計            | 24 |

|     | 2.4.2 InGaAs MSM-PDの設計          | 28 |

| 2.5 | まとめ                             | 35 |

| 第3章 | 受信用集積回路の高性能化設計                  | 36 |

| 3.1 | はじめに                            | 37 |

| 3.2 | 10 Gbit/s 等化増幅集積モジュール           | 38 |

|     | 3.2.1 増幅器、パッケージー括設計法            | 38 |

|     | 3.2.2 デバイス技術                    | 40 |

|     | 3.2.3 入出力整合設計                   | 41 |

|     | 3.2.4 等化増幅集積回路モジュールの試作          | 42 |

| 3.3 | ベースバンド回路に適したデバイス性能指数            | 46 |

|     | 3.3.1 デバイス性能指数の導出               | 46 |

|     | 3.3.2 実験との比較                    | 48 |

| 3.4 | モノリシック集積化による低エネルギー化             | 52 |

|     | 3.4.1 集積化の重要性                   | 52 |

|     | 3.4.2 InP/InGaAs DHBTを用いた3R機能回路 | 53 |

| 3.5 | まとめ                             | 58 |

| 第4章 光            | :電子混在回路シミュレーション手法                      | 59  |

|------------------|----------------------------------------|-----|

| 4.1              | はじめに                                   | 60  |

| 4.2              | デバイスモデル                                | 61  |

|                  | 4.2.1 レーザダイオード                         | 61  |

|                  | 4.2.2 受光デバイス                           | 62  |

|                  | 4.2.3 MESFETおよびHFET                    | 63  |

|                  | 4.2.4 バイポーラトランジスタ、ダイオードおよび抵抗           | 63  |

|                  | 4.2.5 光ファイバ                            | 63  |

|                  | 4.2.6 光変調器                             | 64  |

|                  | 4.2.7 パルスパターン発生器                       | 64  |

|                  | 4.2.8 シミュレータへのインプリメント                  | 64  |

| 4.3              | シミュレーションと実験との比較                        | 65  |

| 4.4              | まとめ                                    | 69  |

| 第5章 集            | 積化受光回路の高速化設計                           | 70  |

| 5.1              | はじめに                                   | 71  |

| 5.2              | InP/InGaAs HBT集積化受光回路の基本構成             | 72  |

| 5.3              | InP/InGaAs SHBTを用いた集積化受光回路の課題          | 74  |

|                  | 5.3.1 InP/InGaAs pin-PD/SHBT集積化受光回路の試作 | 74  |

|                  | 5.3.2 ホモ接合 <i>pin-PD</i> の解析           | 76  |

| 5.4              | InP/InGaAs DHBTを用いた集積化受光回路の高速化設計       | 79  |

|                  | 5.4.1 ダブルヘテロ接合化による高速化                  | 79  |

|                  | 5.4.2 最適なコレクタ層厚さの明確化                   | 82  |

| 5.5              | まとめ                                    | 88  |

| 第6章 結            | 論と将来展望                                 | 89  |

| 6.1              | 結論                                     | 89  |

| 6.2              | 将来展望                                   | 93  |

| 6.3              | まとめ                                    | 96  |

| 付録               |                                        | 97  |

| 謝辞               |                                        | 116 |

| 参考文献             |                                        | 118 |

| 本研究に関            | する公表論文リスト                              | 131 |

| <b>会老</b> 公主\$\\ | +11 7 L                                | 122 |

## 序論

#### 1.1 研究の背景

光の超広帯域性を利用した光通信は、半導体レーザと低損失石英系光ファイバの出現により目覚ましい発展を遂げてきた。日本電信電話公社(現在、日本電信電話株式会社、NTT)は、1983年に1.3 μm 帯単一モードファイバを用いた 400 Mbit/s 伝送方式(F-400M)の導入を開始し[1.1]、1985年に日本縦貫ルートが開通した。1987年にはさらに 4 倍の F-1.6 G 方式が実用化された[1.2]。これらの方式は旧ディジタルハイアラーキに基づくもので、1.544 Mbit/s を 1 次群として F-400M は 5 次群に相当するものであった。 F-400M 方式では光ファイバ 1 本当たり 5760 ch を収容でき電話主体のサービスには十分な性能であった。しかしながら、音声のみならず画像伝送サービスも含めた将来の広帯域ISDN(Integrated Services Digital Network)を実現するためには、さらに高速なネットワークインターフェースが必要であると予想された。また、当時世界的に 3 種類のディジタルハイアラーキが存在し、通信のグローバル化に対処するためには世界標準化が必要であった。このため、1988年に 155 Mbit/s を基本単位とする同期ディジタルハイアラーキ(SDH: Synchronous Digital Hierarchy)が世界標準化された[1.3]。1990年にはSDHに基づいた 2.488 Gbit/s 伝送方式(FTM-2.4G)が商用化された[1.4]。光ファイバについては、当初の 1.3 μm 帯から最低損失の 1.55 μm 帯に零分散をシフトした分散シフトファイバが長距離伝送路の主流となった。

近年、「マルチメディア」というキーワードのもとに将来の情報通信サービスが盛んに議論されている。つい最近NTTは、「10 M ピットを 1 秒で送るマルチメディア・ネットワーク・サービスを 2005年までに月額 1 万円程度のコストで実現するための研究開発」を提案した。このためには、電話の速度 64 kbit/s と比較して、10 Mbit/s で 156 倍、さらに将来の高精彩画像伝送まで視野に入れると、約 3 桁高いネットワークのスループットが必要となる。現在の電話と同程度の料金であること、NTTの電力使用量が日本全体の 0.5 % であり将来のエネルギー問題の観点からこれ以上の電力消費は許されないことを考慮すると、2 - 3 桁低エネルギーな通信機器を来世紀初頭までに実用化することを意味する。現在のネットワーク構成の延長で考えると、現用装置の光ファイバ 1 本当たりのスループットが約 1 Gbit/s 建いであるから、0.2 - 1 Tbit/s 程度のスループットが必要となる。しかしながら、マルチメディアサービスを支えるネットワークは現在の

ネットワークとは異なるものである。リアルタイム性が要求される電話主体の現在のネットワークは回線交換主体で階層化され中央集権的であるのに対して、マルチメディアサービスではリアルタイム性を必ずしも必要としない情報の比率が高まるためバケット交換方式が適しており分散制御型となると考えられている。マルチメディアという多様なサービスを効率的に提供できるネットワークとして波長分割多重(WDM: Wavelength Division Multiplexing)ネットワークが提案され精力的に研究が行われている[1.5]。ユーザアドレスに対して波長を割り当て波長ルーチングを行うことにより、任意の速度およびフォーマットを持つ情報の流通が可能となる。このようなWDMネットワークを実現するためには、高精度な波長制御光デバイス、光メモリ、光フリップフロップ等の研究開発を必要とし、来世紀初頭のサービスに導入されることは難しいと考えられる。当面の現実的な解は非同期転送モード(ATM: Asynchronous Transfer Mode)ベースのネットワークであり、超大容量 ATM バックボーンネットワークに必要なテラビット通信を目指した研究が活発に行われている。

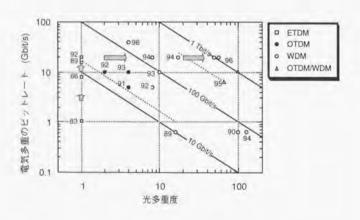

研究段階の光ファイバ伝送実験の変遷を図1.1に示す。1980年代は電子デバイスを用いた時分割多重(TDM: Time Division Multiplexing)により速度向上がなされてきた。1990年に入ると電子デバイスの高速化が難しくなるとともに光デバイス技術が進展したことにより、WDM および光TDM といった光領域での多重化によりスループットの向上が図られてきた。1996年には、富士通、AT&T、NTTの3つの研究グループにより1 Tbit/s の光伝送実験が報告されている[1.6]-[1.8]。また、希土類ドープファイバ増幅器の登場により光のまま信号を増幅することが可能となった[1.9]。希土類ドープファイバ増幅器は減衰した光信号を増幅する機能を有するものの、雑

図 1.1 光ファイバ伝送実験の変遷

音の累積と波長分散に伴う波形歪により信号品質が劣化するため、システムにより決定される伝送距離毎に波形再生を行う必要がある。中心のように光デバイス技術は極めて高いポテンシャルを有しているが、伝送路を全光処理化することは現状では不可能である。波形再生に必須な光フリップフロップの研究が活発に行われているが、残念ながら電子デバイスより優れた光フリップフロップは実現されていない。また、光 TDM 伝送実験に使用されている多重化回路(MUX:Multiplexer)および分離回路(DEMUX:Demultiplexer)は電子回路の MUX および DEMUX と等価ではない。電子回路ではNRZ(Non-Return-to-Zero)信号バルス幅は常にビットレートの逆数であるが、光 MUX および DEMUX は論理積(AND)等の組み合わせ回路であるため信号バルス幅は信号光と制御光のタイミングに依存する。このため高精度なタイミング制御が必要であると考えられる。すなわち、電子デバイスより優れた光フリップフロップが実現されない限り、電子デバイスが不可欠であると考える。

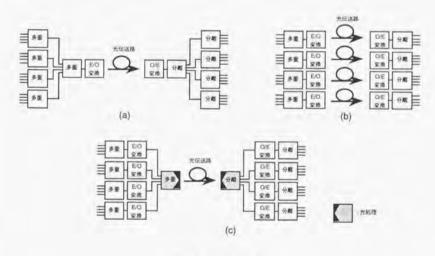

ここで再度、多重化光伝送の形態を整理して図1.2に示す。(a) は電子デバイスで時分割多重化するものであり、スループットの向上には電子デバイスと光デバイスの高速化という方策が採られる。上記のように1980年代のアプローチである。(b) は空間分割多重伝送であるが、この方式はコスト・パフォーマンスでは(a)とほぼ同一である。(c) はある速度まで電子デバイスで時分割多重し、その後WDMあるいは光TDMにより多重化する方式であり、1990年代に研究が活発となっ

図1.2 光伝送の形態

<sup>&</sup>lt;sup>0.21</sup> 光ファイバの波長分散に関しては、分散マネジメントにより 1000 km 以上の伝送が可能となっているが、既設ファイバへ適用するには課題が多い。

たものである。ここで注意すべき点は、光多重化技術により光伝送路のコスト・パフォーマンスは向上するが、(a)と同一の電子デバイスが使用される限り光中継器のコスト・パフォーマンスは(a)の形態と変わらないということである。もちろん、既存の動作原理に基づく電子デバイスでは1 Tbit/sの動作速度を実現することは不可能であり、最終的にはWDMによりスループットを上げることになる。この場合、電子デバイスおよび光デバイスには多重度分だけのコスト・パフォーマンスの向上でが望まれることになる。要約すると、来世紀初頭にマルチメディアサービスを提供するためには、現在と同等のコストで、現状と比較して2-3 桁低エネルギーな光通信装置を実現する必要がある。

#### 1.2 受信回路研究の歴史

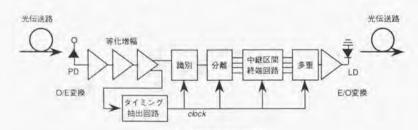

研究段階の光伝送実験にはハイブリッド回路が用いられることもあるが、光通信用中間中継装置および端局装置を実用化するためには信頼性、経済性等の観点から集積回路が必須となる。ここで光通信用中間中継器の構成例を図1.3に示す。各プロックは1チップもしくは数チップの集積回路で構成されている。光伝送路を送られて来た光信号は光一電気(O/E)変換された後、等化増幅部で増幅される(Reshaping)。FTM-2.4G方式では信号フォーマットはNRZであり伝送レートに対応するクロック成分を持たないため、タイミング抽出回路によりクロックを生成する(Retiming)。このクロックを用いて識別器により雑音およびタイミングジッタの少ない同期ディジタル信号に再生される(Regenerating)。これら3つの機能は各々の頭文字を取って"3R"と言われる。再生された信号は分離(DEMUX)され、符号誤り検出等の中継区間の監視処理を行った後が、再び時分割多重化され、電気一光(E/O)変換され光伝送路に送出される。本研究ではO/E変換から識別器までの3R機能回路を対象とし、この部分を受信回路と呼ぶこととする。

図 1.3 中間中継器の構成例

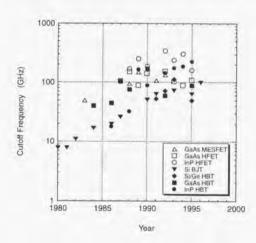

上記のF-400M方式の受光デバイスとしてはGeアバランシェフォトダイオード(APD: Avalanche Photodiode)が、F-1.6G 方式の受光アパイスとしては InGaAs APD が用いられていた[1.2]。高速集 積回路はシリコンバイポーラトランジスタにより実現されていた[1.10][1.11]。ここで、論文ある いは国際会議等で発表されたトランジスタ電流利得遮断周波数の年代推移を尺度とした電子デバ イス性能向上の歴史を図1.4に示す。筆者が本研究に着手した1980年代後半はF-1.6G方式の実用 化が終了した時点であった。当時の実用的なシリコンパイポーラトランジスタおよびGaAs MESFET<sup>(E)</sup>の電流利得遮断周波数は 20 GHz 程度であり、これらのトランジスタを用いて 10 Gbit/ sを越える光中継器用集積回路を実現することは困難であった。このような状況の中で1988年に、 Yamane et al. [1.12]によりゲート長 0.1 µm の自己整合イオン注入 GaAs MESFET により 90.8 GHz という高い電流利得遮断周波数が得られることが報告され、翌年には、このデバイス技術に基づ く識別器を使用した 10 Gbit/s 光伝送実験が Hagimoto et al. [1.13]により報告された。これにより 10 Gbit/s ディジタル回路の実現の見通しが得られたが、等化増幅およびタイミング抽出回路に用 いられる増幅器については 10 Gbit/s の目処は立っていなかった。図 1.4 からも明らかなように、 1980年代後半には分子線エピタキシー(MBE: Molecular Beam Epitaxy)に代表される結晶成長技術 の発展に支えられて、ヘテロ構造電界効果トランジスタ(HFET: Heterostructure Field-Effect Transistor) 在のあるいはヘテロ接合バイポーラトランジスタ(HBT: Heterojunction Bipolar Transistor)

図 1.4 トランジスタ電流利得遮断周波数の年代推移

<sup>\*\*</sup>の高速化が期待できないため、低電力、小型化等が必要となる。

<sup>&</sup>lt;sup>進制</sup>当時、電流利得遮断周波数が 100 GHz 程度のリセスゲート構造 GaAs MESFET に関する研究成果が報告されているが、しきい値電圧制御性の問題があり集積回路用デバイスとは言えなかった。集積回路用デバイスとしてはイオン注入により製造される MESFET が適している。

<sup>&</sup>quot;"種々のデバイス構造が提案されているが、ここでは総称として HFET と呼ぶことにする。

等の化合物半導体へテロ構造デバイスの研究が活性化された。ヘテロ構造デバイスの性能はそのポテンシャルの高さを反映して、急激に向上した。これらのデバイスの高速集積回路応用に関しては AIGaAs/GaAs HBT が先鞭をつけている。1989 年、Akagi er al. [1.14]により 10 GHz 帯域の前置増幅器と 10 Gbit/s 識別器が、Ishihara et al. [1.15]により 9 GHz 帯域の利得可変増幅器が報告された。しかしながら、これらの報告は、そこで用いられた AIGaAs/GaAs HBT デバイス技術と高速集積回路設計技術のポテンシャルの高さを示しているが、ウェバ状態で高周波プローブを用いた測定結果であった。当然のことながら、集積回路はバッケージ実装されて初めて使用できる状態となる。10 Gbit/s を越える周波数領域では実装に付随する寄生容量および寄生インダクタンスの影響が大きくなり、高利得、広帯域な増幅器モジュールを実現することが難しくなる。このため、本研究以前には 10 Gbit/s を越える増幅器モジュールは実現されていなかった。

超高速デバイスの研究開発においては、集積回路の高速化に適したデバイス構造を明確化することが極めて重要である。デバイス研究者と回路研究者のインターフェースとしてデバイスの等価回路バラメータが一般的に採られてきた。従来、等価回路バラメータを変化させて回路シミュレーションを行うこと(感度解析)により回路の最高動作速度を求める方法が用いられていた。しかしながら、これらのパラメータの間には相関があり、相関まで厳密に押えて議論することはかなり困難なことである。むしろ、電流利得遮断周波数あるいは最大発振周波数というデバイス研究者に馴染深いパラメータを用いて回路の動作速度とデバイス性能の関係を明確化する方が集積回路の高速化に寄与できるものと考えられる。さらに、電子デバイスでどの速度まで多重化できるのかということは将来の通信ネットワークを考える上で重要な関心事である。回路の速度性能とデバイス性能との間の簡単な関係式は通信ネットワーク研究にも寄与できるものと考えられる。

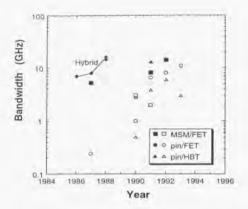

従来の光中継器において、光デバイスは InP 基板上に、電子集積回路は Si 基板上に形成されているため、当然のことながら光中継器はハイブリッド回路とならざるを得ない。これらを同一基板上に形成できれば、ハイブリッド実装に伴う寄生効果を除去できることから性能面での優位性が期待できるとともに、信頼性および経済性でも有利であると考えられる。このような特徴を持つ光電子集積回路(OEIC: Optoelectronic Integrated Circuit)を用いた光電子集積化光中継器が1979年に Yarivの Yu-Tにより報告された [1.16]。その後、Yariv0 Yu-T1 により報告された Yariv1 の様のと性能を表1.1 と図1.5 にまとめて示す。受光の研究が精力的に行われてきた。本研究で対象とする集積化受光回路について、主な国際会議あるいは論文で報告されているもの Yariv1 の構成と性能を表1.1 と図1.5 にまとめて示す。受光デバイスとして Yariv1 の Yariv2 に Yariv3 に Yariv4 に Yariv6 に Yariv6 に Yariv7 に Yariv8 に Yariv8 に Yariv9 に Ya

表 1.1 集積化受光回路の構成と性能

| Ac III. CA ET |     | 構成         |     |        | デバイス性能               |         | 受光回路性能            |       |

|---------------|-----|------------|-----|--------|----------------------|---------|-------------------|-------|

| 年代            | 波長  | デバイス       | 磁   | PD     | トランジスタ               | 帯域      | 速度, 感度            | 参考文献  |

| 1984          | 短波長 | pin/MESFET | (a) |        |                      | 300MHz  | 400Mb/s           | [1:17 |

| 1986          | 短波長 | НРТ/НВТ    | (f) | 2GHz   | fr=8GHz              | 80MHz   |                   | [1.18 |

| 1987          | 長波長 | pin/JFET   | (a) |        |                      | 240MHz  | 400Mb/s           | [1.19 |

| 1988          | 長波長 | HPT/HBT    | (f) |        | ft=5GHz              |         | 100Mb/s, -26dBm   | [1,20 |

| 1988          | 長波長 | pin/HFET   | (c) |        |                      |         | 2Gb/s, -23,7dBm   | [1.21 |

| 1988          | 短波長 | MSM/MESFET | (e) | 105GHz |                      | 5.2GHz  |                   | (1.22 |

| 1990          | 長波長 | MSM/HFET   | (b) | 7.7GHz | ft=13GHz             | 3GHz    |                   | [1.23 |

| 1990          | 長波長 | pin/HFET   | (b) |        | ft=17GHz             | 1GHz    | 1.6Gb/s           | 11.24 |

| 1990          | 長波長 | pin/HBT    | (a) |        | fr=30GHz, fmax=12GHz | 500MHz  | 1Gb/s, -26.1dBm   | [1.25 |

| 1990          | 長波長 | pin/HBT    | (a) |        | ft=35GHz, fmax=25GHz | 2.8GHz  | 4Gb/s, -21dBm     | [1.26 |

| 1990          | 短波長 | MSM/MESFET | (d) |        | ft=40GHz             | 4.6GHz  |                   | [1,27 |

| 1991          | 長波長 | MSM/HFET   | (a) |        | ft=30GH              | 2GHz    | 2Gh/s             | [1.28 |

| 1991          | 長波長 | pin/HBT    | (a) | 8GHz   | fr=32GHz, fmax=28GHz | 3.8GHz  | 5Gb/s, -18.8dBm   | (1.29 |

| 1991          | 長波長 | MSM/HFET   | (b) |        | fr=15GHz             |         | 1.2Gb/s, -25dBm   | 11.30 |

| 1991          | 長波長 | pin/HFET   | (c) |        | fr=72GHz, fmax=80GHz | 6.5GHz  |                   | [1.31 |

| 1991          | 短波長 | pin/HBT    | (f) |        | fr=60GHz             | 13GHz   |                   | [1.32 |

| 1991          | 短波長 | MSM/MESFET | (e) | 9GHz   | fr=60GHz             | 6.5GHz  |                   | [1.33 |

| 1991          | 短波長 | MSM/HFET   | (e) |        | fr=35GHz             | 8.2GHz  | 10Gb/s            | [1.34 |

| 1992          | 長波長 | pin/HFET   | (a) |        | ft=25GHz             | 8GHz    | 10Gb/s            | 11.35 |

| 1992          | 長波長 | pin/HFET   | (c) | 1.7GHz | fr=24GHz, fmax=51GHz | 1GHz    | 1Gb/s, -29.6dBm   | [1.36 |

| 1992          | 長波長 | pin/JFET   | (a) |        | ft=8GHz              | 1.65GHz | 2.4Gb/s, -29.5dBm | 11.37 |

| 1992          | 長波長 | pin/HBT    | (a) |        | fT=71GHz, fmax=43GHz | 6GHz    | 10Gb/s, -15.5dBm  | [1.38 |

| 1992          | 短波長 | MSM/HFET   | (e) |        | fr=66GHz, fmax=70GHz | 4.4GHz  |                   | [1,39 |

| 1993          | 短波長 | MSM/MESFET | (d) |        | fr=34GHz             | 11GHz   |                   | [1.40 |

| 1993          | 短波長 | MSM/HFET   | (c) |        | ft=50GHz             | 14,3GHz |                   | 11.41 |

注) 層(a)-(f)は図 1.6 の(a)-(f)に対応。

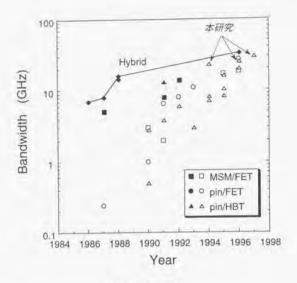

図 1.5 集積化受光回路の 3dB 帯域の年代推移 白印長波長、黒印:短波長 比較のためにハイブリッド受光回路の帯域も示した[1.42]。

図 1.6 集積化受光回路のデバイス構造の分類 (a)-(f)の記号は表1.1 の記号と対応している。

に分けることができる。(a) は一回の成長で両デバイスのエピタキシャル層を形成し、不要な部分を除去するものである。この構成では表面の段差が大きく微細配線の形成で不利になる。(b) は(a) の段差の問題を解決するため、予め基板にリセスを形成した後エピタキシャル層を成長するものである。(c) は一方のデバイスのエピタキシャル層を成長し不要部分を除去した後、他方のデバイスのエピタキシャル層を再成長するものである。(d) と (e) は半絶縁性基板上に MSM-PD を形成するもの、(f) は HBT のベースーコレクタを pin-PD と兼用するというように受光デバイスと電子デバイスを同一のエピタキシャル層構造で作製するものである。(a)-(c)の構成は受光デバイスと電子デバイスを目一のエピタキシャル層構造で作製するものであり、集積化受光回路専用の製造工程が必要となる。これに対して、(d)-(f)の構成は電子デバイスの製造工程で実現できるという特徴

を持っている。表1.1と図1.5から、受光感度の点では(a)-(c)の構成が優れ、帯域の点では(d)-(f)の構成が優れていると言える。その理由は、(a)-(c)では電子デバイス専用の製造と比較して、結晶品質が劣ることとFETのゲート長の微細化レベルが低いことに起因して集積化受光回路を構成する電子デバイスの性能が劣ること、一方、(d)-(f)では元々高性能な電子デバイスを用いるため高い帯域が得られるが、その反面PDの量子効率が低くなることである。図1.5からも明らかなように、集積化受光回路は潜在能力を有しているものの、その速度性能はハイブリッド受光回路の性能[1.42]よりも劣っている。また、長波長系受信OEICは受光デバイスと増幅器の集積化に留まっている。これに対して短波長系では、GaAs MESFET製造工程によりMSM-PDを集積化した1kゲート規模の受信OEIC[1.43]が報告されている。すなわち、高速化、高集積化を追究するには電子デバイスの製造工程で実現できるOEICが望ましいと言える。

受光OEICに使用される MSM-PDの研究は、試料の作製と評価という実験的手法が今まで主と して採られてきた。しかしながら、実験的手法は時間や費用がかかるという問題がある。理論解 析により予測を立て、実験の項目を絞り込むことにより研究の効率化を図ることができる。この ことに留まらず理論解析は、デバイス内部のキャリアや電界の挙動を把握でき物理現象の理解に 役立つという重要な側面を持っている。本研究以前に提案されている理論解析手法として、解析 的な電流式を用いるもの[1.44][1.45]、一定電界の近似のもとでドリフトと拡散近似の電流連続式 を数値計算するもの[1.46]、ボアソン方程式と電流連続式を数値計算する(流体モデルと呼ばれて いる)もの[1.47]、ボアソン方程式とボルツマン方程式を数値計算する(粒子モデルと呼ばれてい る)もの[1.48]、シェレディンガー方程式を数値計算するもの[1.49]が挙げられる。これらは、GaAs MSM-PDを一次元空間で取り扱ったものである。しかしながら、MSM-PDの解析は二次元空間で 取り扱う必要がある。このため、二次元ラプラス方程式を等角写像により一次元に変換して求め た電界分布をもとにドリフト項のみ考慮した電流連続式を解く方法が提案され、長波長系の InGaAs MSM-PD の解析が行われている[1.50]。InGaAs MSM-PD においては暗電流を低減するた めに、InGaAs 光吸収層と電極金属間に障壁を高めるための半導体層(障壁増強層)を挿入する方 法が一般的に採用されるが、上記の解析では障壁増強層が考慮されていない。この障壁増強層は InGaAs MSM-PD の高速化に極めて重要な影響を及ぼすが、体系的な設計法は明確にされていな

最後に、受信回路の設計ツールについて述べる。受信回路の設計はSPICEに代表される電子回路シミュレータを用いた小信号周波数応答解析および大信号過渡解析により行われてきた。受光感度は受光デバイスの寄生容量を含めた前置増幅器の小信号雑音解析結果と受光デバイスの量子効率から推定されている[1.51]。しかしながら、受光感度はE/O変換で生ずる波長チャーピングと光ファイバの波長分散に起因する波形歪とデバイス雑音を考慮する必要があり、厳密な回路シミュレータは開発されていない。抵抗、容量、インダクタンス、電流源を用いて半導体レーザの

レート方程式を等価回路表現しSPICEによりシミュレートする方法が提案されているが[1.52]、光 伝送系を厳密に設計するためには、発光デバイス、光ファイバ、受光デバイスおよび電子デバイ スを扱え、かつ時間領域雑音を考慮した汎用的な光電子混在回路シミュレータが必要である。

#### 1.3 研究の目的と課題

以上のような背景に立って本研究は、光通信用中間中継装置および端局装置のフロントエンド に使用される受信回路について、商用化されている受信回路と比較して2-3桁の低エネルギー 化を実現するために必要なデバイスおよび回路構成を明らかにすることを目的とする。この目的 を達成するために解決すべき課題を整理すると以下のようになる。

- (I) 光通信用受光デバイスとして有望な MSM-PD の理論解析は十分に確立されておらず、高速化 に対するデバイス設計指針あるいは速度性能限界についての予測は必ずしも明確とはなっていない。

- (2) 10 Gbit/s を越える周波数領域において、集積回路チップのみならず、バッケージ実装に付随する寄生容量および寄生インダクタンスの影響をも考慮した高利得、広帯域増幅器モジュール設計法を明らかにする必要がある。

- (3)電子回路の動作速度とデバイス性能の関係を明らかにする手法として、デバイスの等価回路 パラメータを変化させて回路シミュレーションを行うというアプローチ (感度解析) が採られて きた。しかしながら、これらのパラメータの間には相関があり、相関まで厳密に押えて議論する ことはかなり困難であり、見通しの良いものではない。このため、電子回路の動作速度限界がど こにあるのかという、将来の通信ネットワークを考える上で重要な問題に対する答えが必ずしも 明確ではない。

- (4) 光伝送システム設計において重要な設計項目である光デバイスの波長チャーピングと光ファイバの波長分散に伴う伝送波形歪およびデバイス雑音を考慮した時間領域大信号解析手法は提案されていない。将来の光ネットワークを詳細に設計するために、より汎用的なツールを提供する必要がある。

- (5) 受信系OEICは受光デバイスと前置増幅器の集積化に留まり、その性能もハイブリッド回路の

性能より劣っている。超高速領域では寄生効果によりハイブリッド回路の性能向上が飽和する可能性があり、何らかのブレークスルーによりOEICの速度性能を飛躍的に向上させる必要がある。

#### 1.4 本論文の構成

上記課題を解決するために本研究では「受光デバイスも含めた受信回路をモノリシック集積化することにより、その高速化、低消費電力化を達成する」という基本アプローチを探ることとする。その理由は、光ファイバ増幅器の発展により受信感度に対する要求が緩和されており高速化の観点から電子デバイス製造工程に整合した受信OEICが優れていること、従来の化合物半導体高速集積回路の低エネルギー化を制限している最大の要因は低インピーダンスのチップ間インターフェースにあると考えられること、である。

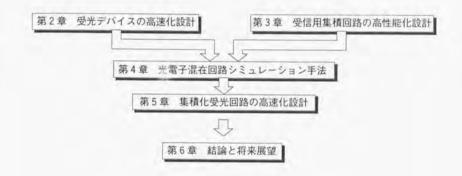

本論文は以下の6章で構成されている。

- 第1章 序論

- 第2章 受光デバイスの高速化設計

- 第3章 受信用集積回路の高性能化設計

- 第4章 光電子混在回路シミュレーション手法

- 第5章 集積化受光回路の高速化設計

- 第6章 結論と将来展望

第2章では、電子デバイス製造工程との整合性が比較的良いMSM-PDの高速化デバイス設計について主に理論解析をもとに議論する。対象とする時間精度に応じた流体モデルと粒子モデルの2つの手法に基づく数値計算プログラムを作成し、MSM-PDの動作機構の把握を行うとともに高速化のためのデバイス構造を示す。また、0.25 μm 程度に微細化された MSM-PDの性能予測を行う。

第3章では、受信回路のうち電子デバイスにより構成される集積回路の高性能化について議論 する。まず、10 Gbit/s 増幅器モジュールを実現するために、パッケージ実装に付随する寄生容量 および寄生インダクタンスを考慮に入れた安定性解析に基づく増幅回路とパッケージの一括設計 法を明らかにする。次に、10 Gbit/s 以上の高速化を目指して、受信回路の基本要素であるベース バンド増幅器および識別器の動作速度とデバイス性能(電流利得遮断周波数と最大発振周波数)との関係を明確化する。これらの結果をもとに、商用化されている受信回路と比較して2-3桁低エネルギーな受信回路の実現を目指すためにはモノリシック集積化が必要であることを指摘する。さらに、高速化、低電力化に適したInP/InGaAs ダブルヘテロ接合バイボーラトランジスタを用いて、前置増幅器、自動オフセット調整回路、後置増幅器、位相同期ループによるタイミング抽出回路、識別器から構成された3R機能回路を試作し、2.4 Gbit/s バイブリッド型3R機能回路と比較して約2桁の低エネルギー化が可能であることを示す。

第4章では、光デバイスと電子デバイスが混在する回路を詳細に設計するためのツール開発を 目的として光電子混在回路シミュレーション手法について議論する。能動デバイスおよび抵抗に 時間領域雑音源を導入し、光ファイバ等のモデルとともに市販の混合モードシミュレータにイン プリメントする。実験とシミュレーションとの比較によりシミュレーション手法の妥当性を検証 する。

第5章では、InP/InGaAs HBT製造工程で作製できる長波長 pin-PD/HBT構成の集積化受光回路の研究を行う。最初に、InP/InGaAs シングルヘテロ接合バイポーラトランジスタ(SHBT: Single-Heterojunction Bipolar Transistor)のベースーコレクタ層を利用したpin-PDとSHBTによる前置増幅器から成る集積化受光回路の課題を指摘する。次に、この課題を解決するためにダブルヘテロ接合化した構造を提案し、その高速性を示すとともに、集積化受光回路の動作速度を最大にする最適なコレクタ層の厚さを明確化する。最後に、最適設計された集積化受光回路により 40 Gbit/s 動作の可能性を示す。

第6章では、本研究で得られた成果と到達点ならびに超高速集積回路に関する最近の成果を踏まえて、さらなる低エネルギー化ための展望を述べる。

各章間の関係を図1.7に示す。

図 1.7 本論文の構成

## 第2章

## 受光デバイスの高速化設計

#### 概要

金属一半導体ー金属フォトディテクタ(MSM-PD: <u>Metal-Semicondoctor-Metal Photodetector</u>)は集 積化受光回路用デバイスとして注目されている。これまでのMSM-PDに関する研究は実験的手法 が主体であり、厳密な理論解析は行われていなかった。

本章では理論解析によりMSM-PDの高速化設計を行う。最初に、二次元ポアソン方程式とドリフトと拡散近似の電流連続式を数値計算すること(流体モデル)によりGaAs MSM-PDを解析し電界とキャリアの挙動を把握する。解析結果から、光通信で使用される弱励起状態においてはポアソン方程式と電流連続式を自己無撞着に解く必要がないことを明らかにする。この結果を反映して次に、モンテカルロ法を用いてボルツマン方程式を数値計算すること(粒子モデル)によりGaAs およびInGaAs MSM-PDの高速化に適したデバイス構造を示す。最後に、InGaAs MSM-PDの電極間隔をクォータミクロンにすることにより50 GHz を越える帯域が期待できることを示す。

#### 2.1 はじめに

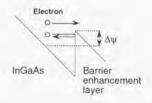

第1章の表1.1に示したように、今までに報告されている集積化受光回路にはMSM-PDとpin-PDが用いられている。MSM-PDは、製造方法が簡単である、電極間容量が小さく高速化に有利 である、等の特徴を有している[2.1]。短波長系のGaAs MSM-PDは半絶縁性GaAs 基板上にショッ トキー電極をパターニングするだけで実現できるため、MSM-PDの電極をMESFETのゲート電極 と同一材料にすれば MESFET の製造工程を何ら変更することなく集積化受光回路を作製できる [2.2]。一方、長距離光通信用の長波長系MSM-PDの光吸収層はアンドープInGaAsで構成される。 MSM-PD用材料としてのInGaAsの最大の欠点は、金属-InGaAsのショットキー障壁がInP整合 系で 0.2 eV 程度[2.3]と低いため、暗電流が大きく高感度化の妨げになることである。この問題を 解決する手段として、InGaAs 光吸収層と電極金属間に障壁を高めるための半導体層(障壁増強層 と呼ぶこととする)を挿入する方法が提案されている。障壁増強層としては、歪 GaAs[2.4]、 Al<sub>a</sub>, Ga<sub>a</sub>, As[2.5]、In<sub>ac</sub>, Al<sub>a</sub>, As[2.6]、鉄ドープInP[2.7]等が用いられている。当然のことながら障壁 増強層とInGaAs層とはヘテロ接合を形成するため、光照射により発生したキャリアがヘテロ接合 界面に蓄積されることが予測される。この課題を解決するために、InGaAsから障壁増強層の材料 に連続的に組成を変化させる[2.8][2.9]、あるいはInGaAsと障壁増強層の材料から成る超格子構造 で厚さの比を変化させること[2,10]により、キャリアの蓄積を防ぐ方法が提案されている。InGaAs MSM-PDは以上のような構造を有するため InP系電子デバイスと同一層構成とはならないが、す べての層が高抵抗であるため電子デバイスと縦積みにしても電子デバイスへの影響は少ない。

MSM-PDの動作速度は、光照射により発生したキャリアが再結合あるいは電極への走行により 半導体中から消滅するまでの時間と、電極間容量と負荷抵抗の積で与えられる時定数とにより決 定される[2.11]。通常のMSM-PDにおいては、前者の方が後者より大きい。したがって、MSM-PD の高速化の方法は、いかに速くキャリアを消滅させるかという課題を解決することである。MSM-PDの高速化に関する研究を概観すると、当初は集積化受光回路応用よりもむしろ、双方向性を活 かした光導電サンプリング[2.12]-[2.14]あるいは光入力論理回路[2.15]-[2.17]応用を目指した高速化 研究から始まっている。そこで採られた手法は不純物の導入[2.18]-[2.22]あるいは低温結晶成長 [2.23]により再結合中心密度を増大させキャリア寿命を短くする方法であった。しかしながら、こ れらの方法により作製されたMSM-PDは量子効率あるいは安定性に関して課題がある。集積化受 光回路応用には電極間隔の短縮によりキャリア走行時間を短縮する方法が適している。電極間隔 が 0.5 μm の GaAs MSM-PD により 105 GHz の帯域が得られている[2.24]が、InGaAs MSM-PD の 高速化は遅れている。

以上の研究は実験的手法に基づくものである。一方、本研究以前に提案されている理論解析手法として、解析的な電流式を用いるもの[2.25][2.26]、一定電界近似のもとにドリフトと拡散近似

の電流連続式を数値計算するもの[2.27]、ポアソン方程式と電流連続式を数値計算するもの(流体モデル)[2.28]、ポアソン方程式とポルツマン方程式を数値計算するもの(粒子モデル)[2.29]、シュレディンガー方程式を数値計算するもの[2.30]が挙げられる。これらは、GaAs MSM-PDを一次元空間で取り扱ったものである。しかしながら、MSM-PDの解析は二次元空間で取り扱う必要がある。InGaAs MSM-PDの解析に関して、二次元ラプラス方程式を等角写像により一次元に変換して求めた電界分布をもとにドリフト項のみ考慮した電流連続式を解く方法が提案されている[2.31]が、高速化に極めて重要な影響を及ぼす障壁増強層が考慮されていない。

本章では、流体モデルと粒子モデルの2つの手法に基づく数値計算プログラムを作成し、MSM-PDの動作機構の把握を行うとともに高速化のためのデバイス構造を示す。さらに、0.25 μm 程度 に微細化された MSM-PD の性能予測を行う。

このため2.2では対象とする時間スケールおよび物理サイズと適用すべき基本方程式との関係を整理する。2.3 では構造が簡単な GaAs MSM-PD を解析対象として二次元ポアソン方程式と流体モデルに基づく電流連続式を数値計算することにより電界およびキャリアの基本的な振る舞いを把握する。2.4 では粒子モデルを用いてサブミクロン電極間隔と障壁増強層を有する MSM-PD を解析し高速化のためのデバイス構造の明確化と性能予測を行う。

#### 2.2 基本方程式

#### 2.2.1 電磁界の挙動

電磁界の挙動は次のマクスウェル方程式で記述される。

$$\nabla \times \mathbf{E} = -\frac{\partial \mathbf{B}}{\partial t} \tag{2.1}$$

$$\nabla \times \mathbf{H} = \mathbf{J} + \frac{\partial \mathbf{D}}{\partial t}$$

(2.2)

$$\nabla \cdot \mathbf{D} = \rho \tag{2.3}$$

$$\nabla \cdot \mathbf{B} = 0 \tag{2.4}$$

ここで、E は電界、B は磁束密度、H は磁界、D は電束密度、J は電流密度、p は電荷密度である。式(2.2)と式(2.3)から電流連続の関係

$$\nabla \cdot \mathbf{J} + \frac{\partial \rho}{\partial t} = 0 \tag{2.5}$$

が成り立っていることがわかる。式(2.4)は式(2.1)から導けるため、電流密度と電荷密度が与えられたとしても、式(2.1)-(2.4)を解くことはできない。このため、次の構成方程式を必要とする。

$$\mathbf{D} = \varepsilon \mathbf{E} \tag{2.6}$$

$$\mathbf{B} = \mu \mathbf{H} \tag{2.7}$$

$\varepsilon$ は誘電率、 $\mu$ は透磁率である。ここで、ベクトルポテンシャル A とスカラーポテンシャル  $\psi$ を導入し、ポテンシャルの任意性を拘束するゲージとしてローレンツゲージを用いる。

今、解析対象とする空間を電磁界が伝搬する時間が解析対象とする時間に対して充分短ければ、 その時刻での電流密度および電荷密度でスカラーボテンシャルが決ることになる。この時、次の ポアソン方程式が得られる。(付録 A.1.1)

$$\nabla^2 \psi = -\frac{\rho}{\varepsilon} \tag{2.8}$$

ささは.

$$E = -\nabla \psi$$

(2.9)

である。例えば、MSM-PDの電極間隔が  $1 \mu m$  の場合、この距離を電磁界が伝搬する時間は波長 短縮を考慮して 10 fs 程度である。したがって、MSM-PD 内部の電界の挙動を 0.1 ps 程度の時間 スケールで議論する場合にはポアソン方程式を解けば充分であると言える。

#### 2.2.2 キャリアの挙動

電子を単一の粒子と看做して半古典的に扱うと、電子の挙動は次のポルツマンの輸送方程式により記述できる。

$$\frac{df}{dt} + \frac{q\mathbf{E}}{h} \cdot \nabla_{\mathbf{k}} f + \mathbf{v} \cdot \nabla_{\mathbf{r}} f = \left[ \frac{\partial f}{\partial t} \right]$$

(2.10)

ここで、f は波数ペクトル k、位置 f、時刻 f に依存する電子の分布関数、f は電子の速度、f は素電荷、f はブランク定数f2fである。左辺の第二項は電界により波数ペクトルが変化することに伴う分布関数の変化を表し、ドリフト項と呼ばれるものである。第三項は電子の位置の変化を通じて分布関数が変化する拡散項と呼ばれるものである。また、右辺は散乱による分布関数の変化である。

ここで、(1) 散乱過程に緩和時間を導入、(2) 電界の変化する時間スケールは緩和時間と比較して 長い、(3) 等方的な放物型のバンド、(4) 分布関数の熱平衡からのずれは非常に小さい、ことを仮定 すると、次のドリフト拡散近似の電流密度式が得られる。(付録A.1.2)

$$\mathbf{J}_{n} = q\mu_{n} \mathbf{n} \mathbf{E} + q D_{n} \nabla_{\mathbf{r}} n \tag{2.11}$$

$$\mathbf{J}_{p} = q\mu_{p}\rho \mathbf{E} - qD_{p}\nabla_{e}p \qquad (2.12)$$

ここで、 $\mu_n$ と $\mu_n$ は各々電子と正孔のドリフト移動度、 $D_n$ と $D_p$ は各々電子と正孔の拡散係数、nとpは各々電子と正孔の密度である。

キャリアの振舞を把握するためには、ボルツマンの輸送方程式(2.10)を解く方法(粒子モデル)あるいは式(2.11)と式(2.12)を用いて電流連続の式(2.5)を解く方法(流体モデル)が採用される。ここで上記(2)の仮定について考察すると、電子の平均的な緩和時間<→は次式より概算できる。

$$\mu_n = \frac{q}{m_e} \langle \tau \rangle$$

(2.13)

ここで、m, は電子の有効質量である。GaAs の場合、ドリフト移動度を  $5000~cm^2/Vs$  とすれば平均的な緩和時間は 0.19~ps となる。正孔については、これより 1 桁程度小さい値となる。大雑把に言えば、数ピコ秒以下のスケールを問題とする場合には粒子モデルを用いる必要がある。また、流体モデルでは上記(4)の仮定がなされているから、キャリア運動へのボテンシャル障壁の影響等は解析できない。

以上のように、マクスウェル方程式を用いて電磁界を動的に扱うのか、ボアソン方程式を用いて静電ボテンシャルとして扱うのか、キャリアに関して、粒子モデルを適用するのか、流体モデルを適用するのか四通りの組み合わせが考えられる訳である。いずれを選択するのかは対象とする時間スケールに依存する。解析の特度はアナログ的であるから明確な線引きは難しいのであるが、電磁界については物理サイズを電磁界の速度で割った時間が、キャリアについては電子の緩和時間が目安となる。

ここでは、電界およびキャリアの基本的な振る舞いを把握するためにボアソン方程式と流体モ

デルによる GaAs MSM-PD の解析から始めることにする。

## 2.3 流体モデルを用いた GaAs MSM-PD の基本動作解析[2.62]

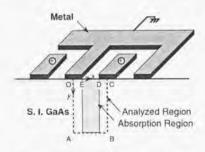

GaAs MSM-PDの概略構造を図2.1に示す。広がった光ビームに対しても良好な外部量子効率が得られるように櫛歯を入れ子にした電極バターンとすることが多い。表面に対して垂直な面内の単位領域OABCでポアソン方程式と電流連続式を解くこととする。

空間電荷として、キャリア、イオン化した不純物 $(N_p,N_A)$ 、帯電した再結合中心 $(N_r)$ を考慮し、 光照射によるキャリアの発生 $(G_n,G_p)$ 、再結合中心を介した生成再結合、発光再結合、オージェ 再結合の過程を含む再結合 $(R_n,R_p)$ を考慮すると、ポアソン方程式(2.8)と電流連続式(2.5)は次のように表される。

$$\varepsilon \nabla^2 \psi = -q(p-n+N_D-N_A+N_T^+) \qquad (2.14)$$

$$\nabla \cdot \mathbf{J}_{n} - q \frac{\partial n}{\partial t} = q(R_{n} - G_{n})$$

(2.15a)

$$\nabla \cdot \mathbf{J}_{p} + q \frac{\partial p}{\partial t} = q(G_{p} - R_{p})$$

(2.15b)

$$\mathbf{J}_{n} = -q\mu_{n} n \nabla \psi + q D_{n} \nabla n \qquad (2.16a)$$

$$\mathbf{J}_{p} = -q\mu_{p}\rho\nabla\psi - qD_{p}\nabla\rho \tag{2.16b}$$

キャリアの生成再結合および光照射による発生モデルを付録A.1.3に示す。

図 2.1 GaAs MSM-PD のデバイス構造モデル

ボアソン方程式および電流連続式の境界条件として、電極との界面(OEとCD)ではショットキー 障壁を考慮したディリクレ(Dirichlet)型境界条件と熱電子放出モデル[2.33]を、GaAs表面(DE)と解析領域の側面(OAとBC)ではノイマン(Neumann)型境界条件を、解析領域の下面(AB)では電荷中性 条件を適用する。これらの境界条件のもとで式(2.14)-(2.16b)を解くこととなるが、これらは非線 形の連立微分方程式であるから解析的に解くことはできない。そこで、ポテンシャルの初期値を 仮定し、式(2.15a)-(2.16b)(A19)-(A26b)を解き、得られたキャリア密度と帯電している再結合中心 密度を式(2.14)に代入して解くという繰り返し計算の手法を用いる。また、各々の微分方程式を差 分方程式に変形し数値計算を行う。本解析では一般的に使われている数値計算上の取り扱いをしており、具体的な手順については成書[2.37]を参考にされたい。

計算に用いたパラメータの値を付表 A1(付録 A.2)に示す。移動度に関するパラメータは、式 (A25a)-(A26b)による計算値が文献[2.38]の実測値と一致するように決めている。再結合中心に関するパラメータは文献[2.35]と、その他のパラメータ値は文献[2.39][2.40]と同一である。

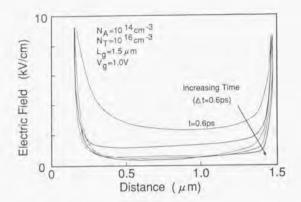

電極間隔 L が 1.5 µm の GaAs MSM-PD の解析を行った。波長 600 nm、半値全幅(FWHM: Full Width at Half Maximum) 0.3 ps 、エネルギー 1 pJ/pulse、 時刻 0.5 ps でピークとなるガウス分布型 光パルスを照射するものとした。GaAs基板表面での横方向電界強度分布の時間変化を図2.2に示 す。ここで、横軸はカソード電極の端(図2.1の点目からの距離である。時間とともに電界強度が 低下して行くことがわかる。この理由は以下の通りである。光照射により発生した電子と正孔は 各々アノード電極とカソード電極の方向に動く。このため、電極近傍に空間電荷領域が形成され、 この影響で電極間の電界強度が低下する[2.41]。空間電荷が形成される様子を図2.3に示す。縦軸 はアノード電極とカソード電極の下の領域で積分したキャリア面密度である。電子速度の方が正 孔速度より速いため、アノード電極下の方が早く空間電荷が形成される。空間電荷形成に伴う電 界強度の低下により、流体モデルを用いた解析により得られるMSM-PDのコンダクタンスは従来 の解析的モデル[2.25]で計算したコンダクタンスより小さくなった。種々の光パワーについて解析 した結果、発生するキャリア密度が 100cm3 を越える場合には、空間電荷形成に伴う電界強度低 下の効果を無視できないことがわかった。上記の解析ではキャリア密度はほぼ 2.7 x 1016 cm3 で あった。光通信へMSM-PDを適用する場合、平均光パワーは 0.1 mW 以下であり、上記解析と比 較して5桁程度小さいものである。この場合には空間電荷形成に伴う電界強度低下の効果を無視 できると考えて良い。ここでは GaAs MSM-PD について解析したが、InGaAs MSM-PD において も同様のことが言えると考える。

図 2.2 表面における横方向電界強度分布

図2.3 電極下のキャリア面密度の変化

## 2.4 粒子モデルを用いた MSM-PD の高速化設計[2.63][2.64]

流体モデルより厳密にキャリアの挙動を議論するためには、ボルツマンの輸送方程式(2.10)を解く必要がある。一般的には、ボルツマンの輸送方程式を解析的に解くことはできず、数値計算により解くこととなる。今までに提案されている数値計算手法の中で最も成功している手法はモンテカル口法である。電子あるいは正孔が散乱なしでどの程度の時間だけ運動するのか、種々の散乱機構のうちどの散乱を受けるのかということは確率過程である。確率過程をシミュレートするために乱数を導入するのがモンテカル口法である。本研究で用いた計算手順は従来のものと同様であるため、具体的手順は文献[2.42]あるいは成書[2.37]に譲るものとし、ここでは本解析に特徴的な仮定およびモデルについて述べる。

前節で明らかとなったように、MSM-PDを光通信用受光デバイスに適用する場合には発生したキャリアによるボテンシャルの変化は無視できるほど小さいものである。このため、GaAs MSM-PDの解析においては式(2.15a)(2.15b)(A19)の時間微分項と発生率をゼロとした方程式とボアソン方程式(2.14)を解くことにより得られるボテンシャルを用いて、InGaAs MSM-PDの解析においては更に簡単化のためラブラス方程式を解くことにより得られるボテンシャルを用いて、ボルツマンの輸送方程式を解くこととする。注1)

バンドモデルとして、伝導帯については $\Gamma$ -L-Xパレーを考慮し、価電子帯については軽い正孔パンドと重い正孔パンドを考慮した。光子エネルギーの吸収により軽い正孔パンドと重い正孔パンドから等確率で $\Gamma$ パレーに電子が励起されるものとする。光パルスが時刻 $I_0$  でピーク値を取る分散 $I_0$  を有するガウス分布型であると仮定すると、単位時間の電子と正孔の発生率は次式により与えられる[2.43]。

$$g(t) = \frac{N_{total}}{\sigma_t \sqrt{\pi}} \exp\left[-\frac{\left(t - t_0\right)^2}{\sigma_t^2}\right]$$

(2.17)

ここで、 $N_{mail}$  は厳密には光パルス照射により発生する全キャリア数であるが、個々のキャリアの運動をシミュレートすることは計算時間の制約で不可能である。そこで、アンサンブルモンテカルロ解析ではいくつかのキャリアが一纏まりで同一の散乱過程を経るものとして扱う。本解析ではボアソン方程式を自己無撞着的に解かないので、一固まりのキャリア数には任意性がある。統計学上 $N_{lmail}$  は大きい程、計算精度は向上するが、ここでは 20000 としている。エネルギー保存則 [2.44]と不確定性原理[2.43]を考慮すると、発生した電子と正孔の持つ初期エネルギーは各々

$$E_{ci} = \frac{-(1+r) + \sqrt{(1+r)^2 + 4r\alpha(hv - E_k)}}{2r\alpha} + \frac{hr_i}{FWHM}$$

(2.18)

$$E_{vi} = (hv - E_{g_i}) - E_{ci}$$

(2.19)

で与えられる。ただし、

$$r = \frac{m_c}{m_o} \tag{2.20}$$

ここで、 $E_g$ はパンドギャップエネルギー、 $m_g$ は電子の有効質量、 $m_g$ は正孔の有効質量、 $\alpha$ はパンドの非等方性を表すパラメータ、FWHMは光パルスの半値全幅、 $r_g$ は正規乱数である。図2.1に示したデバイス構造モデルと同様にDEから下の領域で光が吸収されるものとし、簡単化のため光パワーはx方向に一様であるものとする。発生するキャリアの初期座標値は

$$x_i = \frac{L_k}{2} + r_2 L_k \tag{2.21}$$

$$y_i = -\frac{\ln(1 - r_3)}{\alpha_{abr}}$$

(2.22)

で与えられる。ここで、 $L_{p}$  は MSM-PD の電極間隔、 $\alpha_{ab}$  は光の吸収係数、 $r_{1}$  と $r_{2}$  は区間  $\{0,1\}$  の一様乱数である。以上の初期条件のもとにキャリアの運動をシミュレートする。

本解析で考慮した電子の散乱過程は、有極性光学フォノン散乱、無極性光学フォノン散乱、音響フォノン散乱、バレー内散乱、バレー問散乱である。また、正孔の散乱過程は有極性光学フォノン散乱、音響フォノン散乱、音響フォノン散乱である。各散乱の確率[2.42][2.45][2.46]を付録 A.1.4 と A.1.5 にまとめた。不純物濃度およびキャリア密度は低いため、不純物散乱およびキャリアーキャリア散乱を無視している。また、簡単化のために三元系化合物中の合金散乱も無視している。したがって、電子速度の計算値は実験値と比較して大きくなる可能性がある。解析に用いたパラメータ値[2.47]-[2.54]を付表 A2 から付表 A5 にまとめて示した。 $\ln_{0.52}Al_{0.48}As$  の電子親和力とバレー間エネルギー差は $\ln As$ の値[2.52][2.53]と $\ln As$ の値[2.54]を線形に内挿することにより決めている。また、 $\ln_{0.52}Al_{0.48}As$ のがレー間変形ポテンシャルとフォノンエネルギーは $\ln P$  と同一と仮定している。2.4.2において $\ln_{0.52}(Ga_1Al_1_1)_{0.47}As$ を扱うが、そのパラメータ値は $\ln_{0.52}Al_{0.48}As$ の値と $\ln_{0.52}Ga_{0.47}As$ の値を線形に内挿することにより決めている。 $\ln_{0.52}Ga_{0.47}As$ の位を線形に内挿することにより決めている。 $\ln_{0.52}Ga_{0.47}As$ の位を線形に内挿することにより決めている。 $\ln_{0.52}Ga_{0.47}As$ の位を線形に内挿することにより決めている。 $\ln_{0.52}Ga_{0.47}As$ の他を線形に内挿することにより決めている。 $\ln_{0.52}Ga_{0.47}As$ の他を解形に内挿することにより決めている。 $\ln_{0.52}Ga_{0.47}As$ のの光吸収係数は文献[2.55]の実調値を用いた。

本解析では簡単化のため、単位時間に電極に流入する電子と正孔の数を数えることにより導電

電流を求めている。このようにして計算した光電流パルスのパルス幅は変位電流より求めたパルス幅と比較して若干大きくなる可能性がある[2.31]。本節ではMSM-PDを集中定数回路と看做しており、上記の電流値を持つ電流源と電極間容量の並列回路としてモデル化する。電極幅と電極間隔が等しい時、電極間容量は近似的に次式で計算できる[2.56]。

$$C_g = L(\varepsilon_r + 1)[(N-3)A_1 + A_2]$$

(2.23)

ここで、Lはアノードとカソードの対向する長さ、 $\varepsilon$ , は基板の比誘電率、Nは電極フィンガーの本数、 $A_1$  = 88.6 fF/cm、 $A_2$  = 99.2 fF/cm である。この MSM-PD の等価回路に集中定数回路の負荷抵抗(特に断らない限り 50  $\Omega$ ) を接続し電圧パルス波形を求める。

#### 2.4.1 GaAs MSM-PD の設計

最初に本解析法の精度を明確にするために、Van Zeghbroeck et al. [2,24]の実験と同一条件で計算を行った。その結果、出力電圧バルスのパルス幅(FWHM)は6.0 ps となり、実験値の4.8 ps [2.24]に対して25%大きくなった。誤差の主要因は光電流を導電電流より求めていることにあると思われるが、この程度の誤差は議論を進めて行く上で大きな障害とならないものと考える。

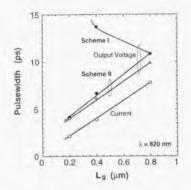

金属一酸化膜-半導体電界効果トランジスタ(MOSFET)の世界では、平均電界強度一定の条件、電圧一定の条件あるいは両者の折衷条件というそれぞれの条件のもとで、チャネル長、ゲート酸化膜厚、チャネル領域不純物濃度、接合深き等のパラメータをどのように変えてゆくべきかという指針となるスケーリング則が知られている。ここでは、MSM-PDに関するスケーリング則について考察してみる。デバイス耐圧の観点から平均電界強度一定の条件を置くこととし、表 2.1 に示す二つの場合を考える。Scheme I はデバイスサイズを変えずに電極間隔を微細化するもの、Scheme II は電極間隔の微細化とともにデバイスサイズも微細化するものである。電極間容量  $C_g$  は式(2.23)により計算している。各々の場合について、波長 820 nm、パルス幅 0.1 ps (FWHM)の光パルスを用いてシミュレーションを行った結果を図 2.4 に示す。Scheme I では微細化とともに電流パルスの幅は減少するものの  $C_g$  が増大するため出力電圧パルス幅は増大する。MSM-PD の高速化には容量の減少が不可欠であり[2.26][2.30]、Scheme II が適していると言える。このため、以下では Scheme II にもとづいて議論する。図 2.4 において、  $\bullet$  は電子と正孔の両電流成分を考慮した場合の出力電圧パルス幅、 $\Delta$  は電子電流のみを考慮した場合の出力電圧パルス幅である。これらの差は 10 % 以下であり、正孔電流は出力電圧パルス幅にあまり影響を与えない。しかしながら、後述するように正孔電流は長い裾引きの原因となり MSM-PD の帯域を決める要因となる。

表 2.1 解析に用いた MSM-PD のパラメータ

|                    | Scheme I |      |      | Scheme II |      |      |

|--------------------|----------|------|------|-----------|------|------|

| Lg (µm)            | 0.8      | 0.4  | 0.2  | 8.0       | 0.4  | 0.2  |

| L (µm)             | 40       | 40   | 40   | 40        | 40   | 40   |

| W (µm)             | 38.4     | 38.4 | 38.4 | 38.4      | 19.2 | 9.6  |

| $C_g$ (fF)         | 50       | 110  | 229  | 50        | 25   | 12.5 |

| V <sub>g</sub> (V) | 2.0      | 1.0  | 0.5  | 2.0       | 1.0  | 0.5  |

図2.4 MSM-PDの応答の L。依存性 ●:電子と正孔の両電流成分を考慮した場合 △:電子電流のみを考慮した場合

図 2.4 の電流パルス幅は次式で近似できる。

$$FWHM = \frac{L_g}{1.06 \times 10^7} + 0.26 ps \tag{2.24}$$

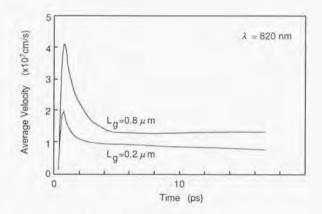

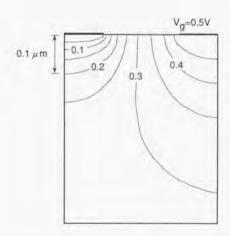

ここで、 $L_{\rm g}$  の単位はcmである。この近似式で注意すべき点は、電子の速度が 5 x  $10^{\rm h}$  cm/s であることを意味していないということである。波長 820 nm の時、光の吸収深さ( $1/\alpha_{\rm obs}$ )は約 0.8  $\mu$ m であるから、電子の平均走行距離が  $L_{\rm g}/2$  より長いためである。実際、図 2.5 に示すように平均電子速度にはオーバーシュート現象が見られる。 $L_{\rm g}=0.8$   $\mu$ m の MSM-PD における平均電子速度のビーク値は  $L_{\rm g}=0.2$   $\mu$ m の場合の 2 倍となっている。この差は電界強度の差に起因する。 $L_{\rm g}=0.2$   $\mu$ m の MSM-PD のポテンシャル分布を図 2.6 に示す。光の吸収深さの半分(0.4  $\mu$ m)の位置は図の下端付近であり、この領域の電界は弱いことがわかる。一方、 $L_{\rm g}=0.8$   $\mu$ m については示していないが、ほぼスケーリングされるから、 $L_{\rm g}=0.2$   $\mu$ m の場合の 0.1  $\mu$ m の深さに相当すると考えて良

い。 $L_{\rm g}$ =0.2  $\mu$ m の場合と比較して電界が強いことが図より明らかである。 $L_{\rm g}$ =0.8  $\mu$ m の場合、より強い電界により電子が加速される。以上の解析から、MSM-PD の電極間隔を微細化しても、光の吸収深さが一定であるため、微細化に比例してパルス幅が短縮化されるわけではないことが明確となった。

図 2.5 電子の平均速度の変化

図 2.6 L<sub>o</sub> = 0.2 μm の MSM-PD のポテンシャル分布

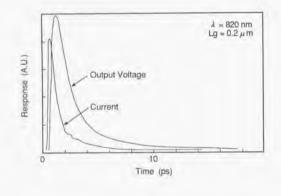

したがって、MSM-PDの高速化を図るためには、GaAs/AlGaAsへテロ接合の導入等により光吸収層を薄いGaAs層に限定する必要がある[2.57]。厳密にはGaAs/AlGaAsへテロ接合を解析する必要があるが、ここでは近似的に  $0 < y < 0.2 \ \mu m$  の領域でのみ光が吸収されるものとして解析を行った。この時の MSM-PD の応答を図  $2.7 \ \iota \pi$  す。出力電圧パルスの半値全幅は  $2.2 \ ps$  であり、図  $2.4 \ \iota t$  散すると約半分になっている。電極間隔の微細化と同時に光吸収層を薄層化することが MSM-PD の高速化に有効である。図  $2.7 \ \iota \pi$  の電流応答において、 $2 \ ps$  までのパルスは電子電流が支配的であり、これに続く裾引きは正孔電流が支配的である。電子電流のみを考慮した電圧パルスをアーリエ変換することにより求めた  $3 \ \iota t$  借助は  $1.78 \ \iota t$  GHz であった。一方、電子および正孔電流を考慮した場合の  $3 \ \iota t$  器 GHz であった。MSM-PD をさらに高速化するためには、速度の遅い正孔をいかに早く消滅させるかが鍵となる。

図 2.7 光吸収層が 0.2 µm の場合の MSM-PD の応答

#### 2.4.2 InGaAs MSM-PD の解析

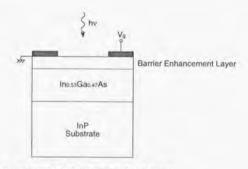

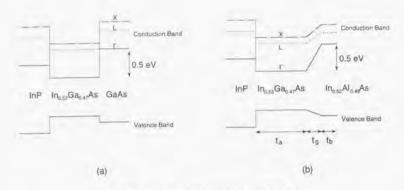

2.1で述べたように、長波長受光デバイスとして有望な InGaAs MSM-PDにおいては、暗電流を低減させるため障壁増大層がInGaAs光吸収層と電極との間に挿入されるのが一般的である。そこで、図 2.8 に示すように MSM-PD の構造をモデル化する。障壁増大層は GaAs、 $In_{ass}Al_{ass}$ As、 $In_{ass}$  ( $Ga_sAl_{1,s}$ ) $_{0.47}$ As傾斜層/ $In_{0.52}Al_{0.48}$ Asとした。ヘテロ接合におけるキャリアの輸送モデル[2.51]を図 2.9 に示す。すなわち、フリーフライト前にキャリアが存在する位置におけるボテンシャルとヘテロ接合におけるボテンシャルの差  $\Delta \psi$  よりもキャリアの持つエネルギーが大きければキャリアはヘテロ接合を通過し、小さければ鏡面反射するものとする。ここでは、ヘテロ接合におけるトンネル電流は考慮していない。付表A2から付表A5(付録A.2)をもとに描いたフラットバンド状態でのバンドモデルを図 2.10 に示す。ここで、 $t_s$  は光吸収層の厚さ、 $t_b$  は障壁増大層の厚さ、 $t_s$  は傾斜層の厚さである。GaAs 障壁増大層は本来 InP と格子整合しない歪み GaAs であるが、計算の簡単化のためバルク GaAsのバンドモデルを用いた。 $In_{ass}Ga_{n47}$ As/ $In_{0.52}$ Al $_{0.48}$ Asへテロ接合は図 2.10(b)の傾斜層の厚さ  $t_s$  = 0 に相当する。

図 2.8 InGaAs MSM-PD のデバイス構造モデル

図2.9 ヘテロ接合におけるキャリア輸送モデル

図 2.10 フラットバンド状態のバンド構造モデル

最初に、Schumacher et al. [2.4]の実験との比較を行う。彼らが実験に用いたMSM-PDの構造パラメータは、 $L_y=2~\mu m$ 、 $t_x=1.5~\mu m$ 、 $t_x=30~n m$  (GaAs)である。また、測定系の時間精度を考慮し、 $Z_0C_x=20.4~p s$  (= 40 ps (FWHM)/ $2\pi \times 0.312$ )とした。出力電圧がピーク値の 90 % から 10 % になるまでの時間で定義した立ち下がり時間の電極間電圧  $V_x$  依存性を図 2.11 に示す。図の〇は障壁増大層がある場合の計算値、 $\bullet$  は障壁増大層がない場合の計算値、 $\triangle$ は実験値[2.4]である。電圧が低くなるとキャリア速度が小さくなり立ち下がり時間が増大する。これに加えて、障壁増大層の存在によりさらに立ち下がり時間が増大する。実験と計算は定性的には良く一致していると言える。障壁増大層がある場合の光吸収層内のキャリア数の変化を図 2.12 に示す。正孔についてはポテンシャル障壁が低いため時間とともに数が減少してゆく。ポテンシャル障壁が 0.58 eV と高い

図2.11 立ち下がり時間の電極間電圧依存性 ○:障壁増大層がある場合の計算値、●:障壁増大層がない場合の計算値、△:実験値2.41

波長: 1.3 μm

図 2.12 光吸収層内部のキャリア数の変化

電子については、 $V_e>10$  V の時には障壁を越えるのに充分なエネルギーを受けるため障壁増大層の影響は小さいが、 $V_e$ が低くなると障壁を乗り越えられず光吸収層内に留まる電子数が増加する。 $V_e=5$  V の場合、電子数は 25 ps 以降ほぼ一定となり本モデルでは電流が流れなくなる。しかしながら、実際にはトンネル電流が流れる。つまり、このシミュレーションでは電流の立ち下がり時間を小さく見積ることになる。また、この解析では計算時間の制約から単発の光パルスに対する応答を扱っているが、実験では繰返しパルスに対する応答が測定されるという違いがある。繰返しパルスに対しては電子が蓄積し障壁増大層の電界が強くなるものと考えられる。この場合、電子がトンネルする確率は増大する。実験と定量的に一致させるためには、繰返しパルスに対する電子の蓄積効果およびトンネル電流を考慮した解析が今後必要となるう。

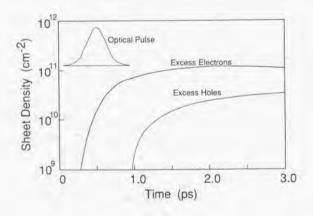

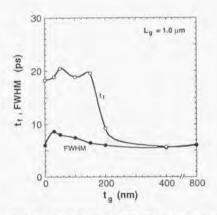

ペテロ接合における電子の蓄積を防ぐために、InGaAs光吸収層と障壁増大層の間に傾斜層を挿入することが提案されている[2.8]-[2.10]。InGaAs MSM-PDの高速化の指針を与えるために、傾斜層の効果を理論的に解析することとする。 $L_g=1.0~\mu m$ 、 $t_a=1.0~\mu m$ 、 $t_b=30~n m$  ( $In_{0.52}AI_{0.48}As$ )、 $Z_0=50~\Omega$ 、 $C_g=20~f$ F、 $V_g=5~V$  として、 $In_{0.53}(Ga_AAI_{0.57}As$  傾斜層の厚さ $t_g$ を変えてシミュレーションを行った。光パルスは波長  $1.3~\mu m$ 、半値全幅 0.1~ps とした。MSM-PD の出力パルスの立ち下がり時間と半値全幅の傾斜層厚さ依存性を図 2.13~c に $_g=200~n m$  を境にして立ち下がり時間

が大きく異なっていることがわかる。光吸収層内のキャリア数の変化を図2.14に示す。正孔数の変化は傾斜層の厚さにあまり依存しないが、傾斜層の厚さを 200 nm にすることにより電子数の減少が速くなることがわかる。アノード電極の右端から深さ方向に見たポテンシャル分布を図 2.15 に示す。  $t_g=50\,\mathrm{nm}$  の場合には電子の障壁が存在しているが、  $t_g=200\,\mathrm{nm}$  の場合には障壁が消滅している。ポテンシャル障壁の消滅により電子の流れが滑らかとなると言える。ポテンシャル障壁が消滅する傾斜層の厚さを臨界厚さと呼ぶことにする。

図 2.13 立ち下がり時間と半値全幅の傾斜層厚さ依存性

図2.14 光吸収層内のキャリア数の変化 実線:電子 破線:正孔

図2.15 深さ方向のポテンシャル分布

GaAs MSM-PDに関して、電界一定のスケーリング則を議論した。InGaAs MSM-PDについて電界一定条件で  $L_{\rm g}=0.25~\mu{\rm m}$  の特性を計算した結果、立ち下がり時間はあまり改善されないことがわかった。ボテンシャル障壁が一定であるということが低電圧化の障害となっているためである。したがって、電圧一定のスケーリング則が適している。また、電極間容量の増大を避けるため、受光面積も小さくする必要があることが 2.4.1 の結果から明らかになっている。そこで、先のパラメータのうち電極間隔  $L_{\rm g}$  のみを 0.25  $\mu{\rm m}$  としてシミュレーションを行った。 MSM-PD の出力パルスの立ち下がり時間と半値全幅の傾斜層厚さ依存性を図2.16に、光吸収層内のキャリア数の変化を図 2.17 に示す。  $I_{\rm g}=200~{\rm nm}$  の場合、電子および正孔数の減少率が悪化している。ボテンシャル分布を検討した結果、このデバイスパラメータについては傾斜層の臨界厚さは約 50  $\mu{\rm m}$  であった。つまり、電極間隔の微細化に対して傾斜層の臨界厚さがスケーリングされているわけである。 臨界厚さ以上に厚くすると、キャリア流出の円滑化の効果は飽和し、走行時間の増加をもたらすこと、光吸収層内部の電界強度を低下させることから電流応答速度が遅くなる。なお、この解析結果では、 $I_{\rm g}=0$ まで立ち下がり時間とパルス幅が減少しているが、図 2.17 にも示されているように電子の蓄積が起き、実際には増大する可能性がある。

図 2.16 立ち下がり時間と半値全幅の傾斜層厚さ依存性

図2.17 光吸収層内のキャリア数の変化 実線:電子 破線:正孔

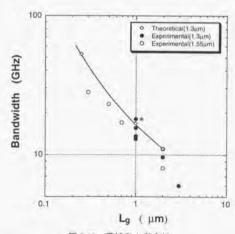

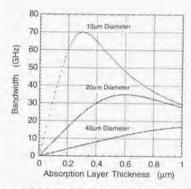

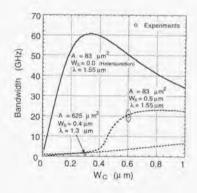

MSM-PDの高速化には電極間隔の微細化とともに光吸収層を薄くすることが重要であることを 2.4.1 で指摘した。 $^{1621}$ また、上の解析より傾斜層も薄くする必要があることがわかった。以上の点を考慮すると、表2.2に示すスケーリング則が $^{16}$ InGaAs MSM-PDの高速化に適していると考えられる。このパラメータを用いて計算したMSM-PDの半値全幅、立ち下がり時間およびフーリエ変換より求めた  $^{16}$ 3dB 帯域も表2.2 にまとめて示した。電極間隔をクォータミタロン程度にすることにより  $^{16}$ 50 GHz を越える帯域が期待できる。  $^{16}$ 3dB 帯域の計算値と実験値[2.6][2.58]-[2.61]の比較を図 2.18 に示す。傾斜層の有効性が明確に示されている。 $^{16}$ 4  $^{16}$ 5  $^{16}$ 6  $^{16}$ 7  $^{16}$ 7  $^{16}$ 8  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9  $^{16}$ 9

表 2.2 InGaAs MSM-PD のスケーリング則、パラメータ値と特性

|                                                | Scaling law |      | Values |      |  |

|------------------------------------------------|-------------|------|--------|------|--|

| Electrode spacing L g (µm)                     | 1/α         | 2.0  | 1.0    | 0.25 |  |

| Barrier-enhancement layer thickness $t_b$ (nm) | 1           | 30   | 30     | 30   |  |

| Graded layer thickness rg (nm)                 | 1/α         | 400  | 200    | 50   |  |

| Absorption layer thickness $t_a$ ( $\mu$ m)    | 1/α         | 2.0  | 1.0    | 0.25 |  |

| Bias voltage $V_g$ (V)                         | 1           | 5.0  | 5.0    | 5.0  |  |

| Parasitic capacitance $C_g$ (fF)               | 1           | 20   | 20     | 20   |  |

| Load impedance $Z_0(\Omega)$                   | - 1         | 50   | 50     | 50   |  |

| Pulse width FWHM (ps)                          |             | 11.9 | 6.0    | 3.5  |  |

| 90-10% fall time t <sub>f</sub> (ps)           |             | 10.7 | 9.2    | 7.5  |  |

| 3-dB bandwidth f <sub>3dB</sub> (GHz)          |             | 11.2 | 16.7   | 52.5 |  |

図 2.18 帯域の L<sub>g</sub> 依存性 実験のうち、\*は傾斜層付き、その他は傾斜層なし

<sup>&</sup>lt;sup>||</sup> 最近、Wohlmuth *et al.* [2.32]は電極間隔 1 μm の InGaAs MSM-PD において光吸収層を 1 μm から 0.25 μm に薄層化することにより 3 dB 帯域が 9.5 GHz から 19.1 GHz に増大することを実験的に示している。

#### 2.6 まとめ

電子デバイス製造工程との整合性が比較的良く、寄生容量が小さいこと、製造方法が簡単であること等を特徴とする金属ー半導体ー金属構造プレーナ型受光デバイス(MSM-PD)の高速化設計について述べた。最初に、理論的な研究手法として、対象とする時間精度(あるいは周波数領域)と適用すべきデバイス解析法の関係を整理し、移動度と拡散係数によりドリフト項と拡散項を近似した電流連続式並びにポアソン方程式を二次元空間で数値解析する方法(流体モデル)とモンテカルロ手法によりポルツマン輸送方程式を二次元空間で数値解析する方法(粒子モデル)の2つの手法に基づく数値計算プログラムを作成した。

流体モデルを用いて GaAs MSM-PD を解析し、次の結果を得た。

- (a) 光パルス照射によりキャリア濃度が  $10^{16}\,\mathrm{cm}^3$  を越える強励起状態では、発生した電子と正孔 が各々反対方向に移動して空間電荷領域が形成されるためMSM-PD内部の電界強度が低下する。 フォトコンダクティビィティを計算する際には、この電界低下効果を考慮する必要がある。

- (b) 光通信で使用される弱励起状態では、電界低下効果を無視できる。

次に、粒子モデルにより GaAs MSM-PD および InGaAs MSM-PD を解析し、以下のような高速 化の指針を得た。

- (c) MSM-PD の高速化のためには電極間隔とともに光吸収層の厚さと受光面積の縮小が必要である。

- (d) 障壁増強層を有する InGaAs MSM-PDにおいては、障壁増強層と光吸収層の間に傾斜層を設ける必要があり、傾斜層の厚さには最適値が存在する。最適な傾斜層の厚さは電極間隔に比例する。 (e) GaAs MSM-PDにおいては電極間隔に比例して電極間電圧を下げる電界一定スケーリングで良いが、障壁増強層を有する InGaAs MSM-PD においては電極間電圧を一定とする電圧一定スケーリングが望ましい。

- (f) 電極間隔をクォータミクロン程度にすることにより 50 GHz を越える帯域が期待できる。

## 第3章

## 受信用集積回路の高性能化設計

#### 概要

超高速集積回路を実現するためには、デバイス技術、回路技術、実装技術を有機的に結合させる必要がある。すなわち、デバイス技術としては回路の高速化に適したデバイスを開発する必要がある。このため、デバイスの等価回路パラメータを変化させて回路シミュレーションを行うことにより回路の動作速度とデバイス性能の関係を把握することが一般的であった。しかしながら、これらのパラメータの間には相関があり、相関まで厳密に押えて議論することはかなり困難なことである。また、集積回路チップとバッケージを独立に設計すると、実装に伴う寄生効果により予期した特性が得られず、最悪の場合には回路が発振することもある。

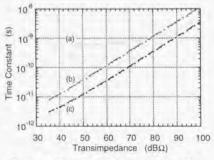

本章では最初に、実装に伴う寄生効果を考慮に入れた安定性解析に基づく増幅回路とパッケージの一括設計法を明らかにする。次に、デバイスの電流利得遮断周波数あるいは最大発振周波数を用いて受信回路のキーとなるベースパンド増幅器と識別器の最高動作速度を表すデバイス性能指数を提案する。これらの結果をもとに、集積回路チップ間インターコネクションが高速化、低消費電力化を阻害することを指摘するとともに、InP/InGaAsダブルヘテロ接合パイポーラトランジスタによりモノリシック3R機能回路を試作し、2.4 Gbit/s 受信回路モジュールと比較して約2桁の低エネルギー化が可能であることを示す。

#### 3.1 はじめに

本章では光通信用受信回路の電子回路部分に関する研究を行う。図1.3 に示した中継器の等化 増幅部は高利得、広帯域な増幅器と利得制御回路から構成される。伝送符号は NRZ(Non-Returnto-Zero)でありクロック成分を持たないため、タイミング抽出回路によりクロックが再生される。タイミング抽出回路には、微分回路、全波整流回路、共振器、リミッタ増幅器から構成される非 線形抽出方式、あるいは位相比較器、低域通過フィルタ、電圧制御発振器から構成される位相同期ループ(PLL: Phase-Locked Loop)方式が用いられる。識別再生部にはDタイプフリップフロップ(D-F/F)が用いられる。この中でクロック用リミッタ増幅器は狭帯域特性で良く、従来のマイクロ 波増幅回路技術を活用できる。これに対して、等化増幅部には 100 kHz から伝送レート周波数の70 % までの広帯域性が要求される[3.1][3.2]。今、光送信パワーを 0 dBm、中継区間を 80 km とすると、伝送路での損失により受光パワーは-16 dBm 程度となる。光ファイバ増幅器(EDFA: Er-Doped Fiber Amplifier)を用いない場合、受光デバイスの感度を 0.7 A/W とすると、1 Vppのディジタルレベルまでに増幅するためには、等化増幅部には 90 dBΩ のインピーダンス変換利得が必要となる。電11

第1章で述べたように、本研究に着手した当時はゲート長0.1 – 0.2 μm級 GaAs MESFET の可能性が見え始めた段階にあり、10 Gbit/sを越える動作を実現するためには回路技術および実装技術の研究開発が必要であった。従来の広帯域増幅器では上記MESFETを用いても必要な帯域を実現できない。また、動作速度が高くなると、実装に付随する寄生容量あるいは寄生インダクタンスの影響が大きくなり、高利得、広帯域な増幅器モジュールを実現することがより難しくなる。

一方、結晶成長の進展に支えられてヘテロ構造デバイスのポテンシャルの高さが示されているが、将来的に電子回路の動作速度限界がどこにあるのかは明確でない。従来、デバイスの等価回路パラメータを変化させて回路シミュレーションを行うこと (感度解析) により回路の動作速度とデバイス性能の関係を把握することが一般的であった。しかしながら、これらのパラメータの間には相関があり、相関まで厳密に押えて議論することはかなり困難なことである。むしろ、電流利得連断周波数あるいは最大発振周波数というデバイス研究者に馴染深いバラメータを用いて回路の最高動作速度を記述する方が集積回路の高速化に寄与できるものと考えられる。

回路の低エネルギー化のアプローチには、高速化とともに低電力化の方策が考えられる。従来の受信回路はSSIから構成されたハイブリッド回路である。将来的にはSSI間のインターコネクションが動作速度と消費電力を制限する大きな要因となる可能性があり、モノリシック集積の効果を明らかにすることは極めて重要である。

## 3.2 10 Gbit/s 等化増幅集積回路モジュール[3.44][3.45]

#### 3.2.1 増幅器、パッケージー括設計法

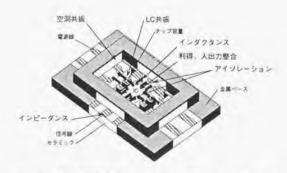

一般的に広帯域増幅器は図3.1に示すような高周波セラミックパッケージに実装されてきた。 パッケージの信号線と増幅器チップ上のパッドとはボンディングワイヤで接続されている。周波 数が高くなると、パッケージの電源線の寄生インダクタンスにより電源線インビーダンスが増加 し、増幅器チップ内の電源線を介した入出力の結合が大きくなり不安定動作を起こすことがある。

図3.1 広帯域増幅器の実装形態と設計上考慮すべき電気的特性

以上の観点に立って本章では、受信回路用集積回路の高速化と低消費電力化の研究を行う。3.2 では 10 Gbit/s 等化増幅集積回路モジュールに関して、寄生効果を考慮に入れた安定性解析に基づく増幅回路とパッケージの一括設計法を明らかにする。実用レベルの GaAs MESFET 広帯域増幅器等を用いて試作した等化増幅モジュールの評価により一括設計法の有効性を示す。3.3 では 10 Gbit/s 以上の高速化を目指して、受信回路の基本要素であるベースバンド増幅器および識別器の動作速度とデバイス性能との関係を明確化する。デバイスの電流利得遮断周波数  $f_r$  および最大発振周波数  $f_{max}$  を用いてベースバンド増幅器および識別器の動作速度を記述し、回路の高速化に即したデバイス性能指数を提案する。文献で報告されている識別器あるいは D-F/F の最高動作速度および AlGaAs/GaAs HBT を用いて試作したベースバンド増幅器の帯域とデバイス性能との関係より、提案したデバイス性能指数の妥当性を検証する。3.4 では3.2 と 3.3 の結果をもとに集積回路チップ間インターコネクションが高速化、低消費電力化を阻害することを指摘するとともに、InP/InGaAs ダブルヘテロ接合バイボーラトランジスタ(DHBT: Double-Heterojunction Bipolar Transistor)によりモノリシック 3 R機能回路を試作し、低エネルギー化の可能性を示す。

IEII もちろん EDFA の使用を前提とすれば必要な利得は減少する。

このため、増幅器チップの電源をチップ容量を介して接地することにより、高周波領域でのインピーダンス増加を補償している。周波数が高くなると、このような実装形態においては以下のような問題が起こる。パッケージの入出力線間のアイツレーションが劣化するとともに、ボンディングワイヤのインダクタンスの影響により入力整合および出力整合特性が悪化する。これらは増幅器の不安定動作(発振)の原因となる。また、電源のチップ容量とボンディングワイヤのインダクタンスによるLC共振のため共振周波数で利得が低下あるいは増大する。さらに、パッケージの空洞共振周波数においては入出力線間が著しく結合し、増幅器モジュールは発振してしまう。これらの問題は広帯域になればなるほど、あるいは高利得になればなるほど深刻なものとなる。

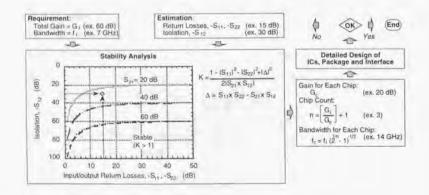

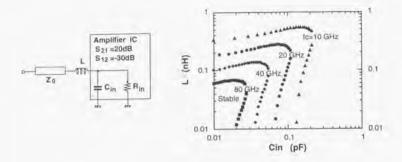

広帯域、高利得な増幅器モジュールを実現するためには、以上の現象をすべて考慮に入れて増幅器とパッケージを一括して設計する必要がある。ここでは、10 GHz 領域においても上記の実 装形態が適用できるものと判断し、電源のチップ容量とボンディングワイヤのインダクタンス等 の受動デバイスを集中定数として扱い、安定性解析(3.3)に基づき等化増幅器モジュールを設計した。設計の流れを図 3.2 に示す。安定性解析は、系の 2 ポート散乱(S: Scattering)パラメータを用いた安定性係数  $K( \boxtimes 3.2$  中に示す)が 1 より大きければ、その系は絶対安定であるという原理に基づくものである。図 3.2 中の曲線は利得  $S_{21}$  をパラメータとして K=1 となる入出力リターンロス $(.S_{21}, ..., S_{22})$ とアイソレーション $(.S_{12})$ の関係を描いたもので、この曲線より下の領域で系は絶対安定となる。4 つのパラメータに対して方程式が 1 つであるから、当然のことながらパラメータを一意に決めることはできない。そこで、文献[3.3]の結果から、10GHz の領域においても入出力リターンロスが 15 dB、アイソレーションが 30 dB を確保できるものと仮定する。この場合、増幅器が安定に動作するためには、利得  $S_{21}$  は 26 dB 以下でなければならない。今、要求条件とし

図3.2 安定性解析に基づく増幅器モジュール設計の流れ

#### 3.2.2 デバイス技術[3.7]

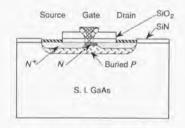

デバイス特性の再現性、デバイス間特性バラッキ、信頼性等の技術成熟度の観点から、ゲート 長  $0.2~\mu m$  の自己整合型 GaAs MESFET[3.4]-[3.7]を採用した。その概略断面構造を図  $3.3~\epsilon i$  ボイジタル応用には対称型構造MESFETが用いられている[3.7]が、高利得性を要求されるアナログ回路応用として、斜めイオン注入によりドレインオフセット構造を実現しドレインコンダクタンスの低減を図ったものである[3.7]。主なデバイス特性を表  $3.1~\epsilon i$  にまとめた。抵抗はシート抵抗  $150~\Omega$  と  $500~\Omega$  の N および N イオン注入層で、容量は第 1 層配線 - 550 nm SiN - 第 2 層配線の MIMにより形成した。配線抵抗を低減するため第 2 層配線上には金メッキを施すことが可能である。また、金メッキ配線は第 2 層配線とエアーブリッジで交差するため、交差容量を低減でき、実質的に  $^{\prime\prime}2.5^{\prime\prime}$  層配線構造である。

図 3.3 GaAs MESFET の断面構造[3.7]

表 3.1 主なデバイス特性[3.7]

| Parameter                           | Value     |

|-------------------------------------|-----------|

| Threshold Voltage                   | - 0.8 V   |

| Transconductance                    | 400 mS/mm |

| Drain Conductance                   | 25 mS/mm  |

| Unity-gain Current Cutoff Frequency | 40 GHz    |

| Maximum Oscillation Frequency       | 70 GHz    |

|                                     |           |

#### 3.2.3 入出力整合設計

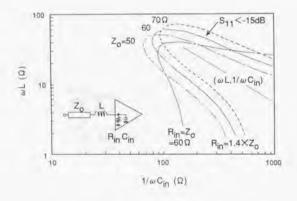

3.2.1 において、入出力反射損失( $-S_{11}$ 、 $-S_{22}$ )が 15 dB 必要であるという指針を与えた。この条件を満たすようにインターフェース設計を行う。入力インターフェースを図 3.4 の挿入図に示すような等価回路で表現する。ここに、 $R_{m}$  と  $C_{m}$  は各々入力抵抗と入力容量、L はボンディングワイヤのインダクタンス、 $Z_{n}$  はパッケージの伝送線路インビーダンスである。 $(1/\omega C_{m}, \omega L)$ のインビーダンス平面で考えると、 $S_{11}<-15$  dB を満たす領域は図中の曲線群の内側の領域となる。 $(C_{m}, L)$ の1つの組み合せについて見ると、周波数が変化する時、 $(1/\omega C_{m}, \omega L)$ のインビーダンス軌跡は左上がりの直線となる。 $S_{11}<-15$  dB となるためには、帯域内での $(1/\omega C_{m}, \omega L)$ のインビーダンス軌跡が曲線の内側に収まっていることが必要である。図 3.4 では、上記 MESFET に典型的な  $C_{m}=0.5$  pF と、通常のボンディングで容易に実現できる L=0.5 nH について 10 GHz までのインビーダンス軌跡を示した。この図から、 $Z_{0}$  は 50  $\Omega$  よりも高めの 50  $\Omega$  程度が、また  $R_{m}$  は  $Z_{0}$  の 1.4 倍程度が、製造マージンの観点から好ましいと言える。

出力インターフェースに関しては、出力容量が入力容量の 1/3 程度であるため、インピーダンス 軟跡は右方向にシフトすることになる。この場合には、出力抵抗をさらに高く設定すべきことが図 3.4  $\pm$  1 容易に類推できる。モジュールの外部は 50  $\Omega$  系であるが、50  $\Omega$  と 60  $\Omega$  の反射量は -20 dB 以下であるため、モジュールの特性インピーダンスを 60  $\Omega$  としても問題ないものと考えられる。

図 3.4 入力整合条件

#### 3.2.4 等化増幅集積回路モジュールの試作

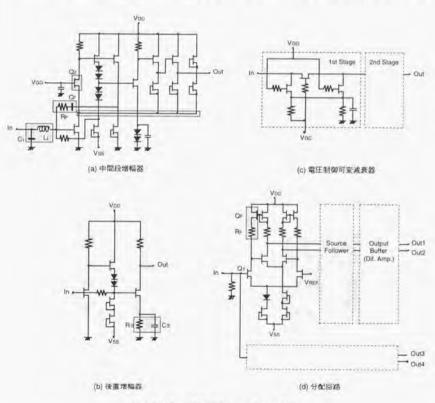

等化増幅集積回路モジュールに用いた回路の構成を図3.5に示す。図3.5(a)の中間段増幅器は、広帯域化を図るためにカスコードFETを用いて入力容量を低減するとともに最終段ソースフォロアからの帰還により高周波領域で負帰還から正帰還に遷移することを利用して広帯域化を図っている。さらに、LC回路、 $R_p$ と  $C_p$ の付加的な帰還により高周波領域での入力整合性の改善と低雑音化を図っている[3.8]。この回路により、従来の並列帰還増幅器と比較して約2倍の広帯域化が可能である。図3.5(b)の後置増幅器は1  $V_{pp}$ 以上の出力振幅を得るために最終段をソース接地構成としソースピーキングにより広帯域化を図っている。等化増幅モジュールに必要な利得制御機能は、電圧制御可変減衰器と中間段増幅器との組み合せで実現することとした。図3.5(c)の $\pi$ 型可変減衰器[3.9]は、制御電圧を変化させた場合、常に平坦な損失一周波数特性と良好な入出力整合特性を示すという特徴を有している[3.8]。増幅した信号を識別再生部とタイミング抽出部に送る

図3.5 等化増幅器モジュール用いた回路

ための分配回路は、図3.5(d)に示すような分岐/差動増幅の構成とし、FETを介した強い帰還により広帯域化を図っている(3.10]。試作した回路の特性を表3.2に示す。

表 3.2 試作した回路の主な特性

| Circuit                | Gain<br>Bandwidth  | Input Matching<br>Output Matching | Supply Voltage<br>Power Dissipation                          | Chip Size    |

|------------------------|--------------------|-----------------------------------|--------------------------------------------------------------|--------------|

| Intermediate Amplifier | 17 dB<br>13 GHz    | < - 12 dB<br>< - 12 dB            | V <sub>DD</sub> = 8 V, V <sub>SS</sub> = - 3 V<br>500 mW     | 1.5 x 1.5 mm |

| Variable Attenuator    | - 424 dB<br>15 GHz | < - 8 dB<br>< - 10 dB             | $V_{GG} = +1.3 \text{ V}, V_{GC} = \text{var}.$ 5 mW         | 1.5 x 1.5 mm |

| Post Amplifier         | 17 dB<br>11 GHz    | < - 8 dB<br>< - 10 dB             | $V_{DD} = 7 \text{ V}, V_{SS} = -3 \text{ V}$<br>450 mW      | 1.5 x 1.5 mm |

| Distributor            | 0 dB<br>10 GHz     | < - 14 dB<br>< - 11 dB            | $V_{DD} = 6.5 \text{ V}, V_{SS} = -3.5 \text{ V}$<br>1350 mW | 1.5 x 2.0 mm |

3.2.1 および3.2.3 で得られた指針をもとに、シングルチップ版とマルチチップ版のパッケージを試作した。それらの概観写真を図3.6 に示す。銅タングステンをベースとしたセラミックパッケージである。信号線は特性インピーダンス約  $60\Omega$  の共平面伝送線路とした。電源のチップ容量とボンディングワイヤのインダクタンスによる LC 共振を緩和するためにパッケージの電源線に  $5\Omega$  のタンタル薄膜抵抗を蒸着で形成した。また、パッケージの空洞共振を帯域外に追い出すために空洞のサイズを  $6\times3.5$  mm とした。入出力間アイソレーションは 15 GHz まで 40 dB 以上であった。 42 リード部分を除くシングルチップ版パッケージのサイズは  $7\times11$  mm、マルチチップ版パッケージのサイズは  $31\times11$  mmである。マルチチップ版パッケージには、 $1.5\times1.5$  mm チップ 3 個と  $2.0\times1.5$  mm チップ 1 個が搭載可能であり、各チップ間には直流カット用のチップ容量を実装することができる。

図3.6 バッケージの機観写真

429 本研究以後、T. Shibuta et al. [3.11]により本パッケージの空洞共振周波数が約 20 GHz であることが理論的に明らかにされた。

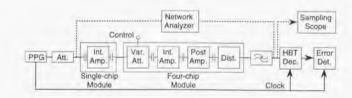

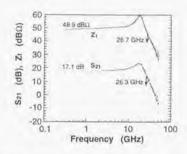

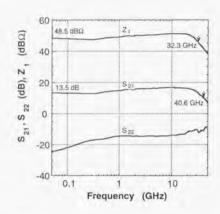

試作したチップとバッケージを用いて等化増幅モジュールを構成した。その構成を実験系と含めて図3.7に示す。シングルチップ版パッケージには中間段増幅器を、マルチチップ版パッケージにはすべての回路を搭載している。Sパラメータの測定にはネットワークアナライザ(HP製)を、符号誤り率の測定にはパルスパターン発生器と符号誤り率測定器(Anritsu 製)を用いた。等化増幅モジュールの出力には、周波数特性を平坦化するための2次低域遮断フィルタと AlGaAs/GaAs HBT を用いて製作した識別器[3.12]を接続した。測定した $S_{31}$ の周波数特性を図3.8 (C 示す。C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C 引 C に C 引 C に C 引 C 引 C に C 引 C に C 引 C に C 引 C に C に C 引 C に C に C の C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に C に

ここで試作した等化増幅集積回路モジュールは、Imai et al. [3.14]のタイミング抽出部、Ohhata et al. [3.15]の識別再生部、Togashi et al. [3.16]の多重化および分離部、Miyamoto et al. [3.13]の E/O および O/E 変換部とともに、Nakagawa et al. による東京唐崎と浜松間の現場環境下での実験に使用され、安定に動作することが確認された[3.17]。この実験により 10 Gbit/s 光再生中継器の実用化の見通しが得られ、ここで提案した高利得、広帯域増幅器モジュール設計法の有効性が実証された。

図3.7 等化増幅モジュールの構成と実験系

図3.8 等化増幅モジュールの S。特性

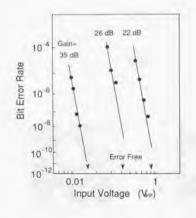

図3.9 アイバターンと符号誤り率特性

### 3.3 ベースバンド回路に適したデバイス性能指数[3.46]

#### 3.3.1 デバイス性能指数の導出

最初に、高速ディジタル回路の基本となる D-F/F の最高動作速度について議論する。高速ディジタル回路は、高速動作に適したバイボーラエミッタ結合論理(ECL: Emitter-Coupled Logic)あるいはソース結合 FET 論理(SCFL: Source-Coupled FET Logic)が主流である。最初に ECL、次に SCFL について最高動作速度の近似式を導出する。

Tien[3.18]の式を拡張すると、ECL インバータの伝搬遅延時間は次式で与えられる。

$$t_{pd} = \tau_f + R_B C_D + R_B C_{BC} \left( 2 + \frac{R_L}{r_D} \right) + R_L C_{BC} \left( 2 + \frac{r_D}{R_L} \right) + R_L C_{BCex} \left( 2 + \frac{r_D}{R_L} \right) \tag{3.1}$$

ここで、 $\tau_c$ は電子走行時間、 $R_B$ はベース抵抗、 $R_L$ は負荷抵抗、 $\tau_D$ は微分エミッタ抵抗、 $C_{BC}$ は内部ベースーコレクタ間容量、 $C_{BC}$ は外部ベースーコレクタ間容量、 $C_D$ は拡散容量である。付表B1(付録B.1)に示した例においては、この近似式は 2%の精度で回路シミュレーション結果と一致している。

ここで、論理振幅  $V_{\rm sw}$  ( =  $I_c R_L$  )が一定という条件のもとで式(3.1)はある最小値を持ち、次式で近似できる(付録 B.1)。

$$t_{pd(\min)} = \frac{1}{2\pi} \left( \frac{1}{f_T} + \sqrt{\frac{2V_{SW}}{0.15}} \frac{1}{f_{\max}} \right) + \left( 2 + \frac{V_{SW}}{0.15} \right) R_B C_{BC}$$

(3.2)

基本インパータの遅延時間とD-F/Fの最高動作速度の間には一定の関係があると考えられる。 したがって、D-F/Fの最高動作速度は次式により表現できる。

$$f_{c \max} \approx \alpha \left\{ \frac{1}{f_T} + \sqrt{\frac{2V_{SW}}{0.15}} \frac{1}{f_{\max}} + \left(2 + \frac{V_{SW}}{0.15}\right) \frac{f_T}{4f_{\max}^2} \right\}^{-1}$$

(3.3)

パラメータαはD-F/Fの回路構成に依存するものであるが、総括的に議論するために一般的に用いられているD-F/Fについて考える。Ichino[3.12]によれば、AlGaAs/GaAs HBTを用いたトグルフリップフロップ(T-F/F)の最高動作周波数は基本インバータの遅延時間の3.5 倍の逆数で近似でき、D-F/Fの最高動作速度とT-F/Fの最高動作周波数の比は1:1.3 である。したがって、式(3.3)のパラメータαは1.38 と見積もられる。

次に、SCFL インバータについて同様の手続きを採る(付録 B.2)。SCFL インバータの遅延時間 は式(3.4)と式(3.5)の和で与えられる[3.47]。

$$\begin{split} D_{CS} &= \left[ -\frac{dA(s)/ds}{A(s)} \right]_{s=0} \\ &= \frac{C_{gd(C)}}{g_{m(C)}} + \frac{R_L(C_{gd(C)} + C_{ds}) + R_L R_g g_{m(C)} C_{gd(C)}}{1 + R_L g_{ds}} + R_g (C_{gs(C)} + C_{gd(C)}) \end{split} \tag{3.4}$$

$$\begin{split} D_{SF} &= \left[ -\frac{dB(s)/ds}{B(s)} \right]_{s=0} \\ &= C_{gd(F)}(R_L + R_g) + C_{gs(F)}[R_L + R_g + \frac{1 - g_{m(F)}(R_L + R_g)}{g_{m(F)} + g_{ds} + \frac{1}{R_S}} - \frac{1}{g_{m(F)}}] + \frac{C_L + C_{ds}}{g_{m(F)} + g_{ds} + \frac{1}{R_S}} \end{split} \tag{3.5}$$

ここで、 $g_m$ は相互コンダクタンス、 $g_{ab}$ はドレインコンダクタンス、 $R_L$ は負荷抵抗、 $R_g$ はゲート抵抗、 $R_g$ はソースフォロア抵抗、 $C_{gr}$ はソースーゲート間容量、 $C_{gg}$ はソースードレイン間容量、 $C_{ab}$ はソースードレイン間容量、 $C_{ab}$ はソースードレイン間容量、 $C_{bb}$ は負荷容量である(付図 B1 参照)。また、添字(C)と(F)を付与したパラメータはバイアス依存性を有しており、付録B.2に示すように動作電圧範囲の平均値で近似する。付表B2(付録B.2)に示した例においては、近似式は7%の精度で実験値と一致している。今、電流スイッチとソースフォロアの容量が同一であるとし、負荷容量 $C_L$ 、ソースードレイン間容量 $C_{dg}$ 、ドレインコンダクタンス  $C_{dg}$ を無視すると、インバータの遅延時間は次式により近似できる。

$$t_{pd} = R_g C_{gg} + R_g C_{gd} (2 + A_v) + R_L C_{gd} \left(2 + \frac{1}{A_v}\right)$$

(3.6)

ここで、 $A_o$ はインバータの電圧利得である。この式はECLに対する式(3.1)の最初と最後の項を除いたものと同一形式である。ここで、バイボーラトランジスタとFETの違いは、前者では拡散容量  $C_D$ が電流に比例するのに対して、後者では  $C_g$ が飽和特性を持つことである。このことから、ECLでは遅延時間最小となる負荷抵抗が存在するのに対して、SCFLでは負荷抵抗が小さいほど遅延時間は小さくなる。つまり、ECLに対する上記の取扱いができないことになる。そこで、 $R_g$ 、 $C_{d_0}$ 、 $S_{d_0}$ が無視できるほど小さいとして、つまり  $f_{max}$  が $f_T$  に対して充分大きいものとして、式(3.4)(3.5)を変形すると次式が得られる。

$$r_{pd} = \frac{C_{g1}}{g_m} + (2 + A_c) \frac{C_{gd}}{g_m} + 2R_L C_{gd}$$

(3.7)

A. g. R. を用いると、

$$t_{pd} = \frac{C_{gs}}{g_m} + (2 + 3A_v) \frac{C_{gd}}{g_m} \propto \frac{C_{g0}}{g_m} \propto \frac{1}{f_T}$$

(3.8)

したがって、SCFL D-F/Fの最高動作速度は次のようになる。

$$f_{c \max} = \beta f_T$$

(3.9)

ここで、付表 B2(付録 B.2)に示した MESFET の  $f_r$  は 50 GHz であるから、インバータ遅延時間  $t_{pd}$  と  $f_r$  との関係は

$$t_{pd} = \frac{0.91}{f_T}$$

(3.10)

ECL に対するインパータ遅延時間と D-F/F 最高動作速度との関係が SCFL についても成り立つものとすれば、式(3.9)の  $\beta$  は 0.24 となる。

次に、受信回路中の基本回路であるベースバンド増幅器について考える。帰還増幅器の帯域は 帰還なしの場合の帯域と一定の関係にあるから、ECLインバータに対する式(3.3)と等価な次式で 表現できる。(ED)

$$f_{3dB} = \alpha_{amp} \left\{ \frac{1}{f_T} + \sqrt{2A_v} \frac{1}{f_{max}} + (2 + A_v) \frac{f_T}{4f_{max}^2} \right\}^{-1}$$

(3.11)

同様に、FET帰還増幅器の帯域は次式で与えられる。

$$f_{3dB} = \beta_{amp} f_T \tag{3.12}$$

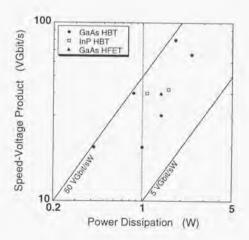

#### 3.3.2 実験との比較

文献[3.23][3.24]で報告されているD-F/F(あるいは識別器)の最高動作速度の実験値と導出したデバイス性能指数との比較を行った結果を図 3.10 に示す。論理振幅  $V_{sw}=0.5$  V を仮定した式(3.3)と式(3.9)の右辺で横軸を、実験値で縦軸をブロットしており、直線に近いほど、デバイス性能指数の近似度が良いことを示す。報告により回路構成、論理振幅、負荷抵抗値が異なる可能性があることを考慮すると、比較的良い近似であると考えられる。1.5 [3.23]の指摘のように、GaAs HBTと比較してシリコンバイポーラトランジスタの方が同一デバイス性能でも最高動作速

<sup>&</sup>lt;sup>15 小</sup>式(3.3)の $V_{var}/0.15$ を電圧利得 $A_c$ で置き換えれば良い。

度が大きい理由は、前者では、通常の回路構成が用いられ、論理振幅が 0.5 V 程度であるのに対して、後者では、高速化に有利な 2 段エミッタフォロア構成を用いている例が多いこと、抵抗とトランジスタサイズの最適がなされていること[3.25]、論理振幅が小さいことによるものと考えられる。なお、図中に a で示したデータの動作速度は市販測定器の測定限界により制限されている可能性もある。

図3.10 デバイス性能指数とD-F/F(あるいは識別器)の最高動作速度実験値との相関

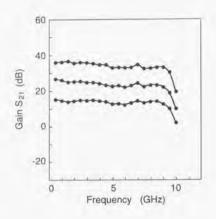

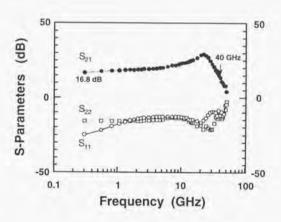

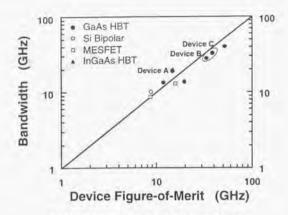

ペースパンド増幅器に対するデバイス性能指数は、文献[3.23][3.26]-[3.29]で報告されている帯域、ならびにAlGaAs/GaAs HBTの一種であるロンチャ付き弾道輸送トランジスタ(L-BCT: Ballistic Collection Transistor with Launcher)[3.30]を用いた実験により検証を行った。実験には3種類のデバイス(A、B、C)[3.19][3.31][3.32]を用いた。各デバイスの層構成を付表B3(付録B.3)に示す。測定は帯域65 GHz の RF プローブ(Cascade Microtech 製)と50 GHz のネットワークアナライザ(HP 製)を用いてオンウェハで行った。デバイスCにおいて、 $f_T$ =100 GHz、 $f_{max}$ =192 GHz の優れた特性が得られた。設計試作したベースパンド増幅器の回路構成を図3.11に示す。この回路は図3.5 (d)と同様にトランジスタ $Q_3$ と抵抗 $R_{f2}$ を介した負帰還により広帯域化を図ったものである[3.10]。通常の増幅段ではベースーコレクタ間容量 $C_{gc}$ が利得倍されて入力側から見える(ミラー効果)が、この回路では帰還作用により $C_{gc}$ がそのまま見えることになる[3.10]。このため、通常の帰還増幅器と比較して約2 倍の広帯域化が可能である。ベースパンド増幅器の特性の一例を図3.12に示す。 $S_{21}$ 利得は16.8 dB、3dB 帯域は40 GHz と広帯域化を達成でき、入出力整合特性も良好である。20 GHz 付近の過剰ピーキングの原因は、次節にて議論する。

図3.11 デバイスBとCを用いて試作したベースパンド増幅器の回路構成とチップ写真

図3.12 デバイスCのSバラメータの周波数特性

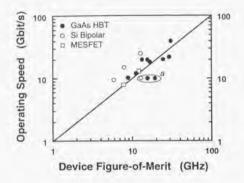

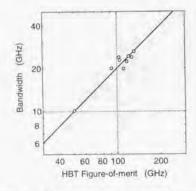

本実験および文献[3.23][3.26]-[3.29]で報告されている 15 dB 以上の $S_{21}$ 利得を有するベースパンド増幅器の帯域とデバイス性能指数との関係を図 3.13 に示す。式(3.11)( $\alpha_{amp}$  = 2.24、 $A_v$  = 10)と式 (3.12)( $\beta_{amp}$  = 0.39)の右辺を横軸に、帯域を縦軸にしてプロットしている。比較的良好な相関関係が得られている。係数  $\alpha_{amp}$ 、 $\beta_{amp}$  は回路構成に依存し、回路の良し悪しを計る目安であるとも言える。図 3.13では他のデバイスについて報告されているベースパンド増幅器の中で広帯域化に適した構成のものを示している。

図3.13 増幅器の帯域とデバイス性能指数の関係

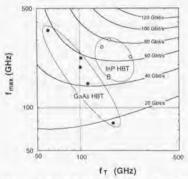

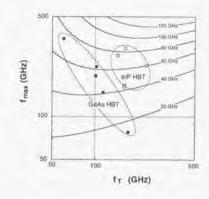

以上の実験との比較から、提案したデバイス性能指数がベースパンド回路の動作速度を比較的精度良く表せることがわかった。そこで、上記のデバイス性能指数を用いて、将来のベースパンド回路の性能を予測してみる。式(3.3)と式(3.11)の左辺、つまりバイボーラトランジスタを用いたD-F/Fの最高動作速度とベースパンド増幅器の帯域をパラメータとして、これらを実現するのに必要な $f_r$ と $f_{max}$ を計算したものを図3.14と図3.15に示す。図では $(f_r$ 、 $f_{max}$ )平面の等高線で表している。同図には文献で報告されているHBTの性能も合わせて示した。デバイス性能の向上により 100 Gbit/s あるいは 100 GHz を実現できる可能性がある。

一方、式(3.9)と式(3.12)から、100 Gbit/s D-F/F あるいは 100 GHz ベースバンド増幅器を実現するためには、各々、 $f_r=410$  GHz、 $f_r=260$  GHz のFET が必要となると予測される。これらのデバイス性能はヘテロ構造 FET の極限性能に近いものと思われる。

図3.14 D-F/F の最高動作速度と f<sub>r</sub> - f<sub>max</sub> の関係

図 3.15 ベースバンド増幅器の帯域と f<sub>s</sub>-f<sub>max</sub> の関係

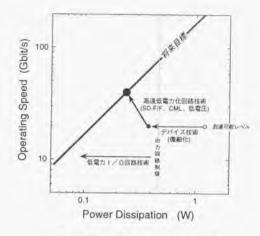

#### 3.4 モノリシック集積化による低エネルギー化

#### 3.4.1 集積化の重要性

前節で 100 Gbit/s 級のベースバンド増幅器とD-F/Fの実現も将来不可能ではないことを示した。 しかしながら、これらの集積回路と受光デバイスから受信回路を構成するためには、実装上の課題を克服しなければならない。ここでは、この課題について議論する。

3.2で示した安定性解析をもとに $S_{21}$  利得が 20 dB の増幅器が安定に動作するために必要なチップ接続部インダクタンスと増幅器入力容量を計算した結果を図3.16に示す。100 GHz 級の増幅器 モジュールを実現するためには、10 fF 程度の入力容量と数 10 pH 程度のチップ接続部インダクタンスが要求される。半絶縁性基板を用いた化合物半導体集積回路のボンディングパッドの容量は 15 fF 程度である。したがって、現状の微小パンプ技術を用いたとしても実現不可能と考えられる。高度な実装技術を開発する、あるいは受信回路と分離回路(DEMUX)を集積化し、高速信号を光で入力し容易に扱える速度までDEMUXして電気で出力する構成等の研究を行う必要があろう。

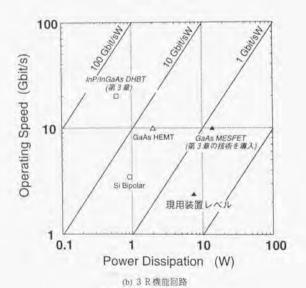

以上のような技術により 100 Gbit/s 受信回路が実現できたとすると、現状の受信回路と比較して約2 桁の低エネルギー化が達成されることになる。低エネルギー化の別のアプローチは低消費電力化である。3.3 に示した等化増幅集積回路モジュールを適用した 10 Gbit/s 受信回路モジュールの消費電力は 14 W であるが[3.33]、全体の消費電力に対してチップ間の 50  $\Omega$  伝送線路インターフェースに必要な消費電力の比率が大きい。増幅器では入出力回路の消費電力を切り分けること

図3.16 安定性条件 出力側についても同一のモデルとした。

は難しいが、10 Gbit/s 級ディジタル IC の内部回路の消費電力はチップ全体の消費電力の 1/10 程度であり[3.34] [3.35]、電力のほとんどは入出力インターフェース回路で消費されている。低消費電力化の方策として受信回路の 1 チップ集積化が最も効果的であると考えられる。

集積化の効果は低消費電力化に留まらない。式(3.2)から明確なようにバイポーラトランジスタによるインバータの遅延時間は論理振幅が大きいほど大きくなる。内部回路の振幅より大きな振幅を出力する必要のある出力ドライバで回路の動作速度が決まることがある。集積化によりその速度制限要因が解消され、高速化にも有利である。さらに、部品コスト、サイズ、信頼性の観点からも集積化が有利であることは、いままでのLSIの高集積化の歴史が物語っているところである。

#### 3.4.2 InP/InGaAs DHBT を用いた 3 R機能回路[3.51]

前節で用いた AlGaAs/GaAs HBT に対して、InP/InGaAs HBT は (1) 電子速度が大きい、(2) ベースーエミッタ間オン電圧が低いという利点を有している。これらの特徴は回路の高速化、低電力化を達成するために適している。通常の InP/InGaAs HBT の欠点はコレクタ耐圧が低いことであるが、InGaAsと InPから成るコンポジットコレクタを採用することによりコレクタ耐圧を上げることが可能である[3.36]。また、前節ではエミッタ電極幅が 2.2  $\mu$ m の HBT を用い、トラジスタ当たり 5 mA 程度の電流を消費していたが、消費電力で規定される集積密度限界を緩和するためには低電流化が必要となる。バイポーラトランジスタの $f_T$  と  $f_{max}$  は電流密度で決まるため、エミッタの微細化により低電流化が可能である。トランジスタの微細化はシリコンバイポーラトランジスタで採られてきた低エネルギー化の指導原理であり、化合物半導体HBTにも当てはまるものと考えられる。ここでは、主としてエミッタ電極幅が 1.2  $\mu$ m の HBT を用いた。

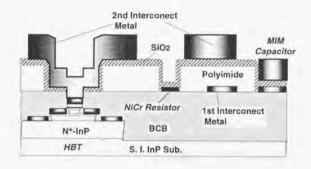

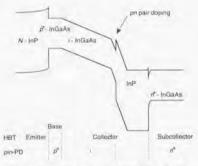

InP/InGaAs ダブルヘテロ接合パイポーラトランジスタ(DHBT: <u>Double-Heterojunction Bipolar Transistor</u>)集積回路の断面概略図を図3.17に示す[3.37]。DHBTのパッシベーションとメサの平坦化のためにBCB(Benzocyclobutene)膜を用いた。配線はTi/Pt/Auの2層配線とし、層間容量を低減するために厚さ1 μm のポリイミドを層間膜として用いた。抵抗はシート抵抗90 Ω のNiCr薄膜、容量は第1層配線-300 nm SiO<sub>2</sub>-第2層配線のMIM により構成している。試作したDHBTのエピタキシャル層構成を表3.3に示す。2インチ半絶縁性InP基板上に有機金属気相成長法(MOCVD: <u>Metal-Organic Chemical Vapor Deposition</u>)法により成長されたものである[3.37]。Chau et al. [3.38] が指摘しているように、InGaAsの熱伝導率がInPと比較して約1桁低いことに起因してInGaAsサブコレクタを用いた場合の接合温度はInPサブコレクタを用いた場合と比較して約50-100°C

図 3.17 InP/InGaAs DHBT 集積回路の断面構造(3.37)

表 3.3 InP/InGaAs DHBT の層構成[3.37]

| Layer        | Material                | Thickness (nm) |  |  |

|--------------|-------------------------|----------------|--|--|

| Emitter Cap  | n*- InGaAs              | 70             |  |  |

|              | N+- InP                 | 30             |  |  |

| Emitter      | N - InP                 | 70             |  |  |

| Spacer       | ud - InGaAs             | 5              |  |  |

| Base         | p*- In Gal-x As         | 45             |  |  |

| Collector    | ud - InGaAs             | 300            |  |  |

|              | N - InP                 | 20             |  |  |

|              | N'-InP                  | 100            |  |  |

| Subcollector | N*- InP                 | - 30           |  |  |

|              | n <sup>+</sup> - InGaAs | 20             |  |  |

|              | N+-InP                  | 430            |  |  |

| Buffer       | ud - InGaAs             | 20             |  |  |

|              | ud - InP                | 100            |  |  |

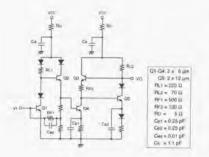

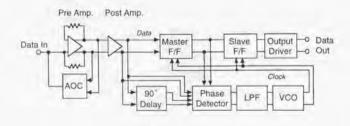

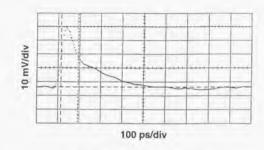

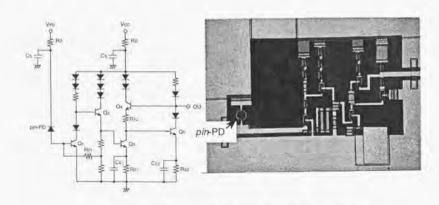

設計および試作した3 R機能回路の構成を図3.18に示す。回路は前置増幅器、自動オフセット 調整回路(AOC: Automatic Offset Controller)、後置増幅器、PLLによるタイミング抽出回路、識別器、出力ドライバから構成されている[3.42]。安定動作を得るため回路は差動構成とした。前置増幅器は通常のトランスインピーダンス型、後置増幅器はカスコード型とした。自動オフセット調整回路は、入力信号レベルが変化した時に入力に帰還をかけて差動出力の中心レベルが一致するようにするための回路である。PLLによるタイミング抽出回路は、90°遅延回路、位相比較器、低域通過フィルタ(LPF: Low-Pass Filter)、電圧制御発振器(VCO: Voltage-Controlled Oscillator)から構成され、非線形抽出方式と比較すると集積化に適した方式である[3.42]。出力ドライバ以外の部分にはエミッタ電極幅1.2 μm、エミッタ電極面積6 μm²の DHBT を用い、コレクタ電流を0.3 から3.5 mA として低電流化を図った。出力ドライバにはエミッタ電極幅2 μm、エミッタ電極面積20 μm²の DHBT を用いた。

図3.18 3 R機能回路の構成

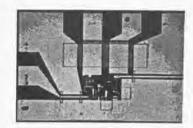

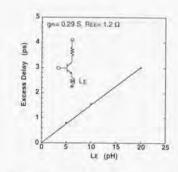

寄生成分の小さな高性能HBTを用いた回路の設計においては、デバイス問配線に伴う寄生効果 を考慮する必要がある。今、図3.19の挿入図に示すようにエミッタと直列に寄生インダクタンス  $L_c$ が付加された場合を考える。この $L_c$ は配線に起因するもので、本3R機能回路で用いた $4\mu m$ 配線では約1pH/µmと推定される。3.3.1に示したTien[3.18]の手法でインパータの遅延時間式を 導出すると、 $L_c$ がない場合と比較して $L_c$ ( $Ug_a+R_{cc}$ )だけ遅延が増加することが示される。回路シ ミュレータにより計算した過剰遅延時間のL。依存性を図3.19に示す。この過剰遅延時間を考慮し ないと帰還増幅器のループ遅延が予期した以上のものとなり図3.12に示したような利得のピーキ ング特性を示すようになる。これにより波形歪を生じアイバターン劣化を引き起こす。厳密に言 えばレイアウトバターンから寄生成分を抽出しバックアノテーションを行う必要があるが、設計 ツールの制限から、ここでは平均的な隣接デバイス間配線を含めてトランジスタと看做し、配線 に起因する過剰遅延を回路シミュレータ(HSPICE)のトランジスタバラメータ過剰位相推移 ptf に より表現することとした。なお、微細化、低電流化されたトランジスタでは低電力化とともに、 (1/g\_+R<sub>ev</sub>)が大きくなり過剰遅延が短くなるという利点があることに注意されたい。また、配線長 の長いプロック間配線を伝送線路モデルとして扱った。VCOの発振周波数の設計値は 19 から 21 GHz、PLLのロックレンジの設計値は350 MHzであった。試作した3R機能回路のチップ写真 を図3.20に示す。190の能動素子を含み、チップサイズは1.6 x 1.6 mm である。

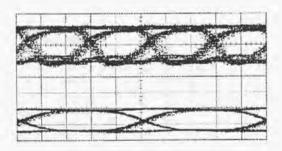

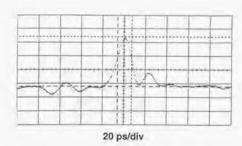

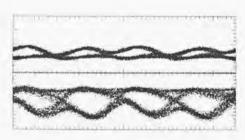

測定はオンウェハで行った。バルスパターン発生器(Anritsu製)からの 10 Gbit/s 疑似ランダム信号(符号長: 27-1)を 20 Gbit/s MUX(NEL製)により多重化し可変減衰器を介して 3 R機能回路に入力した。 3 R機能回路からの出力は 10 Gbit/s の識別器(NEL製)により分離し符号誤り率測定器 (Anritsu製)に入力した。 3 R機能回路からの 20 Gbit/s 信号および DEMUX された 10 Gbit/s 信号のアイパターンを図3.21に示す。入力ダイナミックレンジ 13 dB に渡ってエラーフリー動作を確

図3.19 寄生インダクタンスと過剰遅延の関係

認した。電源電圧 $V_{EE}=-5$  V の時、消費電力は 0.6 W であった。タイミングジッタ特性は必ずし も同一ではないが、10 Gbit/s 受信回路モジュール[3.33]と比較して約 1/40、2.4 Gbit/s 受信回路モジュール[3.43]と比較して約 2 桁の低エネルギー化の可能性が示された。後者のモジュールと本回路を比較すると、使用しているデバイスの $f_T$  と $f_{max}$ の向上により速度性能が約 1 桁向上し、モノリシック集積化により消費電力が約 1 桁低減している。

以上の結果から、微細化されたInP/InGaAs DHBT による 3 R機能回路のモノリシック集積化が 低エネルギー化に有効であることが実証された。

図3.20 3 R機能回路のチップ写真

図 3.21 3 R機能回路の出力アイパターン 横軸: 20 ps/div 上段: 3 R機能回路の出力 (0.4 V/div) 下段: DEMUX された波形 (1.0 V/div)

受信回路のうち電子デバイスにより構成される集積回路の高性能化について議論した。

最初に受信回路を構成する回路に対する要求性能を概観し、10 Gbit/s 増幅器モジュールを実現するために開発した技術を示した。ここでは、実装に付随する寄生容量および寄生インダクタンスを考慮に入れた安定性解析に基づく増幅回路とバッケージの一括設計法を明らかにした。GaAs MESFETによる広帯域増幅器、電圧制御可変減衰器、分配回路を開発したセラミックパッケージに実装して等化増幅モジュールを試作し、10 Gbit/s、最小入力振幅 15 mV の特性を得た。この等化増幅モジュールはNTTによる現場環境下での光伝送実験に使用され安定に動作することが確認された。これにより、10 GHz 帯域の増幅器、バッケージー括設計法が確立された。

次に、10 Gbit/s 以上の高速化を目指して、受信回路の基本回路であるペースバンド増幅器および識別器の動作速度とデバイス性能(電流利得遮断周波数と最大発振周波数)との関係を明確化した。 文献で報告されている識別器あるいは D タイプフリップフロップの最高動作速度および AlGaAs/GaAsへテロ接合バイポーラトランジスタを用いて試作したペースバンド増幅器の帯域とデバイス性能との関係より、提案したデバイス性能指数の妥当性を検証した。これにより、与えられた回路の動作速度を達成するために必要なデバイス性能指数を推定する簡便な方法が得られた。

最後に、低エネルギーな受信回路の実現を目指すためには高速化とともにモノリシック集積化による低消費電力化が必要であることを指摘した。高速化、低電力化に適したInP/InGaAsダブルヘテロ接合バイボーラトランジスタを用いて、前置増幅器、自動オフセット調整回路、後置増幅器、位相同期ループによるタイミング抽出回路、識別器から構成された 3 R機能回路を試作し、10 Gbit/s 受信回路モジュールと比較して約 1/40、2.4 Gbit/s 受信回路モジュールと比較して約 2 桁の低エネルギー化が可能であることを示した。後者のモジュールと本回路を比較すると、使用しているデバイスの $f_r$  と $f_{max}$  の向上により速度性能が約 1 桁向上し、モノリシック集積化により消費電力が約 1 桁低減している。

## 第4章

## 光電子混在回路シミュレーション手法

#### 概要

LSIの設計にCAD(Computer-Aided Design)ツールを用いることは当たり前のこととなっている。これに対して、光デバイス、光回路のCADは技術の習熟度が電子デバイスと比較して低いことと集積規模が小さいこと等から電子デバイスのCADほどには発展していない。光通信システム、さらには一般的な光電子融合システムを詳細に設計するためには、光デバイスと電子デバイスを一括してシミュレーションする必要がある。

本章は、SPICEに代表される電子回路シミュレータに相当する汎用的な光電子混在回路シミュレータを提供することを目的としている。受光回路の感度特性を厳密に求めるために、電子デバイスの時間領域雑音源を含むデバイスモデルを提案し、光デバイスとともに市販の混合モードシミュレータにユーザ定義モデルとしてインプリメントする。半導体レーザの応答、受光回路の感度特性等の実験と計算との比較により、提案したモデルの検証を行う。

#### 4.1 はじめに

光通信システムの設計においては、半導体レーザ、光ファイバ、受光デバイス、再生中継器等を各々一つのモデルで表現して全体をシミュレートするマクロレベルの設計法[4.1]を用いることが一般的である。このような設計法は、システム性能に対する部品性能の影響の把握あるいはシステム最適設計という点で有効なものである。一方、デバイスをより詳細にモデル化した設計手法について見ると、動作機構を反映した電流源、抵抗、容量によりトランジスタ等の能動デバイスを表現して電子回路をシミュレーションする方法が従来から用いられてきた。これに対して光デバイスのシミュレーションは、技術の習熟度が電子デバイスと比較して低いことあるいは集積規模が小さいこと等の理由から電子回路のシミュレーションほどには発展していない。すなわち、電子デバイスのデバイスシミュレーションに対応する半導体レーザ、光導波路のシミュレーションあるいは第2章で述べた受光デバイスのシミュレーションは活発に行われているが、回路レベルのシミュレーションの報告は少ない。特定の課題に対するアプローチとして、半導体レーザを直接変調した時に生ずる波長チャーピングとファイバ波長分散の光伝送に及ぼす影響の解析[4.2]あるいは多モード半導体レーザにおけるモード分配雑音の影響の解析[4.3]のようなレート方程式の数値計算が挙げられる。

光通信システムを詳細に設計するためには、光デバイスと電子デバイスを一括してシミュレーションする必要がある。さらに、光電子融合システムは将来、光通信だけでなく種々の領域に浸透してゆくものと期待されている。光電子融合システムの設計には光電子混在回路シミュレータが必須となろう。光電子混在回路シミュレーションの一つの試みとして、半導体レーザのレート方程式を電流源、抵抗、容量により等価的に表現して回路シミュレータ(SPICE)によりシミュレートする方法が提案されている[4.4]-[4.6]。このような試みをさらに発展させ、汎用的な光電子混在回路シミュレータを構築する必要がある。

光伝送系の性能はデバイスの雑音に大きく依存する。半導体レーザを直接強度変調した場合の立ち上がり時刻の揺らぎ(タイミングジッタ)により符号誤り率が劣化する[4.7]。また、受光回路の感度は等価入力雑音電流により決定される[4.8]。半導体レーザのタイミングジッタはランジュバン雑音源を含むレート方程式解析[4.9]により実験を良く説明できることが知られている[4.10] [4.11]。受光回路は主に小信号雑音解析により設計されているが、受光感度がデバイス雑音と符号間干渉作の複合効果により決まる場合には大信号解析が必要となる。つまり、光伝送系を厳密にシミュレートためには、雑音源を含むデバイスモデルを用いた大信号過渡解析が必要となる。

案し<sup>証力</sup>、市販の混合モードシミュレータにユーザ定義モデルとしてインプリメントする。4.2ではデバイスモデルについて述べ、4.3では実験と計算の比較によりモデルの妥当性を検証する。

#### 4.2 デバイスモデル

光中継器を構成する半導体デバイスとしてのレーザダイオード、受光デバイス、MESFET、 HFET、バイポーラトランジスタおよび抵抗のモデル、光伝送路としての光ファイバのモデル等に ついて示す。

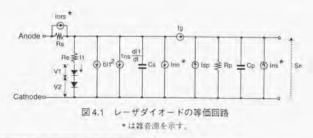

#### 4.2.1 レーザダイオード

レーザダイオードの電気的特性および発光特性はランジュバン雑音源を含むレート方程式[4.4] [4.5][4.9]により記述でき、等価回路表現すると図4.1のようになる。この等価回路のうち、電子および光子の雑音を表わす電流源  $I_{mc}$  と  $I_{nc}$  ならびに寄生抵抗  $R_{s}$  の熱雑音電流源  $I_{mc}$  を除いた部分は文献[4.4][4.5]と同一である。レート方程式は次の通りである。

$$I + I_{nes} = I_1 + bI_1^2 + \tau_{ns} \frac{dI_1}{dt} + \frac{dQ_s}{dt} + I_g + I_{nn}$$

(4.1)

$$I_g + I_{sp} = \frac{S_n}{R_p} + C_p \frac{dS_n}{dt} + I_{ns}$$

(4.2)

記号の意味を付録 C.1 に示す。ここで、寄生抵抗  $R_r$  の熱雑音電流源  $I_m$  を次式で表現する。

$$I_{ner} = \sqrt{\frac{4k_BT}{R_s\Delta t}} r_s \tag{4.3}$$

性が半導体レーザの雑音モデルは既に提案されているもの[4.9]と同一である。

以上の課題を解決するため、電子デバイスについて時間領域雑音源を含むデバイスモデルを考

<sup>&</sup>quot;" 波形のリンギング等による隣接ビットへの影響を符号間干渉と呼ぶ。

ただし、rは正規乱数である。

規格化された光子密度が図 4.1 の右端の "ノード間電圧" として得られる。光子密度 S(t) と出力光パワー W(t) との関係は次の通りである。

$$W(t) = \frac{\eta_{id} V_a S(t) h \nu}{2 \Gamma \tau_p}$$

(4.4)

ここで、 $\eta_{ii}$ は微分量子効率、 $V_o$ は活性領域の体積、 $\Gamma$ は光閉じ込め係数、 $\tau_p$ は光子寿命である。 レーザダイオードを直接強度変調する場合にはチャーピングを考慮する必要がある。光の位相 は次の微分方程式により記述される[4.2]。

$$\frac{d\phi}{dt} = \frac{\alpha}{2} \left[ \Gamma v_g a_g (n - n_{th}) - \frac{1}{\tau_p} \right]$$

(4.5)

ここに、 $\alpha$  は線幅増大係数、 $v_s$  は群速度、 $a_s$  は利得係数、 $n_s$  は利得が正になる電子密度である。

#### 4.2.2 受光デバイス

受光デバイスとして MSM-PD と pin-PD を扱うこととする。その等価回路を図 4.2 に示す。第 2章で示したように、光通信に使用される場合には受光パワーが小さいため、空間電荷領域の形成効果を考慮しなくても良い近似が得られる。ここでは、その効果を無視することとする。電流源  $l_{vi}$  は暗電流  $l_{vi}$  と光電流の和であり、次式で与えられる。

$$I_{pd} = I_{daik} + \frac{q}{I_a} \left( N v_n + P v_p \right) \tag{4.6}$$

ここで、NおよびP は電子と正孔の総数、 $v_n$  と $v_p$  は電子および正孔の速度である(付録C.2)。 寄生抵抗の熱雑音電流は式(4.3)により与えられ、ショット雑音  $I_{nod}$  は次式により与えられるものとする。

$$I_{opd} = \sqrt{\frac{2qI_{pd}}{\Delta t}}r_{p} \tag{4.7}$$

ここで、アルは正規乱数である。

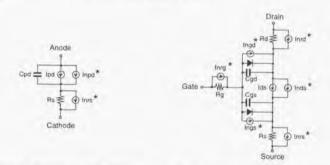

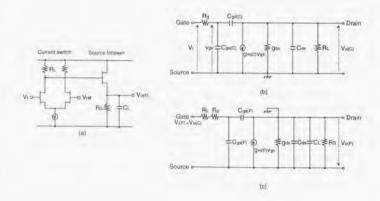

#### 4.2.3 MESFET および HFET

MESFET と HFET の等価回路を図4.3 に示す。ドレイン電流およびゲート容量モデルとして、 MESFET についてはCurticeモデル[4.14]を、HFET についてはYeager-Duttonモデル[4.15]を基本として、時間領域雑音電流源を付加している。寄生抵抗の熱雑音とゲート電流のショット雑音に関する表式は、各々、式(4.3)と式(4.7)と同様である。ドレイン電流の雑音電流は次式で与えられる。

$$I_{nds} = \sqrt{\frac{8k_BTg_m}{3\Delta I}}r_d$$

(4.8)

ここで、 $g_m$  は相互コンダクタンス、 $r_d$  は正規乱数である。

図 4.2 受光デバイスの等価回路

図 4.3 MESFET と HFET の等価回路

## 4.2.4 バイポーラトランジスタ、ダイオードおよび抵抗

帰還増幅器の設計においては相互コンダクタンスの位相遅れを考慮することが重要である。ここでは、位相遅れを考慮したChen[4.16]のモデルに時間領域雑音電流源を付加している。また、従来のダイオードおよび抵抗モデルにも時間領域雑音電流源を追加する。

#### 4.2.5 光ファイバ

光ファイバへの入力光電界と出力光電界の関係は次の畳み込み積分で記述される[4.2]。

$$E_{out}(t) = E_{in}(t) * h_f(t)$$

(4.9)

ここに、h,(n)は光ファイバのインパルス応答であり、次式で与えられる。

$$h_f(t) = \eta \sqrt{\frac{c}{2\lambda^2 DL}} (1 - j) \exp\left(-j\pi \frac{c}{2\lambda^2 DL} t^2\right)$$

(4.10)

ただし、c は光速、 $\lambda$  は波長、D は波長分散パラメータ、L はファイバ長、 $\eta$  は伝搬損失と結合損失を含めた係数である。

#### 4.2.6 光変調器

ここでは簡単のため次式により強度変調のみをモデル化する。

$$P_{max}(t) = \eta_{EM} P_{mr}(t) \sin^2 \left[ \frac{\pi V(t)}{2V_{\pi}} \right]$$

(4.11)

ここに、 $\eta_{EM}$  は結合損失等を表す係数、V(r)は印加電圧、 $V_{\mu}$ は半波長電圧である。

### 4.2.7 パルスパターン発生器

バルスパターン発生器(PPG)のモデルは疑似ランダムパターン発生部とRC低域通過フィルタより構成する。

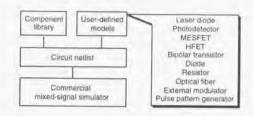

### 4.2.8 シミュレータへのインブリメント

以上述べたような新しいデバイスモデルを用いてシミュレーションを行う方法として考えられることは、これらのモデルを扱えるようにSPICE等の既存回路シミュレータのソースコードを書換える方法である。しかしながら、市販の回路シミュレータはバージョンアップされることが一般的であり、その都度新規モデルに対応する部分のソースコードを修正することは骨の折れる作業である。したがって、シミュレータ本体に触れることなく新しいデバイスモデルを扱える市販シミュレータを用いることが好ましい。ここでは、その一例として混在モードシミュレータSABER™[4.17]を用いることとした。シミュレータ全体の概略構成を図4.4に示す。上記モデルは全てMAST\*プログラミング言語[4.17]で記述している。

図 4.4 シミュレータ全体の概略構成

### 4.3 シミュレーションと実験との比較

モデルの妥当性を検証するために、実験とシミュレーションの比較を行った。

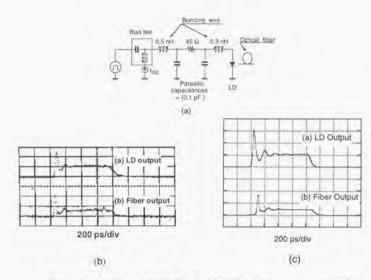

最初の比較はレーザダイオードと光ファイバについて行った。実験に用いたレーザは、液長 1.55  $\mu$ m、しきい値電流 15  $\mu$ m のMQW DFB レーザであり、光ファイバの総分散量は波長 1.55  $\mu$ m において -140  $\mu$ m である。光パルスは帯域 40 GHz の PD(New Focus 製)とサンプリングオシロスコーブ(HP 製)により観測した。シミュレートした回路を図 4.5(a)に示す。レーザのパラメータは、レーザ形状と通常使用される値[4.4]-[4.6]をもとに、電流一電圧特性、電流一光パワー特性、光波形の実験値と計算値が一致するように調整した。パイアス電流を 20  $\mu$ m とし、1 Gbit/s NRZ 固定パターン(1010...、振幅 2  $\mu$ m で直接変調した時のレーザの出力波形と光ファイバ伝送後の光波形の実測と計算結果を図 4.5(b)(c)に示す。実験と計算は良く一致している。なお、この比較では雑音は考慮されていない。

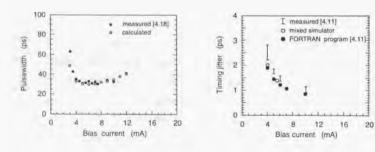

次に、波長  $1.3 \, \mu m$  のDFB  $\nu$  ーザのタイミングジッタ[4.11]について実験とシミュレーションの比較を行った。シミュレーションに用いた回路は図4.5(a) と同様である。電気バルス発生源は、振幅 8 V、バルス幅 100 ps のコムジェネレータとした。レーザパラメータの導出は上記と同一であり、文献[4.11]のものとほぼ同一である。図4.6(a)に光パルス幅のバイアス電流依存性を示す。計算値は実測値[4.18]と良く一致している。なお、この解析では雑音を無視している。次に、雑音を考慮して立上り時のタイミングジッタを計算した。図4.6(b)に計算結果を実測値と比較して示す。図中の $\bullet$ は文献[4.11]に示されている計算値である。バイアス電流  $5.5 \, \text{mA}$  以下では実験値との良い一致が得られた。バイアス電流  $6 \, \text{mA}$  ではタイミングジッタが  $0.1 \, \text{ps}$  程度となり一致しなかった。ここで示したモデルは基本的には文献[4.11]のものと同一であるから、不一致の原因としては 混在シミュレータの中での数値的な切捨て等が考えられる。

図 4.5 (a) シミュレートした回路 (b) 実測波形 (c) シミュレーション波形

図 4.6 (a) 光パルス幅のパイアス電流依存性 (b) タイミングジッタのパイアス電流依存性

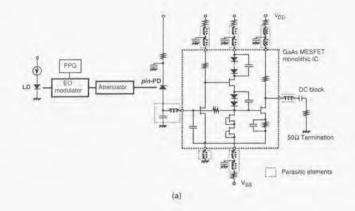

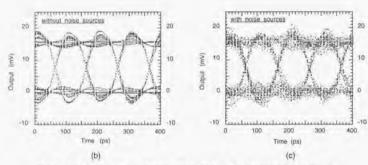

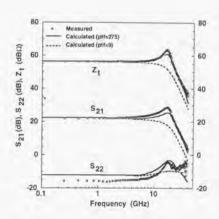

受光デバイスと電子デバイスの過渡雑音モデルを検証するために、図4.7(a)に示す受光回路のシミュレーションを行った。バルス発生器 PPG からの 10 Gb/s NRZ (符号長: 2<sup>7</sup>-1) の疑似ランダムバターンにより CW 光を変調した。接合容量 0.18 pF、量子効率 56 %、暗電流 2.2 nA の pin-PD により減衰した光信号を光電気変換し、GaAs MESFETのトランスインピーダンスアンブ 回により増幅した。MESFETのバラメータは電流一電圧特性と S バラメータの実測値と計算値が一致するように調整した。実装時のボンディングワイヤの寄生インダクタンスを考慮した。図4.7(b)(c) に雑音を考慮しない場合と考慮した場合のアイバターンのシミュレーション結果を示す。雑音を考慮することにより現実感のあるアイバターンが得られる。

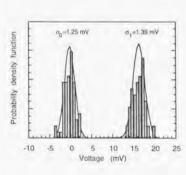

各タイムスロットの中央でサンプリングした出力電圧の確率密度分布を図4.8に示す。図4.7(b) に示されるように出力波形には若干のパターン依存性が見られるため、確率密度を複数のガウス分布で近似するのが妥当であるが、ここでは簡単のため単一のガウス分布で近似してみる。ガウス分布近似により符号誤り率を計算することができる[4.8]。光パワーを変化させることにより、図4.9に示すような符号誤り率特性が得られる。符号誤り率が10°における受光パワーは-15.7 dBmである。これに対して、10 Gb/s NRZ(符号長:2<sup>21</sup>-1)の疑似ランダムパターンについての実験値は-14.5 dBmであった[4.19]。実験と計算の差はビット長の違いあるいは寄生インダクタンスの見積り誤差等に起因するものと考える。伝送システムの設計には、より厳密な符号誤り率推定法が必要となると考えられるが、これについては今後の課題とし、ここでは詳細な議論は行わないこととする。

HFETとパイポーラトランジスタについては実験とシミュレーションの比較を行っていないが、 雑音源にはMESFETと同一の式が用いられている。したがって、ここで示したデバイスモデルの 妥当性が検証されたと言える。なお、シミュレーションに要する計算時間は、図4.7(c)の場合、HP-Apollo Model 720 上で 2500 秒であった。

<sup>(3.2</sup>で述べた後置増幅器とほぼ同一のものである。

図 4.7 (a) シミュレートした回路 (b) 雑音を考慮しない時のアイパターン (c) 雑音を考慮した時のアイパターン

図 4.8 出力電圧の確率密度分布

図4.9 符号誤り率特性

### 4.4 まとめ

光デバイスと電子デバイスの混在する回路を詳細に設計するためのツール開発を目的として光電子混在回路シミュレーション手法について研究を行った。

時間領域雑音源を含む電子デバイスモデルを考案し、半導体レーザ、pin-PD、MSM-PD、光ファイバ等とともに市販の混合モードシミュレータにインプリメントした。直接変調した半導体レーザ出力波形、光ファイバ伝送後の波形、半導体レーザのタイミングジッタ、GaAs MESFET 増幅器とpin-PDから構成されたハイブリッド受光回路の受光感度等について、シミュレーション結果と実験結果を比較しモデルの妥当性を検証した。本シミュレーション手法は光伝送システムのみならず将来の光電子融合システムの設計に有効であると考えられる。

# 第5章

# 集積化受光回路の高速化設計

### 概要

集積化受光回路はハイブリッド回路の速度性能限界を打破する技術とし注目され、種々のデバイス・回路構成が提案されてきた。しかしながら、集積化受光回路に用いられている電子デバイスの性能が電子デバイス専用のデバイス性能より劣るため、その速度性能はハイブリッド回路の性能より劣るものであった。

本章では、InP/InGaAs ハテロ接合パイポーラトランジスタ(HBT)の製造工程を何ら変更することなく形成が可能な pin-PD/HBT 構成により集積化受光回路の高速化が可能であることを示す。最初に、理論検討により高速化に適したデバイス・回路構成が HBT のベースーコレクタを用いた pin-PD と HBT トランスインピーダンス増幅器であることを明らかにする。次に、InP/InGaAs シングルヘテロ接合パイポーラトランジスタ(SHBT)により集積化受光回路を試作し、その速度性能がホモ接合 pin-PD の帯域に制限されることを示す。この課題を解決するために、InP/InGaAs ダブルヘテロ接合パイポーラトランジスタ(DHBT)を用いた集積化受光回路を提案し、その動作速度を最大とする最適なコレクタ層の厚さを明確化する。最後に、最適設計された集積化受光回路によりハイブリッド受光回路の最高速度に匹敵する 40 Gbit/s 動作の可能性を示す。

### 5.1 はじめに

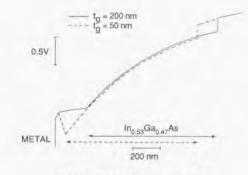

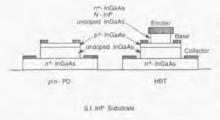

長斯維米通信用中継装置にはハイブリッド受光回路が用いられてきた。しかしながら、動作周 波数が高くなると、受光デバイスと前置増幅器との間の接続に付随する寄生容量や寄生インダク タンスが帯域制限の要因となり得る。このようなハイブリッド受光回路の速度性能の限界を打破 する技術として集積化受光同路が注目され、研究が活発に行われている。しかしながら第1章で 述べたように、その速度性能はハイブリッド回路の性能(帯域 33 GHz [5.1])より劣っている。こ のハイブリッド回路の性能を考慮すると、集積化受光回路が速度メリットを発揮できる周波数領 域は 40 GHz 以上になると予想できる。第3章で述べたように、一般に用いられているトランス インピーダンス型前置増幅器により帯域 40 GHz を実現するためには、電流利得遮断周波数ある いは最大発振周波数が 200 GHz 程度の高性能な電子デバイスを必要とする。いままでに提案され ている集積化受光回路用電子デバイスにより 200 GHz 程度の性能を実現することはかなり困難で ある。一方、希土類ドープ光ファイバ増幅器(EDFA)の進展により、受光感度に対する要求は軽減 される傾向にある。したがって、量子効率を多少犠牲にしても、高性能電子デバイスの製造工程 を何ら変更することなく受光デバイスを形成できる構成を選択することが合理的であると考える。 電子デバイスの製造工程に完全整合する長波長系集積化受光回路の構成は、HBTのベースーコ レクタ層を pin-PD として用いる構成[5,2]-[5.4]あるいは HBT を受光デバイス(HPT: Heterojunction Phototransistor)として兼用する構成[5.2]である。シングルヘテロ接合 HBT(SHBT)を用いる場合、 pin-PD はホモ接合となる。ホモ接合 pin-PD の 3dB 帯域として、i-InGaAs 層の厚さが 0.3 μm の時 に 2.8 GHz 15.31, 0.6 um の時に 20 GHz 以上15.41の値が報告されている。これらの値は通常の pin-PDについての解析式[5,7]では説明できない特性であり、帯域とi-InGaAs層の厚さとの関係は明 確でない。Chandrasekhar et al. [5,2] は、InP/InGaAs DHBTに整合したpin-PD/HBTおよびHPT/HBT 構成の集積化受光回路を試作して両者とも同等の性能であることを報告しているが、いずれの構 成が高速化に適しているのか理論的には明らかとなっていない。また、これらのHBTでは高速化 とコレクタ耐圧のトレードオフを解決できず。Chandrasekhar et al. [5.2] の DHBT では i-InGaAs コレクタ層とm-InPサプコレクタ層のヘテロ接合界面でのキャリアの蓄積のためHBTおよびpin-PD の高速化が期待できない。以上のように、InP/InGaAs HBT 製造工程に完全整合する集積化受 光回路の高速化に関する指針は得られていない。

ここでは、InP/InGaAs HBT 集積化受光回路の高速化のための指針を明確化する。

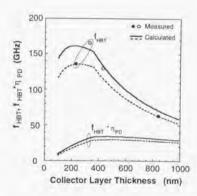

5.2ではpin-PD/HBTとHPT/HBTの構成の比較と通常のpin-PDの理論的帯域をもとに高速化のための基本的なアプローチを示す。5.3ではInP/InGaAs SHBT 製造工程により集積化受光回路を試作し、ホモ接合pin-PDの簡単なモデル計算によりその性能限界を明確化する。5.4では集積化受光回路の高速化に適したInP/InGaAs DHBTを提案し、集積化受光回路の動作速度を最大にする最

適なコレクタ層の厚さを明確化する。最後に、最適設計された集積化受光回路により 40 Gbit/s 動作の可能性を示す。

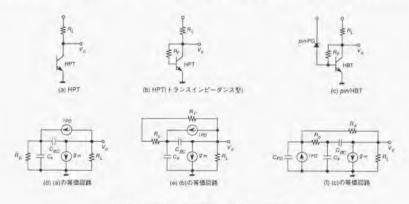

# 5.2 InP/InGaAs HBT 集積化受光回路の基本構成[5.23]

最初に、pin-PD/HBTと HPT/HBTのどちらの構成が望ましいのかについて議論してみる。簡単 化のため、図5.1(a)-(c)に示す受光回路について動作速度の比較を行ってみる。(a)はベースをフロー ティング状態とした通常の HPT の用い方である。(b)はベースに帰還を掛けたものである。図 5.1 (d)-(f)の等価回路について節点方程式を解くことにより、トランスインピーダンスの表式を導出す る。得られた式から極の時定数を求めると、各々の回路に対して以下の式のようになる。

$$\tau_p = R_\pi [C_\pi + (1 + g_m R_L)C_{BC}]$$

(for (a)) (5.1)

$$\tau_{p} = \tau_{f} + \frac{(R_{F} + R_{h})[C_{\pi} + (1 + g_{m}R_{L})C_{BC}]}{g_{m}R_{L}}$$

(for (b)) (5.2)

$$\tau_{p} = \tau_{f} + \frac{(R_{F} + R_{b})[C_{\pi} + (1 + g_{m}R_{L})C_{BC}] + R_{F}C_{PD}}{g_{m}R_{L}}$$

(for (c)) (5.3)

すべてのパラメータの値が構成によらず同一であるとすれば、回路(b)の方が回路(c)よりpin-PDの寄生容量  $C_{po}$ の寄与分だけ高速であることが式(5.2)と(5.3)から理解できる。しかしながら、典型的な HBT のエミッタ幅は  $2\,\mu m$ 、ベースメサの幅も  $4\,\mu m$  程度であり、入射光ビームをこのよう

図 5.1 比較した受光回路の構成と等価回路

を微細な領域に位置決めすることは実用上得策とは言えない。したがって、pin-PDとHPTの受光面積を同一(ここでは  $10 \times 10 \ \mu m$ )として比較することにする。計算に用いたパラメータの値を表 5.1 に示す。HBT の接合容量  $C_{IB}$ 、 $C_{RC}$  は後述する実験に用いたトランジスタのものと同一とし、HPTの接合容量はHBTのものに対して面積比を乗じた値としている。直流におけるトランスインピーダンスの値は回路構成によらず同一とする。これらの値は、回路(b)と(c)については $R_p$ で、回路(a)については電流増幅率と負荷抵抗の積  $\beta R_L$ で与えられる。また、ベース抵抗 $R_g$  は $R_p$  と比較して無視できるほど小さいとする。各時定数とトランスインピーダンスの関係を図5.2に示す。回路(c)が最も高速であることがわかる。トランスインピーダンスが小さい場合、回路(a)の時定数は  $R_g C_g$  が支配的であるため、ほぼ一定となる。また、 $80 \ \mathrm{dB}\Omega$  を越える高トランスインピーダンス領域においては、回路(b)よりも回路(a)の方が高速である。以上のように、pin-PD/HBT 構成が高速化に有利であると言える。このため、この構成に絞って検討を進めることとする。

表 5.1 比較のために用いたパラメータ値

| Parameter                   | Unit       | HPT      | HPT (Transimpedance) | pin/HBT                     |

|-----------------------------|------------|----------|----------------------|-----------------------------|

| Size                        | (µm)       | 10 x 10  | 10 x 10              | 10 x 10 (pin), 2 x 10 (HBT) |

| i pp                        | (µA)       | 30       | 4                    |                             |

| $R_{\pi} = v_{ih} / i_{PD}$ | $(\Omega)$ | 862      | -                    | 4                           |

| β                           |            | 100      |                      | *                           |

| 8 m                         | (S)        | 0.116    | 0.116                | 0.116                       |

| $g_m R_L$                   |            | variable | 10                   | 10                          |

| $R_F$                       | (Ω)        |          | variable             | variable                    |

| T <sub>j</sub>              | (ps)       | 1.0      | 1.0                  | 1.0                         |

| $C_{JE}$                    | (pF)       | 0.55     | 0.55                 | 0.11                        |

| Cr                          | (pF)       | 0.67     | 0.67                 | 0.23                        |

| CBC                         | (fF)       | 45       | 45                   | 9                           |

| $C_{PD}$                    | (fF)       |          |                      | 30                          |

図 5.2 時定数とトランスインピーダンスの関係 (a)(b)(c)は図 5.1 の回路(a)(b)(c)に対応。

次に、Bowers et al. [5.7]のモデルを用いて計算した表面入射型 pin-PD の帯域と InGaAs 光吸収層の厚さ  $W_a$  との関係を受光面の直径 d をパラメータとして図 5.3 に示す。 10 GHz を実現するためには  $W_a$  を 1  $\mu$ m、d を 40  $\mu$ m とすれば良い。表面入射型 pin-PD の高速化のためには、 $W_a$  と d を 小さくする必要があり、40 GHz の帯域を得ようとすれば $W_a$ は0.3  $\mu$ m程度になる。この厚さはHBT のコレクタ層と同程度であり、HBT製造工程に整合した集積化受光回路により高速化を追究できることを意味している。

図5.3 表面入射型 pin-PD の帯域と InGaAs 光吸収層の厚さの関係

# 5.3 InP/InGaAs SHBT を用いた集積化受光回路の課題

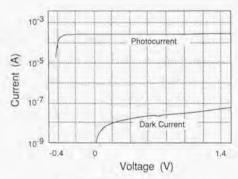

# 5.3.1 InP/InGaAs pin-PD/SHBT 集積化受光回路の試作[5.15]

InP/InGaAs SHBTのデバイス構造の概略を図5.4に、エピタキシャル層構成を表5.2[5.8]に示す。このSHBTは、第3章で示したHBTと同様に自己整合プロセス[5.9]により製造される。すなわち、エミッタ電極をマスクとしてエミッタ層をエッチングする。この時エミッタメサの寸法がエミッタ電極の寸法より小さくなるようにオーバーエッチングを行う。この状態でベース電極を蒸着すると、エミッタとベースがショートすることなく形成される。コレクタについても同様である。したがって、SHBTのエミッタ電極パターンを削除すると、図5.4に示したようにInGaAs pin-PDが必然的に形成される。ただし、この pin-PD は通常のものと異なりホモ接合構造である。

試作したHBTの電流利得遮断周波数 $f_T$ と最大発振周波数 $f_{max}$ のピーク値は各々  $162~{

m GHz}$  と  $90~{

m GHz}$  であった[5.8]。pin-PD の測定は波長  $1.3~{

m \mu m}$  の DFB レーザ[5.10]、RF プローブ、光ブローブ (Cascade Microtech 製)を用いてオンウェハで行った。接合サイズ  $50~{

m x}$   $50~{

m x}$   $50~{

m m}$  m pin-PD の電流一電

表5.2 エビタキシャル層構成

| Layer        | Material   | Thickness |