博士論文

High-frequency organic thin-film transistors for conformable large-area electronics

(コンフォーマブル大面積エレクトロニクスの ための高周波有機薄膜トランジスタ)

**Reuveny Amir**

## Abstract

#### Background

Organic thin-film transistors (OTFTs) are one of the most important building elements to realize large-area flexible electronics. Recent material advancements allow organic transistors to be environmentally and thermally stable and provide good electrical performance. This progress enabled the fabrication of electronic circuits for practical applications, such as displays and processing units. High frequency operation of single devices and oscillators could also be demonstrated on thick plastic foils. In addition to their improved electrical properties, the mechanical flexibility and conformability of such devices can be improved by reducing the thickness of the base films. Organic elements manufactured on ultrathin substrates can provide smaller bending radii and better conformability to complex objects including human skins.

Despite the impressive development of organic electronics, no demonstration for large area electronics that provides both excellent conformability, large bandwidth (cutoff frequency > 100 kHz) and good uniformity (~10% device variation) has been made yet. Organic transistors on thin films suffer from narrow bandwidth due to limited scaling methods and inherently low carrier mobility. So far, only low frequency OTFTs and circuits were demonstrated on ultrathin and conformable substrates. Thermally stable organic devices could be achieved only by the use of specific transistor structure on rather thick plastic foils. Uniformity of organic transistors over large area is another main issue towards reliable implementation of practical applications.

#### Objective

In this study we develop a novel method for fabrication of high frequency organic transistors and circuits on large area and ultrathin foils, which shows high degree of uniformity, mechanical and environmental stability. The technology is based on the fabrication of high performance, short channel OTFTs in the bottom contact architecture to enhance devices bandwidth in low operation voltages. We aim to demonstrate large area compatibility on ultrathin substrates to enable the realization of future conformable sensor sheets for wearable or implantable devices.

#### Method

Our method for devices improvement towards reliable and conformable OTFTs is based on three main principles, demonstrated simultaneously for the first time in this study:

#### - Substrate thickness

Reduction of the base film down to ~1  $\mu$ m thick substrates, allows devices to conform to any three-dimensional object. Small device thickness also facilitates the stress applied on the transistors and enhances their mechanical flexibility.

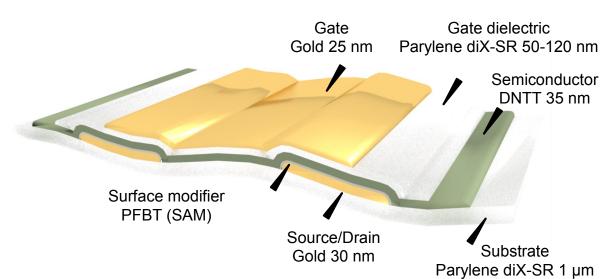

# - **Bottom contact structure** The bottom contact structure allows reliable high resolution patterning using photolithography to increase transistor's cutoff frequency.

## - Vapor deposited polymeric gate dielectric

The choice of flexible vapor deposited polymeric gate dielectric allows uniform device performance and ultrathin, pinhole free interface with the organic semiconductor for reduction of operation voltage.

We utilized those principles in our device fabrication and discuss their effect on device performance.

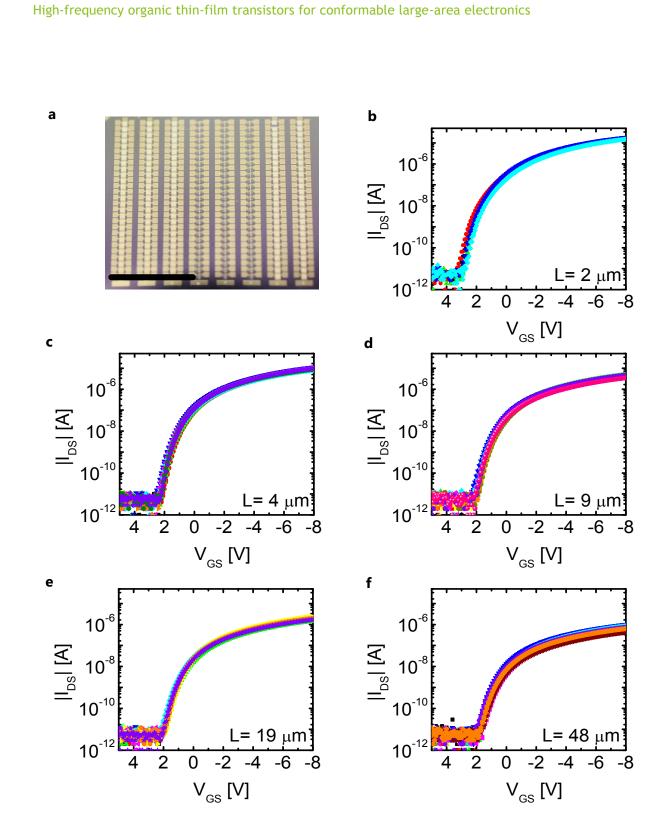

First, we adapt photolithography to be used on ultrathin parylene diX-SR foils and fabricate OTFTs for the first time using this technology on 1  $\mu$ m substrates. By utilizing the bottom contact architecture we pattern channel lengths down to 2  $\mu$ m to realize air stable, dinaphtho[2,3-b:2 '3'-f]thieno[3,2-b]thiophene (DNTT) based OTFTs. We improve device performance by applying contact modification techniques using pentafluorobenzenethiol (PFBT) self-assembled-monolayer (SAM) and optimize mobility with different deposition conditions. We compare this method to other available contact modification techniques and discuss the challenges when applying to ultrathin films.

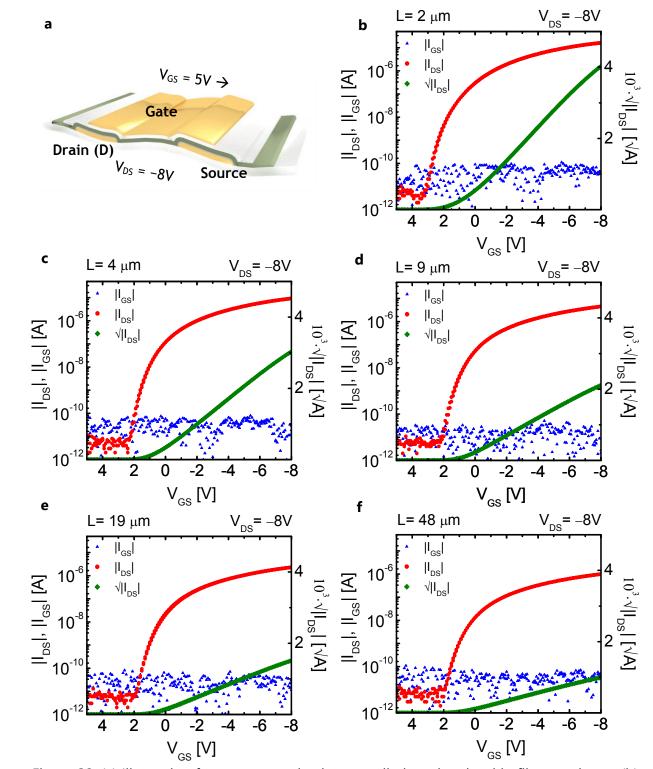

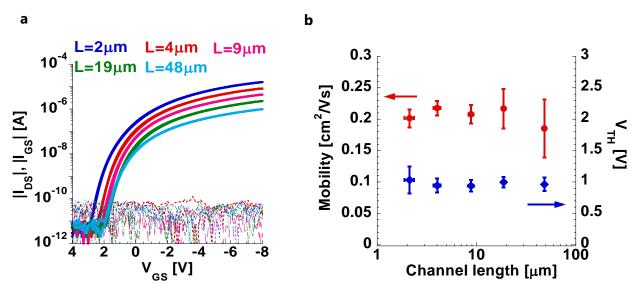

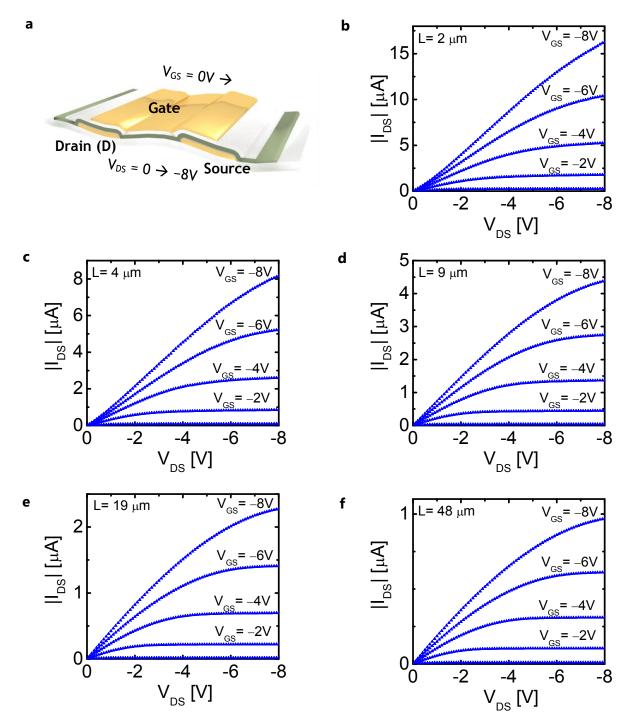

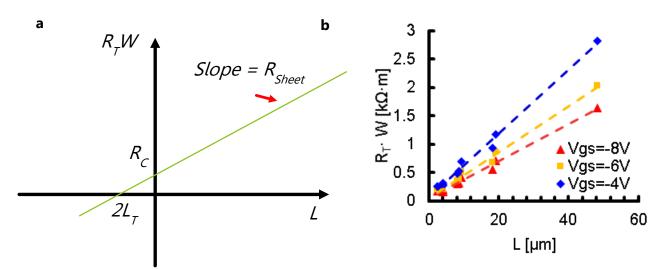

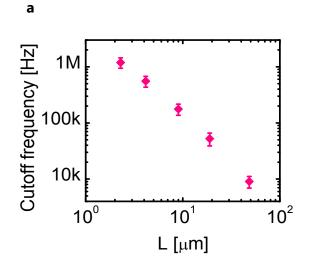

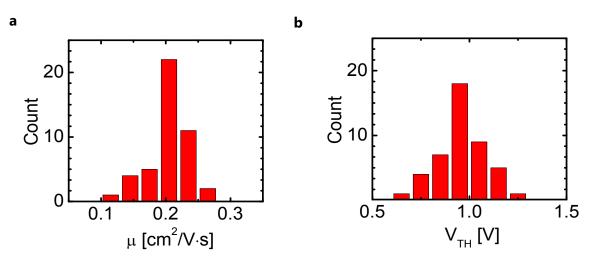

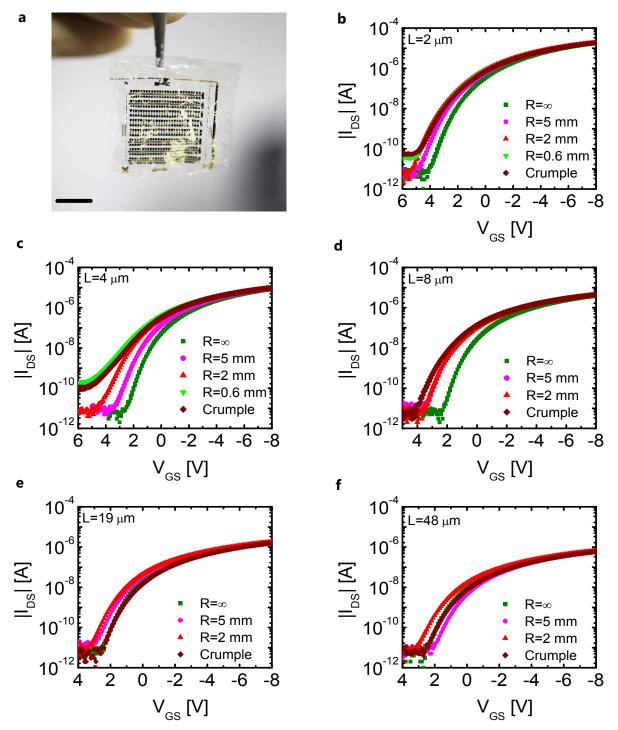

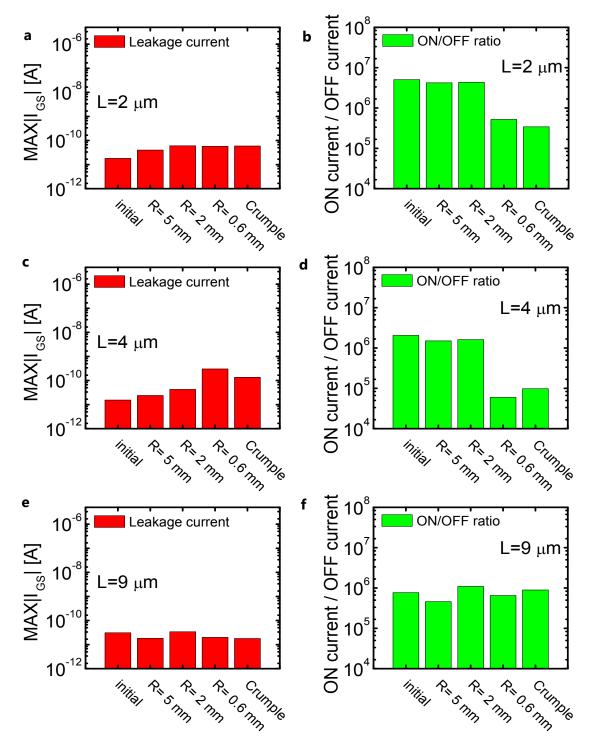

Second, we perform thorough electrical device characterization and analyze important OTFT parameters. Thanks to the effective contact modification we could realize saturation mobility of ~0.2 cm<sup>2</sup>/V·s for short channel transistors (~2  $\mu$ m channel length) in bottom contact architecture with transfer length of only 1  $\mu$ m. The obtained contact resistance in our devices was found to be 5.5 k $\Omega$ ·cm which is comparable to top contact devices with the same materials. The fine patterning method allowed us to reduce the overlap capacitance of less than 0.5 pF per channel were achieved. High ratio between ON and OFF currents of 10<sup>7</sup> was demonstrated which is important for practical sensing applications. We could reduce operation voltage down to 8V by reduction of dielectric thickness to less than 100 nm and still keeping leakage current lower than 100 pA during transistor operation. Theoretical and measured transistor cutoff frequency exceeded 100

kHz on ultrathin foils. We discuss the successful results in light of the top gate architecture implementation and fabrication technique.

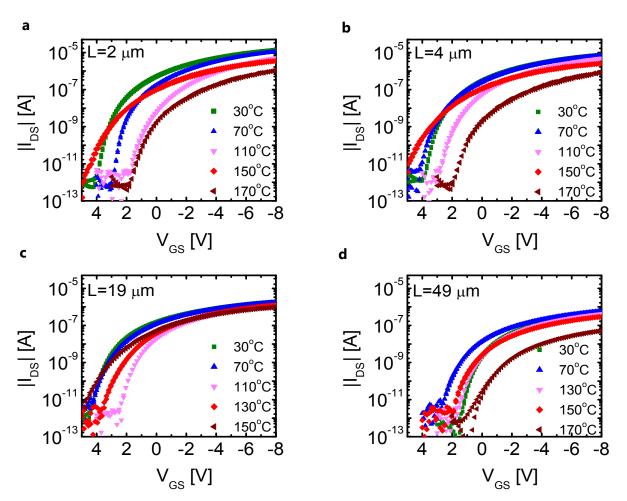

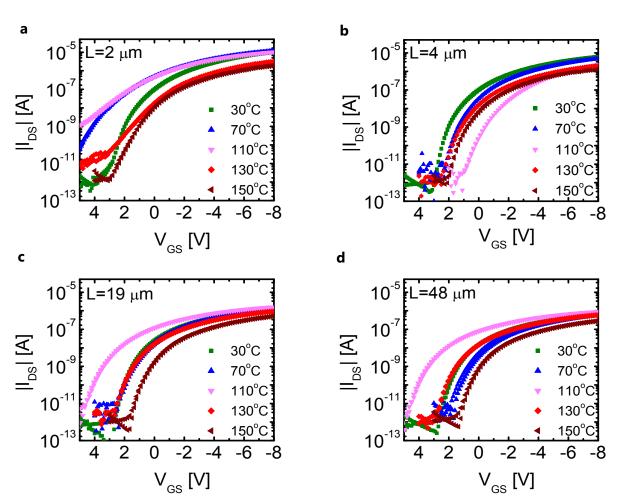

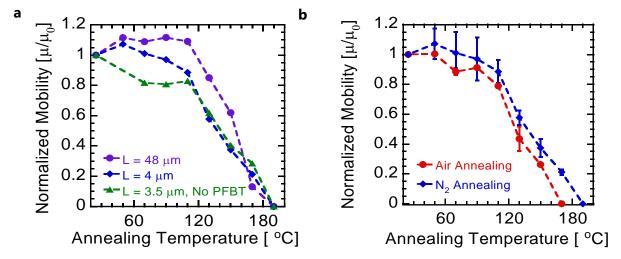

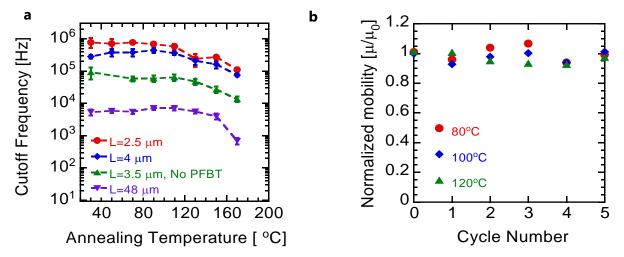

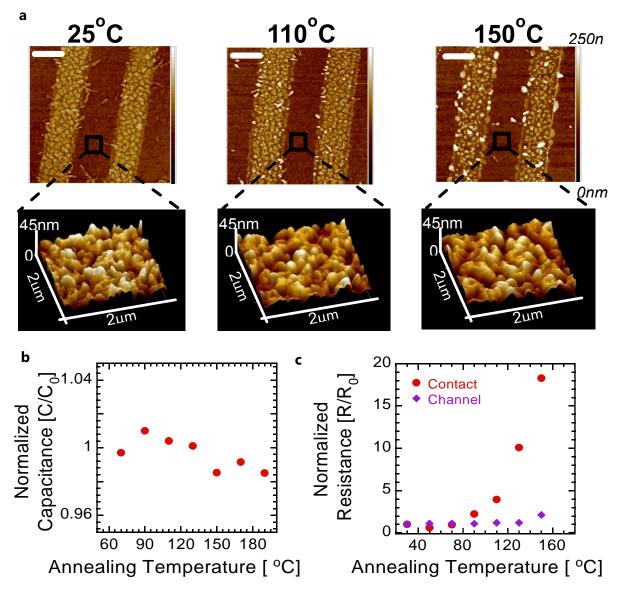

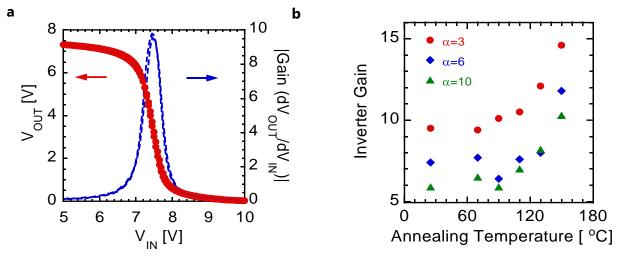

Further stress characterization were conducted on the ultrathin devices. Transistors were tested under severe mechanical bending and crumpling and showed good durability against the mechanical stress. While only 2  $\mu$ m thick, devices could be rolled down to 600  $\mu$ m bending radius and be crumpled several times with showing practically no degradation in performance (< 10% in mobility). We discuss the theoretical considerations in applying stress on the bottom contact structure in the ultrathin form. Additionally, we evaluated devices environmental stability by performing thermal annealing tests. We showed that ultrathin OTFTs in the bottom contact structure could endure heating up to 170°C in N<sub>2</sub> and 150°C when annealed in air. We provide evidence to cyclic stability of those devices after repeated annealing steps. We calculated that thanks to the short channel implementation, cutoff frequency of devices could be kept above 100 kHz even after annealing at 170°C. We analyze the changes in channel and contact resistances and by electrical and topological means,

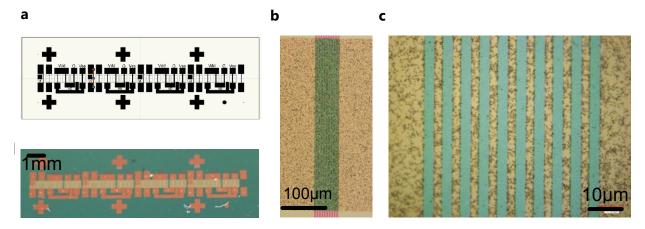

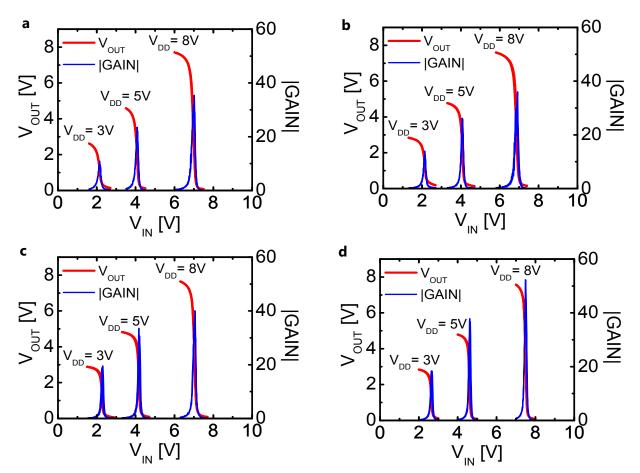

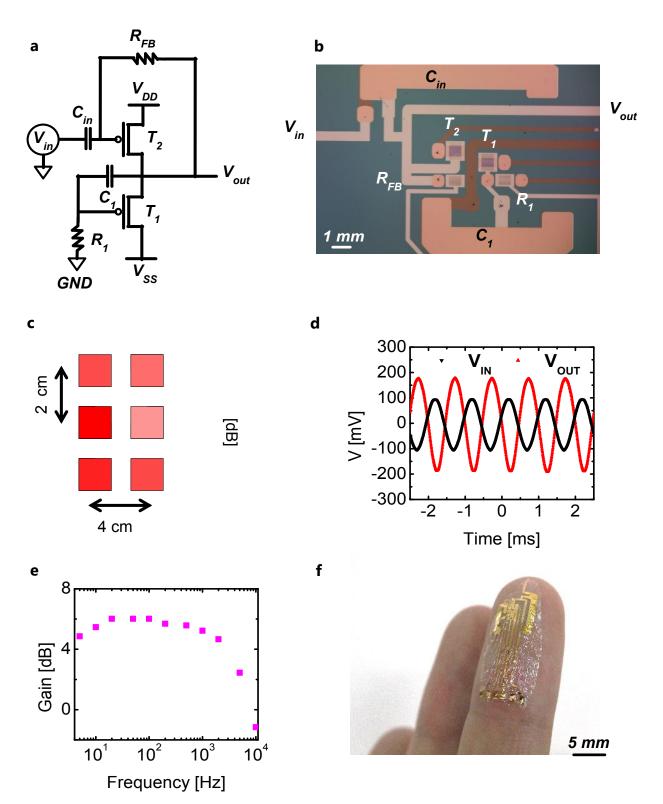

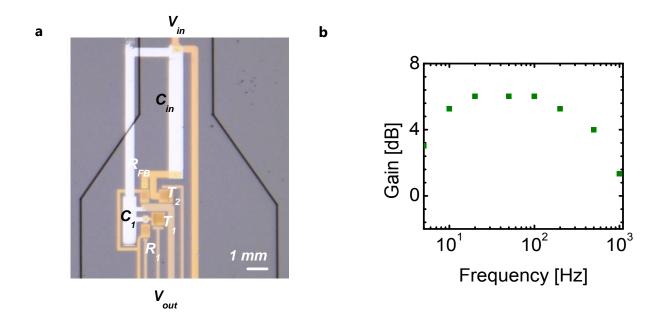

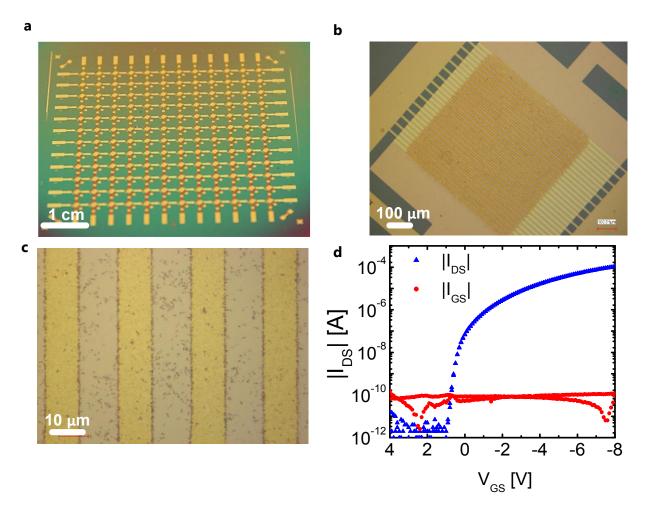

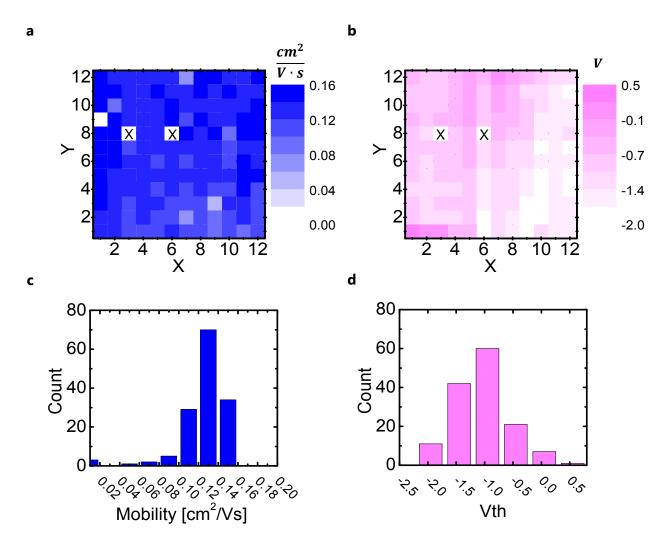

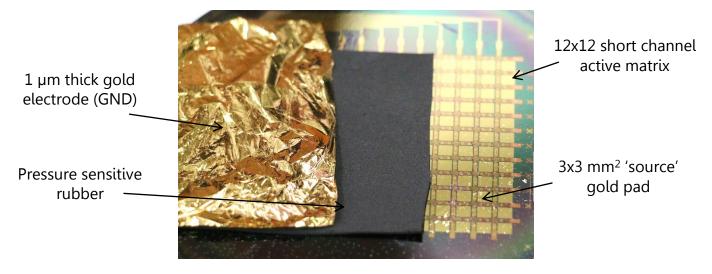

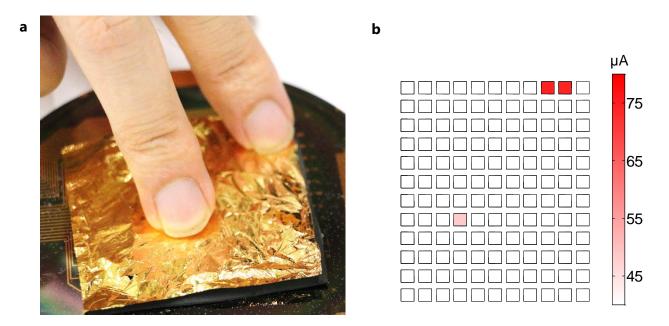

Finally, we demonstrate the reliability of our OTFTs by the realization of electrical circuits and large area active matrix. We designed and successfully fabricated pseudo-CMOS inverters with gain of as high as 30 dB. We also showed that inverter gain can be improved by at least 150% after simple post annealing step at 150°C. Organic amplifier with improved frequency response of up to 25 kHz ( $f_{3dB}$ ) and 45 kHz unity gain could be achieved in the AC coupled architecture. For the closed loop design we added parylene capacitors in total active area of 45 mm<sup>2</sup>, which achieved constant frequency response of from 3Hz to 3kHz. By integrating our devices with aluminum-oxide capacitors (~500 nF/cm<sup>2</sup>) we reduce effective amplifier area to only 15 mm<sup>2</sup> which is suitable to implementation for high resolution sensing devices. Integrated amplifiers showed a closed loop gain of ~6 dB and stable operation between 5Hz-700Hz. The large area uniformity of our devices was successfully demonstrated by the fabrication of 6x6 cm<sup>2</sup> transistor array which showed excellent yield (98.6% out of 144 transistors) and only 0.019 cm<sup>2</sup>/V·s standard deviation from the average value of 0.12 cm<sup>2</sup>/V·s. The transistors were used as a large area pressure sensor to demonstrate their applicability.

#### Summary

We have successfully demonstrated the highest frequency OTFTs reported on ultrathin films (~1  $\mu$ m) in the bottom contact architecture. Channel patterns down to 2  $\mu$ m length with cutoff frequencies greater than 1 MHz were realized. Using ultrathin parylene diX-SR gate dielectric, we could maintain low voltage operation for our devices. OTFTs showed excellent durability to mechanical and thermal stress thanks to our design and material selection. Transistors reliability was demonstrated by the fabrication of ultrathin inverters

and amplifier circuits, showing record high bandwidth (25 kHz) for a single organic amplifier. The smallest organic closed-loop amplifier (15 mm<sup>2</sup> of active area) was realized by integrating the transistors with AlOx capacitors, presenting uniform gain up to 700Hz. Excellent uniformity (~15% of mobility standard variation) and device yield (98.6%) was realized on 36 cm<sup>2</sup> active matrix with 144 transistors, utilized as an ultrathin pressure sensor.

## Table of Contents

| Abstract 2                                                            |

|-----------------------------------------------------------------------|

| 1 Introduction                                                        |

| 2 Organic Thin Film Transistors (OTFTs)14                             |

| 2.1 Architecture                                                      |

| 2.2 Operation modes                                                   |

| 2.2.1 OFF state                                                       |

| 2.2.2 Linear regime                                                   |

| 2.2.3 Saturation regime                                               |

| 2.2.4 Subthreshold regime                                             |

| 2.3 Characterization                                                  |

| 2.3.1 Transfer characteristics                                        |

| 2.3.2 Output characteristics21                                        |

| 2.3.3 Cutoff frequency22                                              |

| 3 Material and Methods24                                              |

| 3.1 Ultrathin plastic foils                                           |

| 3.2 Organic semiconductor                                             |

| 3.3 Gate dielectric                                                   |

| 3.4 Photolithography                                                  |

| 3.4.1 Process principles                                              |

| 3.4.2 Application to ultrathin films                                  |

| 3.5 Vapor deposition                                                  |

| 3.5.1 Basic principles                                                |

| 3.5.2 Physical vapor deposition (PVD)43                               |

| 3.5.3 Chemical vapor deposition (CVD)46                               |

| 3.5.4 Application to ultrathin polymer films47                        |

| 4 Short Channel Organic Transistors on 1 $\mu m$ Thick Film           |

| 4.1 Contact modification                                              |

| 4.1.1 O2 plasma treatment                                             |

| 4.1.2 Pentafluorobenzenethiol (PFBT) self-assembled-monolayer (SAM)51 |

| 4.1.3 PFBT and substrate heating55                                    |

| 4.1.4 PFBT and $O_2$ plasma treatment                                 |

| 4.1.5 PFBT and ultraviolet-ozone treatment58                          |

| 4.1.6 Triptycene                                                      |

| 4.1.7 Summary61                                               |

|---------------------------------------------------------------|

| 4.2 Electrical device characterization64                      |

| 4.2.1 Optimized structure and process64                       |

| 4.2.2 Transfer characteristics                                |

| 4.2.3 Output characteristics69                                |

| 4.2.4 Frequency response71                                    |

| 4.2.5 Transistors uniformity                                  |

| 4.3 Discussion                                                |

| 5 Mechanical Stress Evaluation                                |

| 5.1 Bending tests                                             |

| 5.1.1 Apparatus                                               |

| 5.1.2 Electrical evaluation83                                 |

| 5.1.3 Bending orientation                                     |

| 5.1.4 Characteristics summary87                               |

| 5.2 Discussion                                                |

| 6 Thermal Stress Evaluation                                   |

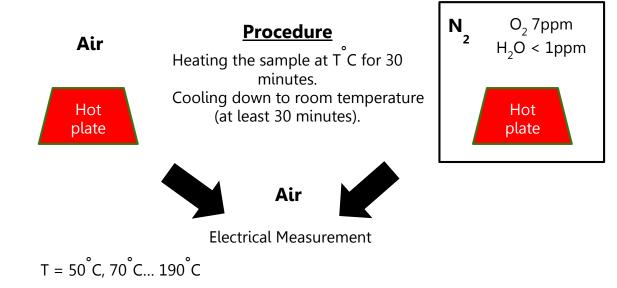

| 6.1 Thermal stability tests94                                 |

| 6.1.1 Apparatus                                               |

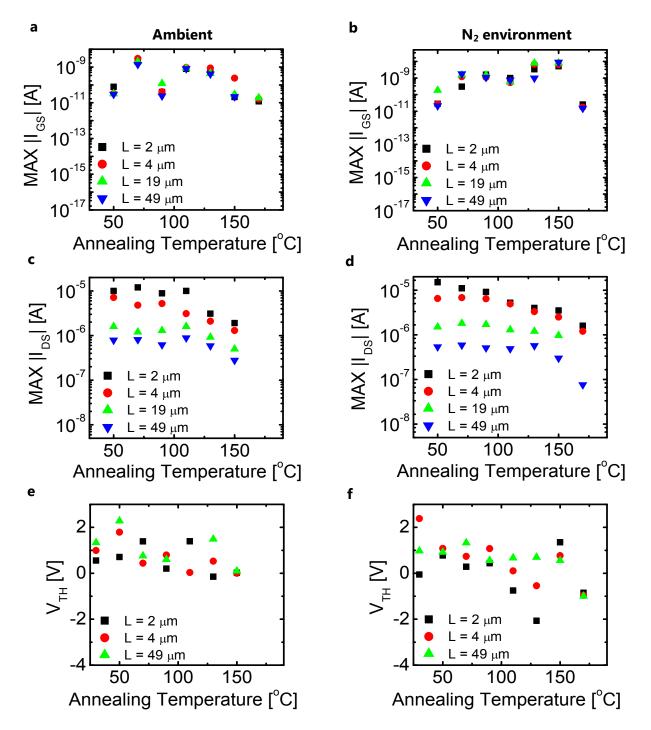

| 6.1.2 Electrical characterization - Air Vs. $N_2$ environment |

| 6.1.3 Analysis                                                |

| 6.2 Discussion                                                |

| 7 Ultrathin circuits                                          |

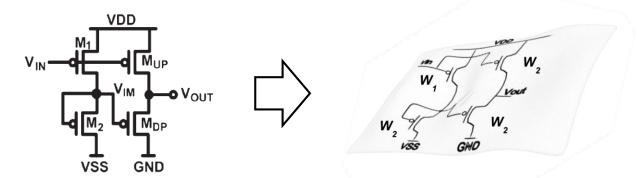

| 7.1 Pseudo-CMOS architecture105                               |

| 7.1.1 Circuit design                                          |

| 7.1.2 Inverter fabrication106                                 |

| 7.1.3 Post-annealing gain enhancement108                      |

| 7.1.4 Threshold voltage control by double gate structure      |

| 7.2 Amplifier fabrication113                                  |

| 7.2.1 AC coupled amplifier113                                 |

| 7.2.2 Fabrication on ultrathin film115                        |

| 7.2.3 Design optimization119                                  |

| 7.2.4 Closed loop ultrathin amplifier122                      |

| 8 Large area application126                                   |

| 8.1 Active matrix                                             |

| 8.2 Large area pressure sensing sheet129                      |

High-frequency organic thin-film transistors for conformable large-area electronics

| 9 Summary and Outlook | 131 |

|-----------------------|-----|

| 10 Acknowledgments    | 134 |

| 11 References         | 137 |

## 1 Introduction

Organic field effect transistors have made a tremendous progress since they were first reported in 1987 [1]. By important process and material improvements, organic transistors have made their way outside from research labs into the commercial, practical world of applications. Organic solar cells [2,3], organic light emitting diodes (OLEDs)[4,5] and organic logic units [6,7] were successfully demonstrated and are now available for the benefit of users around the world. According to recent forecast, the market of organic electronics has a compound annual growth of (CAGR) of 29.5% until 2020 with an expected value of 79.6 billion USD [8]. Within this market, OLED is estimated to have the largest share (about 2/3 of the market) where system components (such as logic and memory) will compose the second largest portion, reaching 20% of the total revenue.

Organic electronics are attractive due to several important factors. First, organic devices are very flexible. The flexibility of devices is originated from the molecular structure of the active semiconducting material. The organic semiconductor is constructed from conjugated molecular chains that are connected to each other by weak van der Waals bonds. Conduction mechanisms occur by an interplay between charge carrier hopping and band transport [9]. The relatively weak bonding between molecules allow the material to be more flexible and less brittle when mechanical stress is applied. Second important advantage of organic devices is their processability. Organic materials can be deposited by low cost per area procedures and at relatively low temperatures [10]. These properties allow fabrication of organic devices over large areas and on wide variety of surfaces. Substrates such as papers, bank note and large area plastic foils [11–15] could be successfully used as the base film for organic device fabrication.

Recently, based on the unique properties of those device, a new branch of organic electronics was proposed – the imperceptible electronics [16]. Imperceptible electronics describe functional electronic devices that are deposited on ultrathin substrates (roughly 1/30 thinner than a human hair) and can be used for many purpose in an unnoticeable manner. The substrates in use are usually plastic foils (such as polyethylene naphthalate, polyethylene terephthalate and poly(p-xylylene)) in thicknesses that do not exceed a few micrometers. In a very short period of time, great development was made in this field and devices such as active matrices [16,17], organic photovoltaic cells [18], organic electrochemical sensors [19] and circuits [20] could be realized on those ultrathin films. Inorganic and oxide electronics devices can also be transferred onto such films [21,22] however the organic counterparts carry the advantage of direct fabrication at low temperatures and in lower cost per area.

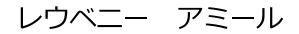

Naturally, the application of organic imperceptible electronics to large-area sensor sheets have attracted much attention, presenting promising features as the next-generation wearable and implantable devices. The basic principle behind those devices is

to allow signal detection - such as thermal, electrical or mechanical - by certain proximity to the monitored object [23]. The detected signal is often translated into electrical signal and transmitted for further processing. In order to provide reliable signal detection the

Figure 1: A conceptual image of intimate electronic devices, presenting ultrathin conformable sensor and an interactive light-emitting touch panel on human skin [23].

sensor arrays should satisfy several conditions. First, the arrays should be large enough and conformable to the monitored object to provide intimate proximity. Good signal-tonoise ratio is of utmost importance for this purpose and can be improved by 'on-site' active amplification. Additionally, devices should be mechanically and environmentally stable to prevent degradation over time and operate in low voltages for efficient energy consumption. Lastly, sensors' amount and their resolution should also be considered, depending on the application. Fast multiplexing large number of signals form sensors is important to provide real-time monitoring of objects.

One the challenges in making large area sensors from organic materials is their limited bandwidth. Transistors' frequency response is closely related to the frequency of signals from sensors (e.g. neural signal at ~1 kHz) and to multiplexing large number of signals from a composed device. Although organic devices have improved their field effect mobility by few orders of magnitudes in the last 28 years and surpass values of amorphous silicon [9], they still present relatively low speed of charge carrier transport, caused by their polycrystalline structure. One of the methods to overcome this problem and improve transistors bandwidth is to reduce their dimensions, i.e. channel length and parasitic overlap ( $f_T \propto 1/L^2$ ). Many groups have tried to improve those properties by various methods [24–28], however there is still a trade-off between the scaling methods,

fabrication complexity and device performance, which is caused by the sensitive organic semiconductor and the application of aggressive scaling methods on plastic foils. So far, there was no demonstration of high frequency (>100 kHz) organic transistors on ultrathin films.

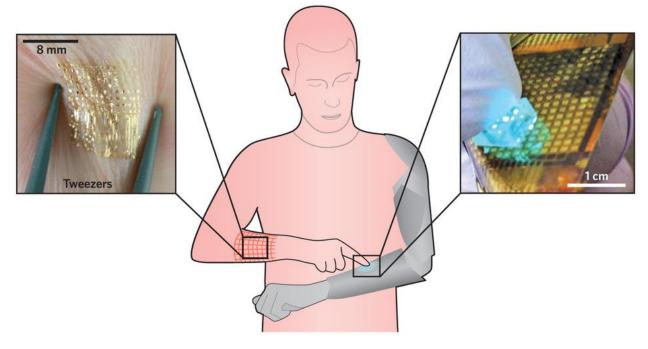

In this research we will challenge the scaling methods of organic transistors on

Figure 2: (a) Demonstration of the lightweight of an ultrathin active matrix. Scale bar is 1 cm [16]. (b) Illustration of the potential of large area, imperceptible sensor arrays for health monitoring. Scale bar is 4 cm [17].

ultrathin films in order to improve their frequency response. The materials and methods in this study will be chosen to allow the fabrication of reliable imperceptible electronic devices to be used as large area sensor sheets. Operation voltage, device stability and uniformity will be considered as well for the practical implementation of our method.

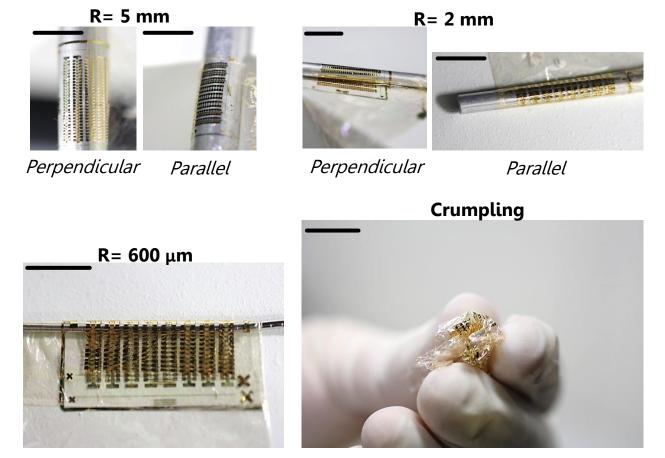

The thesis is constructed as follows: in Chapter 2 and Chapter 3 , we start with describing the background of the organic transistor structure and analysis, following by the materials and methods required for fabrication. We elaborate on our selection for device exploration. In Chapter 4 we give details on single transistor fabrication in the bottom contact architecture. The transistor structure is optimized on ultrathin films, emphasizing the contact resistance issue in our device structure. Several methods are considered and experimented. The optimized design is thoroughly analyzed for its electrical properties. Device mobility, contact resistance, ON/OFF ratio, device uniformity and other important transistors properties are studied. The fabrication results are discussed in light of the specific methods and the application on ultrathin films. Chapter 5 describes the transistors behavior upon mechanical bending stress. We bend the ultrathin devices down to small bending radii (600  $\mu$ m) and crumple the transistors several times

to verify their durability. We test OTFTs with several channel lengths and compare their performance. Different bending orientations are also evaluated. The successful results are theoretically analyzed by calculating the stress on the device in its ultrathin form. In Chapter 6 we report on the high thermal stability of our devices, when annealed up to 170°C. Comparative study of devices annealed in air and N<sub>2</sub> environment is conducted as well as detailed inspection of behavior of different channel lengths. We show that the theoretical cutoff frequency of devices can be maintained above 100 kHz even when annealed at high temperatures. In addition, transistors can show good cyclic stability after several thermal cycles. Surface topology and transistor resistance values during heating are investigated to clarify the change in devices. Chapter 7 illustrates the reliability and uniformity of our technology by the demonstration of several organic electronics circuits. Pseudo-CMOS inverters are designed and fabricated with high gain on ultrathin films. We also optimize the design and manufacturing of an AC coupled organic amplifier. Amplifier gain can range between 5-15 dB and  $f_{3dB}$  can reach 25 kHz. The total device area can be minimized to only 30 mm<sup>2</sup> by the integration of AlOx capacitors. In Chapter 8 we demonstrate a large area application of our fabrication method by fabricating 36 cm<sup>2</sup> active matrix. The active matrix exhibits high device yield with uniform mobility and threshold voltage, which verifies the successful achievement of a reliable technique for large area, bottom contact transistors on ultrathin foils.

## 2 Organic Thin Film Transistors (OTFTs)

Organic thin film transistors (OTFTs) are one of the most important building blocks of organic electronics. With a relatively simple operation model and structure they provide useful mechanism for implementing wide range of applications with organic materials, such as flexible displays, pressure sensors, amplifiers and more [29–31]. In this chapter we will review some of the essential design principles, operation modes and characterization methods of this influential unit.

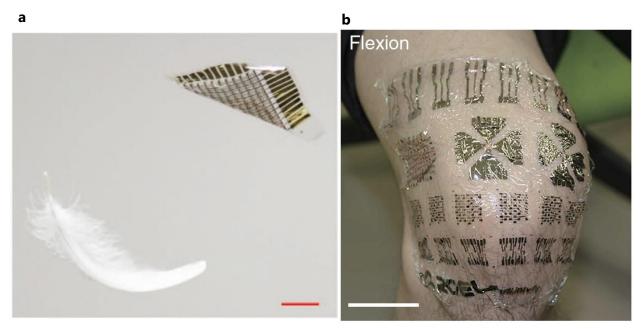

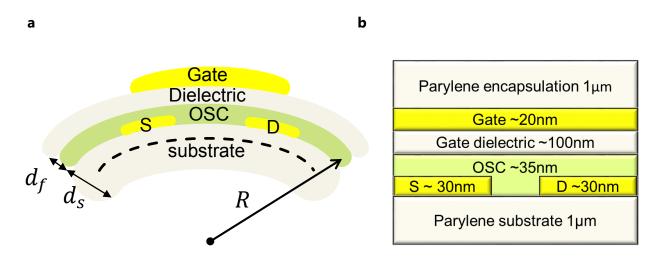

#### 2.1 Architecture

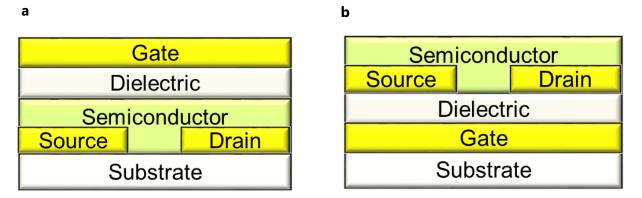

The organic thin film transistor has four main design architectures, namely the bottom gate – top contact, bottom gate – bottom contact, top gate – top contact and top gate – bottom contact (*Figure 3*). The names bottom and top contacts are derived from the position of the contacts in relation to the semiconductor. The architectures can also be distinguished by their channel location in relation to the source and drain: coplanar (such as the bottom gate – bottom contact and top gate – top contact) and staggered (such as the bottom gate – top contact and top gate – bottom contact). All design layout are based on a three terminal transistor structure with gate, source and drain electrodes. In addition organic semiconductor and gate dielectric are deposited as thin films.

Although the OTFT carries some similarities to the conventional metal-oxidesemiconductor field-effect-transistor (MOSFET), the OTFT operates in a different manner. The organic thin film transistor works only in the accumulation mode, where the current is produced by the majority carriers. By applying electrical field from the gate electrode, the organic semiconductor (which will be discussed in detail in section 3.2 ) changes its holes or electrons concentration in the channel. For example, a negative bias on p-type organic semiconductor (holes are majority carriers), holes are accumulated in the channel area. The change in carrier concentration modifies the channel conductivity between the source and drain electrodes. If conductivity becomes high enough (transistor is 'ON'), additional voltage on the two other terminals (the source and the drain) can modulate the current flowing through the device.

The transistor architecture has an immense effect on the manufacturing process and device operation of the OTFT. The thin film transistor is built by stacking metals, organic and inorganic layers on top of each other and each layer patterning method and characteristics are influenced by its predecessor. Properties such semiconductor quality, patterning resolution, energy level barriers and others are affected by the order of layer deposition and the interaction between them. In the following paragraphs we will discuss several considerations and issues related to the OTFT architecture.

Figure 3: (a) bottom gate – top contact, (b) bottom gate – bottom contact, (c) top gate – top contact and (d) top gate – bottom contact. OTFT design. Channel length (L) and contact length ( $L_c$ ) are denoted. Modified from [10].

One of the most important layers interplay is the contacts-semiconductor interface. For example, in bottom contact structures where the semiconductor is deposited after the source and drain pattern, larger process window for metal patterning. Processes such as photolithography or e-beam lithography can be implemented and smaller channel dimensions can be achieved [32,33]. Such methods are more difficult to implement on top contact devices due to the organic semiconductor's sensitivity to solvents and high energy procedures [34]. Additional consideration for semiconductor deposition is the surface energy of the underneath layer. Deposition on high surface energies is often disadvantageous for small molecules semiconductor growth and results in worse device performance [35]. In this case, metal electrodes with high surface energy can degrade charge carrier transportation on contact area in the bottom contact structure. Another interesting aspect related to the OTFT layout is that staggered structures are less sensitive to energy barriers between metal and semiconductor than the coplanar structure [36–38]. In addition surface modification of top gate – bottom contact (Figure 3d) shows better modification by self-assembled-monolayer than the bottom gate - bottom contact (Figure 3b) due to better surface orientation [39]. This gives an important advantage to utilize this

structure for high performance thin film devices. Mechanical durability of devices can also be affected by device structure on flexible films where the metal contacts can be delaminated from the semiconductor during bending [40].

Similarly, the gate dielectric deposition should also be compatible with the semiconductor and previous TFT layers. The thickness of the dielectric plays an important role in determining the operation voltage and leakage current of the device. The gate dielectric – semiconductor interface is very important for parameters such as threshold voltage, device hysteresis and charge carrier mobility. In top gate structures, the use of specific solvents for solution processed gate dielectrics can also degrade the semiconductor. In case of bottom gate structures, surface roughness and energy of the dielectric (and previous layers) should be considered for semiconductor nucleation and quality [38]. Deposition of gate dielectrics by high energy processes (such as chemical vapor deposition of silicon oxide) should be avoided on top of flexible substrate or organic semiconductors [10]. By adopting the bottom gate structure, thin oxides can be deposited on top of metals to provide very thin dielectrics with good insulating properties [41]. During device operation, effect of gate dielectric layer was found to be very important for device durability against mechanical strain in the top contact structure [42].

In summary, the OTFT design is significant for device operation and the selection of materials and methods for fabrication. Interfaces between the layers and growth mechanisms affect charge transport and transistor's performance. Device layout influences the effective charge injection area and surface modification quality to enhance device performance. Device design is also an important consideration for durability against external mechanical stresses. Finally, patterning methods should be selected carefully in the specific design to prevent damage to the already patterned layers.

#### 2.2 Operation modes

Similarly to MOSFET, the organic thin film transistors has three main operation regimes: cutoff, linear and saturation. For sake of simplicity we will analyze those regions in the case where the semiconductor is p-type, meaning that holes are the majority carriers. As mentioned earlier, the OTFT is based on the accumulation of charge carriers in the channel as a result of gate bias.

## 2.2.1 OFF state

The first transistor state we analyze is the transistor's OFF state. This state is based on the low conductivity of the semiconductor under positive (or no) gate bias. When no (or small positive) voltage is applied, the organic material shows high resistivity. In this case, if small drain voltage ( $V_{DS}$ ) exists, the conductivity of the film ( $\sigma$ ) and channel dimensions

determine the current between the source and the drain (I<sub>DS</sub>), according to the simple film resistivity model [43]:

(1)

$$I_{DS} \cong \sigma V_{DS} \frac{L}{W \cdot t}$$

where L, W is the channel length and width respectively and t is the semiconductor thickness. We define this condition as the transistor <u>OFF</u> state where the channel shows very high resistivity and low currents.

#### 2.2.2 Linear regime

The conductivity of the channel can be enhanced by applying negative gate voltage on the metal-insulator-semiconductor (MIS) structure. When applying a negative bias to the gate, accumulation of majority carriers (holes in the p-type semiconductor) occur in proximity to the semiconductor-insulator region in order to compensate the total charge in the metal-insulator interface. The conductivity of the channel becomes significant when the gate voltage is larger (more negative) than a threshold voltage (V<sub>TH</sub>) which represents the energy level difference between the metal and semiconductor and the charge carrier density in the semiconductor [44]:

$$V_{TH} = 2\varphi_B + \frac{Q_{sc}}{C_i}$$

Here  $\varphi_B$  is the gap between the gate work function and the semiconductor Fermi's level (the value 2  $\varphi_B$  is also defined as the flat-band voltage V<sub>FB</sub>), Q<sub>SC</sub> is the charge carrier density in the semiconductor and C<sub>i</sub> the gate-dielectric capacitance per area. The accumulation creates an area in the semiconductor with charge density approximated as C<sub>i</sub>(V<sub>GS</sub>-V<sub>TH</sub>). When V<sub>DS</sub> is small enough ( $|V_{DS}| < |V_{GS}-V_{TH}|$ ), the drain-source current can be represented as [45]:

(3)

$$I_{DS} = \frac{W}{L} \mu C_i (V_{GS} - V_{TH}) V_{DS}$$

Here we introduce an important transistor parameter, the mobility ( $\mu$ ), which represents the relation between the drift velocity and the electric field in the semiconductor. This figure of merit is essential for the evaluation of charge carrier transportation in the channel:

(4)

$$\mu = \frac{v_{drift}}{E}$$

The drain current is directly proportional to the drain voltage and this regime is defined as the <u>linear</u> state of transistor operation.

#### 2.2.3 Saturation regime

This state may be changed by further increasing the drain-source voltage. The drainsource voltage creates a potential gradient in the channel. The channel potential in channel location x is defined as V(x) and equals to the drain voltage near the drain and similarly, to the source voltage in the vicinity of source port. The charge density in the channel would be proportional to the value  $|V_{GS}-V(x)|$ . Thus, an increase of the drain voltage to the value  $V_{DS}=V_{GS}-V_{TH}$  yields the threshold potential (VTH) near the drain and to the creation of low charge density in this region. This state is called channel 'pinch-off', due to the low conductivity channel area near the drain. In this case, further increase of drain voltage would not (ideally) increase the drain-source current and the current through the ports is denoted by [45]:

(5)

$$I_{DS} = \frac{W}{2L} \mu C_i (V_{GS} - V_{TH})^2$$

In this state, the drain-current is saturated in regard to the drain-source voltage and this regime is defined as the <u>saturation</u> regime of transistor. The saturation current will be referred in this thesis as the ON current of transistor.

Ideally, the mobility in the linear and saturation regimes should be equal but in practice, especially in the case of organic semiconductor, this value may be different between the two operation regions. Phenomena such as gate-dependent mobility, short channel effects and contact resistance differ the values between the linear and saturation states [46–48].

#### 2.2.4 Subthreshold regime

In the linear and saturation operation, we analyzed the transistor when  $V_{SG}>V_{TH}$  and the drain voltage is increased. Here we analyze the operation in a different manner. In case we fix the drain voltage to its saturation value ( $V_{DS}=V_{GS}-V_{TH}$ ) and sweep the gate voltage from  $V_{SG}<V_{TH}$  to  $V_{SG}>V_{TH}$  we encounter a different conduction mechanism in the channel. In this scenario, the current depends exponentially in the gate-source voltage [49]:

$$I_{DS} \propto e^{V_{GS}/kT}$$

Where k is the Boltzmann constant and T the temperature. When plotted on a logarithmic scale, with increasing the gate voltage to the threshold value, we can define the area where the drain current increases from its OFF value as the subthreshold swing [49]:

(7)

$$S_S = \ln(10) \frac{kT}{q} (1 + \frac{C_d}{C_i})$$

Where  $C_d$  is the depletion capacitance of the semiconductor and is closely related with the trap concentration in the semiconductor [10]. The subthreshold swing is given in units of V/decade (decade – a 10 times increase in drain current) and the minimum value in room temperature is 60 mV/decade, when  $C_i \rightarrow \infty$ . Low value of S<sub>S</sub> indicates high switching speed of the transistor in a narrow voltage range. The subthreshold slope, which is the reciprocal of the subthreshold swing is sometimes referred.

## 2.3 Characterization

For characterizing OTFT, many single device characteristics can be extracted from two simple voltage sweeps: the output curve and the transfer curve. For both cases, all three of transistor's voltage port should be well defined. Follows is the description of those important characterization methods and a summary of the parameters extracted from them.

#### 2.3.1 Transfer characteristics

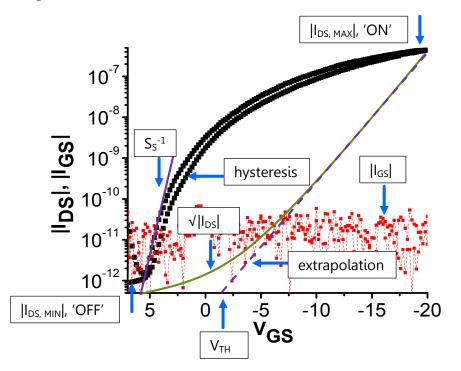

The transfer curve describes the relation between the gate-source voltage (V<sub>GS</sub>) and drainsource current (I<sub>DS</sub>). The transfer curve is measured by holding the drain voltage constant, and sweeping the gate voltage from the non-conductive region to the conductive region and in reverse. The source port is always connected to the common ground of the circuit. The values of V<sub>DS</sub> and V<sub>GS</sub> sweep are determined so that V<sub>DS</sub>=V<sub>GS</sub>, MAX-V<sub>TH</sub> to achieve the maximum saturation current. V<sub>GS</sub>, MAX is defined as the maximum negative (positive) voltage in case of p-type (n-type) semiconductor. The initial V<sub>GS</sub> (V<sub>GS</sub>, 0) is slightly more positive (negative) than the threshold voltage in case of p-type (n-type) transistors. During the sweep of the V<sub>GS</sub>, the drain current (I<sub>DS</sub>) and the leakage current (I<sub>GS</sub>) are recorded using a parameter analyzer. From the transfer curve we can extract several parameters related to transistor operation.

Two of the parameters which can be directly extracted from the transfer curve are the ON/OFF ratio and the maximum leakage current. We can directly recognize the current when transistor is OFF (at V<sub>GS</sub>, 0) and the maximum currents, I<sub>DS</sub> and I<sub>GS</sub>, when the transistor is ON (at V<sub>GS</sub>, MAX). The OFF current (ideally minimum value of  $|I_{DS}|$ ) and maximum leakage (maximum value of  $|I_{GS}|$ ) can imply on the energy consumption of the transistor when it is OFF and are important for circuit design. The leakage current is also important for the evaluation of the gate dielectric insulating properties. The maximum ON current points on transistor's current drive capabilities. An important interpretation of those value is the

transistor's ON/OFF ratio which is essential for switching applications of organic transistors [50].

By derivation of the transfer curve -  $g_m = \frac{\partial I_{DS}}{\partial V_{GS}}$  - an important transistor parameter is calculated.  $g_m$  is the transistor's transconductance (or the transfer conductance) which describes the response of the output current (I<sub>DS</sub>) to the input voltage (V<sub>GS</sub>). From equations (3) and (5) we can quantitavely derive the values of  $g_m$  in the linear and saturation regimes

(8) Linear regime:  $g_m = \frac{W}{L} \mu C_i V_{DS}$ ; Saturation regime:  $g_m = \frac{W}{L} \mu C_i (V_{GS} - V_{TH})$

The transconductance is closely related to the transistor ability to drive current but also to other key parameters of transistor performance (such as the cutoff frequency) and for circuit design.

Figure 4: Illustration of transfer curve and some of the important parameters which are extracted from it. The black scattered line represents the  $|I_{DS}|$  record where the red line exhibits the  $|I_{GS}|$  values during scan.

A key parameter extracted from the transfer curve is the transistor's field effect mobility. The mobility is one of the most material-related parameters and gives important information about the transport mechanism of charge carrier in the semiconductor. This value is sensitive to the presence of traps, impurities or molecular disorders [35,51] and implies on the quality of the semiconductor and transistor's conductivity. The mobility can be easily calculated from equations (3) and (5) for the different operation regimes of the transistor:

(9) Linear regime:

$$\mu = \left(\frac{W}{L}C_i\right)^{-1}V_{DS}^{-1}\left(\frac{\partial I_{DS}}{\partial V_{GS}}\right)$$

; Saturation regime:  $\mu = 2\left(\frac{W}{L}C_i\right)^{-1}\left(\frac{\partial \sqrt{I_{DS}}}{\partial V_{GS}}\right)^2$

As mentioned earlier, in the ideal case the linear and saturation field-effect mobility should be identical as they represent a physical property of the transistor during conduction, however they values may differ as a result of imperfections. In this thesis we mostly refer to field effect mobility in saturation as it is relevant to transistor operation in its ON state. In addition, many studies use this value as a benchmark parameter for comparison.

Information regarding the threshold voltage and subthreshold swing can also be derived from the transfer curve. According to equation (5), the threshold voltage can be found by extrapolation of the square root of  $I_{DS}$  and identifying its intersection with the x-axis. This method is similar to the widely used ELR method [52]. Although this method has some limitations [52] we will apply it through the thesis for consistency. Additionally, the subthreshold swing can be simply obtained from finding the slope of the curve in its exponential region, just before  $V_{GS}$  reaches the threshold voltage. As mentioned earlier this value contain information about the trap density of the semiconductor.

Finally, information regarding trap states in the semiconductor can also be identified by the presence/absence of hysteresis in the transfer curve. Hysteresis referred as the difference between the forward and reverse scan of  $V_{GS}$ , which creates a quantified shift in threshold voltage, according to the sweep direction. The dependence on the scan direction is caused by the history of trapping and releasing of charge carriers from energy states when as a result of voltage application.

Some of the parameters that can be directly extracted from the transfer curve are depicted in *Figure 4.*

#### 2.3.2 Output characteristics

The output curve describes the relation between the drain-source voltage (V<sub>DS</sub>) and drainsource current (I<sub>DS</sub>). In the output curve we can readily detect the transistor's operation in the linear and saturation regimes. The output curve is measured by holding the gate voltage constant, and sweeping the drain voltage from 0 to a pre-defined maximum value. The source port is always connected to the common ground of the circuit. The scan is usually done for several gate voltages to evaluate the transistor performance in different operating voltages. During the scan of V<sub>DS</sub>, the drain current (I<sub>DS</sub>) is recorded using a parameter analyzer. The output curve is important for characterizing the device in its linear and saturation region and is essential for circuit design (for example when transistors are used as current sources). By a qualitative observation of the output curve we can estimate the ideality of the linear and saturation regions. The output curve should present a linear behavior at small V<sub>DS</sub> values and saturated, constant current in the saturation regime. Deviation from this forms implies on inconsistencies with the transistor model. For example, in case that the drain current exhibits non-linear current increase with small values of V<sub>DS</sub>, a non-ohmic interface exists between the contact and channel. A Schottky barrier caused by energy gap between the semiconductor and the contact or the presence of space charge limited region (SCLC) in case of short channel devices, hinders charge injection and create a deviation from the model [53]. Non-saturated current at high values of V<sub>DS</sub> implies on additional conduction mechanisms when the channel is not 'pinched-off' properly [47].

The output curve is also useful for calculating two important resistance values of the transistor – the contact resistance and the output resistance (in saturation). The contact resistance is commonly derived by calculating the linear region resistance  $(\frac{\partial V_{DS}}{\partial I_{DS}})$  for transistors with different channel lengths and implementing the transmission line method (TLM) [54]. The contact resistance becomes very important when decreasing channel length. In short channel lengths the contact resistance accounts for larger portion of the total resistance and decreases the effective mobility of the device. We will implement this method in our work to evaluate the performance of our transistors in short channel lengths. From TLM, we can also extract the transfer length (L<sub>T</sub>) which is an essential parameter for determining the dimensions of the source and drain contacts [54–56]. The output resistance is also calculated from the derivation of the drain voltage in relation to the drain current for a single device in the saturation regime. Ideally, this resistance should go to infinity because the drain current does not depend on the drain voltage. In practice high values of this resistance are preferred, especially for application as current source or load resistance of inverters.

## 2.3.3 Cutoff frequency

The cutoff frequency of a transistor is the frequency where its current gain (i.e.  $i_{DS}/i_{GS}$ , here i represents small signal) equals to unity. In this frequency, the transistor cannot function anymore as a useful device as the current through the dielectric becomes substantial. It can be shown that the gate-source current and a linear dependence in frequency where the drain-source current does not depend in the input signal frequency. This leads to the following relation, describing the ratio between the small signals of the gate and the drain [10]:

(10)

$$\left|\frac{\dot{i}_{DS}}{\dot{i}_{GS}}\right| = \frac{g_m v_{GS}}{2\pi f C_G v_{GS}} = \frac{g_m}{2\pi f C_G}$$

High-frequency organic thin-film transistors for conformable large-area electronics

where  $C_G$  denote the total gate capacitance and is composed of parasitic capacitance and channel capacitance. The parasitic capacitances are originated from the overlap between the gate and source and drain and are independent in the operation mode of the transistor. The channel capacitance, on the other hand, depends on the operation regime. The total gate capacitance is can be presented as [57]:

(11) Linear regime:

$$C_G = C_i W(L + 2L_C)$$

; Saturation regime:  $C_G = C_i W\left(\frac{2}{2}L + 2L_C\right)$

For long channel lengths, the two terms can be approximated to be equal. We will adopt this approximation in our case. By depicting the condition of  $\left|\frac{i_{DS}}{i_{GS}}\right| = 1$  at the cutoff frequency with equations (10) and (11) we derive the following relation for cutoff frequency f<sub>T</sub> [10,33]:

(12)

$$f_T = \frac{g_m}{2\pi f C_G} \cong \frac{g_m}{2\pi W C_i (L+2L_C)} = \frac{\mu (V_{GS} - V_{TH})}{2\pi L (L+2L_C)}$$

This relation clearly shows the importance of the channel dimension to the improvement of transistor's cutoff frequency, as the dependence in the channel length is quadratic. Increasing the device mobility and transconductance can also contribute to high frequency operation.

## 3 Material and Methods

#### 3.1 Ultrathin plastic foils

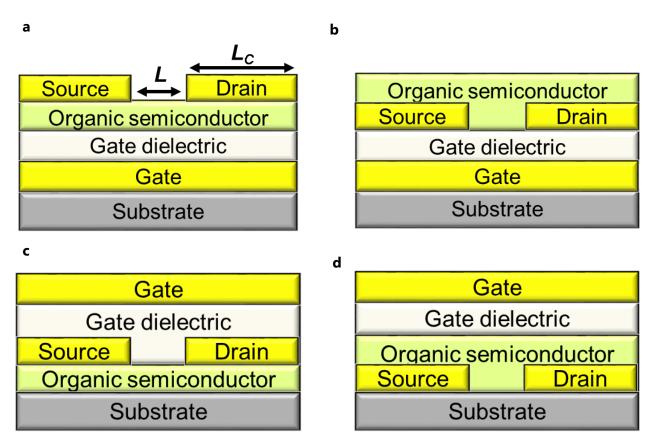

Recently, great development is being made in the field of ultrathin, imperceptible electronics. Large area OTFT fabrication, stretchable photonics devices, epidermal functional tattoos and others [16,18,21,22,58] have shown the feasibility to make electronic circuits more intimate and light that they have ever been before. Besides being imperceptible and conformable to surfaces, ultrathin electronic devices has additional attractive features. Ultrathin devices can achieve higher signal to noise ratio than their thicker counterparts, even when only passive electrodes are implemented on it [59]. Furthermore, reducing substrate thickness significantly reduces the mechanical stress on the device in case of bending. This property allows ultrathin devices to be rolled and crumpled down to very small bending radii [16].

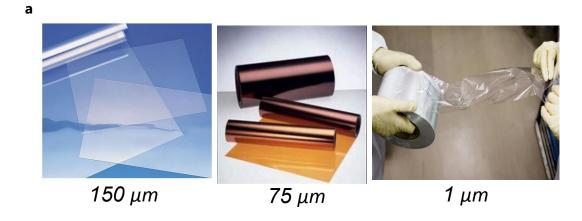

Figure 5: (a) Flexible films, common in use in the plastic electronics research and industry. From left to right: 150  $\mu$ m polyethylene-naphthalate (PEN) film, 75  $\mu$ m polyimide (PI) film and 1  $\mu$ m polyethylene-terephthalate (PET) film. (b) Common lamination method of ultrathin films on flat surfaces using adhesive layer.

For device fabrication on ultrathin films, there are several important considerations. First are the film mechanical properties and surface characteristics. The film should be mechanically durable to reasonable (depends on the application) lateral stress to allow device handling without failure. In addition, surface roughness is of utmost importance when one tries to fabricate organic electronic devices. Semiconductor quality is very sensitive to surface roughness during deposition and shows negative correlation to an increased surface roughness. Surface energy is also important in case that the semiconductor is deposited directly on the thin film [35]. Another requirement is that the film will be flat and stable during device fabrication. This is an important perquisite for reliable patterning and semiconductor deposition. In *Figure 5*a, we give examples of common flexible substrates used for electronic device fabrication. It can be easily seen that the ultrathin foil has different mechanical properties than the thicker plastic foils.

In order to maintain a flat form of an ultrathin film during device fabrication, there are two main approaches: lamination of existing film on flat surface (*Figure 5*b) or direct film formation. In the first method, an adhesive layer (usually spin-coated polymer) is used to provide strong adhesion of the foil to the substrate during processing, yet it should enable stress-free delamination when device fabrication is completed. In this approach, the film can be prepared/purchased separately and be used as a substrate for device fabrication. The lamination procedure should be done in a contamination-free environment and avoid air gaps between the ultrathin film and the adhesive layer in a precise process. In addition, the utilization of this layer limits the process window on the film and device fabrication should also consider the properties of this layer. On the other hand, direct formation of films, using vapor deposition or spin coating, is a simple method that allows good adhesion to surface and compatibility to wide range of processes. Thickness of the film is determined during the formation process. This kind of deposition assures full contact of the film to the substrate once it is done in a clean environment or under vacuum.

Material selection and adhesion technique was critical for successful fabrication of short channel devices on ultrathin films. Previously reported adhesion layers (based on Polydimethylsiloxane) were not applicable to our process. The ultrathin film was easily delaminated when we applied the photolithography process due to use of organic solvents. In order to overcome this issue and improve our device performance we chose parylene diX-SR as a base substrate for device fabrication. Parylene diX-SR shows very small surface roughness of 4 nm RMS (when deposited using SCS LABCOTER, *Figure 6*a [60]), which is considerably lower than ultrathin polyethylene-naphthalate (PEN) [16] and only slightly higher than thick polyimide film [60]. In addition, the material has good yield strength (52.7 MPa) and high melting point of 303.2°C [61]. For practical applications with organic electronics, moisture vapor transition rate (MVTR) and oxygen transmission rate (OTR) are important parameters to keep device stability and prevent degradation.

Parylene derivatives (most commonly parylene-C) are known as good encapsulations in the biomedical field for implantable devices [62,63] due to their relatively low transmission rates. Parylene diX-SR presents MVTR of 0.09 g·mm/m<sup>2</sup>·24h and OTR of 2 cm<sup>3</sup>·mm/m<sup>2</sup>·24h·atm which are comparable to parylene C and provide relatively low rate for device encapsulation [64]. In order to deposit parylene diX-SR in an ultrathin form, we used chemical vapor deposition (CVD) by SCS LABCOTER to form ~1 µm thick layers directly on Si/SiO<sub>2</sub> wafers. The ultrathin film showed strong adhesion to the rigid substrate and we could apply all lithography process steps to the substrate. After the completion of device fabrication, the ultrathin substrate could be carefully delaminated from the rigid Si/SiO2 support to obtain free-standing ultrathin films. In *Figure 6*b surface properties and main typical film characteristics of parylene diX-SR as substrate are summarized.

| a b<br>30 nm | ь<br>80 nm                           | Material Property                                    | Parylene<br>diX-SR |

|--------------|--------------------------------------|------------------------------------------------------|--------------------|

|              | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | Density [g/cm <sup>3</sup> ]                         | 1.28               |

|              |                                      | Yield Strength [MPa]                                 | 52.7               |

|              |                                      | Tensile Strength [MPa]                               | 58.5               |

|              |                                      | Tensile Modulus [GPa]                                | 4                  |

|              |                                      | Melting point [°C]                                   | 303.2              |

|              |                                      | MVTR [g·mm/m <sup>2</sup> ·24h]*                     | 0.09               |

|              |                                      | OTR [ cm <sup>3</sup> ·mm/m <sup>2</sup> ·24h·atm]** | 2                  |

|              |                                      | Water absorption [%]***                              | <0.1               |

\*at 37°C; \*\*at 23°C; \*\*\*over 24 hours

Figure 6: (a) Atomic force microscope scan of parylene diX-SR substrate, deposited using SCS LABCOTER [60]. (b) Typical values of parylene diX-SR 25 µm thick film [136].

#### 3.2 Organic semiconductor

The organic semiconductors are the most essential element that defines the field of organic transistors. The Organic semiconductors are hydrocarbon based materials that can change their conductivity according to external stimulation such as voltage application. Organic semiconductors can be found in two forms: conjugated polymers and conjugated small-molecules [10]. Small molecule semiconductors based OFETs are often preferable due to their advantages of a defined molecular structure, a definite molecular weight, high purity and good reproducibility compared with their polymeric counterparts. Though, processing of conjugated polymers can carry advantages in terms of ease of fabrication and cost. The basic principles of these materials can be described by the valence bond theory and the Born–Oppenheimer approximation [65]. The conduction mechanism is based on the molecular level bonding between the organic

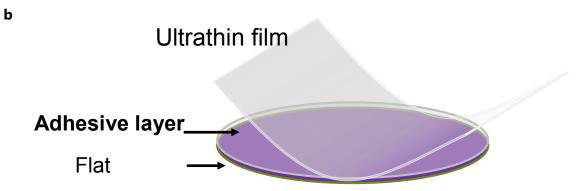

Figure 7: Illustration of simple (a)  $\sigma$  bond orbitals with cylindrical symmetry around the internuclear axis and (b)  $\pi$  bonds perpendicular to the internuclear axis [65].

molecules and their energy gap. In this section, we will review some of the important principles related to the molecular structure and energy levels.

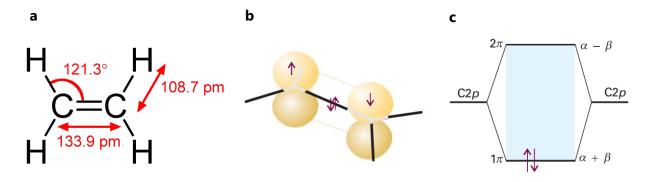

Atoms in the organic material are connected by  $\sigma$  and  $\pi$  chemical bonding which are described by the spatial distribution of electron orbitals. The  $\sigma$  bonds are connections between atoms that their electrons orbitals have cylindrical symmetry around the internuclear axis. On the other hand,  $\pi$  bonds do not have cylindrical symmetry and arise from spin pairing of electrons in orbitals that approach side by side, perpendicular to the axis between nuclei (*Figure* 7). In the case of polyatomic structure, the bonds can be created by hybridization between s and p orbitals to forms hybrid orbitals which consist of  $\sigma$  and  $\pi$  bonds [65]. As an example, we will analyze the hybrid sp<sup>2</sup> orbital which is found in the elementary ethene molecule (or ethylene). In ethane, two carbon atoms are connected via a double bond and to additional 4 hydrogen atoms (*Figure 8*a). The ground state of carbon is  $2s^1p_x^{-1}p_y^{-1}p_z^{-1}$  which allows 4 free electrons for each carbon to bond with

its neighbor atoms. In this configuration three bonds in the sp<sup>2</sup> hybridization are localized  $\sigma$  bonds and found in the same internuclear plane. The remaining p<sub>z</sub> electron is free to form a perpendicular and delocalized  $\pi$  bond, above and below the  $\sigma$  bonding plane (*Figure 8*b). The energy levels of the  $\pi$ -bonds are concentrated in two bands separated by an energy gap - the band gap (*Figure 8*c). Charge transport occurs either in the Highest Occupied Molecular Orbital (HOMO) or in the Lowest Unoccupied Molecular Orbital (LUMO).

Conduction in organic semiconductor, based on the HOMO and LUMO levels of the material, is made via the overlapping  $\pi$  orbitals between molecules which are found in physical proximity to each other ( $\pi$ - $\pi$  stacking). A preferable orientation between molecules is the parallel one, when charge transport is made perpendicular to the

Figure 8: (a) Ethene molecular structure and spatial angles between atom bonds (from 'Ethylene', Wikipedia). (b) Illustration of ethene  $\pi$  bonds (yellow spheres) in the sp<sup>2</sup> hybridization. (c) Highest occupied molecular level (HOMO) denoted with  $1\pi$  bond and the lowest unoccupied molecular level (LUMO,  $2\pi$ ) of the sp2 hybridization in ethane (illustration). Images were adopted from [65].

molecular plane [10,66]. It is important to note that the electronic structure of an organic solid largely preserves that of a molecule or a single chain, as the molecules are attached to each other by weak Van der Waals interaction [67]. Hence the ionization energy and electron affinity of a material correspond to the HOMO and LUMO levels (in relation to the vacuum level) in the molecular case (*Figure 9*a).

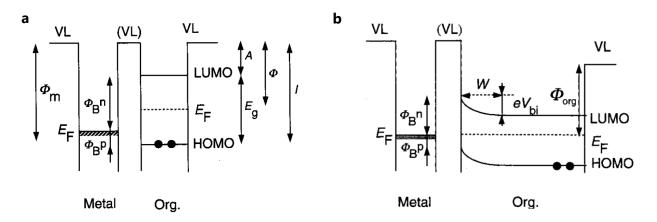

The HOMO and LUMO levels are critical in determining the charge injection from contacts to the semiconductor and affects the material air stability. The HOMO and LUMO can be considered as the valence and conduction bands as in the case of inorganic semiconductors. Conduction of holes is made through the HOMO level and electrons are transferred in the LUMO level. Please note that the conduction in organic semiconductors does not strictly follow the band-like mechanism [9,67], but this simplification is useful for device modeling. P-type and n-type organic semiconductor are characterized by the majority of charge carriers in the materials, holes and electrons respectively. In order to inject carriers from metal to the semiconductor, the energy barriers for injection should be overcome (*Figure 9*a). For example, charge transfer from a contact to a p-type

High-frequency organic thin-film transistors for conformable large-area electronics

Figure 9: (a) Energy band diagram of metal and organic semiconductor. HOMO and LUMO levels correspond to the ionization (I) and electron affinity (A) of the material. Eg is the energy gap between the HOMO and LUMO level.  $\phi_B n$  and  $\phi_B p$  are the injection barriers from the metal for electrons (to LUMO) and holes (to HOMO) respectively. (b) Band bending and build in potential (eV<sub>bi</sub>) of metal and semiconductor with the same vacuum level. Diagrams adopted from [67].

semiconductor is facilitated when the contact's Fermi level is deeper than the HOMO level of the p-type semiconductor. Analogous consideration can be done for n-type materials and their LUMO levels. The energy barrier changes when the metal and semiconductor are interfaced according to the build-in potential which represents the difference in vacuum levels between the solids (*Figure 9*b).

For an organic semiconductor, the key features are high majority carrier mobility, good processability and excellent air and environmental stability. For several years, n-type organic semiconductors fell short in performance and air stability from their p-type counterparts. The reason was mainly the air instability of these materials to reaction with  $O_2$  and  $H_2O$  species [68,69]. An onset LUMO energy of approximately -4.0 eV is essential to stabilize electrons during charge transport. Deeper LUMO level may be better for stabilizing the organic semiconductor however too deep levels (<-4.5 eV) can cause low ON/OFF ratio at device level due to unintentional doping [69]. Recently great improvement is made in this field and n-type semiconductors start showing good air stability and device performance towards complementary organic electronics [69,70]. On the other hand, p-type semiconductors have shown good device mobility (>  $1 \text{ cm}^2/\text{V} \cdot \text{s}$ ) and air stability. Acene and thiophene based p-type organic semiconductors have advantageous  $\pi$ -bond topology and were among the leading functional molecular groups for achieving good electrical and environmental properties [71–73]. Among these groups, pentacene is one of the most studied p-type semiconductor for device and morphological investigations [51,74-78].

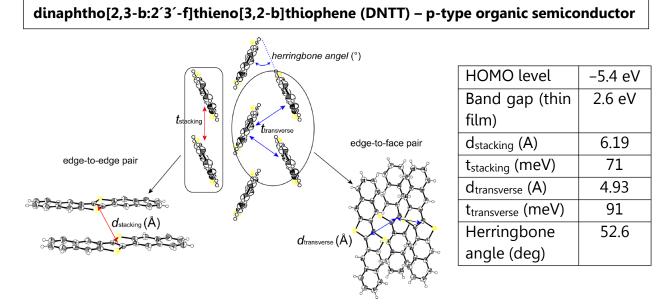

In this work, we will utilize the air stable, thiophene based, dinaphtho[2,3-b:2'3'f]thieno[3,2-b]thiophene (DNTT) as a small molecule organic semiconductor. DNTT was first reported by Takimiya and Yamamoto [79] and since then was proven as a high mobility organic semiconductor with excellent environmental and thermal stability. In its single crystalline form mobility of over 8 cm<sup>2</sup>/V·s could be achieved [80] where in the thin film, polycrystalline layout high hole mobility of 3 cm<sup>2</sup>/V·s was obtained [79]. Air stability tests have demonstrated several months of un-encapsulated operation with negligible degradation [81]. The thermal stability of the semiconductor was also tested in long channel OFET devices that were successfully implemented for biomedical application [82]. Different derivatives of DNTT, such as DPh-DNTT or C<sub>10</sub>-DNTT, can exhibit enhanced performance in terms of device mobility and stability [83–85]. The main properties of the semiconductor are summarized in *Figure 10*.

Figure 10: Molecular structure (left) and key parameters (right) of dinaphtho[2,3-b:2'3'-f]thieno[3,2-b]thiophene (DNTT) organic semiconductor. Images and data were adopted from [72].

## 3.3 Gate dielectric

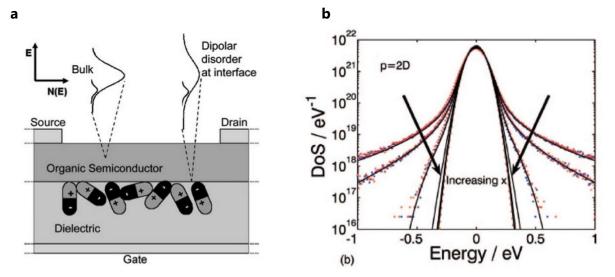

The organic semiconductor is not the only critical component in structuring the organic transistor. An appropriate gate insulator is very important for device characteristics and has immense effect on transistor's mobility, operation voltage and more. The dielectric can affect the morphology of the organic semiconductor and the orientation of molecular segments, via their interaction with the dielectric (especially in bottom gate devices). Furthermore, the interface roughness and sharpness may be influenced by the dielectric itself, the deposition conditions, and the solvents used [35,86]. Large surface roughness creates irregularities in the channel area that can act like charge traps or prevent proper nucleation during the semiconductor growth. Interface traps between semiconductor and gate dielectric can also cause undesired phenomena such as device hysteresis or gate voltage dependent mobility. Polarity of the dielectric interface can lead to morphological inhomogeneity or affect the distribution of the electronic states (*Figure 11*) [41,87,88].

Many of the first OFET deices utilized Si/SiO<sub>2</sub> as gate and gate dielectric due to the availability of this structure and the optimized defect free interface between the gate and dielectric. However, using SiO<sub>2</sub> as dielectric to interface the semiconductor has many disadvantages. The SiO<sub>2</sub> tend to absorb hydroxide or water molecules which negatively affect the interface with the organic semiconductor. Interface states on the inorganic layer also lead to increased hysteresis and charge trapping. In addition, applying oxides as dielectric layers in the bottom gate architectures affects nucleation and semiconductor morphology due to polarity in the interface, which reduces device mobility [89]. Lastly, Si/SiO<sub>2</sub> devices require large operation voltage which leads to high energy consumption.

The gate dielectric layer should satisfy several conditions. One of the crucial parameters is the maximum possible electric displacement  $D_{max}$  that the gate dielectric can endure [90]:

$$D_{max} = \varepsilon_0 k E_{Breakdown}$$

where  $\varepsilon_0$  is the vacuum permittivity, *k* is the dielectric constant of the material and  $E_{Breakdown}$  is the breakdown electric field. The capacitance per area is then defined by:

(13)

$$C_i = \varepsilon_0 k/d$$

where *d* is dielectric layer thickness. High capacitance per area can be achieved in two approaches: reducing dielectric thickness or using materials with high dielectric constants. Increasing the capacitance per area of the dielectric leads to a reduced operation voltage, according to the following relation:

(14)

$$n = \frac{1}{e} C_i (V_{GS} - V_{TH})$$

where e is the elementary charge and  $V_{GS}$ ,  $V_{TH}$  are the gate-source and threshold voltage respectively, and n is a specific charge carrier density in the channel. Lower operation voltage provides safer and more energy efficient devices. Additionally, dielectric layer should provide 'traps free' (ideally) interface with the semiconductor and allow proper nucleation and semiconductor growth. For example in the case of thermally evaporated small molecules organic semiconductors, low surface energy with small surface roughness substrates are generally preferred [35]. Finally, the gate dielectric should be ideally compatible with flexible substrate, allow mechanical durability and preferably low cost

Figure 11: (a) The density of states (DOS) in the bulk of the semiconductor and at the interface with the dielectric as a result of local polarization [88]. (b) Calculated DOS broadening due to static dipolar disorder in the dielectric with increasing distance into the semiconductor [87].

processes. In principle, insulators for OFET application can be classified into 3 main categories: high-k inorganics, polymers and self-assembled small molecules to satisfy the above requirements [41,90].

As mentioned earlier, the use of high-k inorganic materials as insulators can benefit in low operation voltage and high capacitance per area. High permittivity dielectrics have been extensively used in inorganic FETs however only in 1999, Dimitrakopoulos and coworkers were the first to use high-k oxides as dielectrics in OFETs [91]. As a result, the group could reduce operation voltage down to 5V and achieve higher mobility due to an increased charge carrier density in channel at low voltages. Since then, many groups have utilized metal oxide dielectrics for organic electronics. Al<sub>2</sub>O<sub>3</sub> (k~8 and Ta<sub>2</sub>O<sub>5</sub> (k~23) are amongst the most experimented species however other metal oxides such as HfO<sub>2</sub> (k~22-25), TiO<sub>2</sub> (k~41) and ZrO<sub>2</sub> (k~25) are also useful materials for application in OFETs [41]. One of the problems in inorganic oxide layers is their high roughness and surface polarity that degrade the efficiency of charge transport in the channel. This might be solved by surface modifications such as hexamethyldisilazane (HMDS), Octadecyltrichlorosilane (OTS) or others. Additional concerns are the often use of high energy processes, such as plasma enhanced CVD (PECVD), sputtering or atomic layer deposition (ALD), that may damage the plastic substrate during deposition. In this sense, anodization can provide a good compatible process for thin films application. Another issue with the high-k approach the poor mechanical durability of those layers, as they are based on oxides or ceramics.

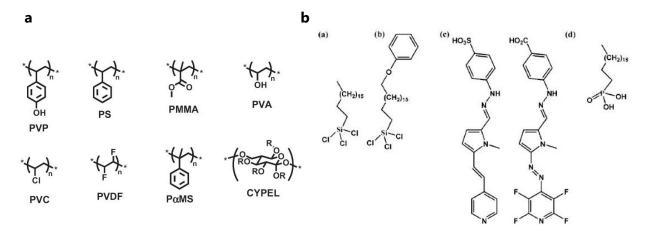

Polymeric dielectrics have a great potential for utilization as OFETs gate insulators. Their characteristics can be tailored to allow different solubility, processability and dielectric coefficients. Polymers can be often deposited by simply spin coating, casting or printing under ambient conditions [10]. In *Figure 12* some of the common polymers used for gate dielectric are presented. The first detailed study on polymeric gate dielectrics was made in 1990 by Peng et al. [92]. The group could show better mobility values and I/V characteristics than the ones achieved on SiO<sub>2</sub> and reported on a positive correlation between the dielectric constant and device mobility. Operation voltage was in the range of 30V. The interface between the gate dielectric and the semiconductor affects not only the semiconductor morphology but also the density of states in the channel. By

Figure 12: Chemical structure of common (a) polymers and (b) self-assembled-monolayers used as gate dielectrics for OFETs. Images adopted from [90] and [41] respectively.

introducing high-k material, random dipole fields at the interface can cause carrier localization and change the density of states in the channel. In 2004, casting of a high breakdown strength (>3 MV/cm) polymeric dielectric layer was demonstrated for the first time in thickness below 300 nm [93]. The devices based on PEDOT:PSSR semiconductor exhibited mobility of  $10^{-4}$  cm<sup>2</sup>/V·s with only 50 nm of gate insulator. Further efforts with polymers (poly-4-vinylphenol and polystyrene) and cross-linking reagents could reduce dielectric thickness down to phenomenal values of 10-20 nm for a pinhole free layer [94]. Different approach, utilizing the top gate structure, vapor deposited parylene-C as the dielectric on top of the semiconductor [95]. Dielectric thickness reached 540 nm and devices ON/OFF ratio exceeded 10<sup>4</sup>. In summary, polymer dielectric layers can readily achieve high breakdown voltage with very small thicknesses in simple fabrication

techniques. Nevertheless, the ultimate polymer dielectric, presenting low voltage operation, device uniformity, low surface roughness and good device characteristics, was not demonstrated yet.

The use of self-assembled-monolayer (SAM) as dielectrics is another promising strategy to provide high capacitance per area for reliable low voltage operation. The basic principle is to deposit a few nanometer thick SAM that has good leakage properties to improve or create a dielectric layer. SAM dielectrics can reach capacitance per area in the order of ~100 nF/cm<sup>2</sup> and leakage currents in the order of 10<sup>-8</sup> A/cm<sup>2</sup>. The use of a SAM as a gate dielectric was pioneered in 1996 by the deposition of octadecyltrichlorosilane (OTS) onto SiO<sub>2</sub>, to realize reasonable OFET devices with low leakage [96]. Self assembled monolayers can be grown directly on various oxides, to improve leakage current, semiconductor formation and device mobility [41]. H. Klauk and his group has made significant contribution in the field by depositing n-octadecylphophonic acid (ODPA) on aluminum gates and obtaining operation voltage of only 2V with low leakage and high device mobility, for n-type and p-type case. The group has demonstrated the reliability of this method by applying it to organic circuits and applications [7,13,24,82]. The versatility of the SAM approach was demonstrated by the development of self-assembled nanodielectric (SAND) by alternating constituent layers and modify the dielectric characteristics [97]. The group has shown that depending on the selected elements, they could change capacitance per area and other dielectric properties, as well as to apply the dielectric to wide variety of semiconductors (including inorganic).

All the above approaches could show promising results towards low voltage, easy processable, mechanically stable and low leakage dielectrics. Intensive study for achieving the optimal gate dielectric for good OFET performance is still ongoing. New approaches for material improvements, deposition techniques and hybrid solutions are being proposed and implemented for this purpose [41]. Currently, the ultimate gate dielectric, achieving all requirements, is still beyond reach and dielectrics for OFETs are often chosen by the specific application.

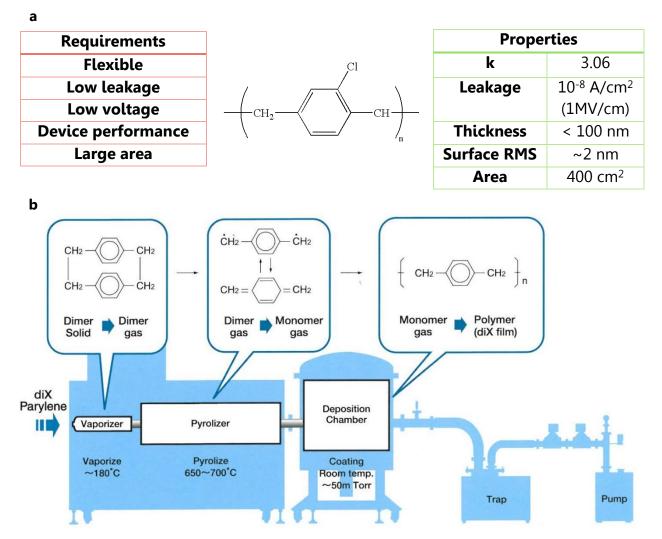

In order to choose the appropriate dielectric layer for our device fabrication we considered several application issues. First, as we aim for ultrathin and ultraflexible devices, mechanical flexibility and stability have high importance in our consideration. Polymer based dielectric is a natural selection in this case allowing compatibility for ultrathin film fabrication and high flexibility. Second, for the use as 'ambient electronics' and large area sensor sheets, low operation voltage and is also critical. We aim for operation voltage < 10V to realize such application reliably and effectively. The requirement for large area constraints us to choose a method for uniform deposition on large scales. Finally, the dielectric should provide interface for the organic semiconductor to enable good device performance for high frequency operation. A brief summary of the requirements is given in *Figure 13*a.

In our contribution, we utilized low-k polymeric gate dielectric for our OTFTs implementation. The chosen material is a derivative of poly(p-xylylene) - parylene diX-SR, provided by KISCO Ltd. The material has dielectric constant of k=3.06 at 1 kHz. Parylene diX-SR can be deposited reliably on large areas (400 cm<sup>2</sup>) in a high vacuum CVD process [98], presents thicknesses below 100 nm and provides capacitance per area in the range 10-100 nF/cm<sup>2</sup>. The utilization of CVD allows facile and conformable coating of many kinds of surfaces. The layer is pinhole free and shows leakage current density lower than 10<sup>-8</sup> A/cm<sup>2</sup> at 1 MV/cm [60]. The dielectric has very small surface roughness (~2 nm RMS) and is compatible with good performance of organic semiconductor and mobilities of ~0.5 cm<sup>2</sup>/V·s were obtained in the top contact architecture. Lastly, parylene diX-SR is thermally and environmentally stable for practical applications. The main characteristics of the dielectric and CVD system description are given in *Figure 13*. The choice of this

Figure 13: (a) Summary of requirements and main features of parylene diX-SR at high vacuum chemical vapor deposition. The chemical structure of parylene C is given as illustration. (b) CVD process and system description as it appears in [98].

material as gate dielectric is a key parameter for a successful fabrication of high frequency devices on ultrathin foils.

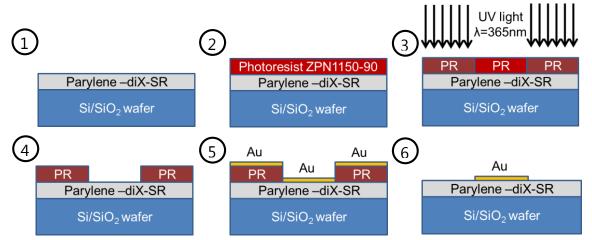

## 3.4 Photolithography

## 3.4.1 Process principles

Photolithography is an optical patterning process made on light-sensitive polymer (photoresist). The process is one of the most important building blocks in the semiconductor industry creating structures and components for billions of transistors every year. Ideally, the process designed to transfer the mask pattern to the photoresist, defined by the thickness of the polymer walls. Photolithography patterns are commonly used for selective etching and ion implantation as well as metal deposition using 'lift off' techniques. The process itself is complicated and involves many steps and theoretical background however here we summarize the characteristics of the typical process steps, based on professional resources [99–101]:

#### Substrate preparation

Proper substrate preparation is required to provide clean surface for the process and improve the photoresist adhesion to it. Surface contamination can take the form of organic or in-organic particles attached to the substrate. These contamination can be removed chemical, mechanical or plasma tripping followed by an additional dehydration step to remove adsorbed water. Dehydration takes place in elevated temperatures for several minutes. The substrate is then allowed to cool down, preferably in a dry environment and coated with photoresist as soon as possible. Adhesion promoters, such as hexamethyldisilizane (HMDS), are often to enhance the surface hydrophobicity for better photoresist coverage.

#### Photoresist coverage

Spin coating is the most common way to apply photoresist on a substrate. Layer uniformity and thickness controllability are of the most important properties of the photoresist coat. Resist properties (viscosity, composition), substrate topography and spin-coat speed and acceleration mainly affect layer thickness and uniformity but also humidity control, resist temperature and spinner cleanliness have some importance on the final result. As a rule of thumb the photoresist thickness is given by:  $d \propto \frac{v^{0.4}}{\omega^{0.5}}$  [99]where v is the photoresist viscosity and  $\omega$  represents the spin-coat speed. Artifacts such as photoresist waviness, streaks (due to particles larger than the photoresist thickness) or edge beads can occur and reduce the coverage uniformity.

#### Post apply bake (PAB)

The post apply bake stage is implemented to remove excess solvent (~20%-40%) from the spin-coated photoresist in order to stabilize it before exposure [99]. Hot plate baking is usually preferable on convection oven baking due to the shorter heating periods and its uniformity. The main outcomes from this process step are the reduction of film thickness, adhesion improvement and tackiness reduction. PAB also changes the film reaction to later stages such as post exposure bake (PEB) and development. Care should be taken for applying the right conditions because elevated temperatures and long annealing time may decompose the photoactive component in the photoresist or crosslink the photoresist resin. It is also important to notice that baking continues even after the wafer is removed from the heating apparatus. As a result, for a well-controlled process, a subsequent cooling step should be performed after baking.

#### Exposure

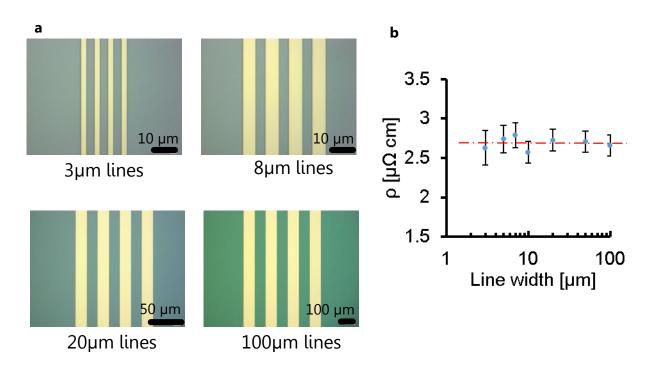

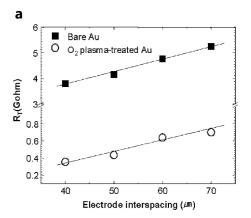

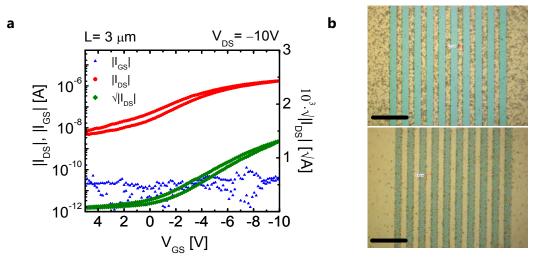

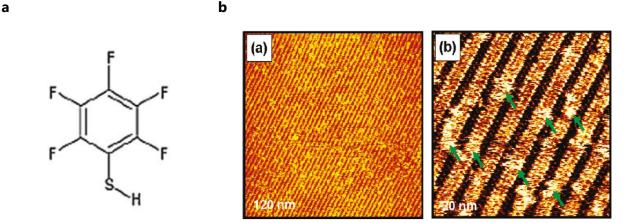

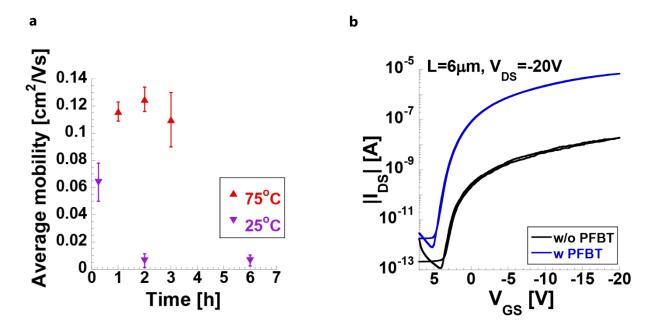

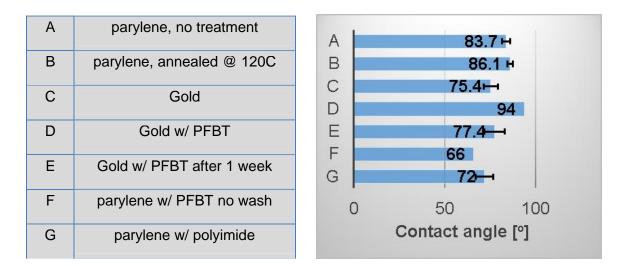

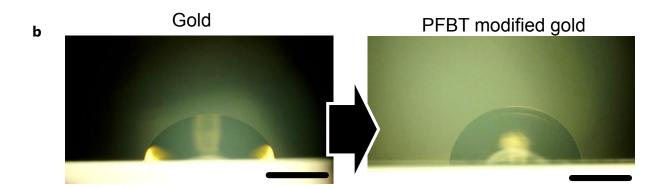

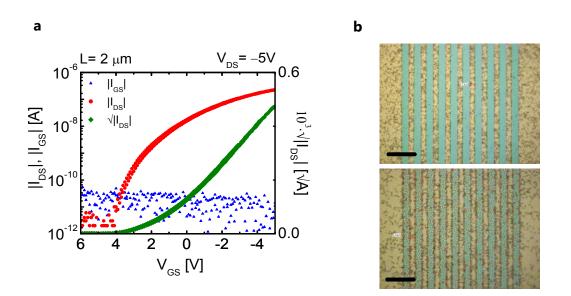

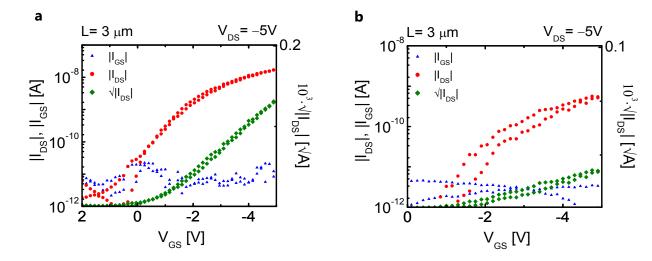

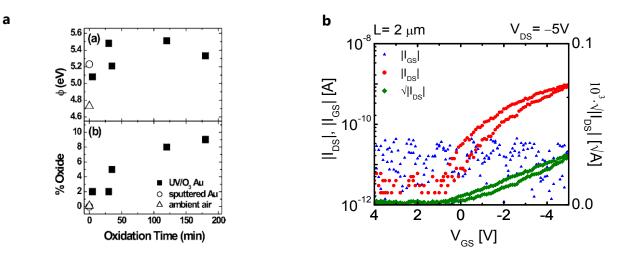

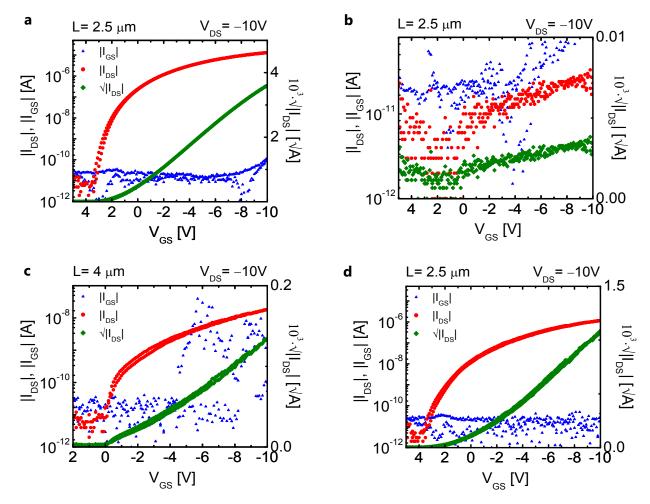

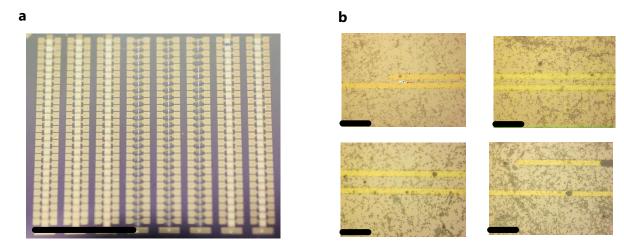

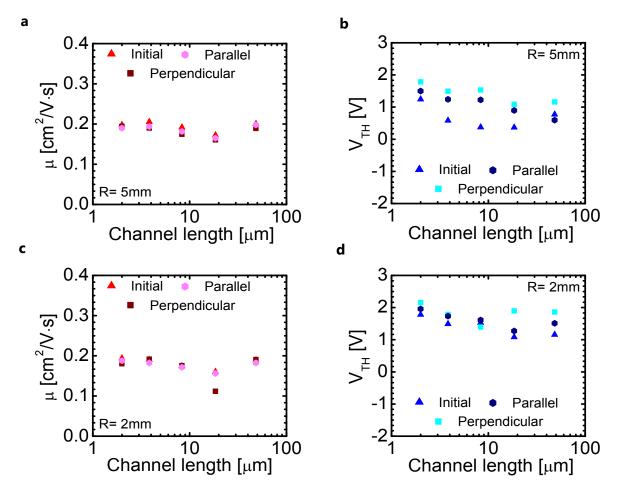

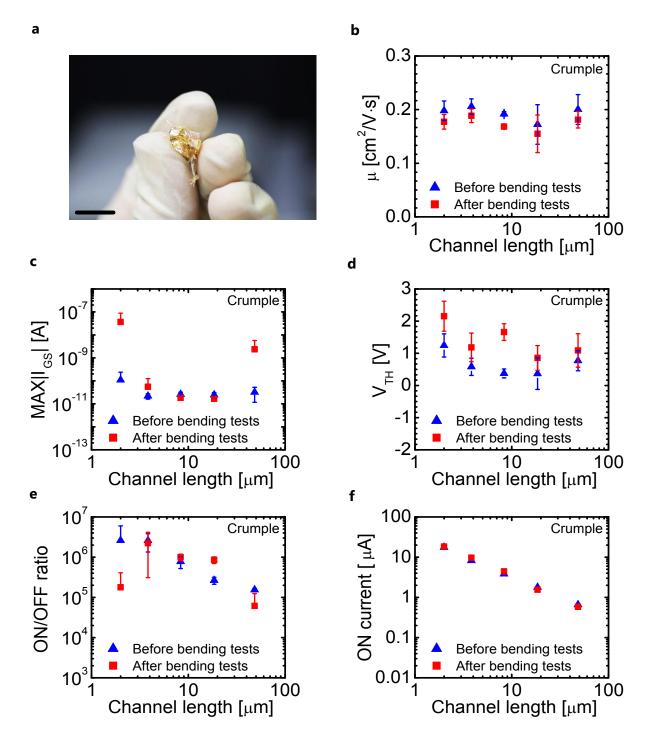

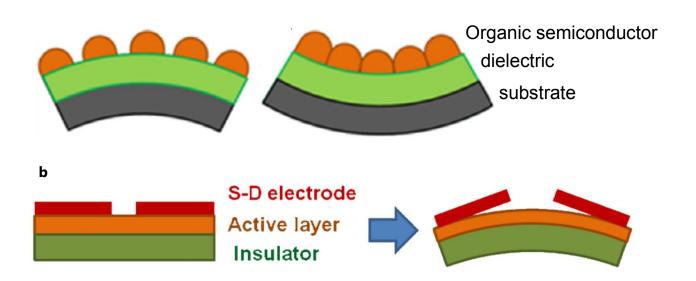

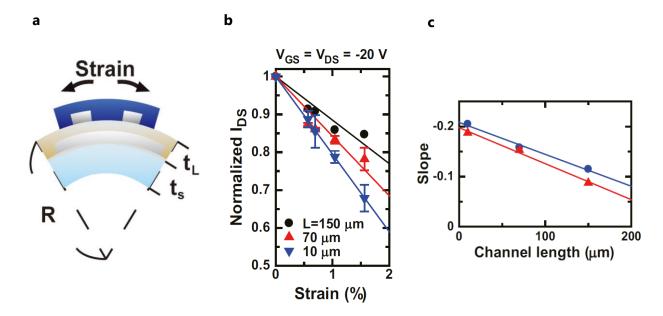

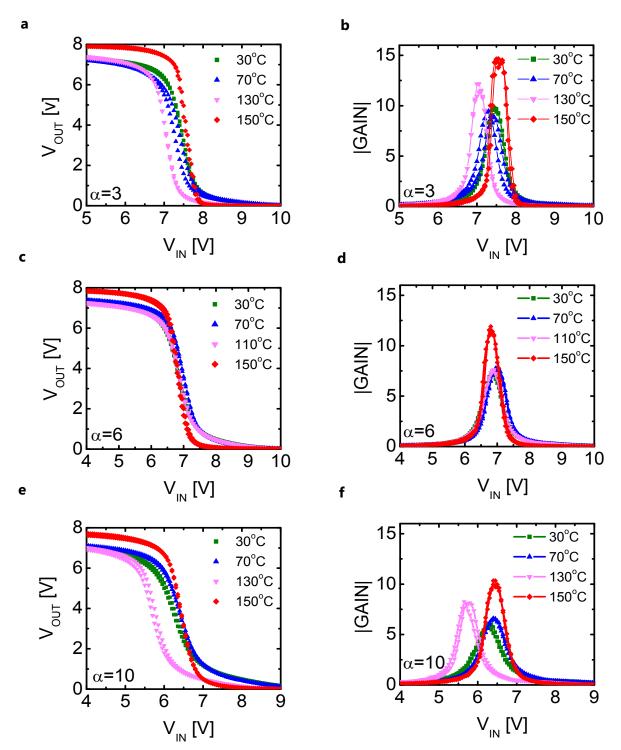

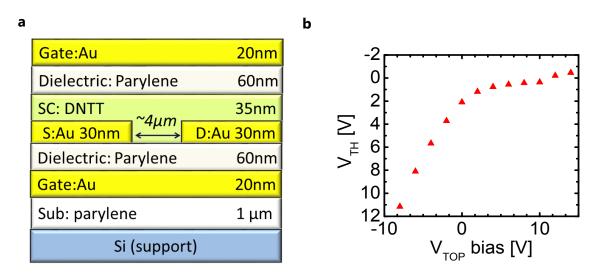

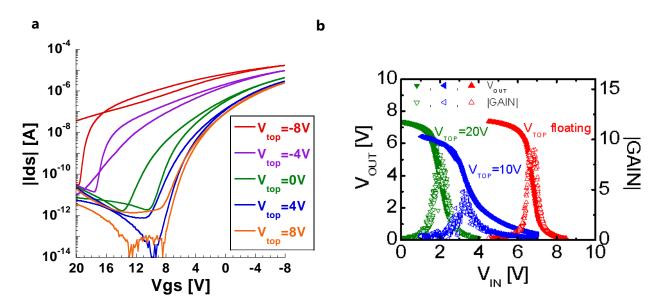

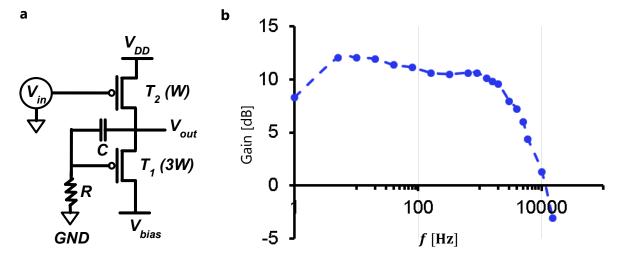

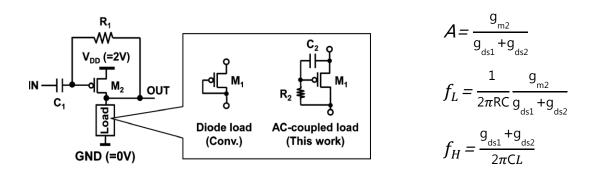

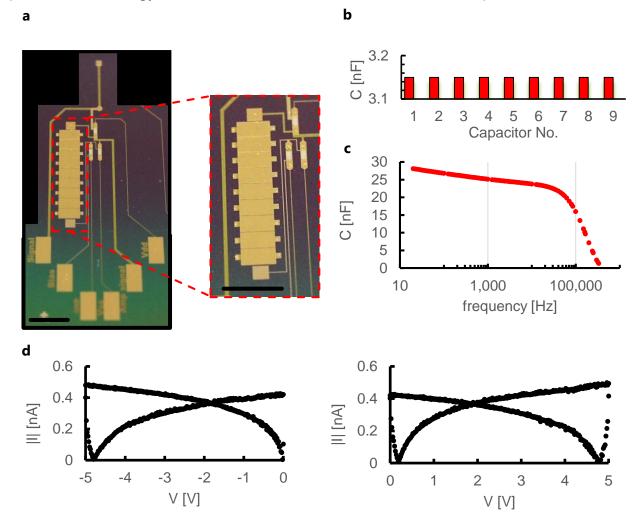

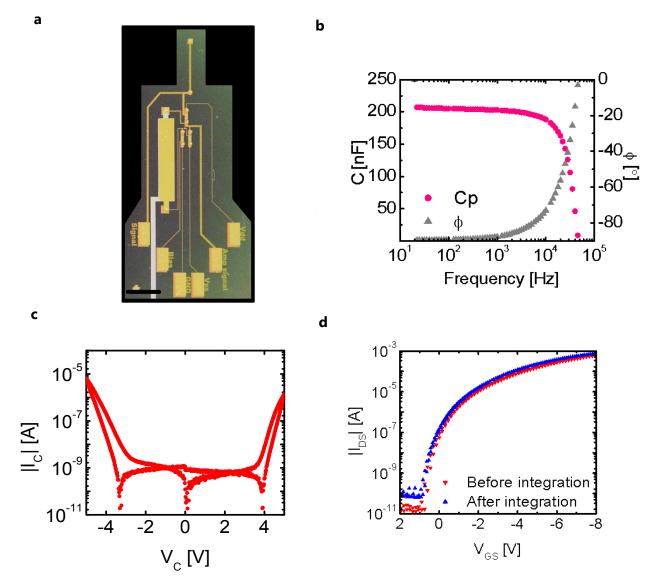

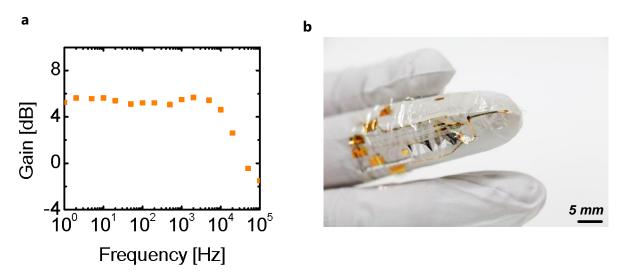

Exposure is one of the most important steps in the photolithography procedure. During this step the pattern is transferred to the photoresist by light exposure which initiate a change in the resist solubility in the developer. There are two types of photoresists: negative and positive type. When the positive type is exposed to light, it becomes soluble to the photoresist developer where the contrary occurs to the negative type. The negative photoresist is initially soluble in the developer and exposure to light in the appropriate wavelength make it insoluble. As an example, diazonaphthoquinone, a common photoactive component (PAC) in positive photoresists is converted to the soluble (in aqueous base developer) carboxylic acid after exposure to UV light between 350 nm – 450 nm. By exposing the pattern to the photoresist, only the parts that become soluble will be removed by the subsequent developing stage. Positive photoresists considered to be more expensive and achieve better resolution and step coverage than the negative type ones.