# 博士論文

# The Effects of Variability on Write Stability in SRAM at Low Supply Voltage

(低電圧 SRAM における特性ばらつきの書き込み安定性への影響)

# 平成 28 年 06 月 01 日提出 指導教員 平本 俊郎教授

東京大学大学院工学系研究科 電気系工学専攻 37-137264 邱浩

# Abstract

Static random access memory (SRAM) acts as the buffer role in pyramid-like memory hierarchy to compensate the speed gap between processors and bottom-level memories. Targeting a larger capacity of SRAM arrays with higher performance and lower cost, both designers and manufacturers are driving efforts to minimize the footprint of SRAM cells. Also, both active energy and leakage power considerations make operating voltage scaling significantly compelling for SRAM. However, continued increase in variability consisting of time-zero and time-dependent variability is perceived to be a major roadblock for future operating voltage scaling. Thus, variability analysis in SRAM becomes critical for both gaining a deeper understanding of the sources of variability and for developing more robust circuits.

By adopting the intrinsic channel, silicon-on-Thin-BOX (SOTB) – in other words, fullydepleted (FD) silicon-on-insulator (SOI) – technology eliminates large time-zero variability from random dopant fluctuations (RDF) in CMOS bulk one. The immunity to RDF also helps suppress the impact of random telegraph noise (RTN). The big innovation facilitates the experimental demonstration of low-power SOTB SRAM cells operable down to sub-0.4 V regime. Considering the limited data to date, this work presents a comprehensive variability analysis on write stability in SRAM at low  $V_{DD}$  based on SOTB technology platform. Firstly, four commonly used write stability metrics – including write static noise margin (WSNM) from write butterfly curve,  $I_W$  from write N-curve, bit-line margin (BLM) from bitline method and combined word-line margin (CWLM) from word-line method – are compared in order to select the good candidate for write yield estimation at low  $V_{DD}$ . The core standard is that the selected one follows good normality and can correctly predict write failure. Bit-line method and word-line method are concluded as good candidates for write yield estimation at low  $V_{DD}$ . On the other hand, the non-normality of WSNM and  $I_W$  is clarified and ascribed to sub- $V_{th}$  operation of cell transistors at low  $V_{DD}$ . HSPICE simulation results help extend our conclusions up to ±6 sigma.

Besides, a new write stability metric is proposed for write yield estimation. The extended write butterfly curve extends the voltage sweeping range of conventional write butterfly curve. Due to the clearer emergence of failure mode, the extended write noise margin (E-WSNM) shows good normality and is demonstrated as a good metric for write yield estimation. More evidence is also given to support the newly proposed one.

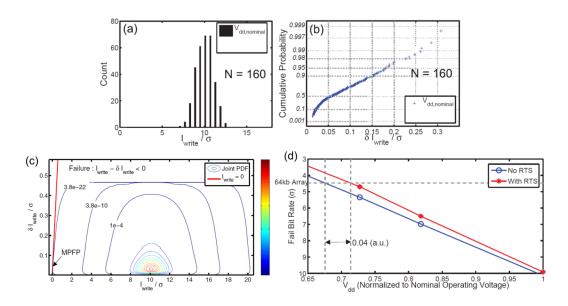

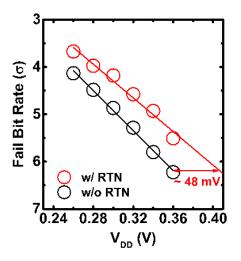

Lastly, a statistical model is developed to evaluate the impact of time-dependent RTN in SRAM at low  $V_{DD}$ . I<sub>W</sub> from write N-curve is selected as the write stability metric due to its being current-based one. Based on the distribution fitting of both I<sub>W</sub> and RTN-induced fluctuation ( $\delta$ I<sub>W</sub>), the degradation due to RTN on fail bit rate (FBR) is discussed. It is found that RTN degrades V<sub>min</sub> – the minimum voltage which guarantees stability of the whole capacity of SRAM arrays – over 10 % in sub-0.4 V regime, thus emphasizing the importance of RTN for low-power SRAM design.

Overall, our conclusions are not limited to SOTB technology but are applicable to other technologies such as FinFET SRAM, and give implications to SRAM design at low  $V_{DD}$ .

# Contents

| List of Figures                                           | iii              |

|-----------------------------------------------------------|------------------|

| Chapter 1 Background                                      | 1                |

| 1.1 SRAM Scaling and Challenging Issues                   | 1                |

| 1.1.1 Memory Hierarchy and SRAM Block Structure           |                  |

| 1.1.2 SRAM Cell and Operating Voltage Scaling             |                  |

| 1.1.3 Variability-limited Scaling                         |                  |

| 1.2 SOTB Technology for Low-power SRAM                    | 6                |

| 1.2.1 SOTB versus Bulk                                    | 6                |

| 1.2.2 Better Control in SOTB Transistors                  | 7                |

| 1.2.3 Sub-0.4V Operation in SOTB SRAM                     | 9                |

| 1.3 Research Goal                                         |                  |

| 1.4 Dissertation Outline                                  |                  |

| Chapter 2 Write Stability Characterization and Time-zero  | v Variability 13 |

| 2.1 Introduction                                          |                  |

| 2.1.1 Commonly Used Write Stability Metrics               |                  |

| 2.1.2 Contemporary Works                                  |                  |

| 2.2 Measurement Results in SOTB SRAM                      |                  |

| 2.2.1 Test Structure                                      | 23               |

| 2.2.2 Write Stability Characterization using Four Metrics |                  |

| 2.2.3 Further Discussions about Unpreferred Metrics       |                  |

| 2.3 HSPICE Simulation Results in SOTB SRAM                | 41               |

| 2.4 Measurement Results in Bulk SRAM                      |                  |

| 2.4.1 Write Stability Characterization and Four Metrics' Comparison4    |

|-------------------------------------------------------------------------|

| 2.4.2 Comparison with SOTB SRAM                                         |

| 2.4.3 Further Measurement in New Bulk Chip                              |

| 2.5 Summary                                                             |

| Chapter 3 Proposed New Write Stability Metric for Yield Estimation 58   |

| 3.1 Introduction                                                        |

| 3.1.1 Drawback of Conventional Write Butterfly Curve                    |

| 3.1.2 Definition of Extended Write Butterfly Curve                      |

| 3.2 Measurement Results in SOTB SRAM                                    |

| 3.2.1 Characterization using Extended Write Butterfly Curve             |

| 3.2.2 Comparison with Conventional Write Butterfly Curve                |

| 3.3 HSPICE Simulation Results in SOTB SRAM                              |

| 3.4 Summary                                                             |

| Chapter 4 Time-dependent Random Telegraph Noise in SRAM                 |

| 4.1 Introduction                                                        |

| 4.1.1 Dynamics of Random Telegraph Noise                                |

| 4.1.2 Random Telegraph Noise in Transistors72                           |

| 4.1.3 Random Telegraph Noise in SRAM                                    |

| 4.1.4 Contemporary Work                                                 |

| 4.2 Measurement and Modeling Results in SOTB SRAM                       |

| 4.2.1 Write N-curve as Write Stability Metric83                         |

| 4.2.2 Random Telegraph Noise Measurement in SRAM and Cell Transistors83 |

| 4.2.3 Statistical Distributions and Implications to SRAM Robustness85   |

| 4.3 Summary                                                             |

| Chapter 5 Conclusion                                                    |

| 5.1 Key Parts                                                           |

| 5.2 Future Work                                                         |

| Bibliography                                                            |

| Publication List                                                        |

# List of Figures

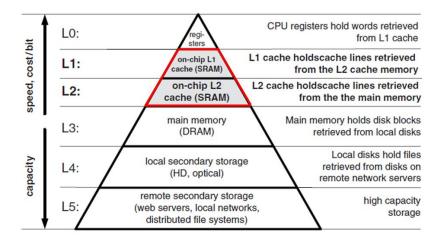

Fig. 1.1. Memory hierarchy of a personal computer [2].

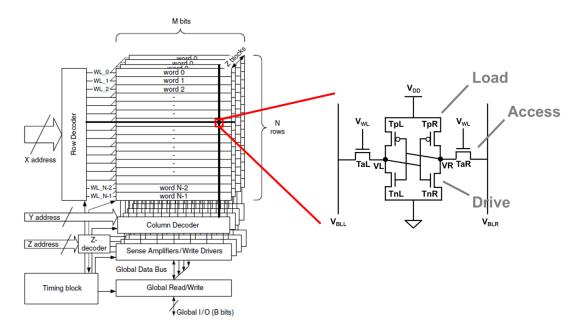

Fig. 1.2. SRAM block diagram [2].

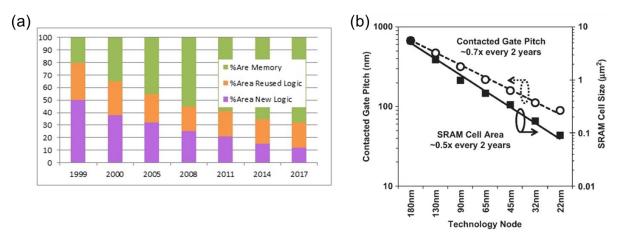

**Fig. 1.3.** (a) Area trends with scaling [4]. (b) Size trends with scaling: SRAM cell area vs. contacted gate pitch [5].

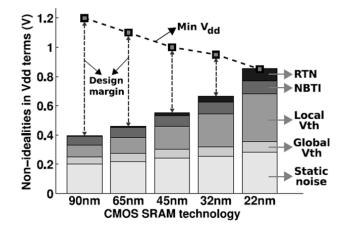

**Fig. 1.4.** SRAM voltage design margin trends with scaling under the impact of variability from different sources [26].

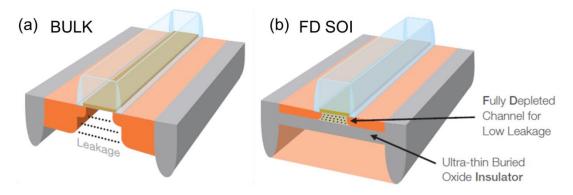

Fig. 1.5. Schematic of (a) bulk and (b) SOTB transistor [30].

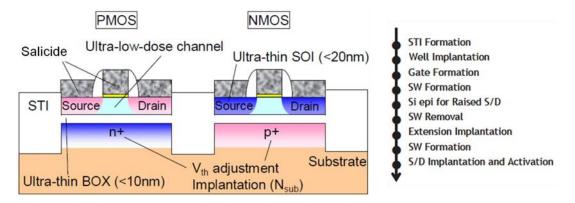

Fig. 1.6. Schematic of SOTB NMOS and PMOS with specified parameters [31-32].

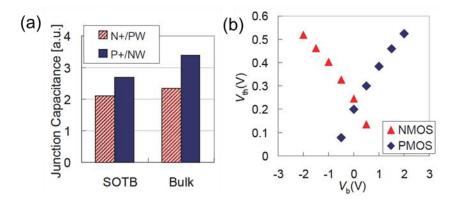

Fig. 1.7. (a) Comparison of junction capacitance in bulk and SOTB NMOS/ PMOS. (b) Demonstration of  $V_{th}$  adjustment by body biasing in SOTB NMOS/ PMOS. From Ref. [32].

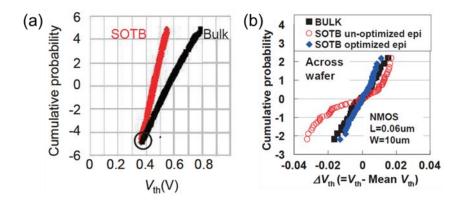

**Fig. 1.8.** (a)  $V_{th}$  distribution in both 1 M SOTB and bulk transistors. (b) Across-wafer  $V_{th}$  distribution in SOTB (w/ and w/o optimized process) and bulk NMOS. From Ref. [32].

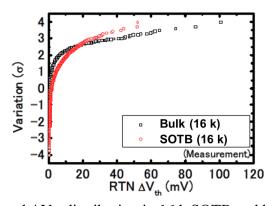

**Fig. 1.9.** RTN-induced  $\Delta V_{th}$  distribution in 16 k SOTB and bulk transistors [34].

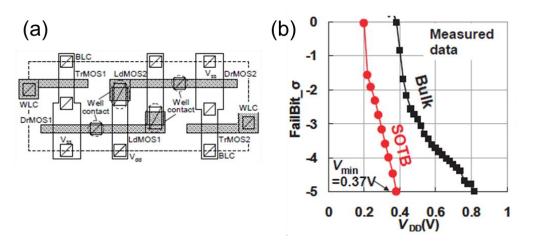

**Fig. 1.10.** (a) Layout of 6-T SOTB SRAM cell [31]. (b) Fail bit count in 2 Mb SOTB and bulk SRAM cells at different  $V_{DD}$  [32].

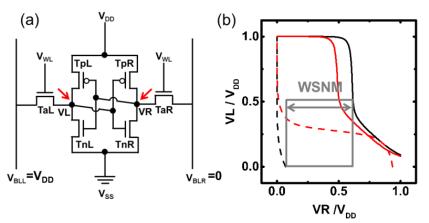

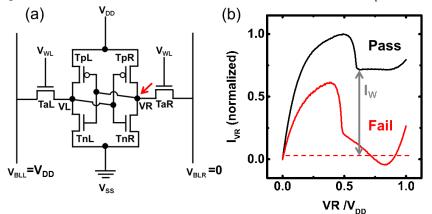

**Fig. 2.1.** (a) Schematic of 6-T SRAM cell with swept terminals indicated by red arrows. (b) Write butterfly curves of one SRAM cell (in black) which passes and the other one (in red) which fails. Take the stable SRAM cell as an example, its write noise margin – WSNM – is

defined by grey double arrow. Voltage is normalized to  $V_{DD}$ . Substrate bias:  $V_{bsn} = -1 V$ ,  $V_{bsp} = 1 V$ .

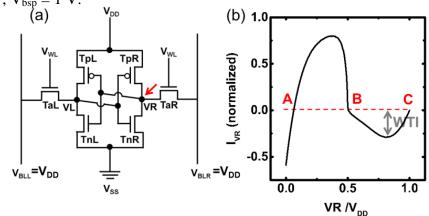

**Fig. 2.2.** (a) Schematic of 6-T SRAM cell with swept node indicated by red arrow. (b) Read N-curve of one SRAM cell. And its write ability – WTI – is defined by grey double arrow. Voltage/ current is normalized. Substrate bias:  $V_{bsn} = -1 V$ ,  $V_{bsp} = 1 V$ .

**Fig. 2.3.** (a) Schematic of 6-T SRAM cell with swept node indicated by red arrow. (b) Write N-curves of one SRAM cell (in black) which passes and the other one (in red) which fails. Take the stable SRAM cell as an example, its write noise margin  $-I_W$  – is defined by grey double arrow. Voltage/ current is normalized. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

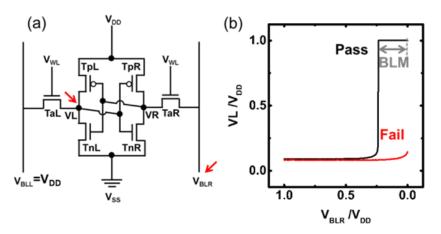

**Fig. 2.4.** Schematic of 6-T SRAM cell with swept terminals indicated by red arrows. (b) Measured waveforms in bit-line method of one SRAM cell (in black) which passes and the other one (in red) which fails. Take the stable SRAM cell as an example, its write noise margin – BLM – is defined by grey double arrow. Voltage is normalized to  $V_{DD}$ . Substrate bias:  $V_{bsn} = -1 \text{ V}$ ,  $V_{bsp} = 1 \text{ V}$ .

**Fig. 2.5.** Schematic of 6-T SRAM cell with swept terminals indicated by red arrows. (b) Measured waveforms in word-line method of one SRAM cell (in black) which passes and the other one (in red) which fails. Take the stable SRAM cell as an example, its write noise margin – CWLM – is defined by grey double arrow. Voltage is normalized to  $V_{DD}$ . Substrate bias:  $V_{bsn} = -1 \text{ V}$ ,  $V_{bsp} = 1 \text{ V}$ .

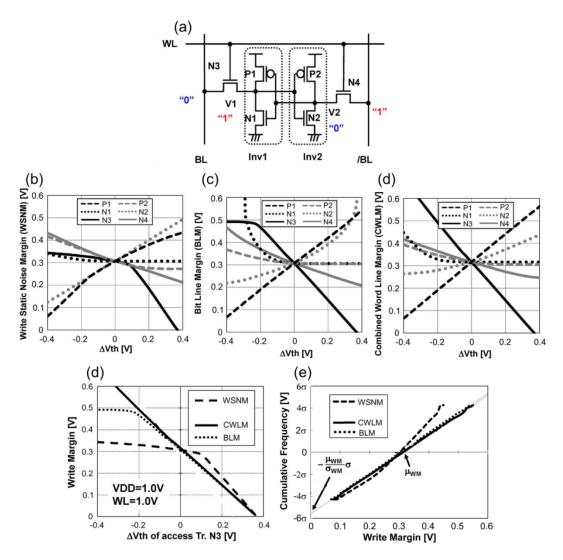

Fig. 2.6. (a) Schematic of 6-T SRAM cell with "0" originally stored. Dependence of (a) WSNM, (b) BLM, and (c) CWLM on  $\Delta V_{th}$  of all six cell transistors. (d) Dependence of WSNM/ BLM/ CWLM on  $\Delta V_{th}$  of N3. (e) Distribution of WSNM/ BLM/ CWLM. All simulations are performed at  $V_{DD} = 1.0$  V. From Ref. [41].

Fig. 2.7. Die photo of the 45 nm bulk SRAM test chip [38].

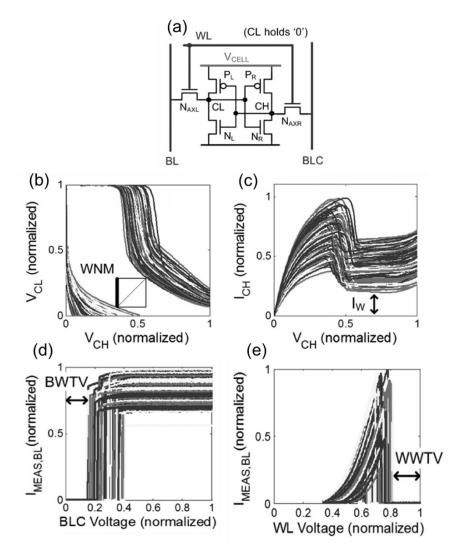

**Fig. 2.8.** (a) Schematic of 6-T SRAM cell. Measured (a) write butterfly curves, (c) write N-curves of SRAM macro and (d) waveforms in bit-line method, (e) waveforms in word-line method of functional SRAM arrays. Voltage is normalized to  $V_{DD}$ . From Ref. [38].

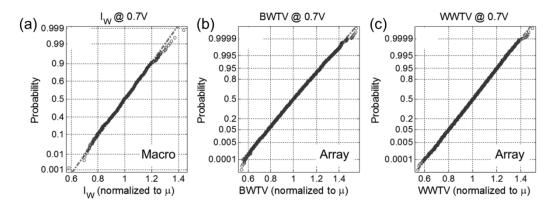

**Fig. 2.9.** Cumulative pots of (a)  $I_W$  of SRAM macro and (b) BWTV, (c) WWTV of functional SRAM arrays at  $V_{DD} = 0.7$  V. From Ref. [38].

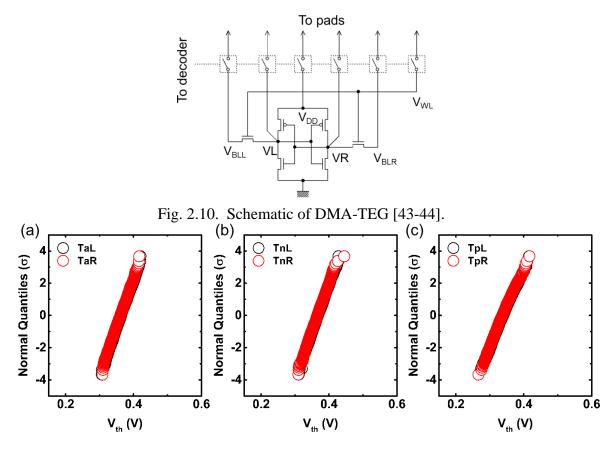

**Fig. 2.10.** Schematic of DMA-TEG [43-44].

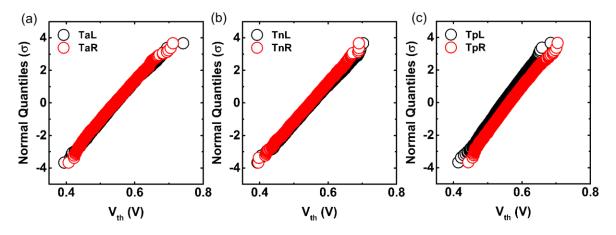

**Fig. 2.11.** Cumulative plots of V<sub>th</sub> of (a) TaL/ TaR, (b) TnL/ TnR, and (c) TpL/ TpR of 4 kb SOTB SRAM cells. Drain bias:  $|V_{ds}| = 50$  mV. Substrate bias:  $V_{bsn} = -1$  V, and  $V_{bsp} = 1$ V.

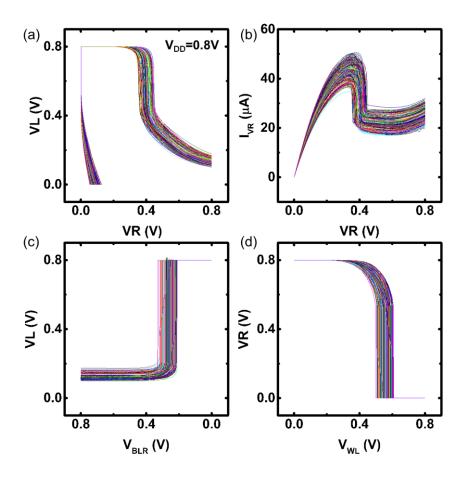

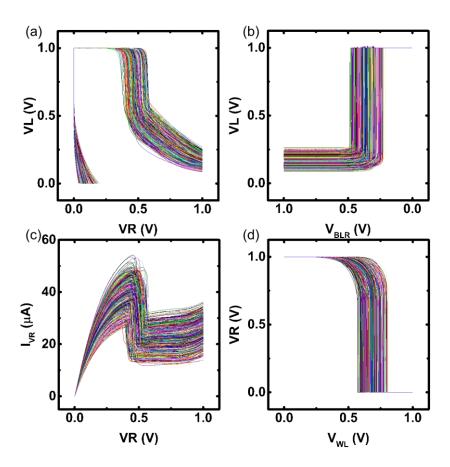

**Fig. 2.12.** Measured (a) write butterfly curves, (b) write N-curves, (c) waveforms in bit-line method, and (d) waveforms in word-line method of 4 kb SOTB SRAM cells at  $V_{DD} = 0.8$  V. Substrate bias:  $V_{bsn} = -1$  V, and  $V_{bsp} = 1$ V.

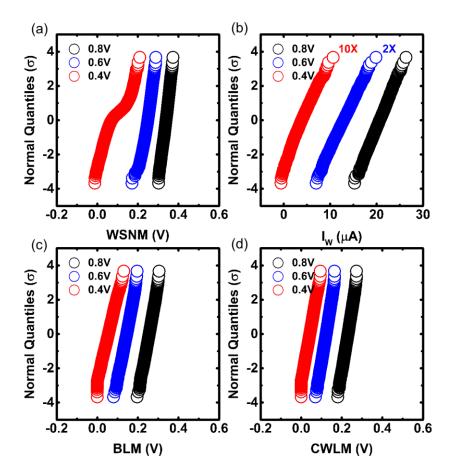

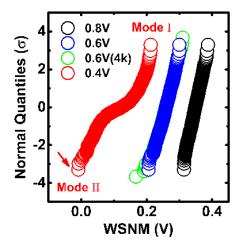

**Fig. 2.13.** Cumulative plots of (a) WSNM, (b)  $I_W$ , (c) BLM, and (d) CWLM of 4 kb SOTB SRAM cells at  $V_{DD} = 0.8$  V (in black), 0.6 V (in blue), and 0.4 V (in red). WSNM,  $I_W$ , BLM, CWLM are defined as the minimum of "0" and "1" write.  $I_W$  at  $V_{DD} = 0.6$  V and 0.4 V have been magnified by 2 and 10 times, respectively. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

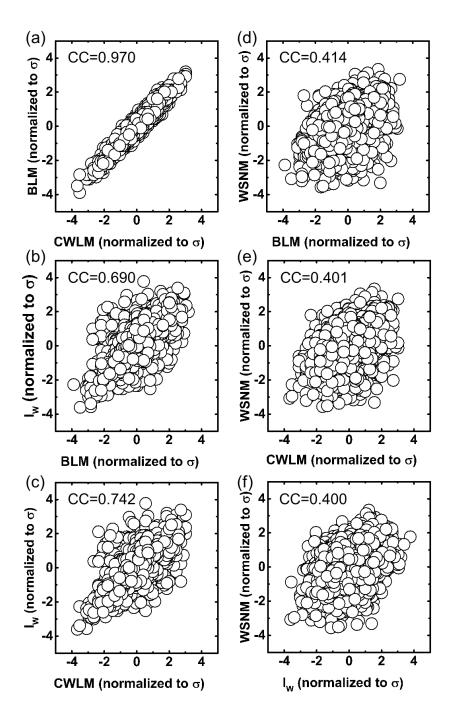

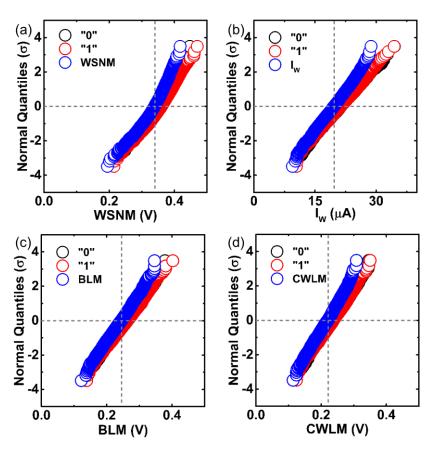

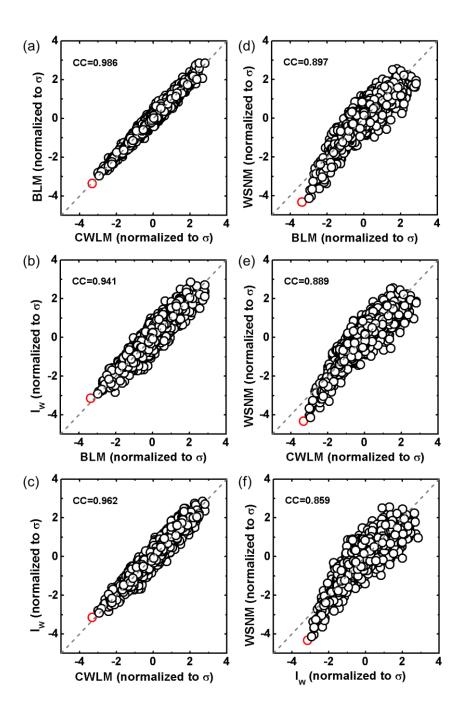

**Fig. 2.14.** Scatter plots of (a) BLM versus CWLM, (b)  $I_W$  versus BLM, (c)  $I_W$  versus CWLM, (d) WSNM versus BLM, (e) WSNM versus CWLM, and (f) WSNM versus  $I_W$  in 4 kb SOTB SRAM cells at  $V_{DD} = 0.8$  V. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

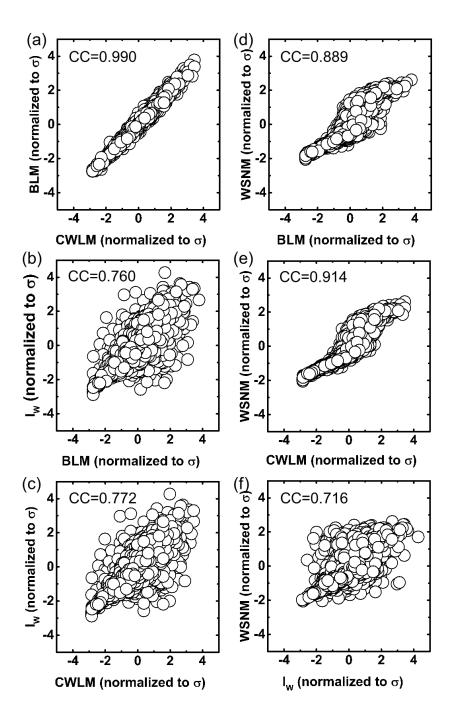

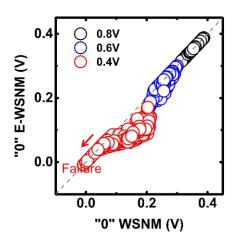

**Fig. 2.15.** Scatter plots of (a) BLM versus CWLM, (b)  $I_W$  versus BLM, (c)  $I_W$  versus CWLM, (d) WSNM versus BLM, (e) WSNM versus CWLM, and (f) WSNM versus  $I_W$  in 4 kb SOTB SRAM cells at  $V_{DD} = 0.4$  V. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

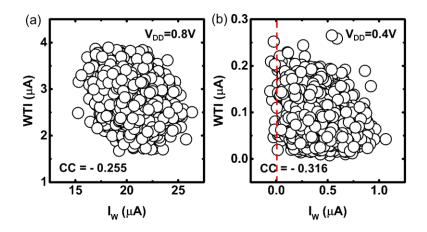

**Fig. 2.16.** Scatter plot of WTI from read N-curve versus  $I_W$  from write N-curve of 4 kb SOTB SRAM cells at (a)  $V_{DD} = 0.8$  V and (b)  $V_{DD} = 0.4$  V. Red dashed line indicates where  $I_W$  equals zero. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

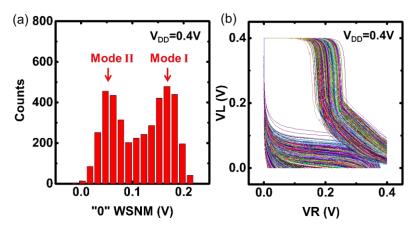

**Fig. 2.17.** (a) Histogram plot of "0" WSNM of 4 kb SOTB SRAM cells at  $V_{DD} = 0.4V$ . Two peaks are indicated by Mode I and Mode II, respectively. (b) Write butterfly curves of 4 kb SOTB SRAM cells in "0" write at  $V_{DD} = 0.4 V$ . Substrate bias:  $V_{bsn} = -1 V$ ,  $V_{bsp} = 1 V$ .

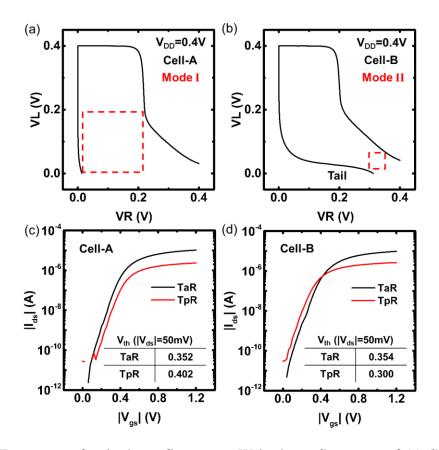

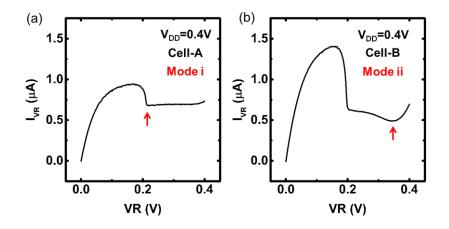

**Fig. 2.18.** Two types of write butterfly curves: Write butterfly curves of (a) Cell-A and (b) Cell-B in "0" write at  $V_{DD} = 0.4$  V. Cell-A/ Cell-B corresponds to Mode I/ II. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.  $|I_{ds}| - |V_{gs}|$  curves of TaR and TpR in (c) Cell-A and (d) Cell-B at drain bias of 50 mV. Inset: The threshold voltage ( $V_{thc}$ ) of TaR and TpR are listed.

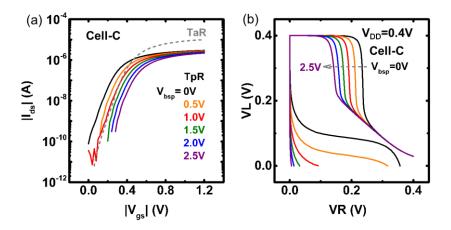

**Fig. 2.19.** (a)  $|I_{ds}|$ - $|V_{gs}|$  curves of TaR (grey dashed line) and TpR in Cell-C at  $V_{bsp} = 0$  V (black), 0.5 V (orange), 1.0 V (red), 1.5 V (green), 2.0 V (blue), and 2.5 V (purple). (b) Write butterfly curves of Cell-C in "0" write at  $V_{DD} = 0.4$  V. Substrate bias:  $V_{bsn} = -1$  V;  $V_{bsp} = 0$  V (in black), 0.5 V (orange), 1.0 V (red), 1.5 V (green), 2.0 V (blue), and 2.5 V (purple).

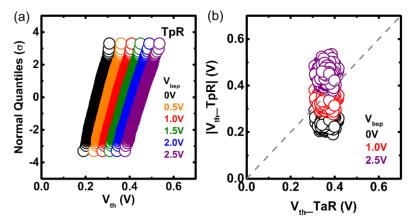

**Fig. 2.20.** (a) Cumulative plots of TpR's V<sub>thc</sub> in 1 kb SOTB SRAM cells at V<sub>bsp</sub> = 0 V (black), 0.5 V (orange), 1.0 V (red), 1.5 V (green), 2.0 V (blue), and 2.5 V (purple). Drain bias: -50 mV. (b) Scatter plot of TpR's V<sub>thc</sub> versus TaR's V<sub>thc</sub>. Drain bias:  $|V_{ds}| = 50$  mV. Substrate bias:  $V_{bsn} = -1$  V;  $V_{bsp} = 0$  V (black), 1.0 V (red), and 2.5 V (purple).

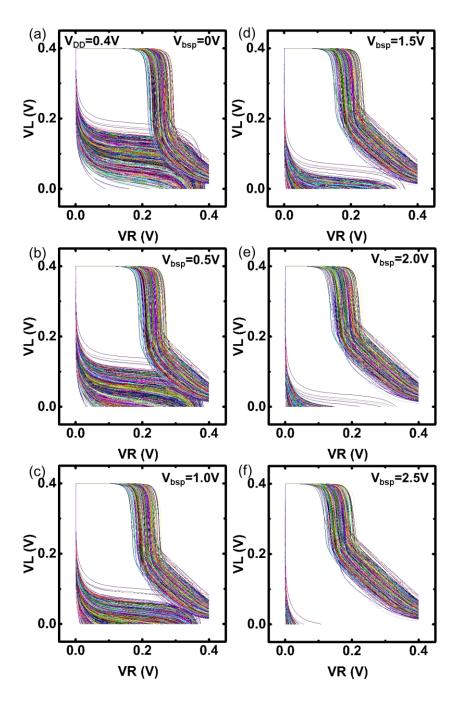

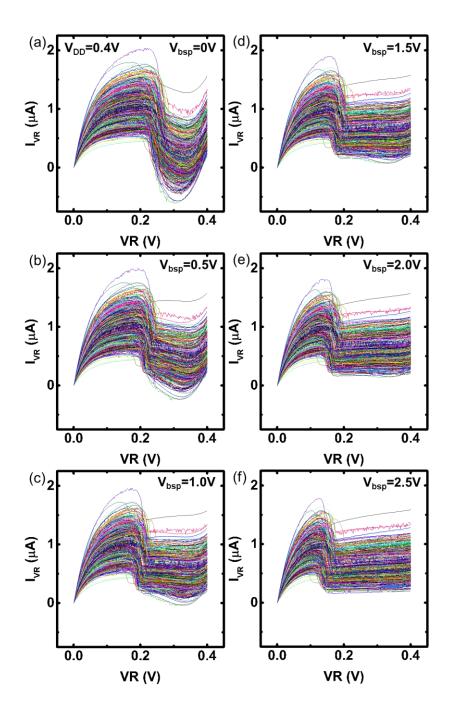

**Fig. 2.21.** Write butterfly curves of 1 kb SOTB SRAM cells in "0" write at  $V_{DD} = 0.4$  V. Substrate bias:  $V_{bsn} = -1$  V, (a)  $V_{bsp} = 0$  V, (b)  $V_{bsp} = 0.5$  V, (c)  $V_{bsp} = 1.0$  V, (d)  $V_{bsp} = 1.5$  V, (e)  $V_{bsp} = 2.0$  V, (f)  $V_{bsp} = 2.5$  V.

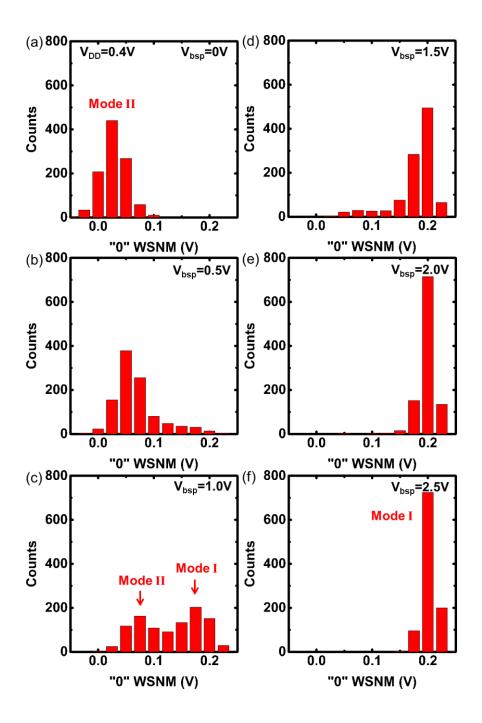

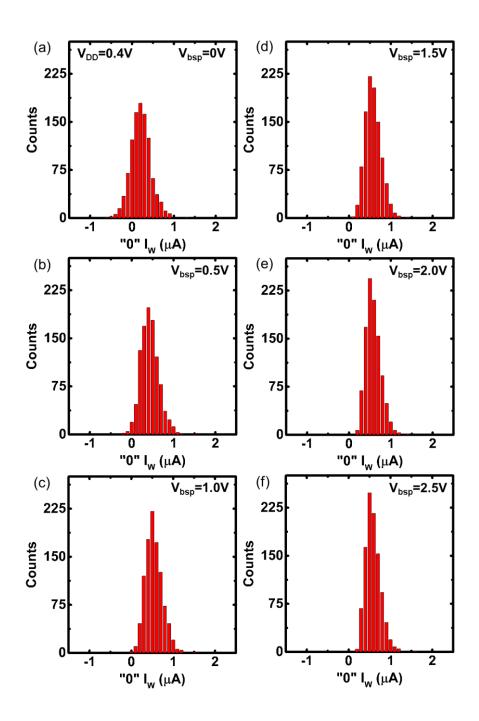

**Fig. 2.22.** Histogram plots of 1 kb SOTB SRAM cells in "0" write at  $V_{DD} = 0.4$  V. Substrate bias:  $V_{bsn} = -1$  V, (a)  $V_{bsp} = 0$  V, (b)  $V_{bsp} = 0.5$  V, (c)  $V_{bsp} = 1.0$  V, (d)  $V_{bsp} = 1.5$  V, (e)  $V_{bsp} = 2.0$  V, (f)  $V_{bsp} = 2.5$  V.

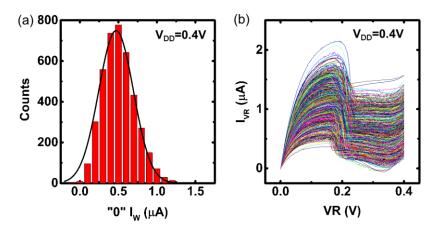

**Fig. 2.23.** (a) Write N-curves of 4 kb SOTB SRAM cells in "0" write at  $V_{DD} = 0.4$  V. (b) Histogram plot of "0"  $I_W$  of 4 kb SOTB SRAM cells at  $V_{DD} = 0.4$  V. The black curve indicates fitting result of normal distribution function. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

**Fig. 2.24.** Two types of write N-curves: Write N-curves of Cell-A and Cell-B (the same as in Fig. 2.20) in "0" write at  $V_{DD} = 0.4$  V. Cell-A/ Cell-B corresponds to Mode i/ Mode ii. The position where "0" I<sub>w</sub> is extracted is indicated by red arrow. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

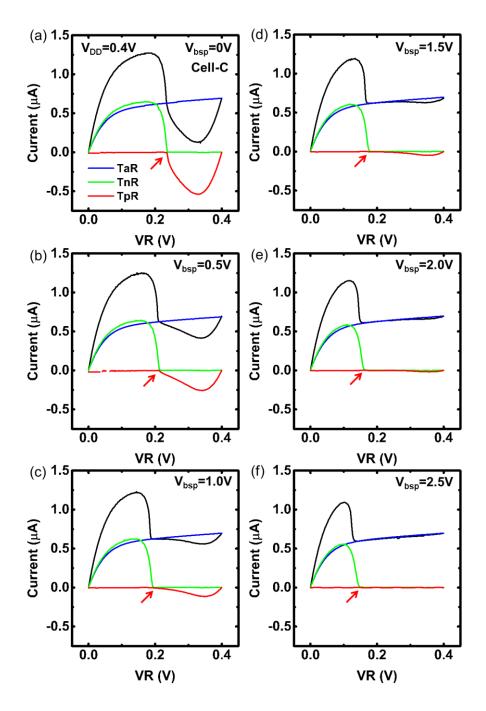

**Fig. 2.25.** Measured currents in TaR (in blue), TnR (in green) and TpR (in red) contributing to write N-curve (in black) of Cell-C in "0" write at  $V_{DD} = 0.4$  V. Substrate bias:  $V_{bsn} = -1$  V, (a)  $V_{bsp} = 0$  V, (b)  $V_{bsp} = 0.5$  V, (c)  $V_{bsp} = 1.0$  V, (d)  $V_{bsp} = 1.5$  V, (e)  $V_{bsp} = 2.0$  V, (f)  $V_{bsp} = 2.5$  V. Here, the positive direction of current is defined as flowing outside node VR.

**Fig. 2.26.** Write N-curves of 1 kb SOTB SRAM cells in "0" write at  $V_{DD} = 0.4$  V. Substrate bias:  $V_{bsn} = -1$  V, (a)  $V_{bsp} = 0$  V, (b)  $V_{bsp} = 0.5$  V, (c)  $V_{bsp} = 1.0$  V, (d)  $V_{bsp} = 1.5$  V, (e)  $V_{bsp} = 2.0$  V, (f)  $V_{bsp} = 2.5$  V.

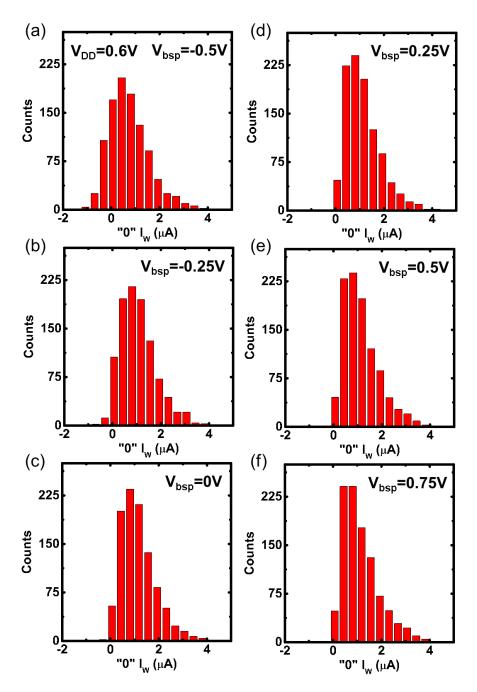

**Fig. 2.27.** Histogram plots of "0"  $I_W$  of 1 kb SOTB SRAM cells in "0" write at  $V_{DD} = 0.4 V$ . Substrate bias:  $V_{bsn} = -1 V$ , (a)  $V_{bsp} = 0 V$ , (b)  $V_{bsp} = 0.5 V$ , (c)  $V_{bsp} = 1.0 V$ , (d)  $V_{bsp} = 1.5 V$ , (e)  $V_{bsp} = 2.0 V$ , (f)  $V_{bsp} = 2.5 V$ .

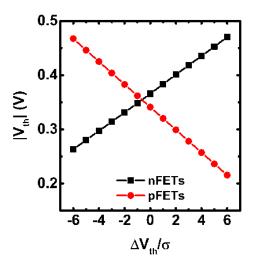

**Fig. 2.28.**  $V_{th}$  is changed from -6 sigma to 6 sigma in nFETs/ pFETs.

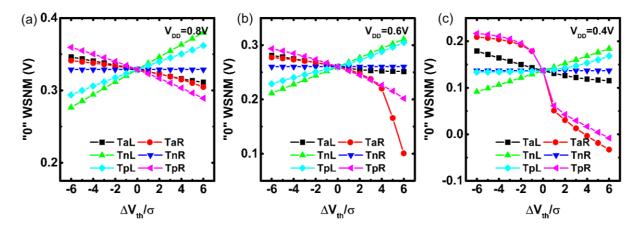

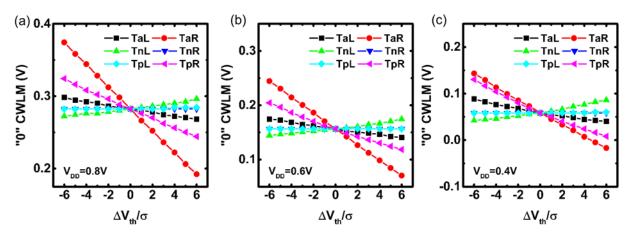

Fig. 2.29. Dependence of "0" WSNM on  $\Delta V_{th}$  of six cell transistors at  $V_{DD}$  = (a) 0.8 V, (b) 0.6 V, and (c) 0.4 V.

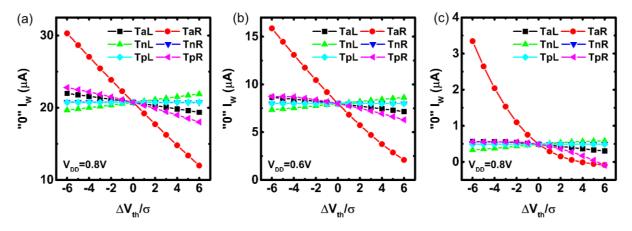

**Fig. 2.30.** Dependence of "0"  $I_W$  on  $\Delta V_{th}$  of six cell transistors at  $V_{DD} = (a) 0.8 V$ , (b) 0.6 V, and (c) 0.4 V.

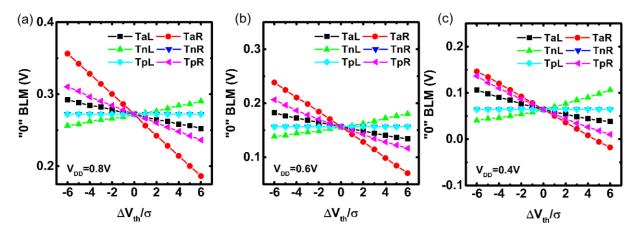

Fig. 2.31. Dependence of "0" BLM on  $\Delta V_{th}$  of six cell transistors at  $V_{DD} = (a) 0.8 V$ , (b) 0.6 V, and (c) 0.4 V.

Fig. 2.32. Dependence of "0" CWLM on  $\Delta V_{th}$  of six cell transistors at  $V_{DD} = (a) 0.8 V$ , (b) 0.6 V, and (c) 0.4 V.

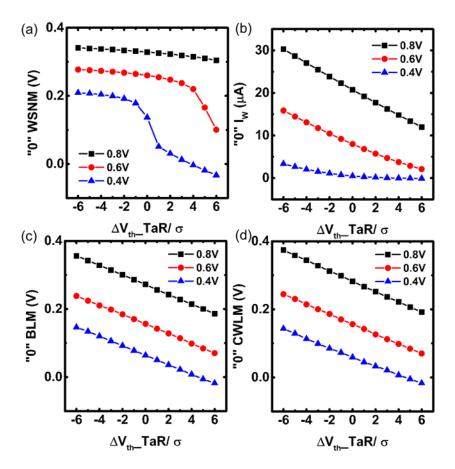

Fig. 2.33. Dependence of (a) "0" WSNM, (b) "0" I<sub>W</sub>, (c) "0" BLM, and (d) "0" CWLM on

$\Delta V_{\text{th}}$  of six cell transistors at  $V_{\text{DD}} = 0.4$  V.

**Fig. 2.34.** Cumulative plots of V<sub>th</sub> of (a) TaL/ TaR, (b) TnL/ TnR, and (c) TpL/ TpR of 4 kb bulk SRAM cells. Drain bias:  $|V_{ds}| = 50$  mV. Substrate bias:  $V_{bsn} = -0.8$  V, and  $V_{bsp} = 0.25$  V.

**Fig. 2.35.** Measured (a) write butterfly curves, (b) write N-curves, (c) waveforms in bit-line method, and (d) waveforms in word-line method of 4 kb bulk SRAM cells at  $V_{DD} = 1.0$  V. Substrate bias:  $V_{bsn} = -0.8$  V, and  $V_{bsp} = 0.25$  V.

**Fig. 2.36.** Cumulative plots of (a) WSNM, (b)  $I_W$ , (c) BLM, and (d) CWLM of 4 kb bulk SRAM cells at  $V_{DD} = 1.0$  V (in black), 0.8 V (in blue), and 0.6 V (in red). WSNM,  $I_W$ , BLM, CWLM are defined as the minimum of "0" and "1" write. Substrate bias:  $V_{bsn} = -0.8$  V,  $V_{bsp} = 0.25$  V.

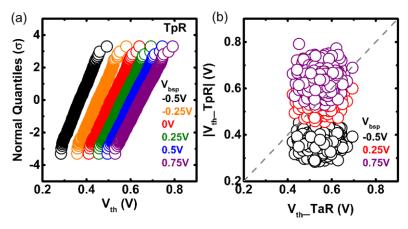

**Fig. 2.37.** (a) Cumulative plots of TpR's V<sub>thc</sub> in 1 kb bulk SRAM cells at V<sub>bsp</sub> = -0.5 V (black), -0.25 V (orange), 0 V (red), 0.25 V (green), 0.5 V (blue), and 0.75 V (purple). Drain bias: -50 mV. (b) Scatter plot of TpR's V<sub>thc</sub> versus TaR's V<sub>thc</sub>. Drain bias:  $|V_{ds}| = 50$  mV. Substrate bias: V<sub>bsn</sub> = -0.8 V; V<sub>bsp</sub> = -0.5 V (black), 0.25 V (red), and 0.75 V (purple).

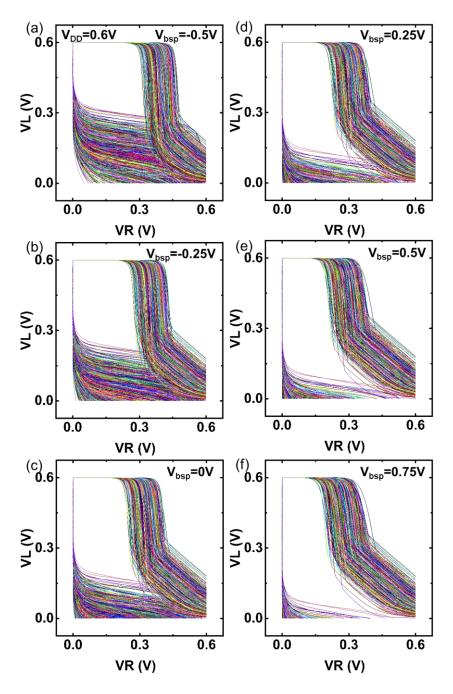

**Fig. 2.38.** Write butterfly curves of 1 kb bulk SRAM cells in "0" write at  $V_{DD} = 0.6$  V. Substrate bias:  $V_{bsn} = -0.8$  V, (a)  $V_{bsp} = -0.5$  V, (b)  $V_{bsp} = -0.25$  V, (c)  $V_{bsp} = 0$  V, (d)  $V_{bsp} = 0.25$  V, (e)  $V_{bsp} = 0.5$  V, (f)  $V_{bsp} = 0.75$  V.

**Fig. 2.39.** Histogram plots of 1 kb bulk SRAM cells in "0" write at  $V_{DD} = 0.6$  V. Substrate bias:  $V_{bsn} = -0.8$  V, (a)  $V_{bsp} = -0.5$  V, (b)  $V_{bsp} = -0.25$  V, (c)  $V_{bsp} = 0$  V, (d)  $V_{bsp} = 0.25$  V, (e)  $V_{bsp} = 0.5$  V, (f)  $V_{bsp} = 0.75$  V.

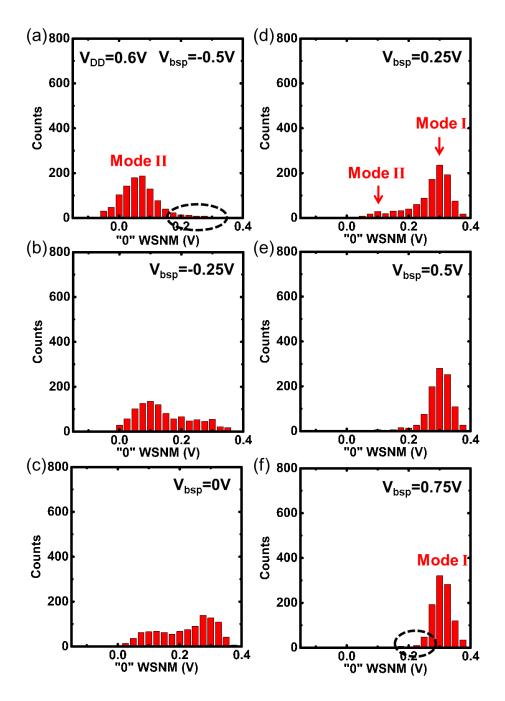

Fig. 2.40. Write N-curves of 1 kb bulk SRAM cells in "0" write at  $V_{DD} = 0.6$  V. Substrate bias:  $V_{bsn} = -0.8$  V, (a)  $V_{bsp} = -0.5$  V, (b)  $V_{bsp} = -0.25$  V, (c)  $V_{bsp} = 0$  V, (d)  $V_{bsp} = 0.25$  V, (e)  $V_{bsp} = 0.5$  V, (f)  $V_{bsp} = 0.75$  V.

Fig. 2.41. Histogram plots of "0"  $I_W$  of 1 kb bulk SRAM cells in "0" write at  $V_{DD} = 0.6$  V.

Substrate bias:  $V_{bsn} = -0.8 V$ , (a)  $V_{bsp} = -0.5 V$ , (b)  $V_{bsp} = -0.25 V$ , (c)  $V_{bsp} = 0 V$ , (d)  $V_{bsp} = 0.25 V$ , (e)  $V_{bsp} = 0.5 V$ , (f)  $V_{bsp} = 0.75 V$ .

**Fig. 2.42.** Cumulative plots of (a) WSNM, (b)  $I_W$ , (c) BLM, and (d) CWLM in 1 kb bulk SRAM cells at  $V_{DD} = 0.9$  V. Write noise margin is the minimum between "0" and "1" write. **Fig. 2.43.** Scatter plots of (a) BLM versus CWLM, (b)  $I_W$  versus BLM, (c)  $I_W$  versus CWLM, (d) WSNM versus BLM, (e) WSNM versus CWLM, and (f) WSNM versus  $I_W$  of 1 kb bulk SRAM cells at  $V_{DD} = 0.9$  V. The red circle indicates the SRAM cell with smallest write noise margin.

Fig. 3.1. (a) Schematic of 6-T SRAM cell. (b) Scatter plots of WSNM versus  $\Delta V_{th}$  of N3 at  $V_{DD} = 1.0$  V and 0.75 V. From Ref. [49].

**Fig. 3.2.** Cumulative plots of WSNM in 1 kb SOTB SRAM cells at  $V_{DD} = 0.8$  V (black), 0.6 V (blue), and 0.4 V (red). Black and blue circles correspond to Mode I. Green circles indicate WSNM of 4 kb cells at  $V_{DD} = 0.6$  V. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

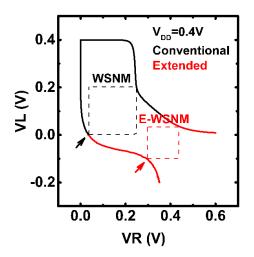

Fig. 3.3. Conventional and extended BC of one SRAM cell at  $V_{DD} = 0.4$  V. WSNM/ E-WSNM is extracted as the side of black/ red square. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

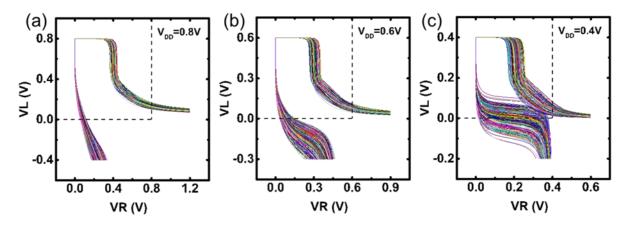

**Fig. 3.4.** Extended BCs of 1 kb SOTB SRAM cells at  $V_{DD} = (a) 0.8V$ , (b) 0.6V, and (c) 0.4 V. The black dashed lines indicate voltage sweep range of conventional BCs. Substrate bias:  $V_{bsn} = -1 V$ ,  $V_{bsp} = 1 V$ .

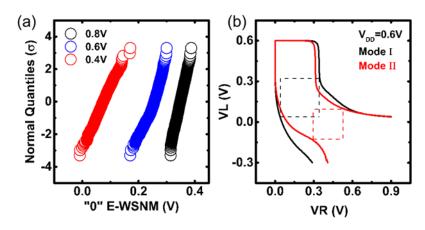

**Fig. 3.5.** (a) Cumulative plots of "0" E-WSNM in 1 kb SOTB SRAM cells at  $V_{DD} = 0.8$  V (black), 0.6 V (blue), and 0.4 V (red). (b) Mode-I and Mode-II extended BCs of two cells at  $V_{DD} = 0.6$  V. WSNM/ E-WSNM is extracted from black/ red square. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

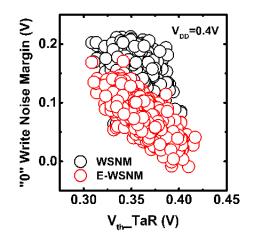

**Fig. 3.6.** Scatter plots of "0" E-WSNM versus "0" WSNM in 1 kb SOTB SRAM cells at  $V_{DD}$ = 0.8 V (black), 0.6 V (blue) and 0.4 V (red). Substrate bias:  $V_{bsn}$  = -1 V,  $V_{bsp}$  = 1 V. **Fig. 3.7.** Scatter plot of "0" E-WSNM (red)/ "0" WSNM (black) versus  $V_{th}$  of TaR in 1 kb SOTB SRAM cells at  $V_{DD} = 0.4$  V. Drain bias for  $V_{th}$  measurement is 50 mV. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

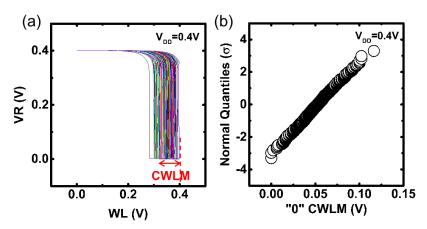

**Fig. 3.8.** Measured waveforms of word-line method in 1 kb SOTB SRAM cells at  $V_{DD} = 0.4$  V. CWLM is defined as the difference between  $V_{DD}$  and  $V_{WL}$  at which VR flips. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

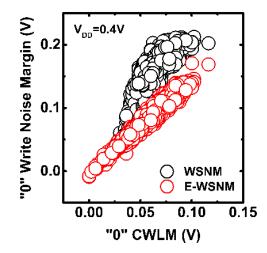

Fig. 3.9. Scatter plot of "0" E-WSNM (red)/ "0" WSNM (black) versus "0" CWLM in 1 kb SOTB SRAM cells at  $V_{DD} = 0.4$  V. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

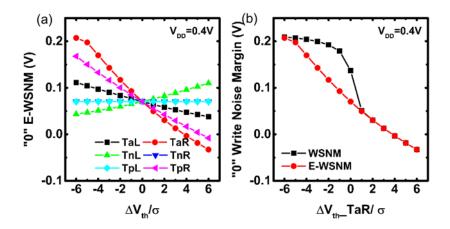

**Fig. 3.10.** (a) Dependence of "0" E-WSNM on  $\Delta V_{th}$  in six cell transistors at  $V_{DD} = 0.4$  V. (b) Dependence of "0" E-WSNM (in red)/ "0" WSNM (in black) on  $\Delta V_{th}$  in TaR at  $V_{DD} = 0.4$  V.

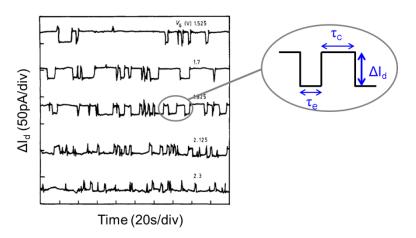

**Fig. 4.1.** Measured  $I_d$  waveform in transistor along with time [51]. Three RTN-related parameters are defined as inset.

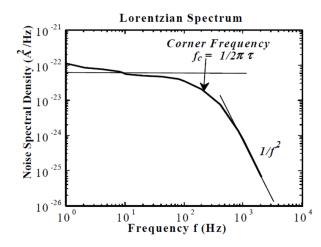

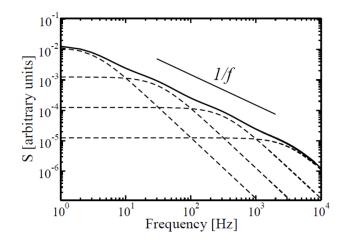

Fig. 4.2. One example of single-trap induced current spectral density [54].

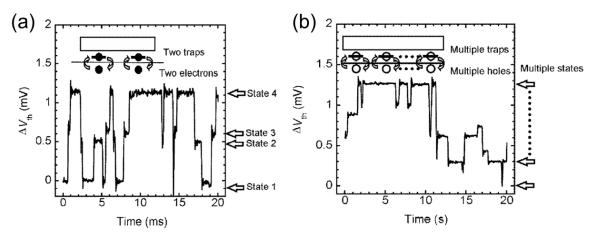

**Fig. 4.3.** RTN-induced  $\Delta V_{th}$  from (a) two traps and (b) multiple traps [55].

Fig. 4.4. One example of multiple-trap induced current spectral density [56].

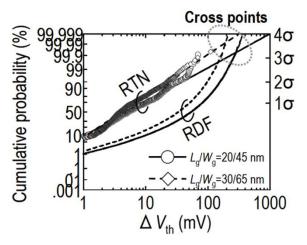

**Fig. 4.5.** Distributions of RTN-induced and RDF-induced  $V_{th}$  variations. Projected RTN-induced  $V_{th}$  variations exceed RDF-induced  $V_{th}$  variations at the ~ 2 sigma level in 22 nm generation [70].

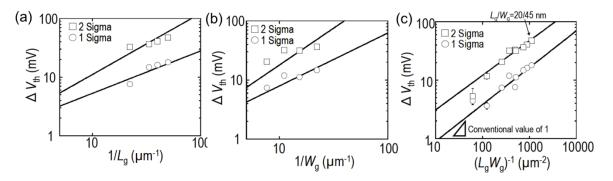

Fig. 4.6. (a)  $L_g$  dependence, (b)  $W_g$  dependence, and (c) size dependence of RTN-induced  $\Delta V_{th}$  at 1 or 2 sigma [70].

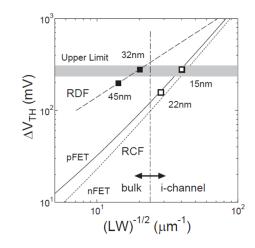

Fig. 4.7. Projected V<sub>th</sub> variation assuming intrinsic channel transistors [74].

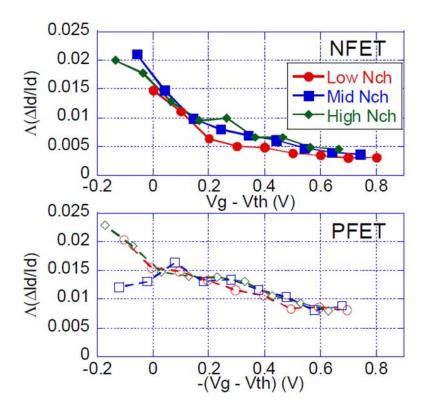

Fig. 4.8. Extracted gate voltage dependence of  $\Delta I_d/I_d$  in NFET and PFET [52].

**Fig. 4.9.** Estimated  $V_{th}$  window to guarantee the stable read/ write operation in 65 nm SRAM cells [55].

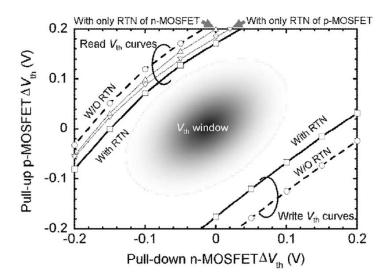

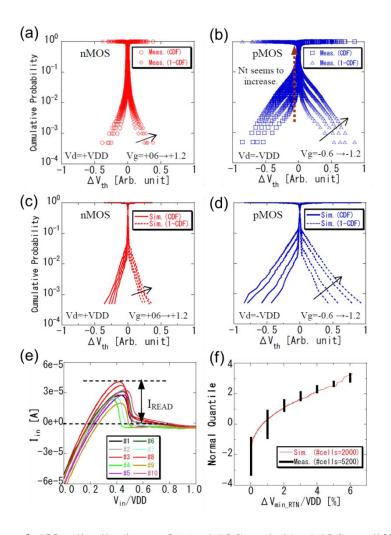

Fig. 4.10. Measured  $\Delta V_{th}$  distributions of (a) nMOS and (b) pMOS at different  $V_{gs}$  in 2 kb SRAM cells. Simulated results in (c) nMOS and (d) pMOS match the measured results well. (e) Simulated read N-curves and ten of them are selected for demonstration. I<sub>READ</sub> is defined as the read stability metric. (f) Cumulative plots of measured (in black) and simulated (in red)  $\Delta V_{min}/V_{DD}$ . From Ref. [77].

**Fig. 4.11.** (a) Accelerated test results (hollow circle) and simulation results (solid circle). Each bit suffers from 32 disturbs per cycle (i.e. entire 512kbit read). Simulated noise margin degradation by RTN in (b) 40 nm and (c) 22 nm technology. From Ref. [78].

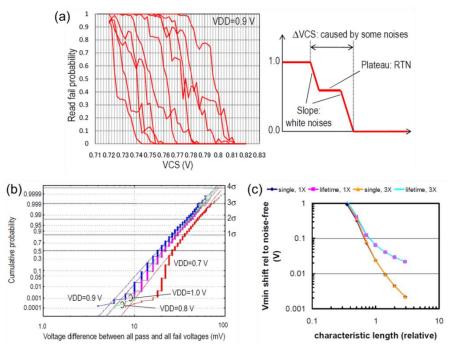

**Fig. 4.12.** (a) Measured fail probability transition in SRAM at  $V_{DD} = 0.9$  V. In the schematic,  $\Delta VCS$  is defined by difference between pass and fail voltage. (b)  $\Delta VCS$  distribution at different  $V_{DD}$ . (c) Calculated guard-band voltage in scaled SRAM assuming 1x and 3x trap density. From Ref. [79].

**Fig. 4.13.** (a) Histogram plot of  $I_{write}$  and (b) Gumbel plot of RTN-induced  $\delta I_{write}$  in 160 bulk SRAM cells at nominal  $V_{DD}$ . (c) Joint PDF plot of  $\delta I_{write}$  versus  $I_{write}$  at nominal  $V_{DD}$ . (c) FBR of SRAM at different  $V_{DD}$ . From Ref. [80].

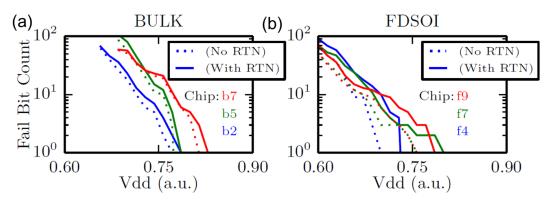

Fig. 4.14. Measured FBC in (a) bulk and (b) FDSOI SRAM at different  $V_{DD}$  and the impact of RTN is evaluated [81].

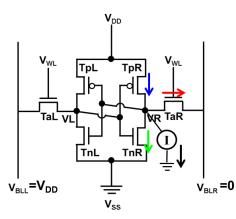

**Fig. 4.15.** Schematic of 6-T SRAM cell with  $I_{VR}$  (black arrow),  $I_{TaR}$  (red arrow),  $I_{TpR}$  (blue arrow), and  $I_{TnR}$  (green arrow) indicated during the measurement of write N-curve.

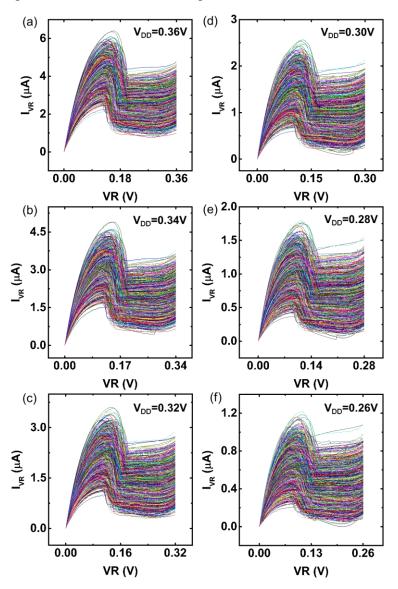

Fig. 4.16. Measured write N-curves in 4 kb SOTB SRAM cells at  $V_{DD} = (a) 0.36 V$ , (b) 0.34 V, (c) 0.32 V, (d) 0.30 V, (e) 0.28 V, and (f) 0.26 V.

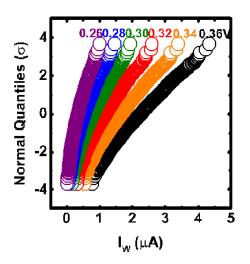

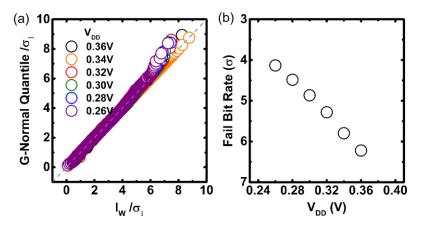

Fig. 4.17. Cumulative plots of measured  $I_W$  of write N-curves in 4 kb SOTB SRAM cells at different  $V_{DD}$  from 0.36 down to 0.26V.

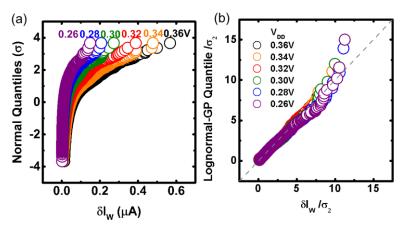

Fig. 4.18. Histogram plot of  $I_W$  in 32 kb SOTB SRAM cells at  $V_{DD} = 0.30$  V. The normal

distribution fit (black curve) shows a large deviation in tail region. (b) Quantile-quantile plot of  $I_W$  with the generalized normal distribution fit (grey dashed line).  $I_W$  is normalized by its standard deviation  $\sigma_1$ . (c) Calculated PDF plot of  $I_W$  with failure region enlarged. Failure edge is defined as  $I_W = 0$ .

**Fig. 4.19.** (a) Quantile-quantile plots of  $I_W$  in 4 kb SOTB SRAM cells at different  $V_{DD}$  with generalized normal distribution fit (grey dashed line).  $I_W$  is normalized by its standard deviation  $\sigma_1$ . (b) Calculated FBR at different  $V_{DD}$ .

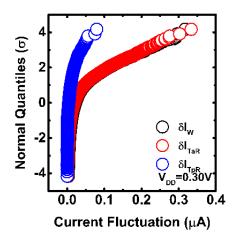

Fig. 4.20. Cumulative plots of measured  $\delta I_W$  and  $\delta I$  of cell transistors in 32 kb SOTB SRAM cells at  $V_{DD} = 0.30$  V.

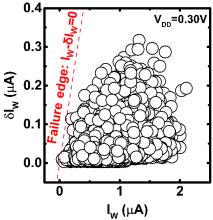

Fig. 4.21. Measured scatter plot of  $\delta I_W$  versus  $I_W$  in 32 kb SOTB SRAM cells at  $V_{DD} = 0.30$ V. Failure edge (red dashed line) is defined as:  $I_W - \delta I_W = 0$ .

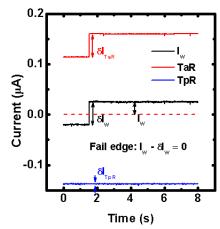

**Fig. 4.22.** Measured  $I_W$ , as well as its two components ( $I_{TaR}$  and  $I_{TpR}$ ), at  $V_{DD} = 0.26$  V along with time. The RTN-induced failure is demonstrated.

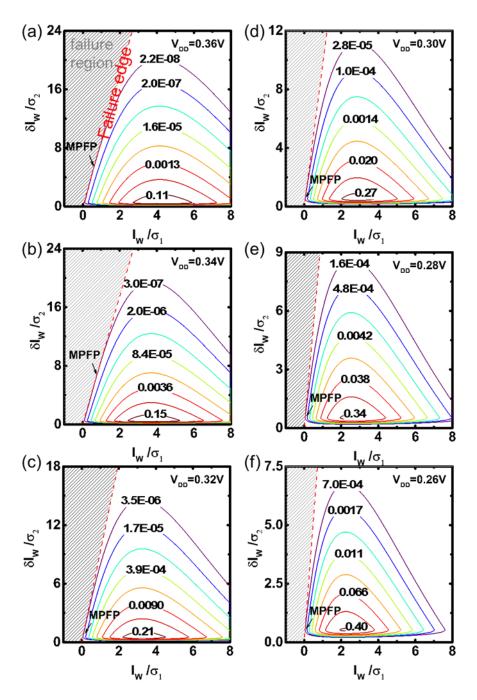

**Fig. 4.23.** Histogram plot of  $\delta I_W$  in 32 kb SOTB SRAM cells at  $V_{DD} = 0.30$  V. The lognormal distribution fit (black curve) shows a large deviation in tail region. (b) Quantilequantile plot of  $\delta I_W$  with lognormal-generalized pareto distribution fit (grey dashed line).  $\delta I_W$ is normalized by its standard deviation  $\sigma_2$ . (c) Calculated PDF plot of  $\delta I_W$ .

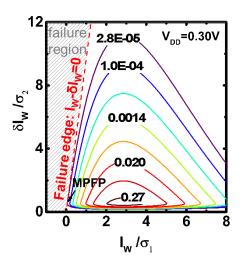

**Fig. 4.24.** Joint PDF plot of  $\delta I_W$  versus  $I_W$  at  $V_{DD} = 0.30$  V. Both  $I_W$  and  $\delta I_W$  are normalized by their standard deviations. The red dashed line and grey patterned area denote failure edge and failure region, respectively. The MPFP indicates where the cell fails in the largest probability.

**Fig. 4.25.** Cumulative plots of measured  $\delta I_W$  in 4 kb SOTB SRAM cells at different  $V_{DD}$  from 0.36 down to 0.26V. (b) Quantile-quantile plots of  $\delta I_W$  with lognormal-generalized pareto distribution fit (grey dashed line).  $\delta I_W$  is normalized by its standard deviation  $\sigma_2$ .

Fig. 4.26. Joint PDF plots of  $\delta I_W$  versus  $I_W$  at  $V_{DD} =$  (a) 0.36 V, (b) 0.34 V, (c) 0.32 V, (d) 0.30 V, (e) 0.28 V, and (f) 0.26 V.

**Fig. 4.27.** FBR of SRAM at different  $V_{DD}$ . Linear  $V_{DD}$  dependence is proposed both with and without RTN.

## Acknowledgments

I would like to begin by expressing my sincere gratitude to my thesis advisor – Prof. Toshiro Hiramoto – for his patient, yet focused, guidance throughout the course of this thesis. His broad, yet profound, knowledge of the issues and challenges faced by the low voltage CMOS devices and random variability in scaled transistors has paved ways for the breadths of projects conducted within our research group. I am particularly impressed with the level of fairness and integrity he brings to work and hope to take that with me in my future career life.

I would also like to thank Prof. Masaharu Kobayashi, for his gracious support as my coadvisor. I greatly appreciate his careful revisions during the preparations of a number of conference and journal publications. In addition, I am pleased to acknowledge many of his good suggestions to help pave my career path.

My research has been supported by The Japan Society for the Promotion of Science (JSPS) Fellowship. The chip fabrication donations were collaborated with Low-Power Electronics Association & Project (LEAP). I also acknowledge the support from The Ministry of Economy, Trade and Industry (METI) and The New Energy and Industrial Technology Development Organization (NEDO) in Japan.

I am grateful for International Multidisciplinary Engineering (IME) Graduate Program and all the help and support from the staff at the Electrical Engineering and Information Systems (EEIS) graduate office at The University of Tokyo.

I would also like to acknowledge many current and former colleagues in Hiramoto & Kobayashi Laboratory. In particular, I would like to thank Dr. Takuya Saraya for his patient and timely technical support; Ms. Tomoko Mizutani for her patient and gracious support with the lab large-scale measurement equipments; Dr. Kiyoshi Takeuchi for his instructive suggestions during the preparations of a number of conference and journal publications; Dr.

Alias Nurul Ezaila and Dr. Seung-Min Jung for their kind help at the beginning of this thesis; Mr. Akitsugu Ueda for his kind help of the basic electrical measurement guidance and Mr. Mitsuaki Nagao as my tutor to help adapt to Japan life; Ms. Miki Shiotani and Ms. Fumiko Oshita for their patient help on many administrative matters; all kinds of assistance from Dr. Waichi Nagashiro, Dr. Kazuo Ito, Dr. Toshihiko Takakura, Dr. Munetoshi Fukui, Dr. Shinichi Suzuki, Mr. Ki-Hyun Jang, Mr. Kyung-Min Jang, Mr. Nozomu Ueyama, Mr. Misumi Kawakami, Mr. Yuki Komine, Mr. Daiki Ueda, Mr. Yukihiro Tsuda, Mr. Shinta Terasawa, Mr. Katsuhisa Tanaka, Mr. Yuma Tanahashi, Mr. Hitoshi Ohno.

Finally, and certainly not the least, I would like to express my heartfelt appreciation for my parents, my wife – Xinyi Wang – and her entire family for their constant prayer and support throughout the hardest and darkest durations of my dissertation work.

# Chapter 1 Background

# 1.1 SRAM Scaling and Challenging Issues

## 1.1.1 Memory Hierarchy and SRAM Block Structure

Memory has been the driving force behind the rapid development of CMOS technology to meet the increasing demand for higher performance and lower power consumption in many different system applications. However, along with advances in processor technology, the speed gap between processors and memories has become intolerably large [1] and makes it necessary to introduce a memory hierarchy into the processor architecture, shown in Fig. 1.1 [2]. The pyramid-like hierarchy covers various kinds of memory ranging from the large capacity but off-chip memory on bottom level to small capacity but fast on-chip memory on top level to approximate the ideal memory behavior.

The advantages of adopting memory hierarchy include reduced cost, improved performance and lower power consumption [3]. The memory hierarchy differentiates data with various levels of access frequency in different storage media. By storing infrequently accessed data in bottom-level memory which is always less expansive, the cost of overall system can be reduced. Besides, by embedding the top-level memory inside a chip, the processor only needs to process the active working set inside the embedded memory. This greatly reduces the time in which the processor would otherwise wait for the required data to

Fig. 1.1. Memory hierarchy of a personal computer [2].

be available from the bottom-level memory. Lastly, accessing the off-chip memory consumes more power than accessing on-chip memory due to larger parasitic capacitance of off-chip wires. Adopting the memory hierarchy is advantageous to reduce the number of off-chip memory transactions, thus reducing power consumption.

Among embedded memories, six-transistor (6-T) based static random access memory (SRAM) plays an important role in nearly all VLSI systems due to its superior access speed and compatibility with logic process technology, compared to other candidates. Fig. 1.2 shows an example of the basic SRAM block structure [2], which consists of SRAM core and peripheral circuits, e.g., sense amplifiers with the corresponding pre-charge and equalization circuits, write drivers, and row/column decoders. The SRAM core is commonly organized as a number of arrays of N×M×Z, where N/M/Z is the number of rows/bits/blocks. With X-, Y-, and Z-decoder, each SRAM cell can be accessed, shown inset in Fig. 1.2.

The basic storage element of an SRAM consists of the pair of inverters and access transistors connected with bit lines and word lines. The pair of inverters is cross-coupled such that the input of one is just the output of the other. As a result, either logic "0" or logic "1" state can be held as long as the SRAM cell is powered up. This is different from the requisite periodically refreshing procedure in dynamic random access memory (DRAM) and enables

Fig. 1.2. SRAM block diagram [2].

SRAM a superior access speed.

## 1.1.2 SRAM Cell and Operating Voltage Scaling

SRAM occupies a significantly large segment of modern system-on-chips (SoCs). For example, the total percentage of occupied SRAM area of overall chip is estimated to reach over 70% in the near future, shown in Fig. 1.3(a) [4]. In order to incorporate large capacity of SRAM arrays into a chip to balance the requirements of boosting performance and reducing cost, both designers and manufacturers are driving efforts to minimize the footprint of SRAM cells. Fig. 1.3(b) shows scaling trend of contacted gate pitch and SRAM cell size [5]. According to Moore's Law that on-chip functionality doubles every two years, technology node scaling of 0.7 in linear size and 0.5 in area has to be carried out every two years.

Besides, power and energy consumption is the other critical factor for SRAM design. For active switching, operating voltage scaling acts effectively since active energy has a square dependence on supply voltage ( $V_{DD}$ ) [6-10]. On the other hand, leakage power also benefits from operating voltage scaling. Here, leakage power is more important than active energy

Fig. 1.3. (a) Area trends with scaling [4]. (b) Size trends with scaling: SRAM cell area vs. contacted gate pitch [5].

[11], considering that leakage in SRAM during retention dominates and its retention time is unrelated with operation or access delay. In addition, the reduction in leakage power can be greatly large, since a reduction of  $V_{DD}$  implies a smaller drain bias in nano-scale cell transistors and significantly alleviates drain-induced barrier lowering (DIBL). For example, in SRAM design with 65 nm technology, operating voltage scaling from 1 V to 0.3 V can reduce the leakage power by over a factor of 15 [12]. Therefore, both active energy and leakage power considerations make operating voltage scaling significantly compelling for SRAM.

### 1.1.3 Variability-limited Scaling

However, maintaining an acceptable stability in embedded SRAM while scaling size and operating voltage becomes increasingly challenging. The continuous delay of lithography in extreme ultraviolet lithography (EUV) forces the industry to keep pushing with double and quad processes, which results in device patterning challenges [13-14]. As a result, precise control of process parameters becomes extremely difficult and the increased process variability is translated into a wider distribution of characteristics. This part is determined during fabrication and is called time-zero variability, whose sources include random dopant fluctuation (RDF) in channel [15-16], line edge roughness (LER) in channel [17], work

Fig. 1.4. SRAM voltage design margin trends with scaling under the impact of variability from different sources [26].

function variation (WFV) in gate [18-19], and so on. On the other hand, time-dependent or post-fabrication variability – e.g., random telegraph noise (RTN) [20-21], bias temperature instability (BTI) [22-23], hot carrier injection (HCI) [24] and soft error induced by high-energy radiation [25] – introduces a growing concern about reliability in the design/ test community. That indicates that the SRAM cell even designed stable with process optimization can fail after a long term.

In addition, both time-zero and time-dependent variability increases with size scaling [26]. It causes large variation of stability in large capacity of SRAM arrays and pushes the cell with smallest margin towards failure edge, shown in Fig. 1.4. With an increased  $V_{min}$  in advanced node technology, the shrinking design margin makes operating voltage scaling much more difficult. Therefore, meeting SRAM design target with both size and operating voltage scaling requires a deep understanding of variability issue.

Fig. 1.5. Schematic of (a) bulk and (b) SOTB transistor [30].

## 1.2 SOTB Technology for Low-power SRAM

#### 1.2.1 SOTB versus Bulk

CMOS Bulk technology has played a long-term role on the scaling road up to 20/28 nm [27]. There are various issues regarding bulk technology [28], such as large RDF-induced variability and performance-degrading leakage between source and drain. Compared with bulk technology, the fully-depleted (FD) silicon-on-insulator (SOI) technology was proposed and promoted by the SOI industry consortium [29], aimed at leveraging the established planar process while ensuring a continuation of the efficient improvements projected by Moore's Law.

Fig. 1.5 gives the comparison between schematic of bulk and FD SOI transistor [30]. The main innovations in FD SOI technology compared to bulk one consist of a fully-depleted channel and an ultra-thin buried oxide insulator. Firstly, RDF-induced variability can be largely eliminated by adopting intrinsic channel. Besides, the buried oxide layer reduces the parasitic capacitance between the source and drain exhibited by bulk technology, allowing for reduction of active switching energy. It also constrains carriers flowing between the source and drain through body to significantly reduce performance-degrading leakage currents. Another advantage with the buried oxide layer is an efficient body biasing. Due to isolation

Fig. 1.6. Schematic of SOTB NMOS and PMOS with specified parameters [31-32].

between body and source/drain, strong biasing voltages can be applied to dynamically switch FD SOI transistor between modes of speed and power efficiency. Other than technological innovations, FD SOI process is an important evolutionary step from bulk CMOS process and can leverage much of the design tools, manufacturing infrastructure, and IP ecosystem already in place.

#### 1.2.2 Better Control in SOTB Transistors

Silicon-on-Thin-BOX (SOTB) [31-32] is one of the FD SOI technologies. The above two innovations in FD SOI give a better control in SOTB transistors compared to bulk ones. Schematic of SOTB NMOS and PMOS with optimized process in 65 nm technology is shown in Fig. 1.6 [31-32]. As is discussed before, the buried oxide layer reduces junction capacitance both in NMOS and PMOS in Fig. 1.7(a). Also, due to its thin thickness ~ 10 nm, an efficient body biasing is demonstrated. For example, a reverse bias of 1 V realizes a large  $V_{th}^{1}$  shift ~ 150 mV in both NMOS and PMOS in Fig. 1.7(b).

Fig 1.8(a) shows distribution of both  $V_{th}$  and  $I_{on}$  of 1 M SOTB transistors. Firstly, both follow a normal distribution up to  $\pm 5$  sigma, contrary to the pessimistic predictions by simulation [33]. Due to the adoption of intrinsic channel, variability of both  $V_{th}$  and  $I_{on}$  is

<sup>&</sup>lt;sup>1</sup> All through the text in this thesis,  $V_{th}$  is defined as threshold voltage at constant current ( $I_d=10^{-7}\times W/L$ , W and L is gate width and gate length, respectively).

Fig. 1.7. (a) Comparison of junction capacitance in bulk and SOTB NMOS/ PMOS. (b) Demonstration of  $V_{th}$  adjustment by body biasing in SOTB NMOS/ PMOS. From Ref. [32].

Fig. 1.8. (a)  $V_{th}$  distribution in both 1 M SOTB and bulk transistors. (b) Acrosswafer  $V_{th}$  distribution in SOTB (w/ and w/o optimized process) and bulk NMOS. From Ref. [32].

Fig. 1.9. RTN-induced  $\Delta V_{th}$  distribution in 16 k SOTB and bulk transistors [34]. much smaller than in bulk transistors. Here, the bulk transistor with the largest leakage is tuned the same as SOTB one for comparison. And it is found that the drive current in SOTB

transistor exhibits twice as in bulk transistor (not shown here). In addition, Fig. 1.8(b) shows

Fig. 1.10. (a) Layout of 6-T SOTB SRAM cell [31]. (b) Fail bit count in 2 Mb SOTB and bulk SRAM cells at different  $V_{DD}$  [32].

across-wafer  $V_{th}$  distribution in bulk and SOTB NMOS for comparison. With optimized S/Depitaxial process, the global variability is shown as good as bulk technology, implying that thickness variability of both top and buried oxide layer is not a big issue in SOTB technology.

Besides time-zero variability, time-dependent variability is also compared between bulk and SOTB technology [34]. Take RTN as an example. Fig. 1.9 shows distributions of RTNinduced  $\Delta V_{th}$  in 16 k bulk and SOTB transistors. Different from the normal distribution of  $V_{th}$ , they both show long-tailed distributions. But the distribution in SOTB transistors has a smaller tail, ascribed to intrinsic channel with smaller number of traps. Therefore, both timezero and time-dependent variability is reduced in SOTB transistors compared to bulk ones.

#### 1.2.3 Sub-0.4V Operation in SOTB SRAM

Consisting of six transistors, in order for a better pattern reproducibility as well as good transistor  $V_{th}$  matching, the layout of SRAM cell beyond 90 nm technology preferred "wide" instead of "tall" one [35-36]. Fig. 1.10(a) shows the layout of 6-T SOTB SRAM which has a uniform orientation of all cell transistors [31]. Due to a much smaller variability compared to bulk technology, a larger margin is tolerable in SOTB SRAM design, thus making it possible to operate under low  $V_{DD}$ . Experimentally,  $V_{min}$  down to 0.37 V in active mode has been

demonstrated in 2 Mb SOTB SRAM cells [32]. Also, it can be seen that  $V_{min}$  in SOTB SRAM degrades linearly with increasing capacity. Differently, degradation of  $V_{min}$  in bulk SRAM becomes much worse beyond 3 sigma's capacity, which makes it difficult to predict yield in bulk SRAM. Thus, SOTB SRAM has demonstrated itself as a good candidate for low- $V_{DD}$  operation in sub-0.4 V regime.

## 1.3 Research Goal

Incorporation of large capacity of SRAM arrays into a chip calls for tightly-packed minimumsize cell transistors. With aggressive technology scaling, variability including time-zero and time-dependent variability increases and results in limited operating voltage scaling. On the other hand, by adoption of intrinsic channel which shows immunity to RDF, SOTB SRAM can operate down to sub-0.4 V regime. However, limited data has been published for the statistical variability analysis in SRAM at low V<sub>DD</sub>, which is critical for gaining a deeper understanding of the sources of variability and for developing robust low-power SRAM.

This dissertation facilitates the design of low-power embedded SRAM design in the presence of variability in the following ways:

Comparing different write stability metrics and selecting the good candidates for write yield estimation in SRAM at low V<sub>DD</sub>.

Write stability characterization is performed at large capacity of SOTB SRAM at low  $V_{DD}$  using several write stability metrics. Write noise margin is extracted for statistical analysis and the one that follows a normal distribution is preferred. The correlation between SRAM and cell transistors is established and the reason for improper write stability metrics is also clarified. In addition, on the basis of our results, one new write stability metric is proposed for write yield at low  $V_{DD}$ . Having a deeper understanding of various write stability metrics can help designers to better evaluate the guard-band for stable SRAM operation at low  $V_{DD}$ .

2) Evaluating the impact of time-dependent RTN on write yield in SRAM at low  $V_{DD}$ .

Besides time-zero variability, the time-dependent variability due to RTN is also considered. Through data analysis based on large-capacity SRAM measurement as well as modeling, the impact of RTN on write yield is evaluated. Also, degradation of  $V_{min}$  at specific SRAM capacity can be estimated which can help designers to enlarge design margin for robust SRAM in a long-term view.

## 1.4 Dissertation Outline

Chapter 2 targets the preferred write stability metric for write stability characterization in SOTB SRAM at low  $V_{DD}$  with our specially developed test-element-group (TEG). Several commonly used write stability metrics are introduced in details and four of them are compared. Based on statistical results, two of them are selected as preferred candidates for write yield estimation at low  $V_{DD}$  and further discussions are given regarding the other two. In addition, write stability characterization using four write stability metrics is also performed in bulk SRAM and compared with SOTB SRAM in low- $V_{DD}$  regime. Lastly, HSPICE simulations are performed to help extend our conclusions up to ±6 sigma.

Chapter 3 proposes a new write stability metric for write yield estimation in SRAM at low  $V_{DD}$ . On the basis of understanding of conventional write butterfly curve [37], an extended write stability metric is proposed. Write stability characterization results using this metric are presented in SOTB SRAM, where direct correlations between the extended and conventional write butterfly curve is established. In addition, more experimental evidence as well as HSPICE simulations supporting proposed metric for yield estimation at low  $V_{DD}$  is given.

Chapter 4 evaluates the effects of time-dependent RTN on write stability in SOTB SRAM at low  $V_{DD}$ . Selecting I<sub>w</sub> from write N-curve [38] as write stability metric, RTN measurement is performed in SRAM, which is also correlated with RTN in cell transistors. Considering the complex distribution of RTN, in order for yield estimation, statistical model is utilized to extend measurement results to a larger SRAM capacity and the effects of RTN are evaluated.

Chapter 5 presents a summary of this dissertation – highlighting the key parts of this work, along with future research directions.

# Chapter 2

# Write Stability Characterization and Time-zero Variability

## 2.1 Introduction

## 2.1.1 Commonly Used Write Stability Metrics

Butterfly curve was proposed by Seevink [39] and has been a popular method for read stability characterization in SRAM, since it considers SRAM cell as a pair of cross-couple inverters and is easy to understand. Afterwards, write butterfly curve [37] was utilized as the method for write stability characterization in a similar way. Since write operation relates to state flip in SRAM and is more complex than read operation, several more methodss are also proposed with their own advantages over write butterfly curve. Then, this section gives an introduction of commonly used write stability metrics, including the measurement method, cell pass/failure, and definition of write stability. Either logic "0"<sup>2</sup> or logic "1" state can be stored in one SRAM cell and the whole write stability is defined as the minimum of the two.

<sup>&</sup>lt;sup>2</sup> All through the text in this thesis, logic "0" write is focused if there is no special note.

Fig. 2.1. (a) Schematic of 6-T SRAM cell with swept terminals indicated by red arrows. (b) Write butterfly curves of one SRAM cell (in black) which passes and the other one (in red) which fails. Take the stable SRAM cell as an example, its write noise margin – WSNM – is defined by grey double arrow. Voltage is normalized to  $V_{DD}$ . Substrate bias:  $V_{bsn} = -1 V$ ,  $V_{bsp} = 1 V$ .

Fig. 2.2. (a) Schematic of 6-T SRAM cell with swept node indicated by red arrow. (b) Read N-curve of one SRAM cell. And its write ability – WTI – is defined by grey double arrow. Voltage/ current is normalized. Substrate bias:  $V_{bsn} = -1 V$ ,  $V_{bsp} = 1 V$ .

Fig. 2.3. (a) Schematic of 6-T SRAM cell with swept node indicated by red arrow. (b) Write N-curves of one SRAM cell (in black) which passes and the other one (in red) which fails. Take the stable SRAM cell as an example, its write noise margin  $-I_W$  – is defined by grey double arrow. Voltage/ current is normalized. Substrate bias:  $V_{bsn} = -1 V$ ,  $V_{bsp} = 1 V$ .

Fig. 2.4. Schematic of 6-T SRAM cell with swept terminals indicated by red arrows. (b) Measured waveforms in bit-line method of one SRAM cell (in black) which passes and the other one (in red) which fails. Take the stable SRAM cell as an example, its write noise margin – BLM – is defined by grey double arrow. Voltage is normalized to  $V_{DD}$ . Substrate bias:  $V_{bsn} = -1 V$ ,  $V_{bsp} = 1 V$ .

Fig. 2.5. Schematic of 6-T SRAM cell with swept terminals indicated by red arrows. (b) Measured waveforms in word-line method of one SRAM cell (in black) which passes and the other one (in red) which fails. Take the stable SRAM cell as an example, its write noise margin – CWLM – is defined by grey double arrow. Voltage is normalized to  $V_{DD}$ . Substrate bias:  $V_{bsn} = -1 V$ ,  $V_{bsp} = 1 V$ .

#### Write Butterfly Curve (WSNM)

In write butterfly curve [37], voltage of one node is swept and that of the other one is monitored. Fig. 2.1(a) shows the schematic of 6-T SRAM cell with two internal nodes indicated. Write butterfly curve consists of the voltage transfer curves (VTCs) of two

consisting cross-coupled inverters. Take one SRAM cell [plotted in black in Fig. 2.1(b)] as an example. One branch (black solid line) is the same as that in read butterfly curve and can be named "read VTC". However, write butterfly curve is characteristic of the other one (black dashed line), due to the different bias condition that  $V_{BLR}$  is biased at zero instead of  $V_{DD}$  in read operation. And this branch can be named "write VTC". Also, different from read butterfly curve where the existence of three intersection points is representative of stable read operation, two branches of write butterfly curve only intersect at one logic state (here, it is "0") if the SRAM cell is stable in write operation. When read VTC and write VTC intersect at more than one point, the SRAM cell [plotted in red in Fig. 2.1(b)] fails. And write stability – "0" write static noise margin (WSNM) – can be extracted as the side of smallest square nested inside write butterfly curves, as indicated for the stable cell in Fig. 2.1(b).

#### N-curve $(I_W)$

Read N-curve, in which  $V_{BLR}$  is biased at  $V_{DD}$ , is usually used for characterization of read stability in the SRAM cell. Fig. 2.2(a) indicates the node in which voltage is swept as well current is monitored. Besides, Ref. 37 has extended its use as an alternative for write ability and write-trip current (WTI) is defined as the negative value of minimum current of write part in read N-curves, as shown in Fig. 2.2(b).

However, due to the bias condition in read N-curve where  $V_{BLR} = V_{DD}$ , the meta-stable point in read N-curve cannot be the write-trip point – where voltage of internal node flips – in real write operation. Instead,  $V_{BLR}$  is proposed to be biased at zero for write N-curve [38], as shown in Fig. 2.3(a). Write N-curve is well correlated with read VTC in write butterfly curve, since in both methods voltage of VR is swept from zero to  $V_{DD}$  during measurement. But current information is the unique feature in write N-curve. Fig. 2.3(b) gives the write Ncurves of two SRAM cells. The black one passes, whereas the red one fails since it has the part below  $I_{VR} = 0$ . Besides, these two represent two typical types of write N-curves which will be discussed in detail in section 2.2.3. Write stability in write N-curve – "0"  $I_W$  – can be defined as the local minimum current for the stable cell as indicated in Fig. 2.3(b).

#### **Bit-line Method (BLM)**

Different from write butterfly curve and write N-curve, two more write stability methods – bit-line method [41] and word-line method [42] – have been proposed. In these two methods, since no voltage is forced in internal nodes, the positive feedback loop is not disrupted and facilitates the change of internal nodes' states. Thus, they can both monitor write-trip point in SRAM cells. In bit-line method, voltage of node (here, it is VL) is monitored while V<sub>BLR</sub> is discharged from V<sub>DD</sub> to zero, as shown in Fig. 2.4(a). The measured waveform of one SRAM cell (plotted in black) is shown in Fig. 2.4(b), where voltage of VL is zero in the beginning and flips up to V<sub>DD</sub> around V<sub>BLR</sub> =  $0.25 \times V_{DD}$ . If VL never flips until V<sub>BLR</sub> is fully discharged, the SRAM cell [plotted in red in Fig. 2.4(b)] fails. Write stability in bit-line method – "0" bit line margin (BLM) – is defined as V<sub>BLR</sub> where voltage of VL flips for the stable cell indicated in Fig. 2.4(b).

#### Word-line Method (CWLM)

In word-line method, voltage of node (here, it is VR) is monitored while  $V_{WL}$  is swept from zero to  $V_{DD}$ , as shown in Fig. 2.5(a). Similar to bit-line method, if state flip occurs, the SRAM cell [plotted in black in Fig. 2.5(b)] passes. If not, failure occurs [plotted in red in Fig. 2.5(b)]. And write stability in word-line method – "0" combined word line margin (CWLM) – is defined as voltage difference between  $V_{DD}$  and  $V_{WL}$  where voltage of VR flips for the stable cell indicated in Fig. 2.5(b).

#### **Performance Factor for Write Operation**

The SRAM cell which has larger write stability corresponds to a more writeable cell.

During the real write process, one bit line ( $V_{BLL}$ ) is charged to  $V_{DD}$  while the other one ( $V_{BLR}$ ) is driven to ground potential by a write driver, followed by a generated voltage pulse to wordline. Meanwhile, voltage of node VR is also driven down through TaR. If the voltage of VR is driven down below the trip point of inverter TpL – TnL, a successful write operation takes place. Thus, the write operation can be facilitated by increasing the strength of access transistor relative to load transistor – that is the SRAM  $\alpha$  ratio. This can be achieved by selection of V<sub>th</sub> or adjusting size ratio (gate width/gate length) of SRAM write performance factor (TaR and TpR).

Above all, four of the mentioned write stability metrics, including WSNM of write butterfly curve,  $I_W$  of write N-curve, BLM of bit-line method and CWLM of word-line method are to be compared in the following part. The primary standard is that write noise margin follows a normal distribution. That means write yield can be easily predicted according to a small number of measured samples, which helps save test duration if more than 6 standard deviations of margin is required.

#### 2.1.2 Contemporary Works

#### **Simulation Work**

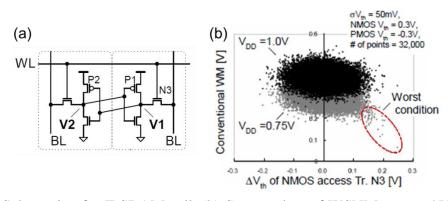

Makino et al [41] compared three write stability metrics – WSNM, BLM and CWLM – and investigated the dependence of each metric on cell transistors'  $V_{th}$  in 45 nm bulk SRAM using SPICE simulation. The basic assumption is that  $V_{th}$  of each cell transistors is independent from each other and the variability of write noise margin is correlated with the variability of cell transistors'  $V_{th}$ . Since the variability is dominant by random fluctuation, if the differential coefficients between write noise margin and  $V_{th}$  are constant, write noise margin is linear for  $V_{th}$  over a wide range of variability, thus obeying a normal distribution.

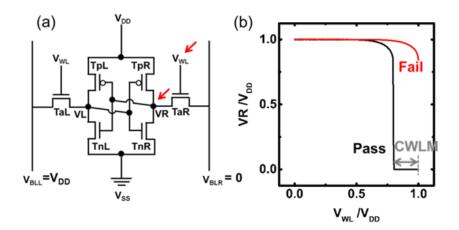

Fig. 2.6. (a) Schematic of 6-T SRAM cell with "0" originally stored. Dependence of (a) WSNM, (b) BLM, and (c) CWLM on  $\Delta V_{th}$  of all six cell transistors. (d) Dependence of WSNM/ BLM/ CWLM on  $\Delta V_{th}$  of N3. (e) Distribution of WSNM/ BLM/ CWLM. All simulations are performed at  $V_{DD} = 1.0$  V. From Ref. [41].

Fig. 2.6(a) shows the schematic of SRAM cell, in which logic "1" write operation is focused. Simulation results at  $V_{DD} = 1$  V are given in Fig. 2.6(b)-(d) for write butterfly curve, bit-line method and word-line method, respectively. As is discussed in section 2.1.1, the access transistor (N3) and load transistor (P1) are the dominant cell transistors in write operation. Since the correlation coefficient (CC) between write noise margin and  $\Delta V_{th}$  of P1 is constant in all figures, Fig. 2.6(d) highlights the dependence of each metric on  $\Delta V_{th}$  of N3. In terms of write butterfly curve, the slope is almost zero below  $\Delta V_{th} = 0.1$  V, which means WSNM is not sensitive to  $V_{th}$  change in access transistor and cannot reflect the real write noise margin in SRAM. Besides, the slope abruptly changes around  $\Delta V_{th} = 0.1$  V and results in non-normal distribution of WSNM all over the  $\Delta V_{th}$  range. On the contrary, BLM/CWLM has linear relationship with  $V_{th}$  change in N3 and P1, except the deviation of CC between BLM and  $V_{th}$  in N3 below  $\Delta V_{th} = 0.2$  V.

For further confirmation, Monte Carlo simulation is performed to calculate the distributions of three write stability metrics at  $V_{DD} = 1$  V, as shown in Fig. 2.6(e). As is predicted, WSNM deviates from a normal distribution indicating write butterfly curve not as a good candidate and CWLM from word-line method has good normality. In terms of bit-line method, BLM also follows a normal distribution though the CC between BLM and  $\Delta V_{th}$  of N3 does not keep constant all over  $V_{th}$  range. Thus, it is concluded that bit-line method and word-line method are good candidates for write yield estimation at  $V_{DD} = 1$  V through simulation.

#### **Experimental Work**

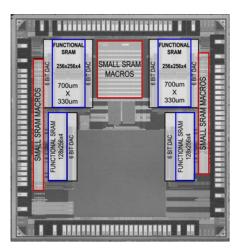

Guo et al. [38] presented a comprehensive stability characterization work based on 45 nm bulk SRAM. Fig. 2.7 shows the test chip consisting of large functional SRAM arrays (by square in blue) and small SRAM macros (by square in red). In SRAM macros, all internal nodes including CL and CH in Fig. 2.8(a) can be accessed. And Fig. 2.8(a) and Fig. 2.8(b) show the measured waveforms of write butterfly curve and write N-curve at  $V_{DD} = 0.7$  V in SRAM macros. With regard to bit-line method and word-line method, the measurement methods are different from described in section 2.1.1 in that bit-line current instead of node voltage is monitored to anchor the state flip. Figs. 2.8(c)-(d) show measured waveforms of bit-line method at  $V_{DD} = 0.7$  V in functional SRAM arrays.

Fig. 2.7. Die photo of the 45 nm bulk SRAM test chip [38].

Fig. 2.8. (a) Schematic of 6-T SRAM cell. Measured (a) write butterfly curves, (c) write N-curves of SRAM macro and (d) waveforms in bit-line method, (e) waveforms in word-line method of functional SRAM arrays. Voltage is normalized to  $V_{DD}$ . From Ref. [38].

Fig. 2.9. Cumulative pots of (a)  $I_W$  of SRAM macro and (b) BWTV, (c) WWTV of functional SRAM arrays at  $V_{DD} = 0.7$  V. From Ref. [38].

Based on measured data, the distributions of these metrics are plotted in Fig. 2.9 (no data of write butterfly curve is shown here). Due to small number of SRAM cells in SRAM macros, the data of write N-curve is limited to around  $\pm 3$  sigma. But no big deviation from a normal distribution is demonstrated in Fig. 2.9(a). 64 kb SRAM cells are accessed for bit-line method and word-line method and support the data analysis up to  $\pm 4$  sigma. These two metrics show good normality, thus confirming them as good candidates for write yield at V<sub>DD</sub> = 0.7 V, similar to simulation results in Ref. [41].

But for statistical analysis, there are two main limitations in this experimental work. One is the limited number of SRAM cells in SRAM macros and the other is the unconvincing comparison of different metrics between SRAM macros and functional SRAM arrays. In addition, both simulation and experimental work up to now focused on SRAM stability characterization at high  $V_{DD}$  and low- $V_{DD}$  characterization [42] is called for by designers for robust low-power SRAM design.

Fig. 2.11. Cumulative plots of V<sub>th</sub> of (a) TaL/ TaR, (b) TnL/ TnR, and (c) TpL/ TpR of 4 kb SOTB SRAM cells. Drain bias:  $|V_{ds}| = 50$  mV. Substrate bias:  $V_{bsn} = -1$  V, and  $V_{bsp} = 1$ V.

# 2.2 Measurement Results in SOTB SRAM

## 2.2.1 Test Structure

A SRAM die is implemented in a 65 nm SOTB CMOS process and includes 16 kb (128 word-line × 128 bit-line) SRAM cells for large-scale read/write stability. Fig. 2.10 shows the schematic of specially developed device-matrix-array (DMA) TEG [43-45], in which two internal nodes and each pin including voltage supply, two bit lines, word lines as well as body substrate for NMOS/PMOS can be accessed. In that way, I-V measurements of individual cell transistors can be performed in order to establish a direct correlation between SRAM and cell transistors. Also, the peripheral decoder makes it easy to access each SRAM cell in a large capacity of SRAM arrays.

Fig. 2.12. Measured (a) write butterfly curves, (b) write N-curves, (c) waveforms in bit-line method, and (d) waveforms in word-line method of 4 kb SOTB SRAM cells at  $V_{DD} = 0.8$  V. Substrate bias:  $V_{bsn} = -1$  V, and  $V_{bsp} = 1$ V.

# 2.2.2 Write Stability Characterization using Four Metrics

Fig. 2.11 shows V<sub>th</sub> distribution of cell transistors in 4 kb SOTB SRAM cells. Though unaffected by RDF, the remained variability can be mainly ascribed to gate work function variation (WFV) [19]. Write stability characterization is performed at  $V_{DD} = 0.8$  V, 0.6 V, and 0.4 V. Take  $V_{DD} = 0.8$  V as an example, Fig. 2.12 shows measured waveforms of (a) write butterfly curve, (b) write N-curve, (c) bit-line method, and (d) word-line method.

Fig. 2.13. Cumulative plots of (a) WSNM, (b)  $I_W$ , (c) BLM, and (d) CWLM of 4 kb SOTB SRAM cells at  $V_{DD} = 0.8$  V (in black), 0.6 V (in blue), and 0.4 V (in red). WSNM,  $I_W$ , BLM, CWLM are defined as the minimum of "0" and "1" write.  $I_W$  at  $V_{DD} = 0.6$  V and 0.4 V have been magnified by 2 and 10 times, respectively. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

Fig. 2.13 shows the cumulative plots of extracted (a) WSNM, (b)  $I_W$ , (c) BLM, and (d) CWLM. They have good normality at high  $V_{DD} = 0.8$  V (in black) up to ±4 sigma. BLM and CWLM keep normal distributions at low  $V_{DD} = 0.6$  V (in blue) and 0.4 V (in red). Thus, BLM and CWLM can be used to extrapolate the present distribution to give write yield in large capacity of SRAM cells, even at low  $V_{DD}$ . On the contrary, when  $V_{DD}$  goes down to 0.4 V, WSNM shows a "two-mode" distribution with the transition region at the center of the distribution and the lower tail of  $I_W$ 's distribution shows slight deviation from a normal distribution. The non-normality of WSNM and  $I_W$  at low  $V_{DD}$  will be discussed later. It also indicates that these two metrics are not good candidates for yield estimation at low  $V_{DD}$ .

Fig. 2.14. Scatter plots of (a) BLM versus CWLM, (b)  $I_W$  versus BLM, (c)  $I_W$  versus CWLM, (d) WSNM versus BLM, (e) WSNM versus CWLM, and (f) WSNM versus  $I_W$  in 4 kb SOTB SRAM cells at  $V_{DD} = 0.8$  V. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

Fig. 2.15. Scatter plots of (a) BLM versus CWLM, (b)  $I_W$  versus BLM, (c)  $I_W$  versus CWLM, (d) WSNM versus BLM, (e) WSNM versus CWLM, and (f) WSNM versus  $I_W$  in 4 kb SOTB SRAM cells at  $V_{DD} = 0.4$  V. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

Fig. 2.14 shows the scatter plots of each two write stability at high  $V_{DD} = 0.8$  V. Both xaxis and y-axis have been normalized to its standard deviation relative to average value. And the CC is calculated in the upper left corner of each plot. The best correlation is found in scatter plot of BLM versus CWLM. This is due to the fact that, in both bit-line method and word-line method, BLM and CWLM are extracted on the basis of write-trip point of the SRAM cell. Setting BLM and CWLM as the standard, I<sub>W</sub> shows much better correlation than WSNM. And the worst correlation is found between WSNM and I<sub>W</sub>. Fig. 2.15 shows the scatter plots at low V<sub>DD</sub> = 0.4 V. Generally, better correlation is demonstrated in each metric pairs than at V<sub>DD</sub> = 0.8 V. The CC of BLM versus CWLM is almost near to 1. In terms of WSNM and I<sub>W</sub>, the dispersion also becomes much smaller at low V<sub>DD</sub> but still cannot be neglected. These four write stability metrics indicate the same failure point, suggesting that all metrics can be used for write failure detection in SRAM cells.

## 2.2.3 Further Discussions about Unpreferred Metrics

Three unpreferred metrics are to be discussed, including WTI, WSNM and  $I_W$ . And the origin of non-normality of write butterfly curve and write N-curve at low  $V_{DD}$  (Fig. 2.13(a) and Fig. 2.13(b)) is also clarified.

#### Read N-curve (WTI)

Correlation between WTI from read N-curve and  $I_W$  from write N-curve is analyzed in 4 kb SOTB SRAM cell at  $V_{DD} = 0.8$  V [Fig. 2.16(a)] and  $V_{DD} = 0.4$  V [Fig. 2.16(b)]. Here, write noise margin is defined as the minimum between logic "0" and "1" write. Large dispersion is found at  $V_{DD} = 0.8$  V and the bad correlation is ascribed to different bias conditions in terms of bit lines in SRAM cells. Moreover, the cells demonstrated write failure by write N-curve in Fig. 2.16(b) show positive WTI, indicating that read N-curve cannot be used for write failure detection. Thus, WTI from read N-curve is not a correct metric.

Fig. 2.16. Scatter plot of WTI from read N-curve versus  $I_W$  from write N-curve of 4 kb SOTB SRAM cells at (a)  $V_{DD} = 0.8$  V and (b)  $V_{DD} = 0.4$  V. Red dashed line indicates where  $I_W$  equals zero. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

#### Write Butterfly Curve (WSNM)

Fig. 2.17 (a) shows the histogram plot of "0" WSNM of 4 kb SOTB SRAM cells at  $V_{DD} = 0.4$  V, with two peaks clearly distinguished. The peak at higher value is defined as Mode I and the other one at lower value is defined as Mode II. Fig. 2.17(b) shows write butterfly curves of these SRAM cells, which can be classified into two types.

To clarify the difference of the two types, Fig. 2.18(a) and Fig. 2.18(b) give write butterfly curves of Cell-A and Cell-B at  $V_{DD} = 0.4$  V. These two cells are characteristic of Mode-I and Mode-II write butterfly curve, respectively. Compared to Cell-A, Cell-B shows a smaller eye enclosed by write butterfly curve and a smaller value of "0" WSNM is extracted in Mode II. Besides, the value of VR on write VTC when VL equals zero approaches  $V_{DD}$ , resulting in the appearance of tail in the write VTC of Cell-B. That is the main difference from write butterfly curve of Cell-A.

Fig. 2.17. (a) Histogram plot of "0" WSNM of 4 kb SOTB SRAM cells at  $V_{DD} = 0.4V$ . Two peaks are indicated by Mode I and Mode II, respectively. (b) Write butterfly curves of 4 kb SOTB SRAM cells in "0" write at  $V_{DD} = 0.4$  V. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

Fig. 2.18. Two types of write butterfly curves: Write butterfly curves of (a) Cell-A and (b) Cell-B in "0" write at  $V_{DD} = 0.4$  V. Cell-A/ Cell-B corresponds to Mode I/ II. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.  $|I_{ds}|$ - $|V_{gs}|$  curves of TaR and TpR in (c) Cell-A and (d) Cell-B at drain bias of 50 mV. Inset: The threshold voltage ( $V_{thc}$ ) of TaR and TpR are listed.

Fig. 2.19. (a)  $|I_{ds}|-|V_{gs}|$  curves of TaR (grey dashed line) and TpR in Cell-C at  $V_{bsp} = 0$  V (black), 0.5 V (orange), 1.0 V (red), 1.5 V (green), 2.0 V (blue), and 2.5 V (purple). (b) Write butterfly curves of Cell-C in "0" write at  $V_{DD} = 0.4$  V. Substrate bias:  $V_{bsn} = -1$  V;  $V_{bsp} = 0$  V (in black), 0.5 V (orange), 1.0 V (red), 1.5 V (green), 2.0 V (blue), and 2.5 V (purple).

Since the value of VR when VL equals zero is determined by resistive voltage divider consisting of TaR and TpR,  $|I_{ds}|$ - $|V_{gs}|$  curves of TaR and TpR in Cell-A and Cell-B are plotted in Fig. 2.18(c) and Fig. 2.18(d), respectively. The near-V<sub>th</sub> or sub-V<sub>th</sub> region is focused on. Different from super-V<sub>th</sub> region, V<sub>th</sub> is dominant over other parameters in transistors' conductance. Here, V<sub>th</sub> is defined as threshold voltage extracted at constant sub-threshold current of W/L × 100 nA (W is gate width and L is gate length). Compared to Cell-A, TpR has a lower V<sub>th</sub> and becomes stronger than TaR in Cell-B in near-V<sub>th</sub> or sub-V<sub>th</sub> region. That is the reason why the tail appears in Cell-B at V<sub>DD</sub> = 0.4 V, which is the characteristic of Mode-II write butterfly curve.

More clear evidence is shown in another Cell-C. By applying substrate bias  $(V_{bsp})$  for TpR, its  $V_{th}$  can be adjusted in a wide range, due to advantageous design to isolate source/drain from substrate in SOTB transistors [45]. Fig. 2.19(a) shows  $|I_{ds}|$ - $|V_{gs}|$  curves of TpR in Cell-C at different  $V_{bsp}$ . And the  $I_{ds}$ - $V_{gs}$  curve of TaR is plotted in grey dashed line for reference. Originally, Cell-C has a balanced pair of TpR and TaR when  $V_{bsp} = 1$  V. So TpR becomes stronger than TaR when  $V_{bsp}$  is decreased to 0 V, whereas becomes weaker when  $V_{bsp}$  is

Fig. 2.20. (a) Cumulative plots of TpR's V<sub>thc</sub> in 1 kb SOTB SRAM cells at V<sub>bsp</sub> = 0 V (black), 0.5 V (orange), 1.0 V (red), 1.5 V (green), 2.0 V (blue), and 2.5 V (purple). Drain bias: -50 mV. (b) Scatter plot of TpR's V<sub>thc</sub> versus TaR's V<sub>thc</sub>. Drain bias:  $|V_{ds}| = 50$  mV. Substrate bias: V<sub>bsn</sub> = -1 V; V<sub>bsp</sub> = 0 V (black), 1.0 V (red), and 2.5 V (purple).

increased to 2.5 V. Fig. 2.19(b) shows the write butterfly curves of Cell-C at  $V_{DD} = 0.4$  V when different  $V_{bsp}$  is applied. A clear transition from Mode-I to Mode-II write butterfly curve is demonstrated when TpR becomes much stronger than TaR.

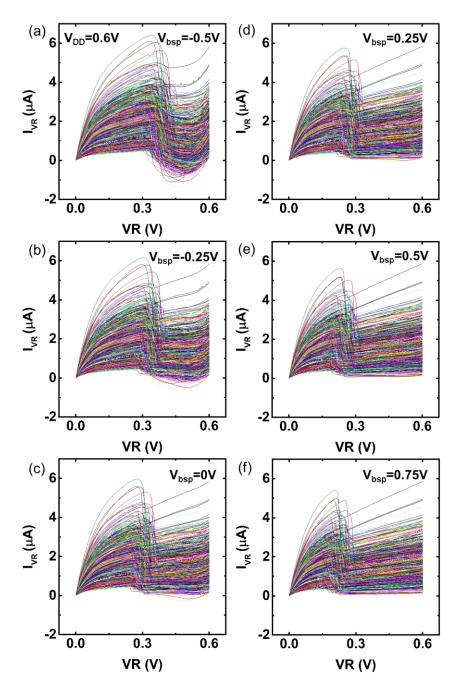

Statistically, Fig. 2.20(a) shows cumulative plots of TpR's V<sub>th</sub> in 1 kb SOTB SRAM cells at different V<sub>bsp</sub>. Also, the scatter plots of TpR's V<sub>th</sub> versus TaR's V<sub>th</sub> at V<sub>bsp</sub> = 0 V, 1.0 V and 2.5 V are plotted in Fig. 2.20(b). Fig. 2.21 and Fig. 2.22 show write butterfly curves of 1 kb SOTB SRAM cells and histogram plots of "0" WSNM, respectively, at V<sub>DD</sub> = 0.4 V when different V<sub>bsp</sub> is applied. According to Fig. 2.20(b), TpR's V<sub>th</sub> centers on the same value as TaR's V<sub>th</sub> at V<sub>bsp</sub> = 1.0 V. When V<sub>bsp</sub> = 0 V is applied, TpRs in all cells become stronger than TaRs, generating Mode-II write butterfly curves in Fig. 2.21(a). Whereas, TpRs in all cells become much weaker at V<sub>bsp</sub> = 2.5 V. Thus, the curves in Fig. 2.21(f) are classified to Mode-I write butterfly curves. That is the reason why "0" WSNM in Fig. 2.22(a) and Fig. 2.22(f) both show normal distributions with single peak. Between these two particular cases, TpRs of some cells are stronger than TaR and vice versa. As a result, both Mode-I and Mode-II write butterfly curves coexist in Fig. 2.21(c) and "two-mode" distribution of "0" WSNM is found in Fig. 2.22(c). That is the origin of WSNM's non-normality at low V<sub>DD</sub>.

Fig. 2.21. Write butterfly curves of 1 kb SOTB SRAM cells in "0" write at  $V_{DD} = 0.4$  V. Substrate bias:  $V_{bsn} = -1$  V, (a)  $V_{bsp} = 0$  V, (b)  $V_{bsp} = 0.5$  V, (c)  $V_{bsp} = 1.0$  V, (d)  $V_{bsp} = 1.5$  V, (e)  $V_{bsp} = 2.0$  V, (f)  $V_{bsp} = 2.5$  V.

Fig. 2.22. Histogram plots of 1 kb SOTB SRAM cells in "0" write at  $V_{DD} = 0.4$  V. Substrate bias:  $V_{bsn} = -1$  V, (a)  $V_{bsp} = 0$  V, (b)  $V_{bsp} = 0.5$  V, (c)  $V_{bsp} = 1.0$  V, (d)  $V_{bsp} = 1.5$  V, (e)  $V_{bsp} = 2.0$  V, (f)  $V_{bsp} = 2.5$  V.

Fig. 2.23. (a) Write N-curves of 4 kb SOTB SRAM cells in "0" write at  $V_{DD} = 0.4$  V. (b) Histogram plot of "0"  $I_W$  of 4 kb SOTB SRAM cells at  $V_{DD} = 0.4$  V. The black curve indicates fitting result of normal distribution function. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

Fig. 2.24. Two types of write N-curves of Cell-A and Cell-B (same as in Fig. 2.20) in "0" write at  $V_{DD} = 0.4$  V. Cell-A/ Cell-B corresponds to Mode i/ Mode ii. The position where "0"  $I_W$  is extracted is indicated by red arrow. Substrate bias:  $V_{bsn} = -1$  V,  $V_{bsp} = 1$  V.

#### Write N-curve (I<sub>W</sub>)

Fig. 2.23(a) shows the histogram plot of "0"  $I_W$  of 4 kb SOTB SRAM cells at  $V_{DD} = 0.4 V$ , which obviously deviates from a normal distribution (black curve). Fig. 2.23(b) shows write N-curves of these SRAM cells. Similar to write butterfly curves, write N-curves can also be classified into two types. Mode-i write N-curve of Cell-A and Mode-ii write N-curve of Cell-B in "0" write at  $V_{DD} = 0.4 V$  are plotted in Fig. 2.24(a) and Fig. 2.24(b), respectively.

Fig. 2.25. Measured currents in TaR (in blue), TnR (in green) and TpR (in red) contributing to write N-curve (in black) of Cell-C in "0" write at  $V_{DD} = 0.4$  V. Substrate bias:  $V_{bsn} = -1$  V, (a)  $V_{bsp} = 0$  V, (b)  $V_{bsp} = 0.5$  V, (c)  $V_{bsp} = 1.0$  V, (d)  $V_{bsp} = 1.5$  V, (e)  $V_{bsp} = 2.0$  V, (f)  $V_{bsp} = 2.5$  V. Here, the positive direction of current is defined as flowing outside node VR.

Compared to Cell-B, the position of local minimum current changes in Cell-A. The value of VR where "0"  $I_W$  is extracted is smaller in Mode-i write N-curve. Here, considering the bad correlation between WSNM and  $I_W$  in Fig. 2.15(f), two modes in write N-curves are named Mode-i and Mode-ii, different from in write butterfly curves. Also, the different mechanism is discussed as follows.

Fig. 2.25 shows write N-curves of Cell-C and currents in cell transistors (TaR, TnR and TpR) at  $V_{DD} = 0.4$  V when different  $V_{bsp}$  is applied. A clear transition is shown from Mode-ii write N-curve to Mode-i write N-curve when  $V_{bsp}$  increases from 0 V to 2.5 V. According to Kirchhoff's current law, the current flowing into node VR is the sum of all currents in TaR, TnR and TpR. Current in TaR (in blue) is the drain current with gate biased at  $V_{DD}$ . Currents in TnR (in green) and TpR (in red) are both zero at intersection point indicated by red arrow, which corresponds to voltage trip point of left half cell. In Fig. 2.25(a), since TpR is strong with a large current (negative) beyond the voltage trip point, the local minimum current of write N-curve is determined by maximum current in TpR. With the increase of  $V_{bsp}$ , TpR becomes much weaker and finally operates in sub-V<sub>th</sub> region in Fig. 2.25(f). In this case, since current in TaR reaches saturation after voltage trip point, the local minimum current in write N-curve is extracted near voltage trip point. Different from in write butterfly curve, Mode-i and Mode-ii write N-curve are distinguished mainly according to the strength of TpR itself. When TpR goes into sub-V<sub>th</sub> region, Mode-ii N-curve transitions to Mode-i N-curve.

Statistically, Fig. 2.26 and Fig. 2.27 show write N-curves of 1 kb SOTB SRAM cells and histogram plots of 0 "I<sub>W</sub>", respectively, at  $V_{DD} = 0.4$  V when different  $V_{bsp}$  is applied. According to Fig. 2.20(a), when  $V_{bsp} = 0$  V is applied, TpRs in all cells operate in super-V<sub>th</sub> region, generating Mode-ii write N-curves in Fig. 2.26(a). That is the reason why "0" I<sub>W</sub> in Fig. 2.27(a) follows a normal distribution. Whereas, TpRs in all cells goes into sub-V<sub>th</sub> region at  $V_{bsp} = 2.5$  V. Thus, the curves in Fig. 2.26(f) are classified to Mode-i write N-curves. Different from "0" WSNM in Fig. 2.22(f), Fig. 2.27(f) shows a right-skewed distribution, rather than a symmetrical one, of "0" I<sub>W</sub> in Mode i. Also, the value of "0" I<sub>W</sub> in Mode i cannot be clearly distinguished from that in Mode ii. Under substrate bias of 1.0 V, Mode-ii and Mode-i write N-curves co-exist in Fig. 2.26(c). As a result, two modes entangle with each other and it induces the non-normal distribution of "0" I<sub>W</sub> at low V<sub>DD</sub> shown in Fig. 2.27(c).