Master's Degree Dissertation

# Design, Fabrication and Measurement of Electrically-Pumped Wavelength-Scale Metal-Clad Semiconductor Laser with Potential for Waveguide Coupling

(導波路結合を可能にする電流励起波長スケール 金属クラッド半導体レーザの設計、作製と評価)

### 37-155014 Kaiyin Feng

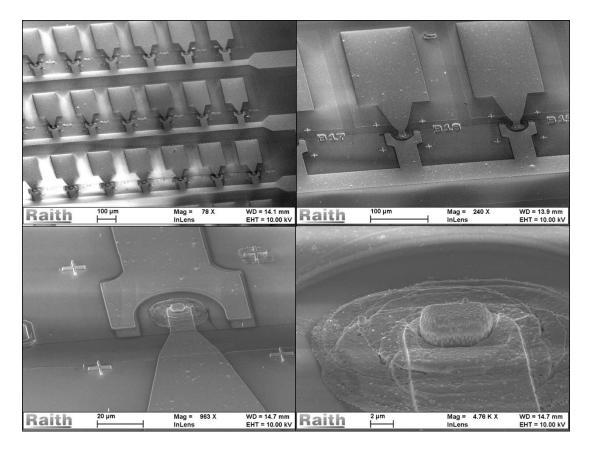

Supervisor: Prof. Yoshiaki Nakano

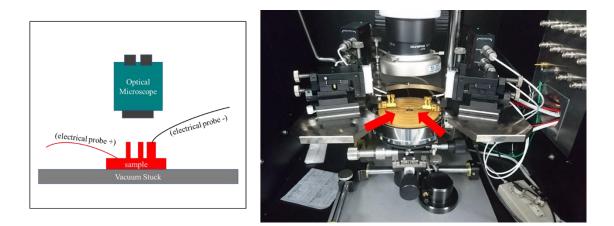

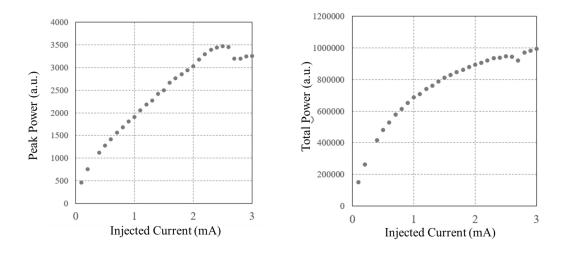

Dept. of Electrical Engineering and Information Systems University of Tokyo, Tokyo, Japan, Aug. 2017

### Abstract

Wavelength-scale metal-clad semiconductor lasers have been of considerable interest as potentially ideal light sources for on-chip optical interconnects and photonic integrated circuits. Eligible device should provide continuous-wave electrically-pumped lasing under room-temperature with integration to waveguides, which gives advancement in terms of energy efficiency, modulation response, as well as high integration density from modern fabrication techniques.

This thesis aims at contributing to research on electrically-pumped wavelength-scale metalclad semiconductor lasers with potential for waveguide-coupling, from both device design and fabrication perspectives. We present design of novel waveguide-coupling schemes with comprehensive numerical computation including both electromagnetic analysis and thermodynamic analysis, and an extensive investigation in fabrication techniques for wavelength-scale metal-clad semiconductor lasers to achieve continuous-wave electricallypumped room-temperature lasing.

For device design, we propose a wavelength-scale silver-clad InP/InGaAs cavity coupled to silicon-on-insulator (SOI) waveguide with thin InP lower-cladding layer for improved heat dissipation under typical working conditions. We present design of an integrated feedback stub for external tuning of the Q-factor for such waveguide-coupled lasers without sacrificing its figure-of-merit or heat-management performance, and we demonstrate more than 5-fold Q-factor improvement of the cavity through finite-dimension time-domain (FDTD) simulation results. In addition, we provide theoretical analysis of the Q-factor-tuning mechanism with coupled-mode theory, and the modeling results agree well with those obtained from FDTD simulations.

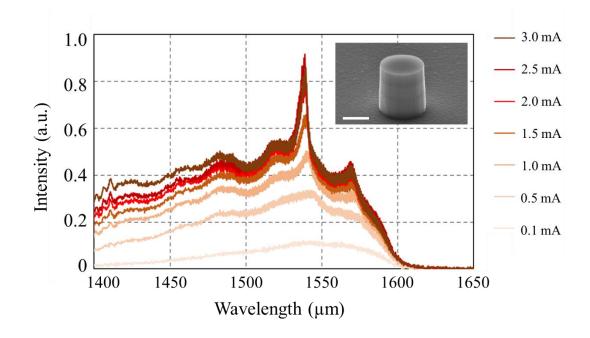

In the case of device fabrication and measurement, we present extensive investigation of the complete fabrication process of silver-clad InP/InGaAs cavities on InP substrate packaged with gold electrodes eligible for electrically-pumped operation. We demonstrate several improvements in the fabrication process including semiconductor side-wall verticality and silver quality, and provide detailed discussions on possible future improvements. We present I-V measurement and electroluminescence measurement results of selected devices after fabrication. In particular, cavity enhancement in room-temperature of a silver-clad InP/InGaAs circular light emitter of volume 0.52  $\lambda^3$  is achieved under continuous wave electrically-pumping.

### **Table of Contents**

| Abstract          | i   |

|-------------------|-----|

|                   |     |

| Table of Contents | iii |

### Chapter 1

| Background: What Leads us to Metal-Clad Semiconductor Lasers |                                                                                 |  |  |

|--------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|

| 1.1                                                          | Introduction1                                                                   |  |  |

| 1.2                                                          | Research Motivation: A Personal Understanding1                                  |  |  |

| 1.3                                                          | Global Energy Consumption and Low-Energy On-Chip Light Source2                  |  |  |

| 1.4                                                          | Wavelength-Scale Semiconductor Lasers                                           |  |  |

| 1.5                                                          | Thesis Outline                                                                  |  |  |

| Chapte                                                       | er 2                                                                            |  |  |

| Desi                                                         | gn of Metal-Clad Semiconductor Lasers: Cavity Structure and Thermal Properties9 |  |  |

| 2.1 | Introduction                                    | 9  |

|-----|-------------------------------------------------|----|

| 2.2 | Cavity Structure                                | 9  |

| 2.3 | Cavity Layer Composition and Thermal Properties | 11 |

| 2.4 | Summary                                         | 15 |

### Chapter 3

| Design of Metal-Clad Semiconductor Lasers: Integration with Waveguides |                                                 |    |

|------------------------------------------------------------------------|-------------------------------------------------|----|

| 3.1                                                                    | Introduction                                    | 16 |

| 3.2                                                                    | Problem with Coupling Cavity to Waveguide       | 17 |

| 3.3                                                                    | Coupling with Straight Integrated Feedback Stub | 18 |

| 3.4 Coupling with Curved Integrated Feedback Stub                       | 20     |

|-------------------------------------------------------------------------|--------|

| 3.5 Understanding the Integrated Feedback Stub with Coupled-Mode The    | eory23 |

| 3.6 Summary                                                             | 27     |

| Chapter 4                                                               |        |

| Fabrication of Metal-Clad Semiconductor Lasers                          |        |

| 4.1 Introduction                                                        |        |

| 4.2 Overall Arrangement of the Fabrication Batch                        |        |

| 4.3 Wafer Preparation and Cleansing                                     | 29     |

| 4.4 Fabrication Technology: Procedures and Discussions                  |        |

| 4.5 Comments on Fabrication Process                                     | 50     |

| Chapter 5                                                               |        |

| Measurement Results and Discussions                                     | 52     |

| 5.1 Introduction                                                        |        |

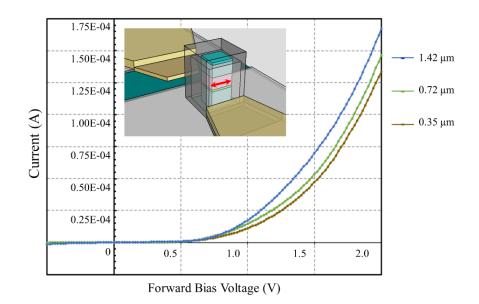

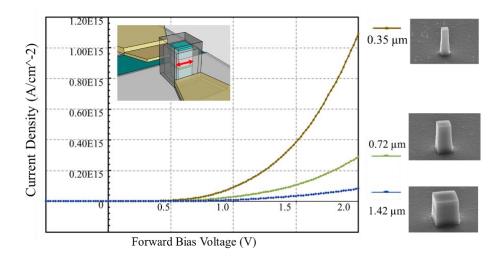

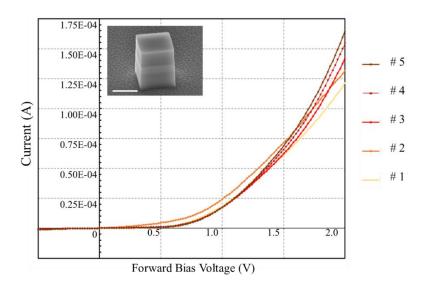

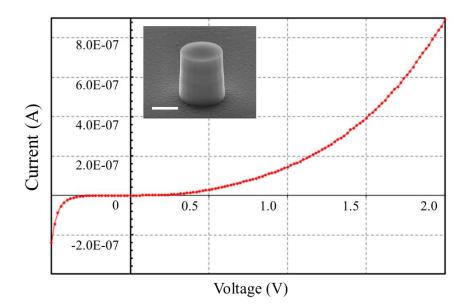

| 5.2 Electrical Properties of the Cavities: I-V Measurement              |        |

| 5.3 Optical Properties of the Cavities: Electroluminescence Measurement | 55     |

| 5.4 Summary                                                             |        |

| Chapter 6                                                               |        |

| Conclusions and Outlook                                                 | 64     |

|                                                                         |        |

| Appendix A. Fabrication Process Flow Chart                              | 68     |

| Appendix B. List of Fabricated Devices                                  | 75     |

| Bibliography                                                            | 76     |

| Acknowledgements                                                        | 80     |

| List of Research Products                                               | 83     |

### **Chapter 1**

# **Background: What Leads us to Metal-Clad Semiconductor Lasers**

#### 1.1 Introduction

This chapter elaborates the motivation of studying design and fabrication of wavelengthscale metal-clad semiconductor lasers with potential of being coupled to waveguide in integrated photonic circuits.

Before we get into the technical problem, in section 1.2, we briefly explain the research motivation from a more philosophical understanding of the problem we face, so as to clarify what benefits this project intends to bring to the world, from a personal perspective of academic research in electrical engineering.

Then, in section 1.3, we would go into the details of the problem, and lead the audience into the role that metal-clad semiconductor laser tries to fit in. After that, in section 1.4, we would provide a brief review of previous research of such metal-clad semiconductor lasers, covering several different works and comparing their results in term of solving the problem discussed in section 1.3.

#### 1.2 Research Motivation: A Personal Understanding

Electrical engineering sets off to tackle problems that could be solved using novel electrical devices. Different from engineering research in the industry, engineering research in academics would target on research projects that may lead to products that come to the market decades ahead of time, and seek for solutions of a problem at higher dimension, or say, would benefit mankind in a longer term. In my opinion, such problems drop into three main categories, to realize novel functionality that is previously unavailable, to develop new technology so as to reduce cost or save energy replacing existing solutions to a given problem, or to demonstrate applications of a new discovery in physics that may potentially raise new problem or develop new technology.

The information and telecommunication industry has been growing rapidly during the past decades and has brought huge change in human's everyday life. It becomes an essential part of almost any urban lifestyle, revolutionizing in every aspect from components of novel electronic devices to computation powers of huge data centers. Human desire

increases inevitably, calling for faster communication and service of larger scale, thus providing a potential market for such solutions. Among them, low-energy on-chip light source for optical interconnects and telecommunication applications is one of a research problem that attracts major attention. This is a problem that drops in the second category, that is, developing new technology so as to reduce cost or save energy replacing existing solutions to a given problem. I am personally interested in problems in this category, because it demonstrates wisdom applied to live life in better quality with lower consumption of nature resources, in the long term. A concept as simple as to "live more with less". This is, in my opinion, the only category that saves mankind from dying of unstoppable desire and losing humanity. Though not usually cared for nowadays, I still feel strongly obligated to clarify this motivation, and therefore this has become a short explanation of why low-energy on-chip light source for optical interconnects and telecommunication applications is worth researching on.

### 1.3 Global Energy Consumption and Low-Energy On-Chip Light Source

In this section, I would like to explain briefly why low-energy on-chip light source for optical interconnects and telecommunication applications falls in the second category, and what problem in energy it is truly served for.

### 1.3.1 Increasing Demand in Energy-Efficient Communication

The data traffic in long distance and short distance are growing rapidly in recent decades, especially after the development of internet. Total internet traffic in 2016 is estimated at ~280 Tb/s, while in 2012 inside a data center the capacity would be estimated for larger than 1Pb/s. As an example, one graphics processor chip has a peak data rate on and off the chip of 1.4 Tb/s, which shows how heavy the interconnect traffic at shorter distances deeper inside information processing machines could be [1, 2].

As to handle such traffic to communicate information, at longer or shorter distance, energy is consumed. In 2012, it was estimated that information processing and computing including data centers, personal computers and networks consume 4.6 % of world electricity production, and the growth rate of consumption exceeds the growth rate in electricity generation capacity. In other words, the energy consumption will be larger than we could afford with current growth rate. Thus, we would need to reduce the total energy consumption.

| Operation                   | Energy per<br>bit   |

|-----------------------------|---------------------|

| Wireless data               | 10 – 30µJ           |

| Internet: access            | 40 - 80 n J         |

| Internet: routing           | 20nJ                |

| Internet: optical WDM links | 3nJ                 |

| Reading DRAM                | 5pJ                 |

| Communicating off chip      | 1 – 20 pJ           |

| Data link multiplexing and  | $\sim 2 \text{ pJ}$ |

| timing circuits             |                     |

| Communicating across chip   | 600 fJ              |

| Floating point operation    | 100fJ               |

| Energy in DRAM cell         | 10fJ                |

| Switching CMOS gate         | ~50aJ - 3fJ         |

|                             |                     |

| 1 electron at 1V, or        | 0.16aJ              |

| 1 photon @1eV               | (160zJ)             |

Table I Energies for communications and computations [1]. WDM- wavelength division

multiplexing, DRAM – dynamic random-access memory, CMOS- complementary metal

oxide-semiconductor transistor. Refer to [1] for detailed notes and references of each data.

To reduce the total energy consumption with a growing data rate, the only solution would be to reduce the energy per bit in communication and processing. That is to say, if we can communicate more efficiently, we can communicate in higher capacity with lower consumption of total energy. Table I shows the approximate energies per bit in various processing and communication operations using electrical circuits [1].

### 1.3.2 Low-Energy On-Chip Light Source

From various previous studies, it is shown that the energy consumption of current electrical interconnects can typically range from picojoules-per-bit to much higher values. The energy efficiency of electrical circuits has a lower limit, since that one has to inevitably charge the line or other electromagnetic medium to the signal voltage.

This is where optics comes to play a competitive role. In optics, one only has to charge or discharge the optoelectronic detector or any equivalent device, and the detection of light is a quantum-mechanical process of absorbing photons, instead of a classical process of measuring the voltage of the light beam. That is to say, the photodetector counts photons, instead of measuring voltage. Also, optics allows higher densities of information to flow (higher bandwidth), which has already been adopted in longer distance communications. With wavelength division multiplexing (WDM) or space division multiplexing (SDM), the information transmission capacity is further expanded.

With such potential in revolutionary reduction in energy consumption, optical interconnect has attracted much attention in research during the past decades. The key challenge of outperforming electrical interconnect would be to realize the lower energy-per-bit as promised. In other words, we should make optoelectronic device that consumes lower energy than the energy required to charge an equivalent length of electrical line.

One of the key component in optical interconnection links is an optical output device that can (1) operate at low energy but deliver the power efficiently, and (2) emit power in a form that can be efficiently delivered to the photodetector at the other end of the link, preferably to emit light into a single spatial mode.

Lasers and light-emitting diodes (LEDs) in wavelength-scale naturally become competitive choices in realizing the required standards for optical output device.

As for lasers, semiconductor lasers today are perfect candidates as they have high gain per unit length. The energy per bit of a laser less than 50 fJ/bit is required for competing with the current electrical interconnects [1]. This could be realized by using advanced structures such as photonic crystal, nano-ring structures and so on [3].

As for LEDs, despite their typical optical inefficiency from emitting into large numbers of spatial modes, it comes into attention in this case due to its advantage in small dimensions. LED with subwavelength volumes can emit into only one spatial mode (or two, including polarization), which is required in low-energy high-efficiency optical communication. Small LEDs also attract much recent attention due to the Purcell enhancement related [4, 5], as in smaller dimension there proves to be enhancement of the spontaneous rate emission into the modes with strong optical concentration. Examples include nanoLEDs with antenna enhancement [6], nanoLEDs coupled to InP waveguides [7] and so on.

### 1.4 Wavelength-Scale Metal-Clad Semiconductor Lasers

In search for an ideal low-energy on-chip light source, we would look into the light emitter in terms of integration density, speed and energy efficiency. Although hybrid III-V/Si lasers using either hybrid growth or wafer bonding techniques have been demonstrated [8], and largely improved confinement in small footprint has been demonstrated using novel designs of ring structures [9] or photonic crystal structures [10, 11], the device footprints are still relatively large and power consumptions are still larger than required.

Another powerful approach, however, has also been under active research during the past decade. That is to use a metal-cladding layer outside the semiconductor laser cavity for improving the device performance for devices of small footprint at wavelength scale. Such wavelength-scale metal-clad semiconductor lasers are promising because of their high integration density, fast modulation, and ease for electrical-pumped operation [12-14].

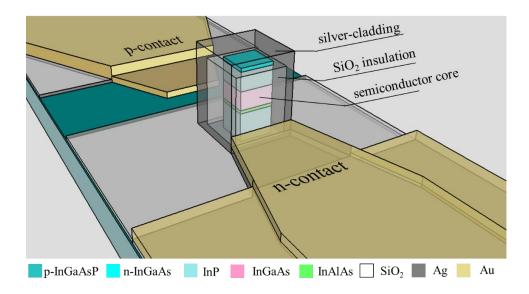

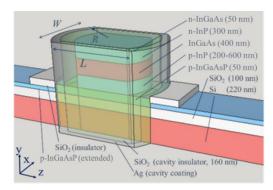

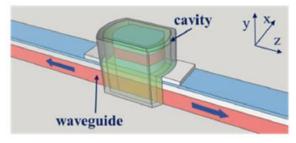

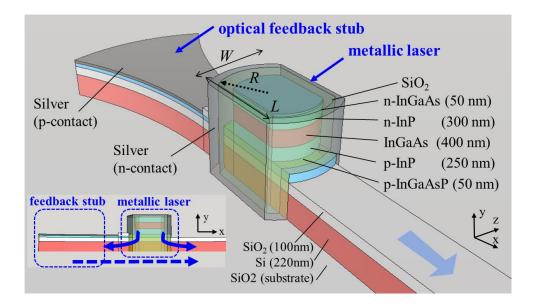

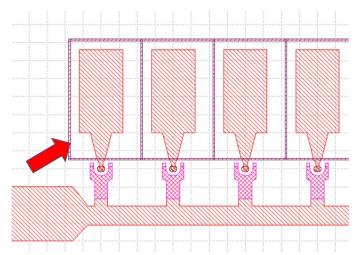

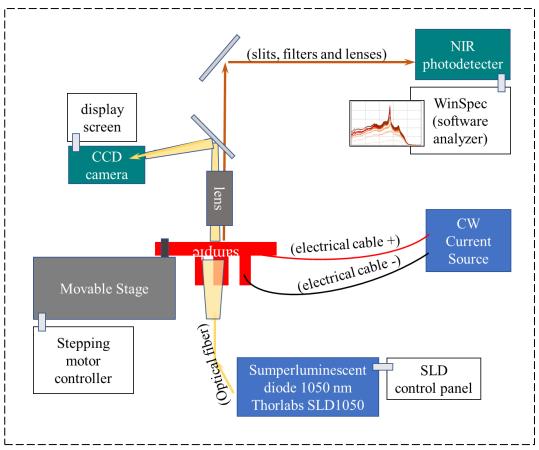

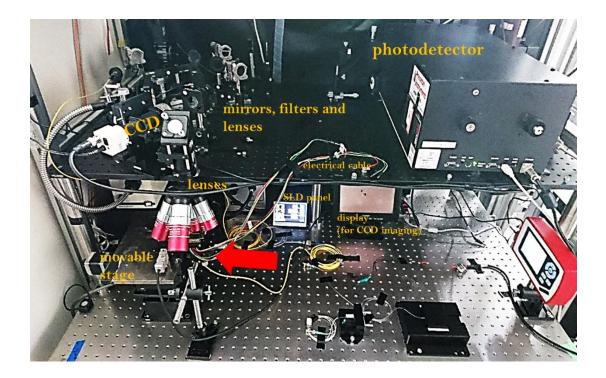

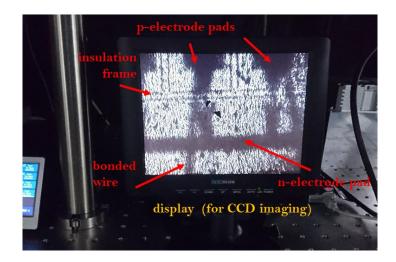

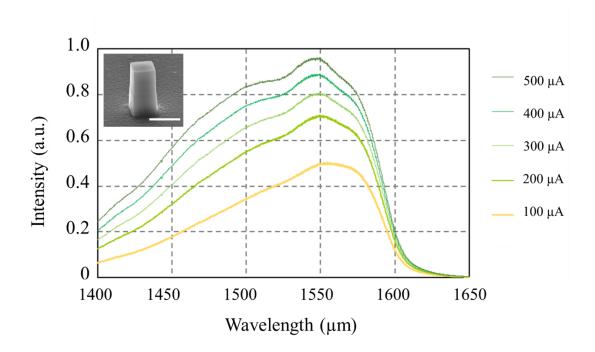

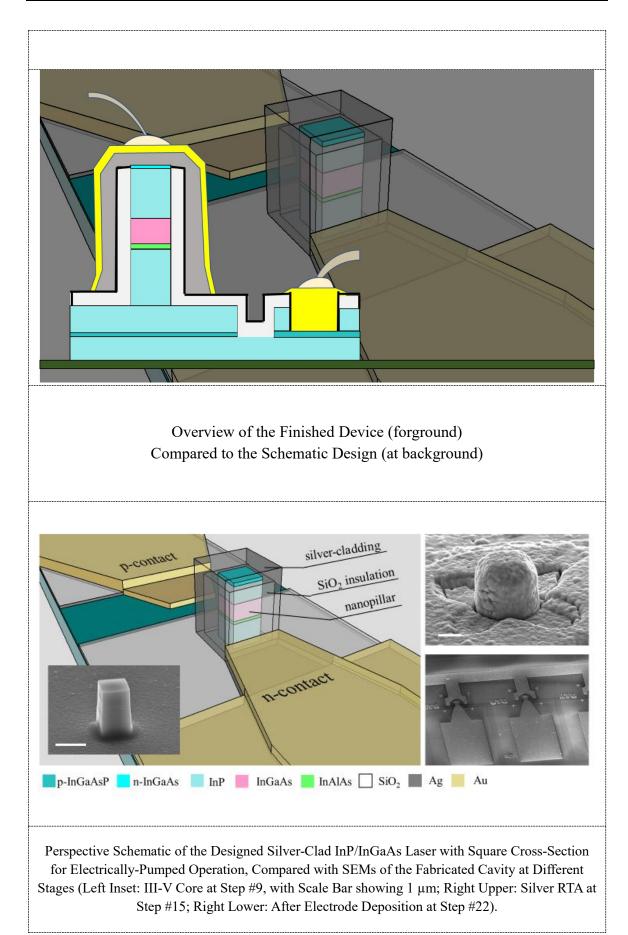

**Figure 1.1** Schematic of a typical wavelength-scale metal-clad semiconductor laser compatible for electrically-pumped operation. In this schematic, the semiconductor core is formed by InP/InGaAs/InP stack, and the insulation layer is formed by SiO<sub>2</sub>, with a metal-cladding coated by silver.

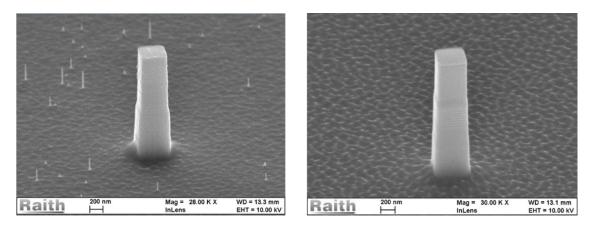

Figure 1.1 shows a schematic of a typical wavelength-scale metal-clad semiconductor lasers compatible for electrically-pumped operation. Various types of metal-clad semiconductor lasers have been demonstrated experimentally by using cylindrical [15-22], narrow waveguide [23], rectangular [24, 25], and capsule-shaped [26, 27] geometries.

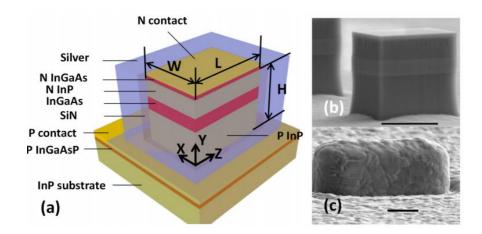

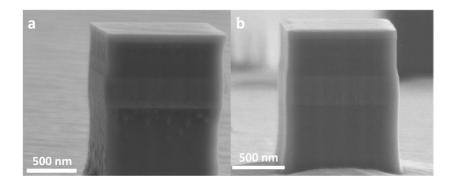

**Figure 1.2** Structures of electrically-pumped wavelength-scale metal-clad semiconductor laser[24]. (a) Layer compositions of the silver-clad InP/InGaAs rectangular semiconductor cavity. (b) Scanning electron microscope (SEM) image of the semiconductor core, (c) SEM image of the cavity after coating with SiN and silver. Scale bars in (b) and (c) are both 1 um.

Electrically-pumped wavelength-scale metal-clad semiconductor laser was firstly demonstrated for room-temperature continuous-wave operation in 2013, reported by K.Ding *et al* [24]. As shown in Fig 1.2, this laser cavity has a cavity volume of  $0.67\lambda^3$  ( $\lambda =$

1591 nm) including the SiN insulation layer. The linewidth is measured as 0.5 nm at RT, giving a Q-value of 3182 and a turn-on threshold around 1.1 mA.

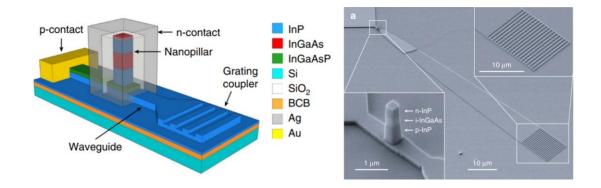

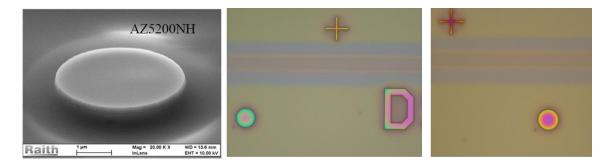

**Figure 1.3** Design of the metal-clad nanopillar LED on silicon substrate coupled to InP-waveguide. The left graph shows schematic representation of the design, while the right shows the SEM image of the fabricated device before metallization with enlarged view of the nanopillar on top of the waveguide and the grating coupler connected downstream [28].

More recently, metal-clad nanopillar LED on a silicon substrate coupled to an InPmembrane waveguide has been demonstrated, showing the potential of metal-clad nanoLEDs for efficient low-power interconnects operating at Gb/s data rates [28]. As shown in Fig 1.3, this device is composed of layers stack from top to bottom as: n-InGaAs(100nm) /n-InP(350nm) /InGaAs(350nm) /p-InP(600nm) /p-InGaAsP(200nm) /InP(250 nm) /SiO<sub>2</sub> /BCB /SiO<sub>2</sub> /Si. It is reported to give nW measured output powers at ~100  $\mu$ A current injection levels, at room temperature.

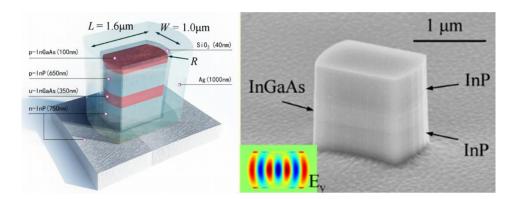

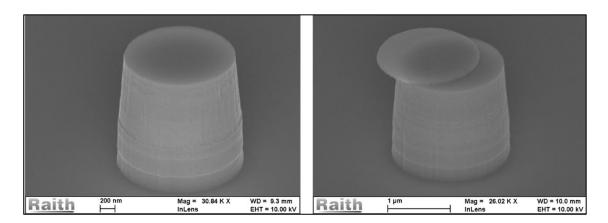

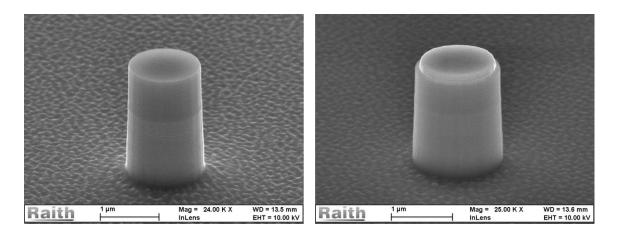

**Figure 1.4** Design of the metal-clad InP/InGaAs semiconductor laser with capsule-shaped cavity. The left graph shows schematic representation of the cavity layer compositions and shaping design, while the right shows the SEM image of the fabricated semiconductor core before metal deposition, with inset showing electric field profile of the TE-like mode as of a top-view cross-section inside the active layer [29].

Apart from common rectangular and square cavities, active research in our group has recently proved some special properties in wavelength-scale metal-clad semiconductor laser with capsule-shaped cavity. As shown in Fig 1.4, this device is composed of a cavity

with capsule-shape introduced to reduce scattering loss and improve TE-mode competence. With pulsed-mode optical pumping at room temperature, this cavity shows spectrum with two peaks at 1535 nm and 1522 nm respectively, and its threshold power of TE-mode lasing is estimated to be 230  $\mu$ W [29].

From previous efforts, research of wavelength-scale metal-clad semiconductor light emitters have made much progress during the past years. In order to achieve its best application so as to tackle the problem described in section 1.3, serious improvement is needed in terms of (1) efficient coupling of the laser with Si-based or InP-based waveguide for integrated fabrication and compatibility with downstream photonic circuits, (2) electrically-pumped operation of the wavelength-scale metal-clad semiconductor laser under room temperature with lower current threshold and higher efficiency.

In this thesis work, research of wavelength-scale metal-clad semiconductor light emitter is presented. We present our endeavor in (1) theoretical and comprehensive simulation work in designing a novel waveguide-coupling scheme with integrated feedback stub for wavelength-scale metal-clad semiconductor laser, and (2) fabrication and measurement of electrically-pumped wavelength-scale silver-clad InP/InGaAs laser under room-temperature. These two aspects serve to investigate possible improvements mentioned in the above paragraph accordingly, aiming for realization of truly energy-efficient on-chip light source coupled to waveguide for optical interconnects.

### 1.5 Thesis Outline

This thesis is organized in six chapters as described below.

**Chapter 1** gives an introduction to the motivation of this research work, from a general perspective of what problem we face, to details of background research in previous works in this field of wavelength-scale metal-clad semiconductor lasers. It also introduces the scope we work on and the potential applications it may bring in to solve the problem.

**Chapter 2** explains the design of metal-clad semiconductor laser cavity in this work. Comprehensive analysis including both electromagnetic and thermodynamic simulation of the cavity structure is presented and discussed, in search for a cavity with improved optical performance as well as thermal management.

**Chapter 3** presents the design of metal-clad semiconductor laser cavity coupled to a silicon-on-insulation (SOI) waveguide. Novel design of a feedback stub on one end of the waveguide is proposed and discussed with finite-dimension time-domain (FDTD) simulation which gives detailed analysis of its optical performance. Theoretical explanation using coupled-mode theory is presented and compared with the simulation results.

**Chapter 4** describes the fabrication of metal-clad semiconductor laser cavity. Detailed procedures are presented step by step for the fabrication of silver-clad InP/InGaAs laser cavity with various dimensions and shapes integrated with electrodes ready for electrically-

pumped operation, with discussions on fabrication quality and possible future improvements.

**Chapter 5** presents the characterization of selected fabricated devices, including the electrical property measurement and optical property measurement. Room-temperature electrically-pumped lasing is observed in selected laser cavities, proving the advancement in device design as well as the improvement in fabrication quality.

**Chapter 6** summarizes the main conclusions of the research presented in this thesis and provides an outlook on related future works.

### Chapter 2

# **Design of Metal-Clad Semiconductor Lasers: Cavity Structures and Thermal Properties**

### 2.1 Introduction

Many of the works mentioned in Chapter 1 of metal-clad semiconductor lasers have demonstrated high quality performance with low energy, but only under low temperature. However, as candidates of light source in integrated photonic circuits, it is inevitable to investigate the possibility of room-temperature operation for these lasers. Thermal considerations thus become an essential part in device design, as the device self-heating may be severe for these lasers due to small device size and high local current density. To improve this situation, the relationship of the thermal properties with the cavity structure needs to be studied in detail. In this chapter, we explain the design of metal-clad semiconductor laser cavities and conduct thermodynamic simulations for improving the cavity design with better heat dissipation.

In section 2.2, the structure of wavelength-scale metal-clad semiconductor laser cavity is explained, including its key components and the factors to be taken into consideration for an optimized cavity design. We present a silver-clad InP/InGaAs cavity with an advanced capsule-shape that could be coupled to silicon-on-insulator (SOI) waveguide.

Then, in section 2.3, we investigate the thermal properties of the silver-clad InP/InGaAs cavity with relation to cavity layer components. Thermodynamic analysis is carried out to study the temperature distribution and self-heating with different InP p-cladding layer thickness.

#### 2.2 Cavity Structure

Figure 2.1 Design of a wavelength-scale silver-clad InP/InGaAs semiconductor laser cavity in capsule-shape.

As shown in Fig. 2.1, the laser cavity active layer is formed by InGaAs, with InP cladding on top and bottom serving as cladding. This design has been adopted from previous works in our laboratory, with serious efforts of optimizing each component [30]. Details of the cavity structure are explained as below.

**Cavity Dimension** The cavity dimension is set as in wavelength-scale, which means around 1.55  $\mu$ m as of the desired working wavelength for InGaAs, aiming at applications in telecommunication fields. We set the cavity length L to be 1.1  $\mu$ m and the cavity width W to be 0.84  $\mu$ m. The cavity is basically rectangular in shape, forming a Fabry-Perot cavity through the horizontal direction along the longer side of the cavity. In addition, the cavity has a curvature of R/L = 1.4 (R is radius of curvature) at both ends of the sidewall to form a capsule-like shape. Such capsule-shaped cavity is proved to reduce corner scattering and improve the optical confinement as compared to strictly rectangular cavities of the same dimensions [26, 27].

Active Layer The active layer is formed by InGaAs, with its thickness designed as 400 nm. This value is expected to provide enough confinement and Q factor of the cavity, while not being too high to bring difficulty in device fabrication.

**Cladding Layers** Above and below the active layer, there are two InP cladding layers which provides optical confinement in the vertical direction for the cavity. Regarding their layer thickness, the same trade-off between optical property and fabrication feasibility exists. We consider them to be at least 300 nm thick from results of optical simulations. For the lower InP cladding layer, it appears that the thickness also affects the coupling of cavity to the waveguide beneath, if there is any, since the light is expected to be coupled evanescently. For this layer, higher thickness provides better optical confinement and cavity Q factor, but gives worse coupling efficiency to the waveguide. Apart from optical properties, we later find out that this layer thickness also affects the thermal property of the cavity significantly, thus, we would keep the value as a range of 200 nm – 600 nm for the time being, and leave the discussion of this parameter in section 2.3.

**Contact Layers** The cavity is designed to work under electrically-pumped operation. The active layer and two adjacent InP cladding layers form a p-i-n junction ready for electroluminescence. There should be contact layers next to the InP layers, providing proper current injection. The n-contact layer is formed by n-InGaAs with a doping of 2e19 cm<sup>-3</sup>. The p-contact layer is formed by p-InGaAsP with a doping of 2e19 cm<sup>-3</sup>. In this case, the device is chosen to be n-top, since the electron injection from silver to n-InGaAs is easier without any barrier, while hole injection from metal into p-InGaAs has a large barrier of nearly 1 eV. As a result, the upper InP is n-doped, with a 50-nm n-InGaAs layer on top, and the lower InP is p-doped, with a 50-nm p-InGaAsP at the bottom.

**Insulation Layer** Since the cavity will be later covered in metal-cladding, there ought to be an insulation layer surrounding the III-V core (but not on top or bottom), separating it from the metal-cladding to avoid heavy optical loss from metal absorption. The insulation layer can be formed with various materials, such as SiN or SiO<sub>2</sub>. The choice of this insulation material depends on both optical and thermodynamic performance, as well as the ease of fabrication given the facilities available. The thickness of the insulation layer is also a critical parameter for the cavity performance. For smaller cavity of ~300 nm in diameter, the insulation layer is preferred to be gently thicker, about 175 nm, for higher quality factor [31]. However, for larger cavity, a thinner insulation layer reduces the cavity radiation loss into the substrate [31]. As SiO<sub>2</sub> has very low thermal conductivity, higher thickness may also bring in additional heat dissipation challenges. Thus, we use SiO<sub>2</sub> of about 70-100 nm in our design and fabrication.

**Metal Clad** A metal shield is covered all over the cavity, giving the name of "metal-clad" semiconductor cavity. Noble metal such as silver or gold would be preferred to act as a mirror-like structure, which is proved to bring strong optical confinement with relatively low loss, and to give better heat dissipation for the semiconductor structure in small size [15]. Silver is usually chosen, as it as it has lower loss under room temperature compared to gold or aluminum [30]. We also choose silver in our case, and it naturally acts as the cathode electrode adjacent to the n-InGaAs contact layer. In addition, very thin titanium is usually added as an adhesive layer underneath silver as silver may have poor adhesion to SiO<sub>2</sub> in real fabrication situation. The anode electrode, on the other hand, is chosen to be a gold layer, placed at some distance to the cavity and connected to the p-InGaAsP layer that is exposed through etching from the substrate. Since it would have not so much effect on the optical performance of the cavity itself, it is not included in this cavity model.

In the schematic shown in Fig 2.1, the cavity is seated on top of a silicon-on-insulator (SOI) waveguide at the bottom, which is proposed as a possible coupling scheme for downstream integration. SOI waveguide is chosen as it is compatible with the silicon technology and can be fabricated with standard techniques and low cost. In this design, the waveguide has a Si thickness of 220 nm, with a thin SiO<sub>2</sub> of 100 nm on top and a thick SiO<sub>2</sub> substrate at the bottom. Details of the integration with waveguide will be covered in Chapter 3.

### 2.3 Cavity Layer Composition and Thermal Analysis

The heating issue plays an important role for the room-temperature operation of the electrically-pumped metal-clad semiconductor laser given its small foot print in micrometer scale. The major heating sources in the device are explained as below [32].

**Joule Heating** This is the heating due to resistance in the semiconductor layers, and can be interpreted from its definition  $Q = I^2 R$ . In this structure, larger Joule heating will be generated mainly by the lower InP cladding layer and the bottom p-contact layer. However, Joule heating only contributes to a small part of the self-heating generally.

**Junction and Heterojunction Heating** The junction and heterojunction heating is the heat generated by the voltage change at the layer junctions. Junction heating is the heat generated between the undoped layer and adjacent doped layers, at the top and bottom of active layer in this case. Heterojunction heating is the heat generated between the doped semiconductor layers. Though heterojunction heating is estimated to be higher than Joule heating, they can be easily dissipated through the contact layers to the metal electrodes.

**Surface Recombination Heating** This heating source plays a more important role in small lasers than larger lasers, as the surface-to-volume ratio is higher. Surface recombination heating can be simulated with the electronic simulation model considering carrier density, surface recombination velocity, gain region area and quasi-Fermi level.

Auger Recombination Heating Auger recombination is another major heat source in small lasers, which is related to the carrier density, gain region volume, and quasi Fermi level. From previous studies, Auger recombination contributes largely to the self-heating issue with small lasers, and it is generated in the middle of the semiconductor layers which could be hard to dissipate [32].

| Layer Material       | Thickness (nm) | Refractive index <i>n</i> | Doping (cm <sup>-3</sup> ) |

|----------------------|----------------|---------------------------|----------------------------|

| n-InGaAs             | 50             | 3.53                      | 2 e19                      |

| n-InP                | 300            | 3.17                      | 1 e18                      |

| InGaAs               | 400            | 3.53                      | Undoped                    |

| p-InP                | 200-600        | 3.17                      | 5 e18                      |

| p-InGaAsP            | 50             | 3.4                       | 2 e19                      |

| SiO <sub>2</sub> /Ag | 160/100        | 1.45/-                    | N/A                        |

**Table II** List of layer materials and their doping concentration used for thermal analysis [33]. The refractive index of each layer is also shown for reference.

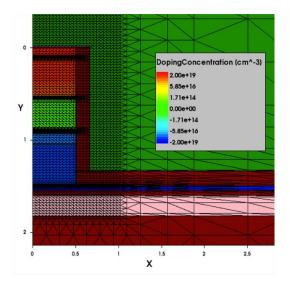

In order to improve the cavity design with better heat dissipation aimed for roomtemperature operation, we look into the thermal properties of this cavity to investigate its temperature distribution and self-heating with relation to cladding layer thickness. A commercial simulator, Sentaurus TCAD by Synopsys, is used for conducting thermodynamic simulations. The model is built according to layer constructions shown in Table II [30, 33].

**Figure 2.2** Constructed 2D structure with cylindrical symmetry in Sentaurus TCAD. Different color indicates p- and n- doping in the compositions. Black lines show the non-universal mesh for conducting simulation. The units for x- and y- axis are both um. The lower substrate is InP, and the upper green background is assumed to be silver.

For simplicity, we approximate the structure to be a symmetrical cylindrical cavity occupying the same footprint as the capsule-shaped one, and conduct 2D simulation in the cylindrical coordinate, as shown in Fig 2.2. The black lines are the non-universal mesh defined for simulation, and the color indicates the doping concentration in the 2D map. The mesh is set to be denser near the junctions for giving accurate calculation while keeping the simulation time rather feasible. We also include the silicon-on-insulator substrate at the bottom of the cavity, since the substrate also plays an important role in heat trapping, which should be taken into consideration for the device design. To analyze the self-heating effect, we include three main categories of heat sources: (1) Joule heating, (2) junction and heterojunction heating, and (3) non-radiative recombination heating [30, 33]. The thermal conductivities of critical materials are listed in Table III.

| Materials        | Thermal Conductivity $(W \cdot m^{-1} \cdot K^{-1})$ |

|------------------|------------------------------------------------------|

| Ag               | 429                                                  |

| InGaAsP          | 9.3                                                  |

| InP              | 68                                                   |

| InGaAs           | 5.0                                                  |

| SiO <sub>2</sub> | 1.1                                                  |

| Si               | 155                                                  |

**Table III** Thermal conductivity of different materials used in thermal simulations. It can be seen that  $SiO_2$  has extremely low thermal conductivity, which makes it hard for heat dissipation in this structure, while silver provides great thermal conductivity as a metal.

In order to have a general idea of the heating issue inside the cavity, we look into the heat localization inside the device by studying the temperature distribution at its cross-section at a typical operating current.

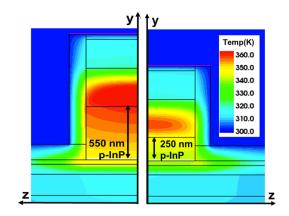

**Figure 2.3** Temperature distribution inside the cavity under I = 2mA. The graph on the left shows a cavity with p-InP thickness of 550 nm and the graph on the right shows a cavity with p-InP thickness of 250 nm. The color map shows severe heat localization at the active layer and its surrounding, and more at lower regions as compared to upper regions.

Figure 2.3 depicts the temperature distribution at the device cross-section under an operation current of I = 2 mA. The left shows a device with thick (550 nm) p-InP cladding, and the right shows one with thin (250 nm) p-InP cladding, while other factors are kept as the same. One could tell that in each case, the active layer has the highest temperature, while lower p-InP cladding also has higher temperature than the upper n-InP cladding. This is probably due to that the upper cladding has an easy heat dissipation path from the silver cladding at top, while the lower cladding is surrounded by insulation layers densely, without direct heat dissipation path. For the model with p-InP thickness lower as 250 nm, however, we see that self-heating effect inside this cladding layer is significantly suppressed.

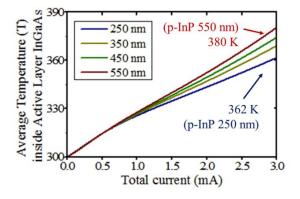

**Figure 2.4** Average temperature inside the device active layer InGaAs with increasing current, for cavities with different p-InP cladding thickness ranging from 250 nm to 550 nm.

We then move on to study the relationship of p-InP thickness with the overall device temperature. We calculate the average temperature inside active layer with increasing current, for devices with different p-InP thickness ranging from 550 nm to 250 nm. It can be seen that the relationship of the temperature with p-InP thickness is obvious, while the temperature inside active layer rises much quicker for a device with thicker p-InP cladding layer than that with thinner p-InP cladding layer. The cavity of 250 nm p-InP gives almost 20K temperature reduction at I = 3 mA compared to that of 550 nm p-InP thickness. The result proves that lower p-InP thickness gives advantage in device's thermal management and reduces the self-heating issue. Such improvement is critical for realizing room-temperature electrically-pumped operation of wavelength-scale metal-clad semiconductor laser.

However, a lower p-InP thickness may give worse optical confinement on the other hand, as the light could easily leak out to the device substrate, especially when the contrast of dielectric constant in InP (3.14) and InGaAs (3.53) is not sharply large. Further optimization of the cavity design in order to keep the improvement in thermal performance while not undermining the optical confinement is covered in Chapter 3.

### 2.4 Summary

In this chapter, the design of a wavelength-scale silver-clad InP/InGaAs cavity with advanced capsule-shape is presented and explained in detail. The thermal properties of this cavity sitting on top of SOI waveguide is studied.

It can be seen that the self-heating issue of small-size metal-clad semiconductor cavity is related to the p-InP layer thickness at the bottom of active layer, mainly due to the non-radiative process happened inside and at the junctions. By reducing the p-InP layer thickness to as low as 250 nm, one could mitigate the heat-trapping inside the cavity and reduce the active layer temperature as a result. In this way, the cavity structure is optimized for possible operating in room temperature.

### Chapter 3

## **Design of Metal-Clad Semiconductor Lasers: Integration with Waveguides**

#### 3.1 Introduction

In the previous chapter, we discuss the structure of the metal-clad semiconductor laser cavity and several factors affecting its performance in both optical and thermodynamic aspects. However, related optical confinement problems may arise when the we set the low p-InP layer thickness to be thinner as suggested by thermal considerations.

In order to solve this problem, we keep the optimized device cavity structure proposed in chapter 2, but look into the waveguide coupling scheme in search for a solution of both improved optical and thermal performance. There are two main considerations:

(1) For the design of cavity itself, optical confinement and thermal trapping are correlated as a trade-off, as a thicker InP gives better optical confinement but a thinner InP gives better heat dissipation, thus one would go into dead-end if limited to optimization of the cavity layer structure.

(2) For the application of our ultimate goal as searching for energy-efficient on-chip light source, the integration with waveguide is anyway inevitable to be taken into consideration for cavity design, since the proposed laser is aimed for emitting light to be coupled for downstream applications in integrated photonic circuits.

As a result, we look into design of the cavity with integration to waveguides, in search for a solution to save us out of the dilemma and solve both problems. In this chapter, we investigate integration of the metal-clad III-V semiconductor laser to a common silicon-on-insulator (SOI) waveguide, as proposed in chapter 2.

In section 3.2 to 3.4, we present our design of a special integrated feedback stub in the silver-clad InP/InGaAs laser coupled SOI waveguide, which serves as a powerful tool offering external tuning of the cavity quality factor (Q factor). We provide the result of finite-dimension time-domain (FDTD) simulation to confirm the effect of Q-factor tuning. We show step by step that with this integrated feedback stub, one could compensate the optical loss related to low InP thickness, without sacrificing the heat dissipation merits from the previous cavity design.

After that, in section 3.5, we provide theoretical analysis based on coupled-mode theory to explain this Q-factor-tuning mechanism quantitatively, and we compare the theoretical analysis result with those obtained from FDTD simulation.

### 3.2 Problem with Coupling Cavity to Waveguide

For integrated photonic circuits, there has been the debates over III-V/Si hybrid system with III-V-only system regarding active devices integrated with passive components. III-V-only system certainly gives advantages in the fabrication realm for research purpose, since the wafer can be grown directly using Metal-Organic Chemical Vapour Deposition (MOCVD) and do not need further manipulation such as alignment or bonding. However, III-V/Si hybrid system still remain a popular choice, as it can potentially make use of the supreme optical property of III-V materials for high quality active devices as well as the fundamental fabrication techniques in Si industry [34, 35]. Common methods of III-V/Si hybrid fabrication are either bottom-up (such as hybrid epitaxial growth of III-V on Si) or top-down (such as III-V layer and Si layer bonding).

In our design, we propose to couple the cavity evanescently to a silicon-on-insulator waveguide at the bottom for its simplicity in design and practicality in applications.

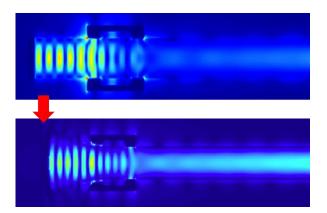

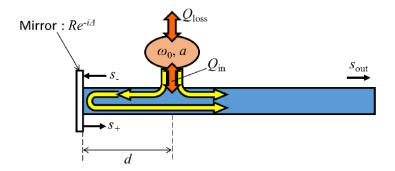

**Figure 3.1** Schematic of a typical metal-clad semiconductor cavity coupled to waveguide with two-end output.

Figure 3.1 shows the schematic of the cavity structure optimized from chapter 2 coupled to SOI waveguide. We study the cavity quality and the coupling situation of this structure with 3D finishte-dimension time-domatin (FDTD) simulation using a commercial software by *Lumerical Solutions, Inc.*

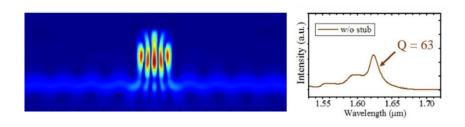

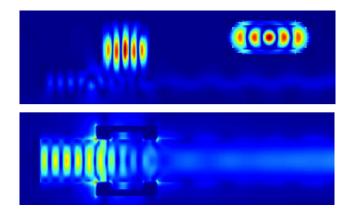

Figure 3.2 Left: The electric field intensity distribution of the resonant mode of this cavity coupled to SOI waveguide, obtained from FDTD simulation with a point-source excitation

inside the cavity. It can be seen that much light is leaked from both ends of the waveguide. Right: Simulated spectrum of light collected from the cavity of this coupled structure, under the same point-source excitation, showing a resonant mode with very low quality-factor, Q = 63.

The results are shown in Fig 3.2. From the electric field intensity distribution, it can be seen that both ends of the waveguide serve as an outlet of the light, and due to weak overlapping of the fields as well as scattering loss at the structure corners, the quality factor of the cavity is very low. The low InP thickness also contributes to the poor confinement, as light tends to be radiated out on their way to the waveguide. From the spectrum emitted from the cavity coupled to SOI waveguide, one could tell that this design has very poor optical quality and would not be feasible for an efficient on-chip light emitter.

Aiming for more efficient coupling scheme, we look into possibilities in advanced waveguide design.

### p-contact n-contact y x stub length j v z optical feedback stub metallic laser

### 3.3 Coupling with Straight Integrated Feedback Stub

**Figure 3.3** Left: Proposed coupling scheme with a straight integrated feedback stub. Right: Side view of the structure, with arrows showing the tentative light paths through the metal-clad laser (metallic laser) and the optical feedback stub.

To explore possible structures, we truncate one end of the waveguide with a mirror, and construct a laser integrated to waveguide with single-end output. In this structure, one-end of the silicon waveguide is truncated and coated with silver to serve as a mirror, forming a stub-like structure with certain distance to the cavity. The distance from this mirror to the cavity edge is defined as the stub length l.

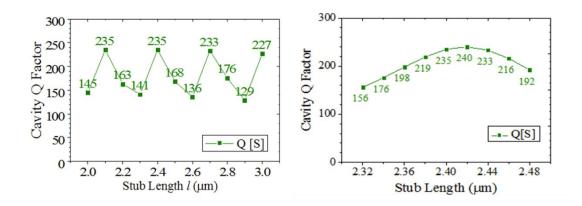

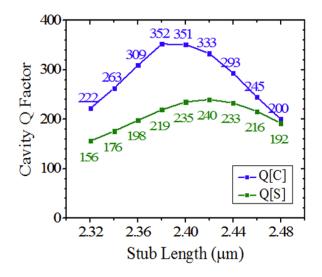

We construct this structure using 3D FDTD simulation and investigate the Q factor in the cavity with the same method as in section 3.2. It seems that there could be constructive or destructive interference of the light from the stub and from the cavity, when they interfere at the edge of the cavity. As a result, the overall quality factor of the cavity may be affected by the stub length 1. Thus, we study the cavity Q factor with relation to varying stub length *l*.

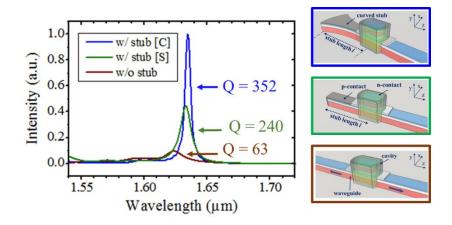

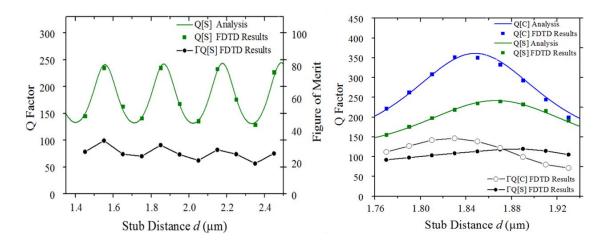

**Figure 3.4** The Q factor of the cavity obtained from 3D FDTD simulation, as a function of varying stub length *l*. The left plot shows the periodic change of Q factor as *l* changes from 2.0  $\mu$ m to 3.0  $\mu$ m at steps of 0.1  $\mu$ m, while the right plot shows the result at finer resolution as 1 changes from 2.32  $\mu$ m to 2.48  $\mu$ m at steps of 0.02  $\mu$ m, and the peak value of Q factor in this local case is 240. [S] stands for straight waveguide, as it will be compared to different structures in the following sections.

Figure 3.4 shows the result of the changing of Q factor as a function of stub length *l*. The left is the relationship as l changes from around 1.4  $\mu$ m to 2.5  $\mu$ m. One can see that as the distance changes, the quality factor of the cavity gets affected periodically, which agrees well with our intuitive expectation. To look further into the effect, we conduct the simulation with finer step of stub length, as shown on the right of Fig 3.4. It can be seen that the quality factor rises up to Q = 240 at a stub length of 2.42  $\mu$ m in this case, which is much larger than the double-end output waveguide case with Q = 63.

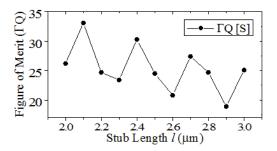

Figure 3.5 Figure of merit ( $\Gamma Q$ ) of the cavity coupled to waveguide with integrated feedback stub of changing length l.

Apart from cavity quality factor, we are actually more interested in its effect on the lasing threshold of the cavity. We would like to see whether the overall lasing threshold can be reduced from improvement of the cavity Q factor. In this case, the lasing threshold is determined by  $\Gamma Q$ , where  $\Gamma$  is the confinement factor of the mode inside the entire structure. We include the computation of  $\Gamma$  in our simulation, and plot  $\Gamma Q$  as the figure-of-merit along with the cavity Q factor, as of changing stub length *l*. The result is shown in Fig 3.5. One could see that the figure of merit changes accordingly as well, and it drops only very moderately with slightly a longer stub length.

This proves that the integrated feedback stub serves as a powerful tool in improving the overall optical performance of the device from optimized waveguide design. It improves the overall optical performance for the given cavity, with more efficient manipulation of the light with less radiative loss. Moreover, the improvement is made in the waveguide part, and does not affect the previously optimized thermal properties from the cavity structure.

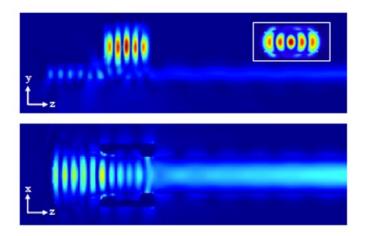

**Figure 3.6** Electric field intensity of *y-z* plane at x = 0 (top), *x-z* plane at center of waveguide core (below) and *x-z* plane at center of active layer (inset) at the resonant wavelength 1630 µm, with a straight feedback stub of length l = 2.42 µm.

To have a better understanding of the optical performance of this integrated structure, we look into the electric field intensity of the resonant mode in several critical cross-sections, as shown in Fig 3.6. One could see that the resonant mode inside the cavity is nicely confined, and there is also similar light confinement in the feedback stub. However, it can also be seen that there exists certain scattering loss, especially as the stub geometry is in a scale comparable with of the wavelength-scale-sized cavity, probably owing to the sharp corners of the stub shape.

We then look into possibilities to further improve the waveguide structure with this integrated feedback stub. Following the same philosophy of designing capsule-shaped cavity as an improvement of the rectangular ones, we propose to tune the shape of the feedback stub and investigate its potential pros and cons.

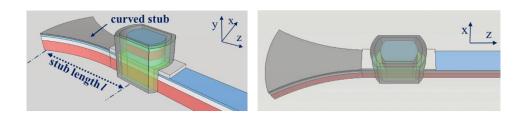

### 3.4 Coupling with Curved Integrated Feedback Stub

We would like to find an improved shape of the feedback stub. In order to do so, we simulated the electric field distribution of the metal-clad III-V cavity coupled to an infinite silicon-on-insulator plate and studied the shape of such vertically guided wave front. We expand the sidewalls to match with such shape, which actually resembles a Gaussian-beam profile. The structure of the metal-clad cavity coupled to waveguide with such a curved integrated feedback stub is shown in Fig 3.7. The stub length l is defined in a similar manner, from the end of the feedback stub mirror to the cavity. Again, we use 3D FDTD to study the Q factor and figure of merit of this structure, with changing stub length l.

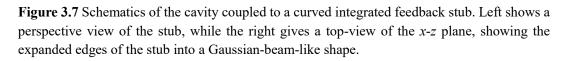

**Figure 3.8** Cavity Q factor with the feedback stub of changing stub length *l*, from 2.32  $\mu$ m to 2.48  $\mu$ m at step of 0.02 um. The blue line plots Q[C] as of a curved stub, while the green line plots Q[S] as of the previous results we obtained from a straight stub.

As shown in the plots in Fig. 3.8, the results show clearly significant improvement in cavity quality factor of a feedback stub with tuned shape compared to that of the straight one. At stub length  $l = 2.38 \ \mu m$ , the overall cavity Q factor reaches a local peak of Q = 352 at resonant wavelength of 1630 nm. The shift of the locally optimized stub length *l* from 2.42  $\mu m$  to 2.38  $\mu m$  can be intuitively understood as a change of effective reflective index of the waveguide in the stub from the expanded curved shape.

To confirm the improved optical property with a curved integrated feedback stub of tuned shape, we look into the electric field intensity distribution inside the center of waveguide of both a curved structure and straight structure, as shown in Fig 3.9 below.

**Figure 3.9** Electric field intensity of *x-z* plane at center of waveguide core at the resonant wavelength 1630 um, with a straight feedback stub of length  $l = 2.42 \,\mu\text{m}$  (top) and with a curved feedback stub of length  $l = 2.38 \,\mu\text{m}$  (bottom).

From the figure, one could see that the loss at the sharp corners that appear in straight feedback stub is largely reduced in the curved structure, which is consistent with the higher Q factor obtained from curved structure.

**Figure 3.10** Electric field intensity of *y*-*z* plane at x = 0 (top), *x*-*z* plane at center of waveguide core (below) and *x*-*z* plane at center of active layer (inset) at the resonant wavelength 1630 um, with a curved feedback stub of length  $l = 2.38 \mu m$ .

Figure 3.10 shows the electric field intensity of the cavity coupled to waveguide with curved integrated feedback stub with  $l = 2.38 \,\mu\text{m}$  obtained from 3D FDTD simulation. One could see that the cavity mode is well confined, while the coupling to waveguide gives improved results.

To see a more straight-forward comparison of the improvements, we plot the optical spectrum of the cavity with curved feedback stub of  $l = 2.38 \,\mu\text{m}$ , compared with that in the same cavity with a straight feedback stub at  $l = 2.42 \,\mu\text{m}$ , as well as without feedback stub but only SOI waveguide with double-end output. The spectrum is collected from FDTD simulation in the same method as described before, from a point-source excitation inside

the cavity. The results are shown in Fig 3.11. Schematics of the corresponding coupling schemes are also listed on the right side for comparison.

**Figure 3.11** Optical spectrum of the cavity with a curved feedback stub at 1 = 2.38 um (blue) which gives Q = 352, compared to that of the same cavity with a straight feedback stub at  $d = 2.42 \mu m$  (green) which gives Q = 240, and without feedback stub but only SOI waveguide (brown) which gives Q = 63. Schematics of the corresponding structures are listed at the right.

It is worth noticing that in addition to nearly 5-fold higher Q factor and lower threshold, the feedback stub section is broadened to 2.47  $\mu$ m<sup>2</sup> in this design, which could be used for practical p-type electrical contact with reduced contact resistance and improved overall heat dissipation, since it is coated in metal. This is also an improvement compared to previously-demonstrated designs, where the electrodes are not taken into consideration during numerical investigation [36-38], or large-area electrical contact on the bottom InP substrate is proposed, which might be challenging for device fabrication [39, 40].

#### 3.5 Understanding the Integrated Feedback Stub with Coupled-Mode Theory

From the previous investigations, we propose the design of a capsule-shaped metal-clad InP/InGaAs laser cavity coupled to a curved integrated optical feedback stub, as shown in Fig. 3.12.

**Figure 3.12** Perspective view of the of proposed wavelength-scale silver-clad InP/InGaAs laser coupled to SOI waveguide with curved integrated feedback stub. Inset shows a side view from x-y plane which explains the interaction between the metal-clad cavity (marked as metallic laser) and the feedback stub.

As mentioned before, we can intuitively understand this model by the idea of engineering the optical phase of the reflected wave from the stub from tuning the stub distance carefully, and reduce the light coupled directly from the cavity to the waveguide through destructive interference.

In order to understand the mechanism of such improvements in optical performance quantitively from a theoretical perspective, we look into the mode-coupling theory for a given coupled-cavity system.

**Figure 3.13** Diagraph of a typical system that consists of cavity and the optical feedback stub. The orange oval represents the cavity, and thee blue rectangle represents the waveguide. Yellow arrows partially show the light flowing in the system.

We adopt a general coupled-cavity system as shown in Fig 3.13. It consists of a cavity coupled to a waveguide terminated by a perfect mirror on one end, where  $\omega_0$  is the resonant

frequency of the cavity,  $Q_{\text{loss}}$  is the quality factor that represents the excess cavity loss due to absorption and/or scattering, and  $Q_{\text{in}}$  is the one that accounts for the optical coupling between the cavity and waveguide.  $s_+$  and  $s_-$  represent complex electrical amplitudes of the incoming and outgoing wave at the edge of the stub, R and  $\Delta$  are reflectance and phase-shift at the mirror, and d is the distance from the cavity to the end of stub.

One should notice that here, the stub distance d is used instead of the length l. d is defined as the distance from the edge of cavity to the end of stub, while l is the length from cavity center to the end of stub. In our case,  $d = l - 0.55 \mu m$ . For the theoretical analysis, the distance d is used since it is more intuitively relevant in the coupling mechanism, though l is a more general parameter and is independent of cavity size.

If we define a(t) as the electric amplitude of the resonant mode inside the cavity, its time evolution can be described based on the coupled mode theory as [41, 42]

$$\frac{da(t)}{dt} = \left(i\omega_0 - \frac{\omega_0}{2Q_{\text{loss}}} - \frac{\omega_0}{2Q_{\text{in}}}\right)a(t) + \sqrt{\frac{\omega_0}{2Q_{\text{in}}}}e^{-i\theta}s_+\left(t - \frac{d}{\nu}\right), \quad (1)$$

where v is the light velocity inside the stub. Incoming and outgoing wave  $s_+$  and  $s_-$  can be expressed as follows:

$$s_{+}(t) = Re^{-i\Delta}s_{-}(t)$$

, (2)

$$s_{-}(t) = -\sqrt{\frac{\omega_{0}}{2Q_{\rm in}}}e^{i\theta}a\left(t - \frac{d}{v}\right).$$

(3)

By inserting Eqs. (1) and (2) to Eq. (3), we obtain

$$\frac{da(t)}{dt} = \left(i\omega_0 - \frac{\omega_0}{2Q_{\text{loss}}} - \frac{\omega_0}{2Q_{\text{in}}}\right)a(t) - Re^{-i\Delta}\frac{\omega_0}{2Q_{\text{in}}}a\left(t - \frac{2d}{\nu}\right).$$

(4)

Now, let us write a(t) as

$$a(t) \equiv a_0 \exp\left(-\frac{\omega_{\rm sys}}{2Q_{\rm sys}}t + i\omega_{\rm sys}t\right),\tag{5}$$

where  $\omega_{\text{sys}}$  and  $Q_{\text{sys}}$  are the resonant frequency and quality factor of the total system that we want to derive. Then,  $a(t - \frac{2d}{\nu})$  in Eq. (4) can be expressed as

$$a\left(t - \frac{2d}{v}\right) = \exp\left[\frac{\omega_{\text{sys}}}{Q_{\text{sys}}}\frac{d}{v} - i\omega_{\text{sys}}\left(\frac{2d}{v}\right)\right]a(t) .$$

(6)

As a result, we can solve Eq. (4) with  $\omega_{sys}$  and  $Q_{sys}$  expressed as

$$\omega_{\rm sys} = \omega_0 \left[ 1 + \frac{R}{2Q_{\rm in}} \exp\left(\frac{\omega_{\rm sys}}{Q_{\rm sys}} \frac{d}{v}\right) \sin\left(\frac{2\omega_{\rm sys}d}{v} + \Delta\right) \right],\tag{7}$$

$$\frac{1}{Q_{\rm sys}} = \frac{\omega_0}{\omega_{\rm sys}} \left[ \frac{1}{Q_{\rm loss}} + \frac{1 + R\cos\left(2\frac{\omega_{\rm sys}}{c}d + \Delta\right)\exp\left(\frac{\omega_{\rm sys}d}{Q_{\rm sys}v}\right)}{Q_{\rm in}} \right].$$

(8)

When  $Q_{in} \gg 1$  (> R) and stub is sufficiently short,  $\omega_{sys} \approx \omega_0$  in Eq. (7), so that Eq. (8) can be approximated as

$$\frac{1}{Q_{\text{sys}}} = \frac{1}{Q_{\text{loss}}} + \frac{1 + R\cos(2\beta d + \Delta) \exp\left(\frac{\beta d}{Q_{\text{sys}}}\right)}{Q_{\text{in}}},$$

(9)

where phase constant  $\beta$  is defined as  $\beta = \frac{\omega_{sys}}{\nu}$ .

From Eq. (9), we can understand that  $Q_{sys}$  changes periodically by tuning the stub distance d. This is due to the fact that the backward travelling wave reflected by the mirror interferes with the forward wave and influence the Q factor of the total system.

We apply this theory to the simulation results we obtain in section 3.3 and section 3.4, and plot the relationship of Q factor and figure of merit with distance d from theoretical analysis, as shown in Fig 3.14.

**Figure 3.14** Relationship of Q factor (green for straight feedback stub and blue for curved feedback stub) with changing stub distance d, obtained from the coupled mode theory (lines) compared to that from FDTD simulation results (dots). The figure-of-merits obtained from FDTD simulation results are also plotted accordingly. Again, [S] stands for straight stub, and [C] stands for curved stub.

For the case of straight integrated feedback stub, as shown in the left of Fig. 3.14, the  $Q_{in}$  and  $Q_{loss}$  are derived to be 650 and 235 respectively. From the graph, we could see that excellent agreement is observed between the theory and simulation, both showing that the Q factor oscillates periodically with d as a result of interference and coupling.

For the case of curved integrated feedback stub, as shown in the right side of Fig. 3.14, the

$Q_{in}$  and  $Q_{loss}$  are 600 and 650, respectively. Such results imply reduced scattering loss and increased coupling efficiency of the curved integrated feedback stub compared to the straight case, which agrees well with the intuition of such design, as well as the simulation results we obtained.

### 3.6 Summary

In this chapter, we study the design of the cavity with integration to waveguides, in search for a structure that gives improved optical performance without disturbing the merits of heat dissipation we obtained with the low p-InP thickness structure discussed in Chapter 2.

We present our design of the silver-clad InP/InGaAs laser coupled to SOI waveguide with an integrated feedback stub formed at the non-output end of the waveguide, and investigate the relationship of cavity Q factor as well as figure of merit with relation to the feedback stub length and shape.

Periodic change of the cavity quality factor with relation the length is proved, and an optimized shape and length of the stub is obtained to effectively to tune the Q factor of the resonant mode inside the cavity. 5-fold improvement of the overall Q factor is obtained with a curved integrated feedback stub, confirmed through optical analysis using FDTD simulation.

In addition, theoretical explanation of the Q-factor tuning mechanism adopting coupledmode theory is presented, and the computation results agree well with the simulation data obtained from FDTD simulation.

As a result, an advanced structure of silver-clad InP/InGaAs laser cavity of capsule shape coupled to SOI waveguide with a curved integrated feedback stub is proposed to give significantly improved optical quality while keeping the advanced heat dissipation properties from the cavity structure.

It is also worth notice that the concept of integrated feedback stub is rather general and not limited to this specific case, and can be applicable to a variety of other waveguide-coupled metal-clad small lasers.

### **Chapter 4**

### **Fabrication of Metal-Clad Semiconductor Lasers**

#### 4.1 Introduction

As one could tell from the device structural design, the fabrication of metal-clad semiconductor lasers consists of a number of steps covering a fabrication process time of over 80 hours in total, and usually takes more than two weeks of continuous work for one complete batch. The fabrication process involves almost all aspects of modern nano- and micro- scale fabrication technology, including and not limited to wafer handling, multi-layer e-beam lithography, III-V semiconductor etching and cleansing with both dry-etching and wet-etching methods, plasma-enhanced chemical vapor deposition, multi-layer e-beam evaporation with lift-off processes and so on. As for devices designed for electrically-pumped operation and coupled to waveguide, the handling of electrodes, contact layers as well as the underneath waveguide geometry add even more complexity and additional steps in the fabrication flow.

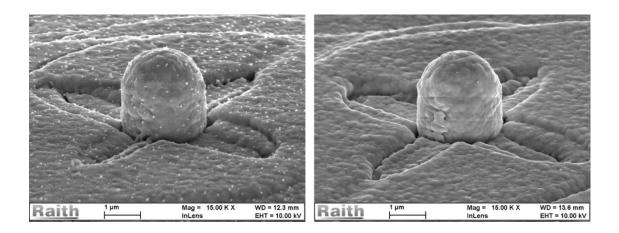

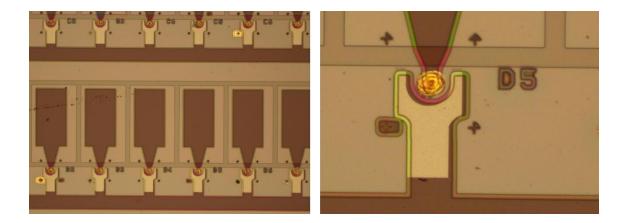

The overall performance of the proposed metal-clad semiconductor lasers largely depends on the fabrication quality, and it is non-trivial to optimize each step in the fabrication process for the realization of such devices in application [30, 43]. Before proceeding to advanced structures with waveguide and feedback stubs, we start from the fabrication of wavelength-scale silver-clad InP/InGaAs cavities, of various shapes, on InP substrate with gold electrodes aimed for electrically-pumped room-temperature lasing aiming for roomtemperature electroluminescence.

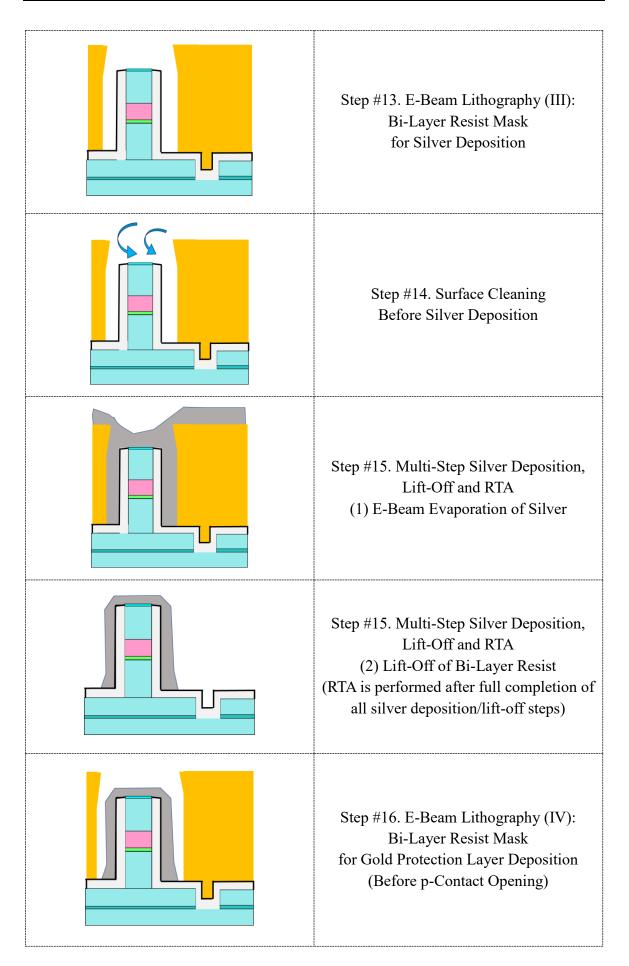

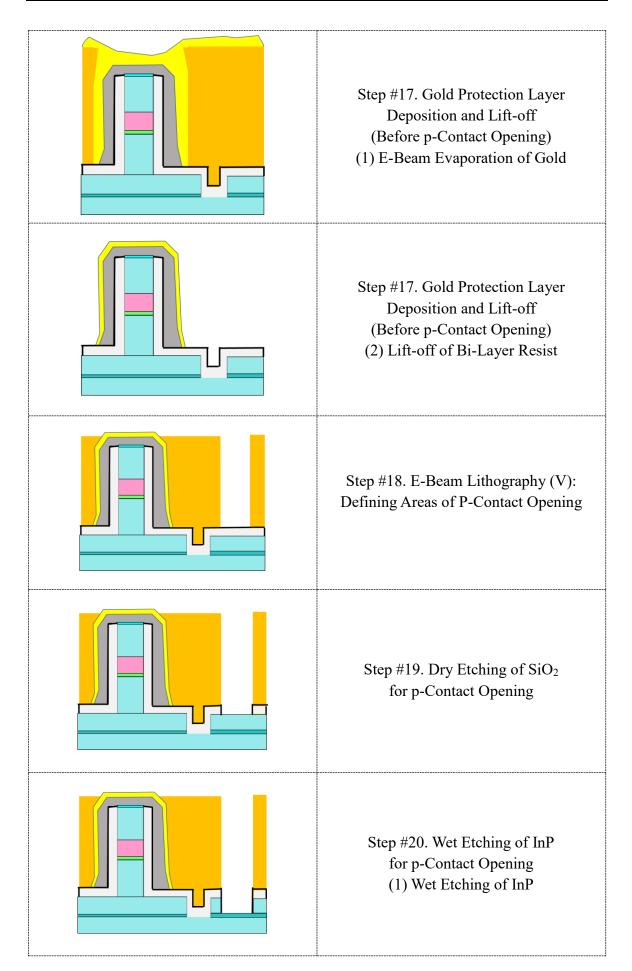

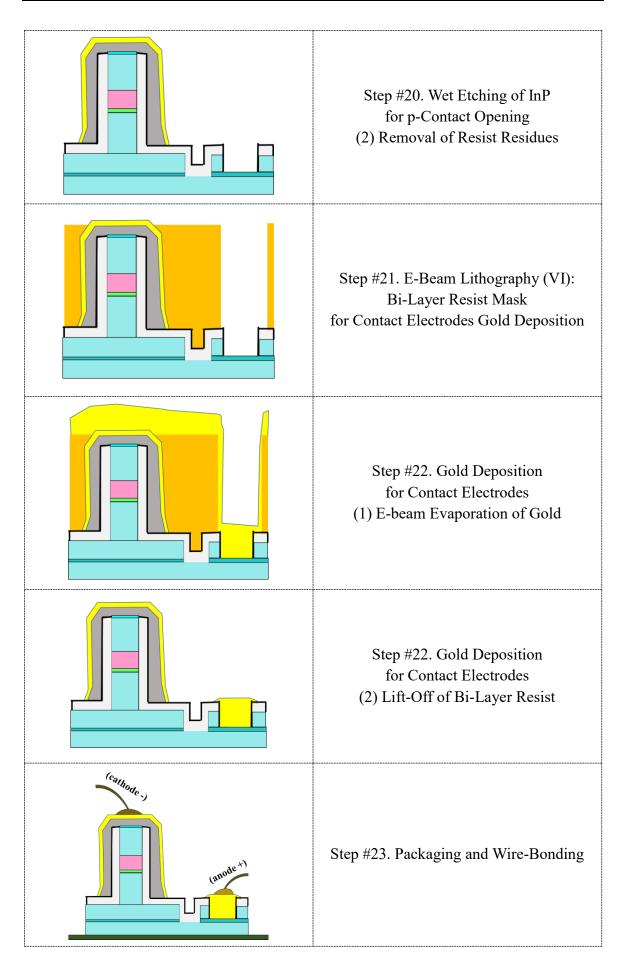

In this chapter, a complete fabrication flow including all relevant steps with detailed discussions on possible improvements in each step is presented. In section 4.2, we provide an introduction of the overall arrangement of device design of one fabrication batch. From section 4.3 to 4.4, extensive descriptions of the fabrication details and some characterization results of the fabrication quality with discussions on their effect and potential improvements are provided. Section 4.4 is divided into 23 steps in consequence, explaining the fabrication process of a batch of cavities on one sample. In addition, a flow chart of the fabrication process is included in Appendix A. In section 4.5, we give a brief review with general comments on the fabrication process instead of a summary. Potential improvements and some unsolved mysteries are also listed.

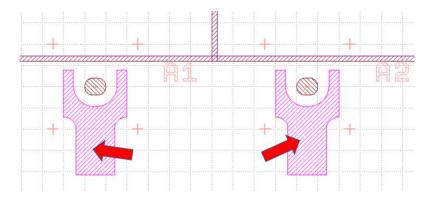

#### 4.2 Overall Arrangement of the Fabrication Batch

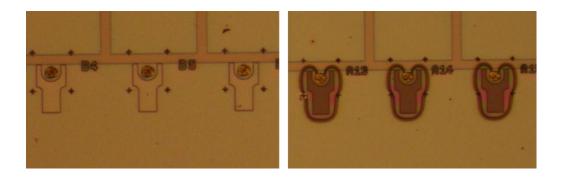

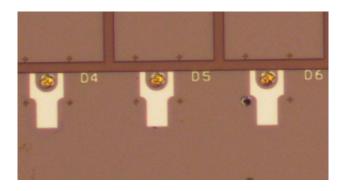

In each batch of fabrication, a group of cavities are fabricated and compared. It is very important to design wisely the cavity geometries for the experiment groups. As the pattern will be written in one wafer and go through exactly the same fabrication process, it provides a naturally controlled group of cavities to study only the effect of cavity shapes on their performance.

In this work, a series of 84 cavities are fabricated in each batch. There are 3 cavities for each design, and 28 different geometrical designs in total. The cavities are placed in 21 columns and 4 rows, and certain space is designed in between cavities for placing the electrodes in electrical pumping. The whole pattern occupies a space of around 6 mm length and 4 mm width on a wafer sample of about 1 cm by 1 cm size, which is easy to handle in various clean-room fabrication facilities. A list of the fabricated device designs is shown at Appendix B.

### 4.3 Wafer Preparation and Cleansing

InP-based wafer is utilized for fabrication. The epitaxial wafer is pre-ordered from a company and the layer composition is shown in Table IV. In particular, there is an InAlAs layer added next to the active layer which acts as an electron blocking layer to reduce the lasing threshold, suggested by previous thermoelectrical studies [30, 44].

| Layer Number | Layer Thickness | Composition     | Doping (cm^-3) |

|--------------|-----------------|-----------------|----------------|

| 0            | -               | InP Substrate   | Fe-Doped       |

| 1            | 200 nm          | p-1.4um InGaAsP | > 5 x 10e18    |

| 2            | 690 nm          | p-InP           | > 1 x 10e18    |

| 3            | 100 nm          | p-InP           | 1 x 10e18      |

| 4            | 12 nm           | p-InAlAs        | 1 x 10e18      |

| 5            | 400 nm          | U-InGaAs        | Undoped        |

| 6            | 200 nm          | n-InP           | 1 x 10e18      |

| 7            | 250 nm          | n-InP           | 5 x 10e18      |

| 8            | 50 nm           | n-InP           | >5 x 10e18     |

| 9            | 50 nm           | n-InGaAs        | 2 x 10e19      |

Table IV Layer composition of the InP-based III-V wafer utilized in fabrication process.

The wafer is usually stored in a vacuum chamber in clean room to keep its quality. Before using, the wafer can be taken out and cut to desired size. Standard organic cleansing is recommended to generally clean the surface.

### 4.4 Fabrication Technology: Procedures and Discussions

### 4.4.1 PECVD of SiO<sub>2</sub> as hard mask

A layer of  $SiO_2$  is deposited to the epitaxial wafer surface. The thickness is usually a few hundreds of nanometers, and it is not very critical. For example, we deposited 430 nm and 350 nm for two of our wafers. The  $SiO_2$  is deposited using plasma-enhanced chemical vapor deposition (PECVD).

This step was performed before cutting the wafer into smaller pieces, thus performed to the whole sheet of wafer at one time. There might be some non-uniformity of the deposited  $SiO_2$  thickness near the edges of the wafer, but since this layer of  $SiO_2$  serves as the hard mask and will be removed, it is not especially critical. The potential drawback might be non-uniformity when spin-coating resist gel in the following step, causing some non-uniformity of the pattern development time after e-beam lithography.

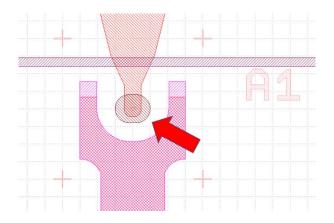

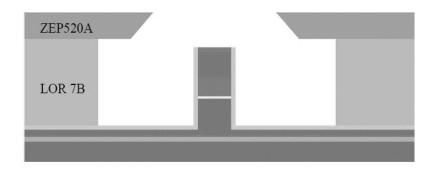

### 4.4.2 E-Beam Lithography (I): The Cavity

We perform the first E-beam lithography for defining the cavity structure for future etching. Since this is the first layer we write, it is very important to also define all markers for future alignments. Apart from markers surrounding each cavity, additional corner markers are placed. Some special markers are also included for exposure leading to corner markers. Waveguides, square and circular arrays are also included for checking the conditions in future steps such as development and etching.

Organic cleansing of the wafer is performed before spin-coating. Then OAP, a gel precursor, and ZEP520A, a positive e-beam resist gel, are spin-coated onto the SiO<sub>2</sub>-covered wafer.

E-beam lithography is carried out using RAITH SEM and E-Beam Lithography. In this step of E-beam lithography, the aperture is set to be the smallest possible, which is 10  $\mu$ m, and the step size is also set to as small as 6 nm. The dosage is tuned to be different for cavities and markers of different sizes so as to get the best development results.

The development is done using ZED-N50 followed by IPA rinsing. The development time is very critical. Based on previous experience, we use 1 min at first and check the results under an optical microscope. If it is not developed thoroughly, we add time section of 20 s and check the results. If one is not sure about the development according to new conditions and changed dosage, it is recommended to start from shorter time, e.g. 20 s or 40 s, and add on additional sections gradually after checking each time.

### 4.4.3 Cr Deposition and Lift-off

After E-beam lithography, the pattern of cavities and markers is developed, and these areas have  $SiO_2$  exposed out as ZEP520A is a positive resist gel.

We perform deposition of Chromium afterwards. The deposition is done using e-beam evaporation, and it is quite vertical as we keep the sample non-rotated in the chamber. The Cr thickness is designed to be around 30 nm. This thickness has been optimized roughly. If it is too thick like over 50 nm, the following lift-off step would be hard. If it is too thin like thinner than 25 nm, the pattern edges may also be not sharp enough for serving as high-resolution hard mask for future etching steps.

After Cr Deposition, we perform a process called lift-off. This is to use organic solution to react with the un-developed e-beam resist gel ZEP520A, so as to lift away the Cr on those areas together with the gel, leaving only Cr on the patterned area sticking to SiO<sub>2</sub>.

The solution used is ZDMAC, which can wash away ZEP520A effectively. Heating the beaker to 90 °C on a hot plate can improve the effectiveness of lift-off. The reaction last for over 2 min, sometimes for about 5 min or even 10 min to make sure the lift-off is completed. This step needs to be very carefully conducted inside the organic process hood, as ZDMAC is harmful if inhaled or absorbed through skin, and may produce vapors of mists that can cause eye, skin or respiratory tract irritation. The heating of ZDMAC may be skipped if room-temperature process is enough for successful lift-off. Then the sample will go through acetone and IPA cleansing.

# 4.4.4 Dry Etching of SiO<sub>2</sub>

Reactive-ion etching (RIE) is performed afterwards to etch the  $SiO_2$  in areas where it is exposed, i.e. not covered by Cr from the previous lift-off step. In this way, we expose the top layer of InP epitaxial wafer to air at regions without the pattern. The regions of patterning, the cavities and markers, are protected by Cr and  $SiO_2$  layers on top of the wafer.

We use Samco RIE etcher for the  $SiO_2$  etching, using CHF<sub>3</sub> and Ar as the source. The conditions are summarized in Table V below.

| RF Power | Gas Source           | Gas Flow   | Pressure | Tray   | Reference<br>Etch Rate |

|----------|----------------------|------------|----------|--------|------------------------|

| 80 W     | CHF <sub>3</sub> /Ar | 20/10 sccm | 2 Pa     | Quartz | 22 nm/ min             |

Table V Samco RIE  $SiO_2$  etching conditions.

Standard 10 min  $O_2$  cleansing procedures are carried out before and after reaction with the sample, aiming to keep the chamber as clean as possible. To minimize the dirt left after dry etching, it is also important to keep the sample clean before putting in the reaction chamber. The SiO<sub>2</sub> etching rate in this recipe is about 22 nm/ min, thus it takes about 16 min to etch the 350 nm SiO<sub>2</sub> mask, and about 22 min to etch the 430 nm SiO<sub>2</sub> mask. We add about 2 min of additional cleansing, using CHF<sub>3</sub>/Ar/O<sub>2</sub>, so as to improve the surface conditions. The table VI below shows the condition of additional cleansing.

| Step R | RF Power Gas Source | Gas Flow | Pressure | Tray | Reference<br>Etch Rate |

|--------|---------------------|----------|----------|------|------------------------|

|--------|---------------------|----------|----------|------|------------------------|

| (1) SiO <sub>2</sub><br>etching                 | 80 W  | CHF3/Ar                             | 20/10 sccm      | 2 Pa | Quartz | ~ 22<br>nm/min   |

|-------------------------------------------------|-------|-------------------------------------|-----------------|------|--------|------------------|

| (2) SiO <sub>2</sub><br>additional<br>cleansing | 100 W | CHF <sub>3</sub> /Ar/O <sub>2</sub> | 20/10/5<br>sccm | 2 Pa | Quartz | ~ 21.5<br>nm/min |

**Table VI** Samco RIE etching protocol for (1)  $SiO_2$  etching; (2) post-SiO<sub>2</sub>-etching additional cleansing conditions.

After dry-etching, we conduct hydrogen chloride surface cleansing to remove the oxide residues left. Diluted hydrogen chloride acid (H<sub>2</sub>O : HCl 100:6) is utilized. The sample is soaked in the solution for 2 min and rinsed in water twice. Then it is dried on top of 140 °C hot plate surface for 2 min.

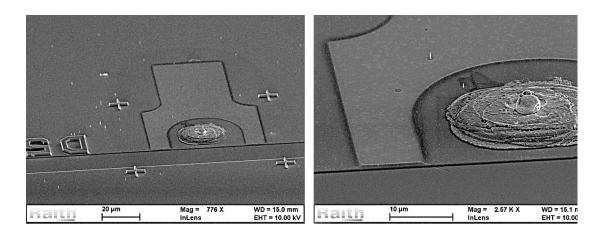

# 4.4.5 Dry etching of III-V cavity

Following the previous steps, a  $Cr/SiO_2$  hard mask of cavities are formed. Thus, we would move on to one of the most critical steps of this fabrication procedure, dry-etching of the III-V cavity.

Oxford ICP-RIE is used for dry etching of the III-V cavity, using  $CH_4$  and  $H_2$  as source. The conditions are summarized as Table VII below.

| HF Power | ICP Power | Pressure | Gas flow                | Step time | Steps of a cycle |

|----------|-----------|----------|-------------------------|-----------|------------------|

|          | 100 111   |          | CH <sub>4</sub> 15 sccm | <u>()</u> |                  |

| 120 W    | 100 W     | 15 mTorr | $H_2$ 45 sccm           | 60 s      | 4 - 8            |

Table VII Oxford ICP-RIE etching condition of InP/InGaAs/InP structure [30].

This recipe has been developed and tuned by C. Yu [30]. Huge efforts have been paid so as to improve the verticality of the cavity, so as to maximize the optical confinement performance. There are also several additional points to note in performing this step:

(1)  $O_2$  cleansing of the empty chamber is performed before and after the sample etching and cleansing.

(2) Sufficient rest of about 10 min is recommended for after every about 4 or 5 cycles, so as to cool down the chamber temperature.

(3) For wafer with InAlAs layer, the etching recipe has to be changed when etching through the InAlAs layer. This special recipe is as Table VIII below.

| HF Power | ICP Power | Pressure | Gas flow                  | Step time  | Steps of a cycle |

|----------|-----------|----------|---------------------------|------------|------------------|

| 00.111   | 0.111     | 16 5     | CH <sub>4</sub> : 15 sccm | <i>.</i> . |                  |

| 80 W     | 0 W       | 15 mTorr | H <sub>2</sub> : 45 sccm  | 5 min      | depends          |

Table VIII Oxford ICP-RIE etching conditions for etching through InAlAs layer.