## Research on Performance Optimization Methods based on Performance Analytical Modeling and Communication Latency Hiding in GPU

(GPU の性能分析モデリングと通信レイテンシの隠蔽に基づく性能の最適化方法に関する研究)

Doctoral Dissertation 博士論文

## Cheng Luo

#### 羅成

Submitted to Department of Computer Science,

Graduate School of Information Science and Technology,

The University of Tokyo

in partial fulfillment of the requirements for the degree of

Doctor of Information Science and Technology

Thesis Supervisor: Reiji Suda (須田礼仁) Professor of Computer Science

June 14, 2013

**Abstract:** Stream processing has been widely used since the emergence of stream applications such as time varying visualization and audio/video processing. Stream processing can exploit the inherent parallelism of the pipeline while the different stream elements also can be processed simultaneously to achieve data parallelism. Graphic processing unit(GPU) is one of the most successful stream architectures in recent years which is originally designed for acceleration of graphics applications. Now, it is widely used as General-purpose computing on graphics processing units (GPGPU) to accelerate many scientific applications with more than 10 times speedup over CPU platform. There are many new programming languages that help programmers to write parallel applications with GPUs such as Brook+, CUDA and OpenCL. With these programming and architectural features, programmers can quickly port their programs to a GPU based platform. However, if programmers want to have a better performance, they need to have a further understanding at various features of the low-level architecture and associated bottlenecks in their applications which will increase their burden in writing parallel applications. Therefore, there are many researches working on performance optimization methods from many aspects for programmers without much knowledge of GPU.

The motivation behind this work was caused by the emerging of high computational potential GPU along with the difficulty of writing high performance parallel programs on GPU based system. Our interests focus on performance prediction problem and communication latency between the host and the device problem. For performance prediction problem, it is difficult to predict the performance of kernel codes on GPU without enough knowledge about the low level architecture. Therefore, programmers may use unsuitable configuration to run their applications on GPUs which may lead to poor performance. Therefore, performance analytical model is needed to help programmers better understand the performance of their applications on GPU and find out the performance bottlenecks.

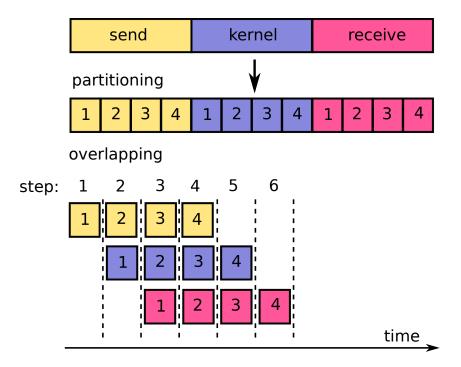

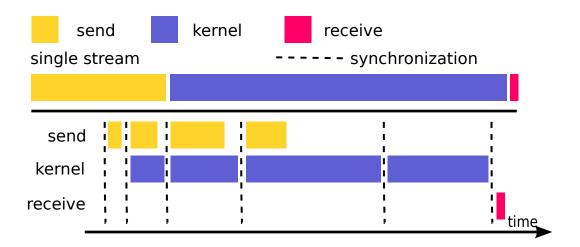

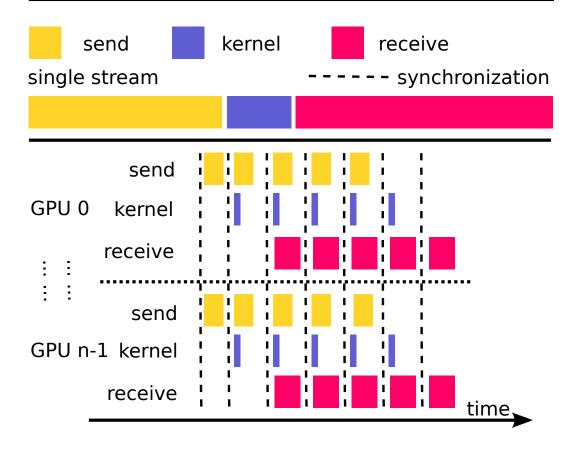

On the other hand, the communication latency between the host and device also can greatly affect the performance. CUDA programs include two parts: host code running on CPU and device code running on GPU. The host code invokes the device code to execute the kernel operation while the input and output streams are stored in device memory. As the device memory is separated from the host memory, streams are required to be transferred between them which leads to the communication latency between the host and device. According to different application types, the communication latency overhead between the host and device will account from very little to very high proportion of the total execution time cost. It is difficult for programmers to achieve high performance without awareness of the communication latency. CUDA supports concurrent execution for kernel execution and data transfer. Notice that some latest NVIDIA Tesla series GPUs begin to support two copy engines for bi-directional data transfer which enables to launch data send, kernel execution and data receive simultaneously. With this new feature, it is possible to use three streams respectively for data send, kernel execution and data receive to hide the communication latency by overlapping the three streams.

In this thesis I am proposing performance optimization methods based on performance analytical modeling and communication latency hiding to solve the performance prediction problem and communication latency problem respectively. For performance prediction problem, I propose a performance analytical model which can help programmers have a better insight into their applications and give a better configuration to execute application based on the predicted results. For communication latency problem, I propose a task partitioning and scheduling method named TPSM to help programmers achieve to hide the communication latency between the host and the device in GPU based system.

The performance analytical model can estimate the execution time of massively parallel programs which take the instruction-level and thread-level parallelism into consideration. The model contains two components: memory submodel and computation submodel. The memory submodel can estimate the cost of memory instructions by considering the number of active threads and GPU memory bandwidth. Correspondingly, the computation submodel can estimate the cost of computation instructions by considering the number of active threads and application's arithmetic intensity. I use ocelot to analyze PTX codes to obtain several input parameters for the two submodels such as memory transaction number and data size. Based on the two submodels, the analytical model can estimate the cost of each instruction while considering instruction-level and thread-level parallelism, thereby estimating the overall execution time of an application. With the predicted results, programmers can choose a suitable configuration to execute their applications with better performance.

I also propose a Task Partition and Scheduling Method(TPSM) which can help programmers to partition individual GPU application into subtasks and improve the performance of individual application with three streams by overlapping data send, kernel execution and data receive. With two copy engines, the work support simultaneous data send, kernel execution and data receive while previous work can only support simultaneous unidirectional data transfer and kernel execution. To extract the features of application, I classify GPU applications into several basic types from computation-to-communication ratio aspect and send-to-receive ratio aspect.

With the classification, I design corresponding task partitioning and scheduling submethods. I also design a time optimal data transfer algorithm to achieve optimal data transfer between host and device in multiple GPU architecture. TPSM can be applicable in single GPU architecture, multiple GPU symmetric architecture and multiple GPU non-symmetric architecture.

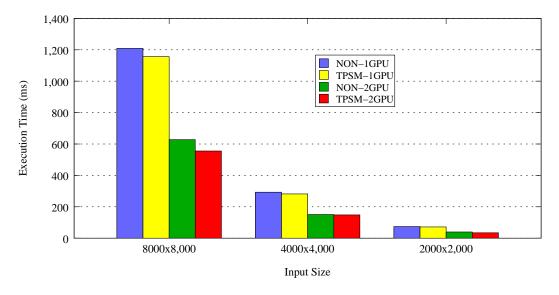

I use four benchmarks to test the performance analytical model and tasking partitioning and scheduling method on various GPUs. The results show that the performance analytical model can achieve on average around 90% accurate ratio for the prediction of kernel execution. The results of TPSM show that the work proposed in this thesis can successfully hide the communication latency between for individual application to achieve high performance which is very close to the lower bound time cost.

**Keywords:** Performance, prediction, model, task partitioning, task scheduling, overlapping computation and communication, parallelism, GPU

### Acknowledgments

I would like to express gratitude to all those people who helped me during the writing of this thesis.

I owe my deepest gratitude to my supervisor, professor Reiji Suda, for guiding me into this inspiring and challenging area in computer science. I have been extremely lucky to have a supervisor who cared so much about my work, my life in Japan and who discussed with me and responded to my questions every week. Thank him so much for all his support and encouragement over these past three years.

I also would like to thank all members in Suda lab for provide the support for everything.

I thank my parents for supporting and understanding me all the time.

I must express my gratitude to Ting, my wife, for her continued support, encouragement, quiet patience unwavering love which in the end makes this dissertation possible.

Many thanks to Sunpyo Hong for applying information about GPU emulator and benchmarks.

Thanks to Michael Linderman for applying Merge benchmarks.

Thanks to the patient technological replies from the gpuocelot groups.

This work was partially supported by Core Research of Evolutional Science and Technology (CREST) project "ULP-HPC: Ultra Low-Power, High-Performance Computing via Modeling and Optimization of Next Generation HPC Technologies" of Japan Science and Technology Agency (JST) and Grant-in-Aid for Scientific Research of MEXT Japan.

# Contents

| 1 | Inti | roduction                                                         | 1  |

|---|------|-------------------------------------------------------------------|----|

|   | 1.1  | Parallel Computing from CPU to CPU+GPU                            | ]  |

|   | 1.2  | Motivation                                                        | į  |

|   | 1.3  | Contributions                                                     | 4  |

| 2 | Bac  | kground                                                           | 7  |

|   | 2.1  | CUDA Framework                                                    | 7  |

|   | 2.2  | GPU Architecture                                                  | Ć  |

|   | 2.3  | GPU Ocelot                                                        | 1( |

|   | 2.4  | Divisible Load Scheduling                                         | 11 |

| 3 | Per  | formance Analytical Model                                         | 13 |

|   | 3.1  | Architecture                                                      | 13 |

|   | 3.2  | Assembly Code Analysis                                            | 14 |

|   | 3.3  | Execution of Multiple Warps                                       | 15 |

|   |      | 3.3.1 MPD submodel                                                | 17 |

|   |      | 3.3.2 CPD submodel                                                | 17 |

|   | 3.4  | Calculation Model                                                 | 19 |

|   | 3.5  | Experiment Evaluation                                             | 21 |

|   |      | 3.5.1 Configuration                                               | 21 |

|   |      | 3.5.2 Results                                                     | 23 |

| 4 | АЛ   | Cask Partitioning and Scheduling Method                           | 37 |

|   | 4.1  | Application Classification                                        | 37 |

|   | 4.2  | TPSM for Single GPU Architecture                                  | 36 |

|   |      | 4.2.1 Partitioning and Scheduling for Kernel Bound Applications . | 40 |

|   |      | 4.2.2 Partitioning and Scheduling for Data Transfer Bound Appli-  |    |

|   |      | cations                                                           | 47 |

|   | 4.3  | TPSM for Symmetric Multiple GPUs Architecture                     | 55 |

|   |      | 4.3.1 Time Optimal Data Transfer Algorithm for Symmetric Mul-     |    |

|   |      | tiple GPUs Architecture                                           | 55 |

|   |      | 4.3.2 TPSM                                                        | 32 |

|   | 4.4  | TPSM for Non-symmetric Multiple GPUs Architecture                 | 77 |

|   |      | 4.4.1 Time Optimal Data Transfer Algorithm for Non-symmetric      |    |

|   |      | CPUs Architecture                                                 | 75 |

| viii | Contents |

|------|----------|

|      |          |

|              |       | 4.4.2  | TPSM                                  | . 80  |

|--------------|-------|--------|---------------------------------------|-------|

|              | 4.5   | Exper  | imental Evaluation                    | . 82  |

|              |       | 4.5.1  | Symmetric Architecture                | . 83  |

|              |       | 4.5.2  | Non-symmetric Architecture            | . 100 |

| 5            | Rela  | ated W | Vorks                                 | 109   |

|              | 5.1   | GPU I  | Performance Prediction                | . 109 |

|              |       | 5.1.1  | GPU Analytical and Performance Models | . 109 |

|              |       | 5.1.2  | GPU Simulators                        | . 110 |

|              | 5.2   | Comm   | nunication Latency Hiding             | . 111 |

|              |       | 5.2.1  | Divisible Load Scheduling             | . 111 |

|              |       | 5.2.2  | GPU Performance Optimization          | . 114 |

|              |       | 5.2.3  | Stream Overlapping                    | . 115 |

| 6            | Con   | clusio | ns and Future Work                    | 117   |

|              | 6.1   | Conclu | usions                                | . 117 |

|              | 6.2   | Future | e Work                                | . 118 |

| $\mathbf{A}$ | App   | oendix |                                       | 121   |

| Bi           | bliog | raphy  |                                       | 125   |

# List of Figures

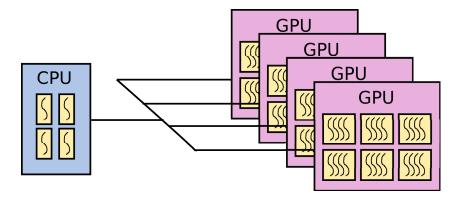

| 1.1  | CPU + GPU heterogeneous system                                 | 2  |

|------|----------------------------------------------------------------|----|

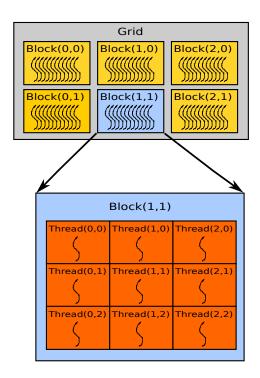

| 2.1  | Grid of Thread Blocks                                          | 8  |

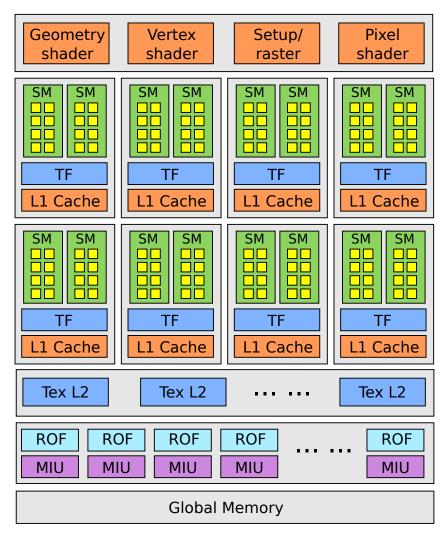

| 2.2  | GPU Architecture                                               | (  |

|      |                                                                |    |

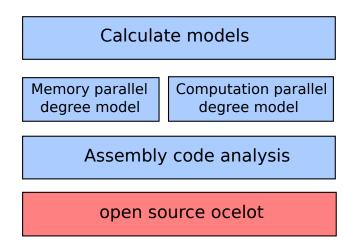

| 3.1  | Performance Analytical Model Architecture                      | 13 |

| 3.2  | PTX code generated from CUDA code with ocelot                  | 14 |

| 3.3  | Multiple Warps Execution in GPU Architecture                   | 16 |

| 3.4  | The Execution of Multiple Warps with MPD Awareness             | 16 |

| 3.5  | Calculate Period Type 1                                        | 19 |

| 3.6  | Calculate Period Type 2                                        | 20 |

| 3.7  | Calculate Period Type 3                                        | 21 |

| 3.8  | Calculate Period Type 4                                        | 21 |

| 3.9  | Linear Filter Results in GTX260                                | 23 |

| 3.10 | Linear Filter Results in Tesla C2050                           | 24 |

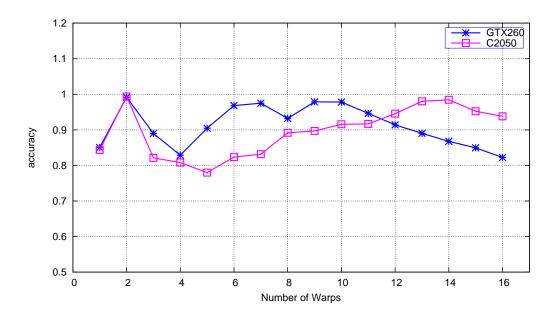

| 3.11 | The Accuracy of Linear Filter in GTX260 and Tesla C2050 $$     | 24 |

| 3.12 | Linear Filter Results in Tesla C2075                           | 25 |

| 3.13 | Linear Filter Results in Tesla K20c                            | 25 |

| 3.14 | The Accuracy of Linear Filter in Tesla C2075 and Tesla K20c $$ | 26 |

| 3.15 | Sepia Filter Results in GTX260                                 | 26 |

| 3.16 | Sepia Filter Results in Tesla C2050                            | 27 |

| 3.17 | The Accuracy of Sepia Filter in Two GPUs                       | 27 |

| 3.18 | Sepia Filter Results in Tesla C2075                            | 28 |

| 3.19 | Sepia Filter Results in Tesla K20c                             | 28 |

| 3.20 | The Accuracy of Sepia Filter in Tesla C2075 and Tesla K20c     | 29 |

| 3.21 | Black-scholes Results in GTX 260                               | 29 |

| 3.22 | Black-scholes Results in Tesla C2050                           | 30 |

| 3.23 | The Accuracy of Black-scholes in Two GPUs                      | 31 |

| 3.24 | Black-scholes Results in C2075                                 | 31 |

| 3.25 | Black-scholes Results in Tesla K20c                            | 32 |

| 3.26 | The Accuracy of Black-scholes in Tesla C2075 and Tesla K20c    | 32 |

| 3.27 | Matrix Multiplication Results in GTX260                        | 33 |

| 3.28 | Matrix Multiplication Results in Tesla C2050                   | 33 |

| 3.29 | The Accuracy of Matrix Multiplication in Two GPUs              | 34 |

| 3.30 | Matrix Multiplication Results in Tesla C2075                   | 34 |

x List of Figures

|      | Matrix Multiplication Results in Tesla K20c                                  | 35<br>35 |

|------|------------------------------------------------------------------------------|----------|

| 4.1  | The Classification of Applications                                           | 38       |

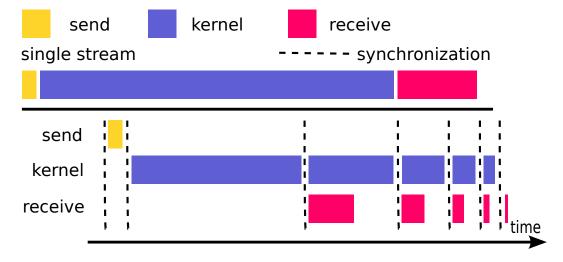

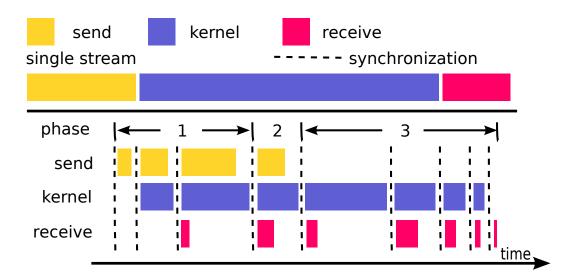

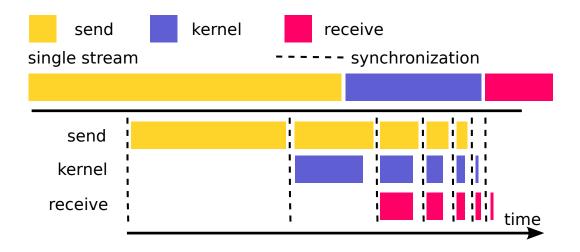

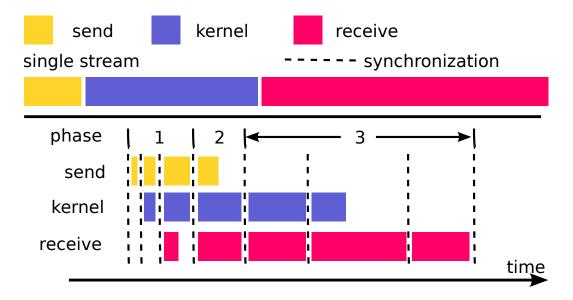

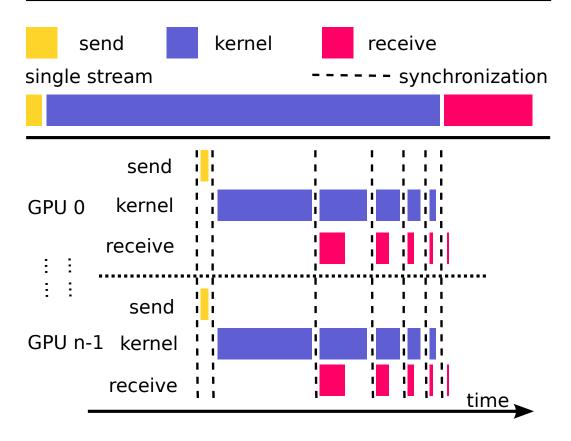

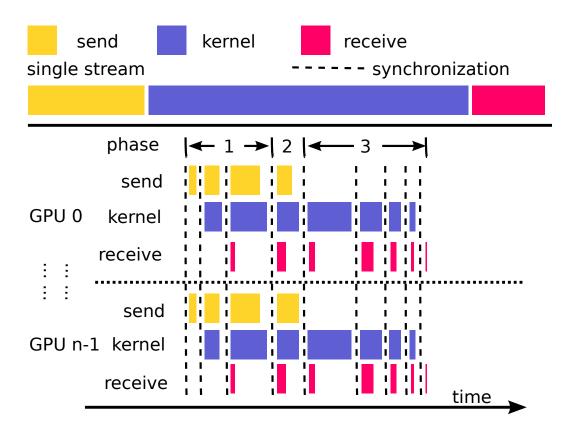

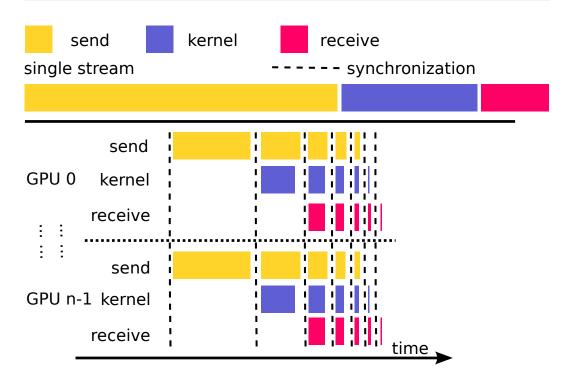

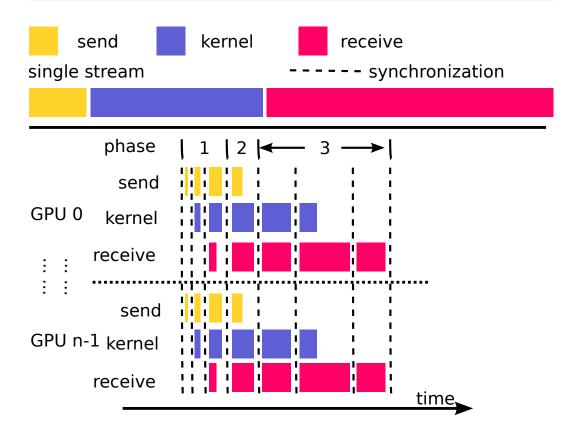

| 4.2  | The Basic Idea of TPSM                                                       | 40       |

| 4.3  | TPSM for Kernel Bound and Send Heavy in Single GPU Architecture              | 41       |

| 4.4  | TPSM for Kernel Bound and Receive Heavy in Single GPU Architecture           | 42       |

| 4.5  | TPSM for Kernel Bound and General Heavy in Single GPU Architecture           | 44       |

| 4.6  | TPSM for Data Transfer Bound and Send Heavy in Single GPU Ar-                |          |

|      | chitecture                                                                   | 48       |

| 4.7  | TPSM for Data Transfer Bound and Receive Heavy in Single GPU                 |          |

|      | Architecture                                                                 | 51       |

| 4.8  | TPSM for Data Transfer Bound and General Heavy in Single GPU                 |          |

|      | Architecture                                                                 | 54       |

| 4.9  | Data Size Optimality Problem                                                 | 58       |

| 4.10 | Convex Mixture                                                               | 59       |

| 4.11 | Upper-right Convex Hull Data Transfer Size with Scheduling Length ${\cal T}$ | 60       |

| 4.12 | TPSM for Kernel Bound and Send Heavy in Symmetric Multiple                   |          |

|      | GPU Architecture                                                             | 62       |

| 4.13 | TPSM for Kernel Bound and Receive Heavy in Symmetric Multiple                |          |

|      | GPU Architecture                                                             | 65       |

| 4.14 | TPSM for Kernel Bound and General Heavy in Symmetric Multiple                |          |

|      | GPU Architecture                                                             | 66       |

| 4.15 | TPSM for Data Transfer Bound and Send Heavy in Symmetric Mul-                |          |

|      | tiple GPU Architecture                                                       | 70       |

| 4.16 | TPSM for Data Transfer Bound and Receive Heavy in Symmetric                  |          |

|      | Multiple GPU Architecture                                                    | 73       |

| 4.17 | TPSM for Data Transfer Bound and General Heavy in Symmetric                  |          |

|      | Multiple GPU Architecture                                                    | 76       |

| 4.18 | Two Layer Partitioning                                                       | 80       |

| 4.19 | Scheduling Process for Non-symmetric Dual GPUs                               | 81       |

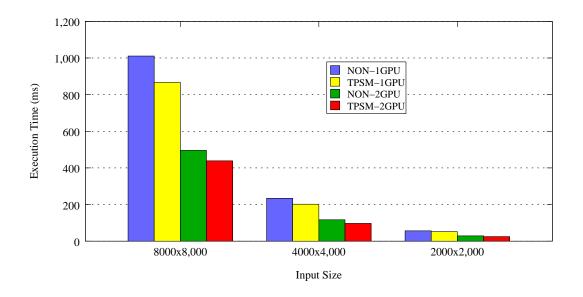

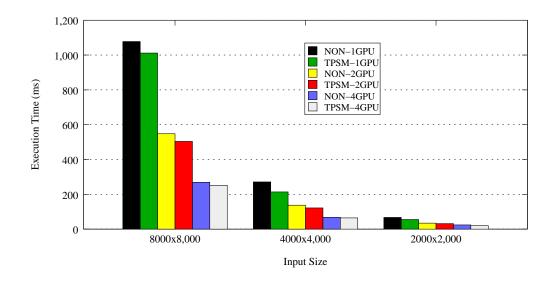

| 4.20 | Linear Filter Results in Tesla C2070                                         | 84       |

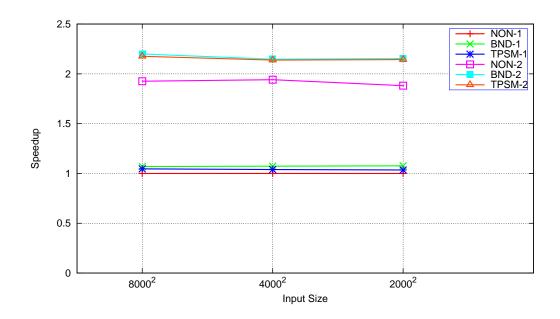

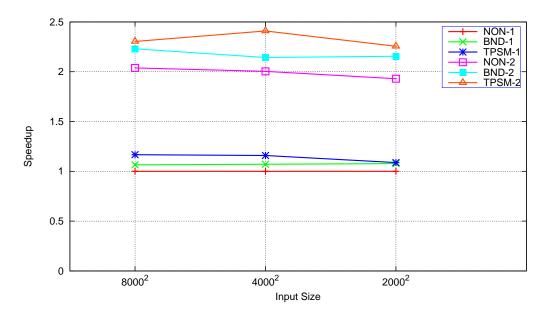

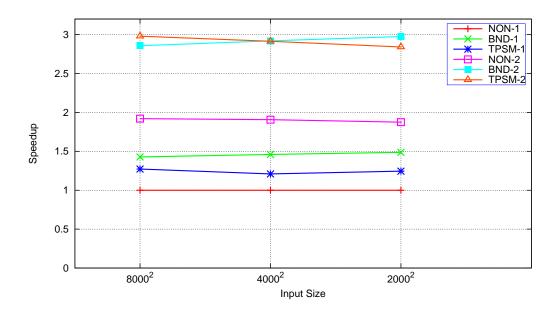

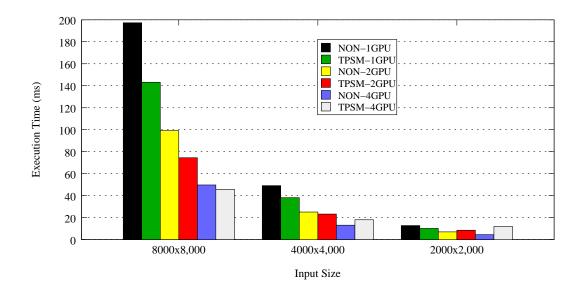

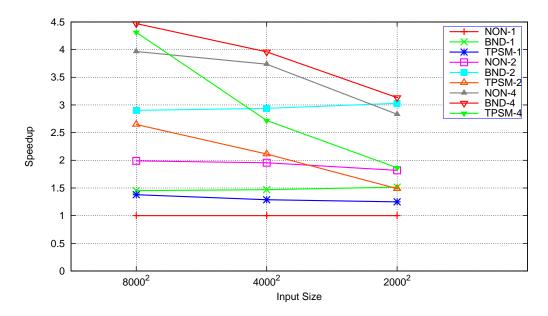

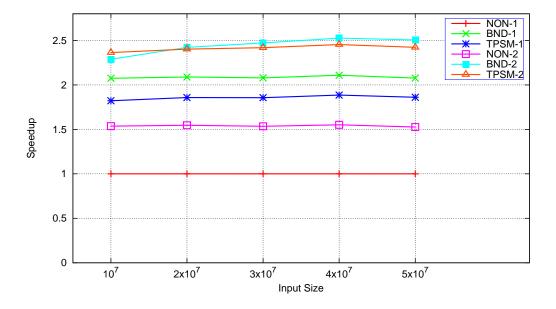

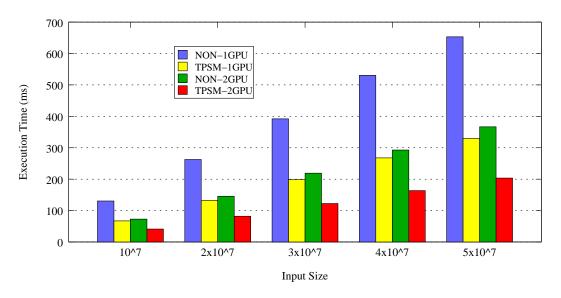

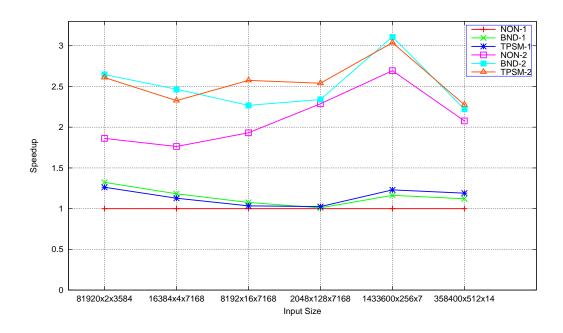

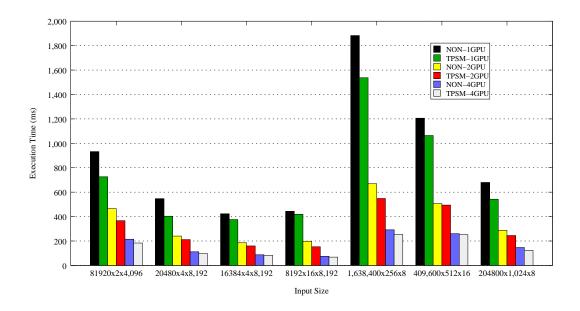

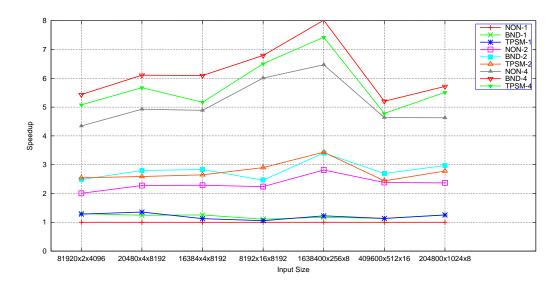

|      | Linear Filter Speedup Results in Tesla C2070                                 | 85       |

|      | Linear Filter Results in Tesla C2075                                         | 85       |

|      | Linear Filter Speedup Results in Tesla C2075                                 | 86       |

|      | Linear Filter Results in Tesla M2090                                         | 87       |

|      | Linear Filter Speedup Results in Tesla M2090                                 | 87       |

|      | Sepia Filter Results in Tesla C2070                                          | 88       |

| 4.27 | Sepia Filter Speedup Results in Tesla C2070                                  | 88       |

List of Figures xi

| 4.28 | Sepia Filter Results in Tesla C2075                                         |

|------|-----------------------------------------------------------------------------|

| 4.29 | Sepia Filter Speedup Results in Tesla C2075                                 |

| 4.30 | Sepia Filter Results in Tesla M2090                                         |

| 4.31 | Sepia Filter Speedup Results in Tesla M2090                                 |

| 4.32 | Black-Scholes Results in Tesla C2070                                        |

| 4.33 | Black-Scholes Speedup Results in Tesla C2070                                |

| 4.34 | Black-Scholes Results in Tesla C2075                                        |

| 4.35 | Black-Scholes Speedup Results in Tesla C2075                                |

| 4.36 | Black-Scholes Results in Tesla M2090                                        |

| 4.37 | Black-Scholes Speedup Results in Tesla M2090 95                             |

| 4.38 | Matrix Multiplication Results in Tesla C2070                                |

| 4.39 | Matrix Multiplication Speed Results in Tesla C2070 96                       |

| 4.40 | Matrix Multiplication Results in Tesla C2075                                |

| 4.41 | Matrix Multiplication Speed Results in Tesla C2075 98                       |

| 4.42 | Matrix Multiplication Results in Tesla M2090                                |

| 4.43 | Matrix Multiplication Speedup Results in Tesla M2090 99                     |

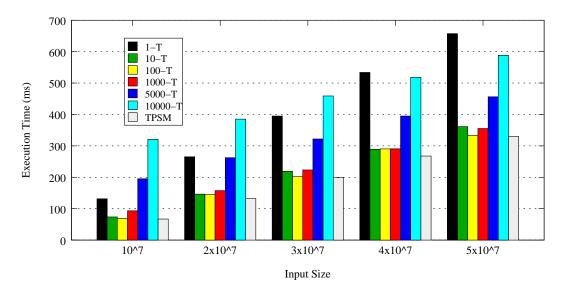

| 4.44 | Black-Scholes Results with equal size subtasks in Tesla C2075 $\ldots$ 100  |

| 4.45 | Black-Scholes Speedup Results with equal size subtasks in Tesla C2075101 $$ |

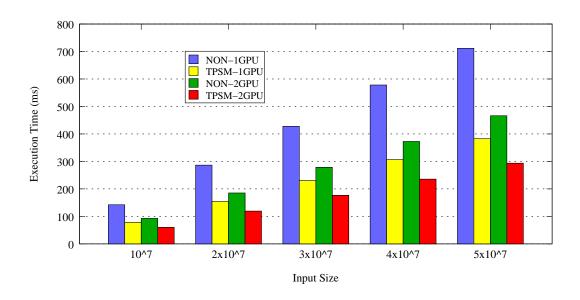

| 4.46 | Linear Filter Results in Non-symmetric Architecture                         |

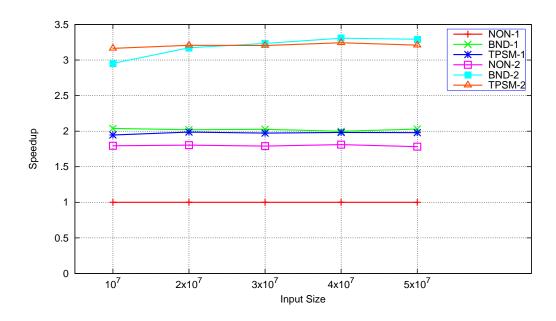

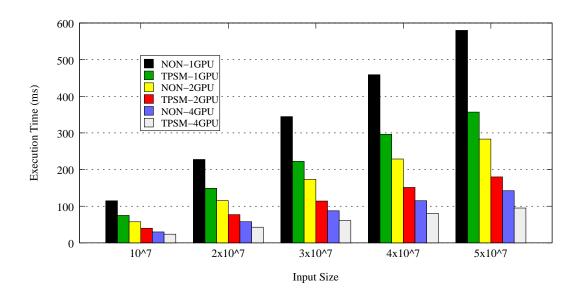

| 4.47 | Linear Filter Speedup Results in Non-symmetric Architecture $102$           |

| 4.48 | Linear Filter Results with Different Block Number in Non-symmetric          |

|      | Architecture                                                                |

| 4.49 | Linear Filter Speedup Results with Different Block Number in Non-           |

|      | symmetric Architecture                                                      |

| 4.50 | Sepia Filter Results in Non-symmetric Architecture                          |

| 4.51 | Sepia Filter Speedup Results in Non-symmetric Architecture $106$            |

| 4.52 | Black-scholes Results in Non-symmetric Architecture 106                     |

| 4.53 | Black-scholes Speedup Results in Non-symmetric Architecture $107$           |

| 4.54 | Matrix Multiplication Results in Non-symmetric Architecture $108$           |

| 4.55 | Matrix Multiplication Speedup Results in Non-symmetric Architecture 108     |

# List of Tables

| 3.1 | Time cost of PTX instructions in GTX 260 (unit: GPU clock)        | 15  |

|-----|-------------------------------------------------------------------|-----|

| 3.2 | The features of GPUs used in this work                            | 22  |

| 3.3 | Specification of The Machines                                     | 22  |

| 3.4 | The features of benchmarks used for Performance Prediction        | 22  |

| 3.5 | The Arithmetic Means of Accuracy for Each Benchmark               | 30  |

| 4.1 | The Type of Applications                                          | 39  |

| 4.2 | Bandwidth of Dual Tesla C2075 under Different States              | 56  |

| 4.3 | Bandwidth of Dual Non-symmetric GPUs under Different              |     |

|     | States(G0:Tesla K20c, G1:Tesla C2075)                             | 78  |

| 4.4 | Specification of The Host Machines                                | 82  |

| 4.5 | Specification of GPUs                                             | 83  |

| 4.6 | Benchmark Programs used for TPSM                                  | 83  |

| A.1 | Time cost of PTX instructions in GTX C2050 (unit: GPU clock) $$ . | 121 |

| A.2 | Bandwidth of Dual Tesla C2070 under Different States              | 122 |

| A.3 | Bandwidth of Dual Tesla M2090 under Different States              | 122 |

| A.4 | Bandwidth of Four Tesla M2090 under Different States              | 123 |

# List of Algorithms

| 1 | Algorithm for a good base value $a$           | 50 |

|---|-----------------------------------------------|----|

| 2 | Algorithm for finding out optimal hull subset | 79 |

# Introduction

### Contents

| 1.1 | Parallel Computing from CPU to CPU+GPU | 1 |

|-----|----------------------------------------|---|

| 1.2 | Motivation                             | 3 |

| 1.3 | Contributions                          | 4 |

### 1.1 Parallel Computing from CPU to CPU+GPU

Gordon Moor once predicted that the number of transistors placed on an integrated circuit will double every 18 to 24 months [85]. Until several years ago, Moor's law translated to increase in clock speed and performance which enable the same sequential program automatically gain performance just by using a faster hardware. The performance improvement for single thread is achieved by scaling up the speed and automatic exploitation of Instruction Level Parallelism (ILP).

Automatic extraction of instruction level parallelism from sequential programs is very limited [115, 116]. The scaling up of clock frequency stopped working in around 2005 because the memory speed could not catch up with the increase of processing capability. The power consumption also became very high. Therefore, people start to add more processing cores into a single microprocessor chip in order to exploit thread level parallelism to gain performance improvement.

Many desktop and notebook computers began to use dual core processors since 2006 and some high-end desktops and workstation computers began to use four core processors since 2008. Moreover, Graphic Processing Units (GPUs) which contain hundreds of processing cores are emerged. CPUs are also going into many-core period[22]. Processors in portable devices such as mobile phones also have been using multi-core processors for better power efficiency and performance.

Besides the increase of core count, people also begin to use heterogeneous cores in a single system for the demand to increase power efficiency[70]. Ultra-low Energy per Instruction (EPI) cores are very essential to scale multi-core processor to many-core processors [50]. With this consideration, computing system designers

combines heterogeneous processors to optimize the systems. Currently, most of super computer adopts a heterogeneous design which includes both multi-core CPUs and GPUs as co-processing units on each node of the super computer. With this design evolution, now mainly parallel systems have many processing cores with different processing characteristics. The CPUs with simultaneous multi-threading are used for running complex operating system software and task parallelism while the GPUs with hundreds or thousands of simpler cores are used for simple throughput computation task as shown in Figure 1.1 [45].

Figure 1.1: CPU + GPU heterogeneous system

The movement to massively parallel hardware leads to huge impact on software programmers. In the past, even a poorly written program can speed up with a faster hardware. With many-core hardware, however, the sequential programs can not be able to achieve better performance on parallel hardware unless the codes are properly parallelized.

Besides parallelism, programmers also need to pay attention to the characteristics of the heterogeneous processors. CPU cores are suitable for complex control flows and has limited throughput and poor power efficiency. GPU cores can work together to calculate simple computation with higher speed. Depending on different requirements on performance and energy efficiency, the cooperation between CPUs and GPUs to optimize power consumptions also is a hot research topic. Moreover, the memory access also greatly affects the performance as the hierarchical nature of memory system depends on the programs[105, 51].

The movement of parallel system from CPU based system to the system equipped both CPU and GPU and using GPU for acceleration (CPU+GPU system) brings high performance as well as new challenge.

1.2. Motivation 3

### 1.2 Motivation

Graphic Processing Unit (GPU) which is originally designed for acceleration of graphic applications now is widely used as General-Purpose Computing on Graphic Processing Units (GPGPU) to accelerate many scientific applications with more than ten or hundred times speedup over CPU platform. There are many programming languages to help programmers with writing parallel applications in GPU architecture such as Brook+ [24] CUDA [37] and OpenCL [89]. With these programming and architectural characteristics, programmers can easily port their programs to a GPU based system. However, further understanding at various features of the low level architecture and associated bottlenecks in the programs are required to achieve better performance in a GPU architecture. This will require programmers pay more energy on the implementation rather than the design of the parallel applications.

The motivation behind this thesis was caused by the emergence of high computational potential from GPU along with the difficulty of implementing high performance parallel programs in GPU platform. The interests of this thesis focus on performance prediction problem and communication latency problem between CPU and GPU.

For performance predication problem, I find that sometimes it is difficult to predict the performance of kernel codes on GPU as programmers do not have enough knowledge about the low level architecture. Therefore, programmers may use a unsuitable configuration to run their applications on GPUs which may lead to poor performance.

For example, the thread configuration can greatly affect the kernel performance on GPUs. Ideally it is thought that the performance of applications can be improved with more threads. However, the performance does not always increase along with the increase of thread number. There are many factors that can affect the performance such as the process clock, the bandwidth and application features. For computing bound applications that have more computing instructions than memory access instructions, increasing the number of threads will lead to a linear increase of performance. This is because more computing resources are used to compute with more threads. However, when the number of threads continue to increase and the utilization of GPU reaches the peak performance, the performance will decrease because of running out of computing resources and extra overhead from thread launching and synchronization. In this case, the limited computing capability is the performance bottleneck. For memory access bound applications that have more memory access instructions than computing instructions, there is a similar problem.

The bandwidth of global memory is limited while the increase of thread number will lead to the increase of bandwidth requirement from applications. In this case, the performance will increase first along with the increase of thread number and then it will decrease as bandwidth is used up and frequent switch between threads leads to extra overhead.

Therefore, it is very important to have a good understanding of the application and the architecture details to achieve high performance in GPU architecture. To release programmers from this burden, performance analytical model is required to help programmers implement better parallel programs in GPU architecture.

For the communication latency problem, the communication latency can be very significant for some applications which already greatly affect the total performance. As CUDA programs include two parts, the host codes run on CPU and the device codes run on GPU. The host codes invoke the device codes to execute kernel operation while the input and output streams are stored in the device memory. As the device memory (GPU memory) is separated from the host memory (CPU main memory), streams are required to be transferred between CPU and GPU which leads to the communication latency between them. In CUDA, stream includes a sequence of sequential execution commands such as send, kernel execution or receive. For some data transfer bound applications such as black-scholes (a benchmark that we will introduce in later), the communication latency can account for half of the total time cost in single GPU platform. In multiple GPU platform, the proportion of the communication latency in the total time cost becomes larger as the limited bandwidth is shared by all GPUs. Therefore, it is difficult to achieve high performance without awareness of the communication latency between CPU and GPU.

Notice that CUDA enables concurrent execution for data transfer and kernel execution. Also some latest NVIDIA Tesla series GPUs support two copy engines for bidirectional data transfer which means it is possible to launch data send, kernel execution and data receive simultaneously. With these new features, it is possible to hide the communication latency by overlapping.

#### 1.3 Contributions

The main research question that I aim to solve can be defined as the following questions:

- How to predict the performance of CUDA programs in GPUs?

- How to use efficiently the bandwidth between CPU and GPU in multiple GPU architecture?

• How to hide the communication latency between CPU and GPU?

In order to solve these questions, I am presenting performance optimization methods based on performance analytical modeling and communication latency hiding in GPU which includes a performance analytical model and a task partitioning and scheduling method.

To solve the first question, I propose a performance analytical model with instruction-level and thread-level parallelism awareness to predict the kernel execution time cost of CUDA program on GPU. I propose two definitions: CPD and MPD for the prediction of CUDA program on GPU. I introduce Computing Parallel Degree (CPD) to describe the parallel execution for computation instructions and to present the characteristic of applications. I also introduce Memory Parallel Degree (MPD) to describe the maximum number of memory accesses that can be executed concurrently. Based on the two definitions, the performance analytical model includes two submodels: memory submodel and computation submodel. The memory submodel uses MPD to estimate the time cost of memory instructions by considering the number of active threads and the GPU global memory bandwidth. The computation submodel uses CPD to estimate the time cost of computation instructions with awareness of active thread number and arithmetic intensity of applications. Based on the PTX codes generated from Ocelot [88], I develop a set of micro benchmark to test the time cost of PTX instructions. With the two submodels and time cost of PTX instructions as input, I use calculate model to estimate the time cost of overall kernel execution. I compare the predicted results with the actual execution results with four benchmarks in four kinds of GPUs, and the results show that the performance analytical model can achieve on average around 90% accurate rate.

To solve the second question, I propose a time optimal data transfer algorithm to achieve optimal data transfer between CPU and GPU in multiple GPU architecture (include symmetric and non-symmetric architecture). I propose a series of definitions to describe the status of GPUs and the whole system. I also introduce many notations to model the time cost of data transfer with mathematical methods. By finding the solution of the dual problem of time optimal data transfer problem, the time optimal data transfer can give out a optimal data transfer plan for a given data transfer input in multiple GPU architecture.

To solve the third question, I propose a *Task Partitioning and Scheduling Method* (TPSM) which can partition individual GPU application into subtasks and hide the communication latency between CPU and GPU by overlapping the data send part, kernel execution part and data receive part of different subtasks. Notice that it is very important to take the characteristic of application into consideration. Therefore, I propose a classification for GPU applications which classify GPU applications

into six basic types from computation-to-communication ratio aspect and send-to-receive ratio aspect. For each basic type, I propose a corresponding task partitioning and scheduling sub-method based on the characteristic of the type. I use the performance analytical model in TPSM to make suitable load allocation in multiple GPU non-symmetric architecture. I also use the time optimal data transfer algorithm in TPSM to improve the utilization of bandwidth between CPU and GPU. I use four benchmarks and four type GPUs to test my work and the results show that TPSM can well hide the communication latency between CPU and GPU. The results are very close to the lower bound results (the maximum time cost of data send part, kernel execution part and data receive part).

# Background

#### Contents

| 2.1 | CUDA Framework            | 7  |

|-----|---------------------------|----|

| 2.2 | GPU Architecture          | 9  |

| 2.3 | GPU Ocelot                | 10 |

| 2.4 | Divisible Load Scheduling | 11 |

In this chapter, we discuss the relevant details of the CUDA framework, the GPU architecture, GPU occlot and the divisible load scheduling.

### 2.1 CUDA Framework

Nvidia developed Compute Unified Device Architecture (CUDA)[37] in order to provide a more developer friendly environment for GPU application development. CUDA looks like an extension to the C language which provides access to all of the threading, memory and functions required by developers when working with the GPU.

The GPU device provides a tremendous level of exploitable parallelism within one single chip. A standard GPU contains hundreds of processing cores and support thousands, hundreds of thousands or even millions of threads being scheduled for execution. CUDA provides a number of levels of thread organization to make the management of all threads simpler. The top level of the thread organization is the thread grid. The thread grid includes all threads that will execute the GPU kernel. The thread grid is split into multiple equal size blocks named thread block. Users specify the organization of threads within a thread block and thread blocks within a grid. Therefore, we can organize and address threads in one, two or three dimensional fashion. We can also organize and address the blocks in the thread grid in the same way. Figure 2.1 shows an example of two dimensional organization.

In the lowest level of the thread organization is the *thread warp*. The thread warps are formed by equal sized chunks of threads within the block. The size of warp is determined by the hardware specifications and the threads within one warp

Figure 2.1: Grid of Thread Blocks

are ordered in a one dimensional fashion. For Tesla C2075, one warp includes 32 threads. GPU issues each thread within the warp the same instruction to execute. CUDA also provides some synchronization mechanisms based around the thread warp, block and grid. For the threads within one warp, they are always synchronized as they all receive the same instruction to execute. For block level synchronization, CUDA provides \_\_syncthreads() instruction. All threads reaching the instruction will wait until all threads in the block arrive this point. However, CUDA does not provide any mechanisms within kernel to synchronize all threads in a grid. Therefore, we have to complete execution of the kernel and depend on the CPU to perform the synchronization. CUDA provides two kind of methods for the kernel synchronization:

- Launching another kernel: After launch one kernel, launching another kernel will lead to the application halting until the previous kernel execution finish.

- cudaThreadSynchronize() instruction in CPU code: This has the same results but need to be controlled by users.

### 2.2 GPU Architecture

Here we will introduce the GPU architecture details combined with the CUDA framework information discussed in the previous section. GPU includes two separate units: the processing cores and the off-chip memory which is connected by a proprietary and undisclosed interconnection network. One GPU device normally compose several Streaming Multiprocessors (SMs). As shown in Figure 2.2, each SM contains eight cores or more (For Nvidia Tesla K20c, each SM contains 192 cores). These cores are the computational cores of the GPU and handle the execution of instructions for the threads executing within the SM. SMs also contain a multi-threaded instruction dispatcher and some special function units which provide extra transcendental mathematic capabilities.

Figure 2.2: GPU Architecture

Each SM executes the instructions in a SIMD (Single Instruction Multiple Data) pattern. And all threads within a thread block must execute entirely within a single SM which means the threads in a thread block can not be split up between multiple SMs. However, multiple thread blocks can be executed on a single SM only if the SM has enough resources to support the requirements of more than one thread block.

Each SM also has small shared memory which essentially acts as a user-controlled cache for data required during kernel execution. Therefore, users are responsible to place data into this memory space. There is no any automatic hardware data caching. Nvidia changed this in their Fermi architecture and introduced a hardware-controlled cache at each SM. The accesses to shared memory are up to 100 times faster than global memory without bank conflicts. As shared memory is split into 16 32-bit wide banks, multiple data requests from the same bank at the same time will cause bank conflicts so they are serialized. Bank conflicts reduce the overall shared memory throughput. Because some threads have to wait for the data until previous threads are serviced. Shared memory is exclusive to each thread block on a SM. Therefore, one thread block can not access the shared memory data from another thread block even within the same SM.

GPU device includes global memory which is the largest memory space available on the GPU and is accessible to all threads. Global memory accesses have significant latency and are not cached at any level. Therefore, each access to global memory results in the same latency hit. Each SM has access to caches for the constant and texture memory which are still technically part of global memory. These caches help to reduce the latency by exploiting data locality.

### 2.3 GPU Ocelot

GPU Ocelot [88, 39] is a dynamical compilation and binary translation infrastructure for CUDA which implements CUDA runtime API and executes PTX kernels on various backend execution targets. Ocelot contains a functional simulator for offline workload characterization, correctness checking and profiling. With an additional runtime execution manager, a translator from PTX to LLVM provides efficient execution of PTX kernels on multi-core CPUs. To support Ocelot's Nvidia GPU device, PTX kernels are launched and invoked via CUDA driver API. Ocelot can inspect the state of the application as it is running, transforming PTX kernels before executed natively on GPU devices. Ocelot also manages additional resources and data structures that are needed to support instrumentation.

Ocelot replaces the CUDA runtime API library linked with CUDA applications. Ocelot enables API calls to CUDA provide a layer of compilation support, resource management and execution. CUDA kernels may be modified by Ocelot as they are registered and launched. Ocelot will insert additional state and functionality into the host applications. Therefore, it is mainly designed for transparently instrument applications and respond to data dependent applications behaviors which is not possible for static transformation techniques. For instance, Ocelot can insert instrumentation into a kernel, profile for a brief period and ten re-issue the original kernel without instrumentation to implement random sampling while the application is running.

### 2.4 Divisible Load Scheduling

Scheduling is an important research area for a long time which is also one of the main area of contemporary mathematics. The origin of scheduling on operation research is mainly about production and project management [5, 12, 33]. As computer systems become more complex, scheduling is now an important part for the design of compilers and libraries [7, 94], operating systems [32, 110] and real-time systems [99, 101, 108, 121].

Since the computer systems come to parallel distributed systems which have high computing capabilities to process larger computation tasks, how to exploit its parallelism in these system is one major challenge. Programmers often focus on improving functional parallelism which means to identify and adapt the features of serial programs to be properly executed in parallel. For data intensive applications, there is another kind of parallelism named *data parallelism* which means large computational load can be distributed among available processing units and executed in parallel.

Parallel load distribution is mainly about the partitioning of single large load for one processing unit. If the large load is processed as a whole, the processing time may be unbearable. To reduce the total time cost, the large load can be partitioned and distributed among the processing units in the system. However, it is very important to have knowledge of data features and system to assure an appropriate data partitioning. *Divisible Load Theory* (DLT)[17] is used to study the problem of partitioning and sharing load in parallel systems.

Divisible load theory is a mathematical model which can enable performance analysis of parallel and distributed systems by including both communication and computation problems[28]. The divisible load scheduling theory uses a system of linear equations to define load distribution and provides many models which have lots of advantages such as the ease of computation, the use of a schematic language and the facility to be applied to different fields[102, 20, 21]. There are many studies

on the optimization of Divisible Load Scheduling (DLS) with DLT[8, 10, 11, 15, 16, 18, 112, 19, 35, 48, 47, 71, 119, 29, 52, 71, 81, 40, 111, 95, 106, 107, 120, 126].

However, the partitioning method depends on the load divisibility property which refers to the features that determine whether the load can be decomposed into a set of smaller ones[114]. The divisibility property classifies into indivisible and divisible. For divisible load, it can further classify into modularly divisible and arbitrarily divisible. On the one hand, the loads can be indivisible where the size of new pieces may be different and can not be further subdivided. Therefore, they do not have any precedence relations and need to be assigned and processed in single processor. On the other hand, the loads can be divisible including modularly divisible and arbitrary divisible.

A modularly divisible load can be divides into smaller modules based on the features of the load or the system. The load processing is completed when all the modules are processed and the processing of the modules should be subject to precedence relations. Normally such kind of loads are represented as interaction graphs tasks that the vertices correspond to the modules and the edges correspond to interaction between these modules and the precedence relationships.

For arbitrary divisible load, all the elements in the load can be processed in the same way. These kind of loads can be arbitrarily split into any number of load fractions. These fractions may or may not have precedence relationships. For example, the data can be arbitrarily partitioned but there may be a precedence relationship among the generated data chunks. Or if the data chunks do not precedence relationships, then each chunk can be processed independently.

The applications that satisfy the divisibility property include image processing applications, processing of massive experimental data, signal processing applications, matrix computations, tree and database search and Monte Carlo simulations. As the divisible load scheduling considers that both the communication and computation loads can be arbitrarily partitioned among the parallel system[96], it is suitable for modeling a large class of data intensive problems. Under this scheme it is possible to model and schedule load distribution for systems with GPU devices.

# Performance Analytical Model

| Contents | 5                         |                          |           |  |

|----------|---------------------------|--------------------------|-----------|--|

| 3.1      | Arcl                      | hitecture                | 13        |  |

| 3.2      | Asse                      | embly Code Analysis      | 14        |  |

| 3.3      | Exec                      | cution of Multiple Warps | <b>15</b> |  |

|          | 3.3.1                     | MPD submodel             | 17        |  |

|          | 3.3.2                     | CPD submodel             | 17        |  |

| 3.4      | Calc                      | culation Model           | 19        |  |

| 3.5      | 3.5 Experiment Evaluation |                          |           |  |

|          | 3.5.1                     | Configuration            | 21        |  |

|          | 3.5.2                     | Results                  | 23        |  |

# 3.1 Architecture

Figure 3.1: Performance Analytical Model Architecture

Our performance analytical model is based on the open source occlot and includes four parts: assembly code analysis, memory parallel degree model, compu-

tation parallel degree model and calculate models as shown in Figure 3.1. The assembly code analysis part is responsible for PTX code generating, PTX instructions time cost testing and PTX code information gathering. The memory parallel degree model is used to describe the parallel execution for memory access instructions. The computation parallel degree model is used to describe the parallel execution for computation instructions. The calculate models will use the information from previous three parts to prediction the time cost of the total kernel execution.

### 3.2 Assembly Code Analysis

Parallel Thread Execution(PTX)[36] is a pseudo-assembly language used in Nvidia CUDA programming environment. The NVCC compiler translates the CUDA programs into PTX codes, and the GPU driver has a compiler which translates the PTX codes into machine codes to execute on GPUs. By analyzing the PTX codes, we can have a deep insight into the performance bottlenecks in GPU architecture.

With the help of ocelot, many details of PTX codes from CUDA program can be obtained. As shown in Figure 3.2, we can generate PTX codes from CUDA codes with ocelot. Therefore, we can design two CUDA kernels : Kernel A and kernel B that there only exists one PTX instruction difference between the two corresponding PTX codes. Then we can test the time cost of the PTX instruction by running the Kernel A and B and calculating the time difference. We design a set of micro

```

__global__void sampleKernel(double* a)

{

a[threadIdx.x]+=threadIdx.x;

}

```

```

cvt.u32.u16 %r0, %tid.x

memory size 0

mul24.lo.u32 %r1, %r0, 8

memory size 0

ld.param.u32 %r2,

cudaparm Z12sampleKernelPd a]

memory size 4

add.u32 %r3, %r2, %r1

memory size 0

cvt.rn.f64.u32 %r4, %r0

memory size 0

ld.global.f64 %r5, [%r3+0]

memory size 8

add.f64 %r6, %r4, %r5

memory size 0

st.global.f64 [%r3+0], %r6

memory size 8

```

(b)PTX code

(a)CUDA code

Figure 3.2: PTX code generated from CUDA code with ocelot

|       | int_const | int_reg | float_const | float_reg |

|-------|-----------|---------|-------------|-----------|

| add   | 22        | 65      | 22          | 65        |

| sub   | 22        | 65      | 22          | 65        |

| mul   | 44        | 136     | 22          | 65        |

| div   | 728       | 753     | 748         | 783       |

| neg   | 22        | 22      | 17          | 17        |

| min   | 62        | 62      | 62          | 62        |

| max   | 62        | 62      | 62          | 62        |

| and   | 64        | 64      | 64          | 64        |

| or    | 62        | 62      | 62          | 62        |

| xor   | 62        | 62      | 62          | 62        |

| not   | 22        | 22      | 22          | 22        |

| shl   | 22        | 63      | 22          | 63        |

| shr   | 22        | 63      | 22          | 63        |

| mv    | 40        | 40      | 40          | 40        |

| cvt   | 22        | 22      | 22          | 22        |

| ld/st | 200       | 200     | 200         | 200       |

Table 3.1: Time cost of PTX instructions in GTX 260 (unit: GPU clock)

benchmarks to test the time cost of PTX instructions and Table 3.1 shows the time cost of PTX instructions in NVIDIA GTX 260.

## 3.3 Execution of Multiple Warps

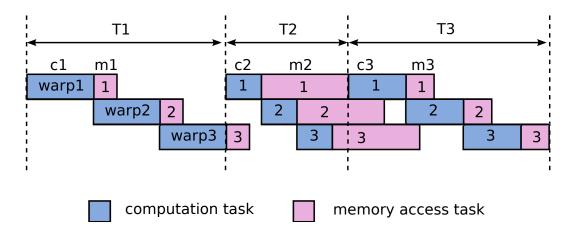

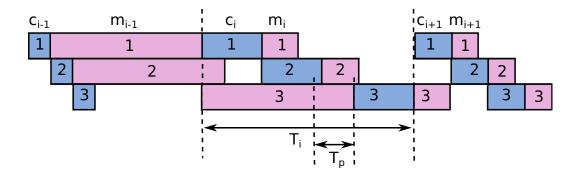

To explain how the execution of multiple warps in each SM affects the total execution time, we use a typical scenario to illustrate as shown in Figure 3.3. For each warp, the PTX codes can be considered as an instruction queue of computation instructions and memory access instructions. We define a set of continuous computation instructions in one warp as a **computation task**. Similarly, we also define a set of continuous memory access instructions in one warp as a **memory access task**. With these definitions, the PTX codes can be considered as a crossed permutation of computation tasks and memory access tasks. The time period from the beginning of the ith computation task to the beginning of the (i + 1)th computation task in one warp is called **the** ith **calculate period**. The time cost of the ith calculate period is  $T_i$ . Here our model firstly assume that one SM can only execute one warp in one time and the computation task can not be executed in parallel. (We will discuss the parallel execution of computation task in CPD submodel). Therefore,

Figure 3.3: Multiple Warps Execution in GPU Architecture

the computation tasks between warps cannot be paralleled. However, the memory access tasks between warps can be executed in parallel. During the memory access waiting time, another active warp will be swapped to execute until the next memory access arrive.

Figure 3.4: The Execution of Multiple Warps with MPD Awareness

#### 3.3.1 MPD submodel

MPD is the Memory access Parallel Degree which is used to present the maximum warp number that can be executed in parallel. The MPD can greatly affect the total execution time. Here, we assume that there is no parallel execution for computation task. The value of MPD can be affected by the bandwidth of GPU device, the bandwidth used by each warp, the number of active warps in each SM and the number SMs in the GPU device. In one word, MPD means how many warps with memory access instructions can be executed in parallel under a limited bandwidth of device memory.

For example as shown in Figure 3.4, when there are not enough warps to execute or the value of MPD is very low (an extreme example is 1), the execution process would be serial execution like the case 1. When there are enough warps to execute and the value of MPD is very high (the value of MPD is higher than the number of active warps), the execution process would be like case 2. With high MPD, the latency of each memory access can be hidden by executing multiple memory access concurrently.

For each memory access task, we introduce the following equations to calculate MPD:

$$Warp_{bwt} = (N_{thread} * D_{mem})/(N_{trans} * t_{mem}), \tag{3.1}$$

$$MPD = \min\{N_{act}, \lfloor GPU_{bwt}/(N_{act} * N_{sm} * Warp_{bwt}) \rfloor\}.$$

(3.2)

$N_{thread}$ : the number of threads in one warp, in this paper is 32;

$D_{mem}$ : the data size required for each thread during each memory access;

$N_{trans}$ : the number of memory transactions for each memory access instruction;

$N_{act}$ : the number of active warps in one SM;

$N_{sm}$ : the number of active SMs;

$t_{mem}$ : the latency of memory access;

$Warp_{bwt}$ : the bandwidth used by one warp during one memory access;

$GPU_{bwt}$ : the bandwidth of GPU device.

We obtain the memory access addresses of half-warp threads with ocelot[88] and calculate the number of memory transactions by following the rule of the generation of memory transaction in PTX 1.4[36].

### 3.3.2 CPD submodel

**CPD** is the computation parallel degree which is used to present the parallel execution between warps and within warps in one SM. The parallel executions for the computation instructions in GPU are so complex that it is hard to give a perfect model to present. Many factors can affect the parallel execution degree such

as the relationship of adjacent instructions, instruction types, computing resource requirements, the number of warps and the features of applications. To simplify the model, we only take the number of warps and the features of applications into consideration.

We use **computation instruction proportion** in the PTX codes to present the features of applications which is defined as follows:

$$P = T_{cmp}/(T_{cmp} + T_{mem}). (3.3)$$

P: the computation instruction proportion;

$T_{cmp}$ : the sum of the time cost of all computation instructions;

$T_{mem}$ : the sum of the time cost of all memory access instructions. When the computation instruction proportion is very low, the increase of the number of warps will lead to the increase of parallel execution of computation instructions. With more warps, the number of computation instructions which can be executed in parallel will show a linear increase. Because of the low computation instruction proportion, the computing resources are always available to execute computation instructions in parallel. On this reasoning, we propose the following equation to calculate the CPD:

$$CPD1 = (c - P) * (N_{act} - b) + a.$$

(3.4)

$a,\,b$  and c: the empirical parameters which get from each specific GPU device. (We write a micro benchmark to obtain these parameters. In GTX 260, a is set to 3, b is set to 11 and c is set to 0.5.)

The GPU will schedule warps to execute once there are spare computing resources. When the computation instruction proportion is high enough, the increase rate of the CPD will decrease along with a big enough warp number. Although the increase of warps leads to a linear increase of computation instructions that can be parallelized, the available computing resources become fewer and the increase rate of computation instructions that have enough computing resource to execute in parallel decreases. Therefore, when all computing resources are used up, the CPD will come to a limitation. In this situation, we use the following equations to calculate the CPD:

$$CPD2 = (n/(m-1)) * \sqrt{(m-1)^2 - (N_{act} - m)^2} + a,$$

(3.5)

$$n = d * (P - c)^2. (3.6)$$

m: the maximum warp number that can be executed in GPU;

d: the empirical parameters which get from each specific GPU device.

We write a micro benchmark to obtain the parameter and d is set to 80 in GTX260. Therefore, the final value of CPD for a specific number of warps is equal to min $\{CPD1, CPD2\}$ . Notice that our CPD model is an empirical model as we do not know the details of the computing instruction execution. Based on black box testing, we have current CPD model.

#### 3.4 Calculation Model

So far, we have explained the execution of multiple warps and two submodels. In this section, we put them all together into the prediction model to predict the total time cost of the execution. Notice that each block will be assigned to a SM for the execution. The execution of computation instructions between SM is relatively independent. The execution of memory access instructions can affect each other between SM as the local memory bandwidth is shared by all SMs. We have considered the factors in the previous two submodels. The total time cost of an application in GPU is equal to the time cost of SM which has the longest execution time cost. Therefore, to simplify the prediction, we can only consider the single block execution in one SM.

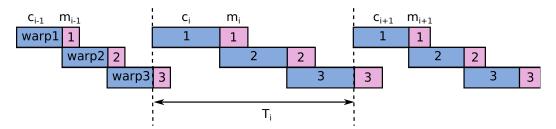

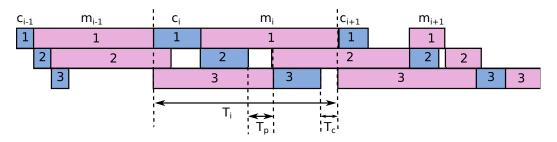

By analyzing the PTX codes, we can calculate the time cost of each calculate period and sum them up to get the total time cost. The calculate methods for each calculate period may be different due to long memory access waiting from current calculate period or previous calculate period. Ideally we hope the processors always have instructions to execute. However, long memory access tasks can let the processors wait because the following computation tasks need the results from the previous memory access tasks. Therefore, according to whether the calculate period has been affected, we classify the calculate periods into four types. We can analyze the relationships between time cost of computation tasks and memory access tasks in current period and previous period to select a corresponding type.

Figure 3.5: Calculate Period Type 1

As Figure 3.5 shows, the type 1 is that there is no long memory access waiting

influence from current period and previous period which means  $c_{i-1} \geq m_{i-1}$  and  $c_i \geq m_i$ . Here, the parameters are defined as follows:

$c_i$ : the time cost of computation task in the *i*th calculate period;

$m_i$ : the time cost of memory access task in the *i*th calculate period;

$T_i$ : the time cost of the *i*th calculate period.

Therefore, only the computation tasks make contribution to the total time cost. We sum up the time cost of all computation tasks while the parallel execution of computation parts should also be taken into consideration. We can use the following equation to calculate the *i*th calculate period time cost:

$$T_i = \lceil (N_{act} * c_i)/CPD \rceil. \tag{3.7}$$

Figure 3.6: Calculate Period Type 2

In type 2,  $c_{i-1} \ge m_{i-1}$  and  $c_i < m_i$  as illustrated in Figure 3.6. The long memory access tasks in current period will cause a waiting period between the last computation task in current period and the first computation task in the following period. In this case, we can use the following equations to calculate the *i*th calculate period time cost:

$$T_i = \lceil (N_{act} * c_i)/CPD \rceil + T_c, \tag{3.8}$$

$$T_c = \max\{m_i - (n-1) * c_i, 0\}. \tag{3.9}$$

$T_c$ : the extra time cost caused by the long memory access tasks in current period.

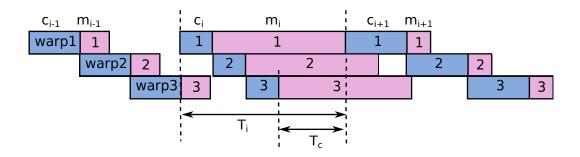

In type 3,  $c_{i-1} < m_{i-1}$  and  $c_i \ge m_i$  as illustrated in Figure 3.7. The long memory access tasks in previous period will cause a waiting time between the execution of computation tasks in current period because the results of memory access task in previous period do not arrive. Therefore, we can use the following equations to calculate the *i*th calculate period time cost:

$$T_i = \lceil (N_{act} * c_i)/CPD \rceil + T_p, \tag{3.10}$$

$$T_p = \max\{m_{i-1} * | (N_{act}/MPD) - 1 | - (N_{act} - 1) * c_i, 0\}.$$

(3.11)

Figure 3.7: Calculate Period Type 3

Figure 3.8: Calculate Period Type 4

$T_p$ : the extra time cost caused by the long memory access task in previous period. In type 4,  $c_{i-1} < m_{i-1}$  and  $c_i < m_i$  as illustrated in Figure 3.8. The long memory access tasks from current period and previous period both make extra time

memory access tasks from current period and previous period both make extra time cost in the current calculate period. We can use the following equations to calculate the *i*th calculate period time cost:

$$T_i = \lceil (N_{act} * c_i)/CPD \rceil + T_p + T_c, \tag{3.12}$$

$$T_p = \max\{m_{i-1} * \lfloor (N_{act}/MPD) - 1 \rfloor - (N_{act} - 1) * c_i, 0\},$$

(3.13)

$$T_c = \max\{m_i - ((N_{act} - 1) * c_i + T_p)\}. \tag{3.14}$$

Finally, we can calculate the time cost for each calculate period according to the different scenarios and sum up to obtain the total time cost.

### 3.5 Experiment Evaluation

#### 3.5.1 Configuration

The GPUs used in our experiments are shown in Table 3.2. We have to big machines as shown in Table 3.3. We install GTX 260 and Tesla C2050 in machine AT38 and

install Telsa C2075 and Tesla K20c in machine AT50. We use cudaEventRecord API in CUDA 4.2 to measure the execution time of GPU kernels. All the benchmarks are compiled with NVCC.

To test the performance of our prediction model, we use four different benchmarks that are mostly used in Linderman's work[78] and we port them from multicore platform to GPU platform. The benchmarks used in our work are explained in Table 3.4. The computation instruction proportions of the four benchmarks are different from very low 26.23% to very high 86.97%. We use these in the hope of proving our model can have good prediction results in various applications. We compare our predicted results with the actual test results. The abbreviations used in the Figures are as follow:

test: the results from the actual execution in GPU;

model: the results from our performance model prediction.

Table 3.2: The features of GPUs used in this work

| features                 | GTX 260 | Tesla C2050 | Tesla C2075 | Tesla K20c |

|--------------------------|---------|-------------|-------------|------------|

| the number of SPs        | 192     | 448         | 448         | 2496       |

| CUDA core frequency(MHz) | 1242    | 1150        | 1150        | 710        |

| Memory size              | 896 MB  | 3 GB        | 6GB         | 4800MB     |

| Memory bandwidth(GB/s)   | 111.9   | 144         | 144         | 208        |

| Peak Tflop/s             | 1.43    | 1.03        | 1.03        | 3.5        |

| (double precision)       | 1.40    | 1.03        | 1.05        | J.J        |

Table 3.3: Specification of The Machines

| machine | Device                 | Cores | Clock speed        | Cache | Main Memory    |

|---------|------------------------|-------|--------------------|-------|----------------|

| AT38    | 4 x Intel Xeon X5650   | 4 x 6 | $2.67\mathrm{GHz}$ | 12MB  | $6 \times 2GB$ |

| AT50    | 2 x Intel Xeon E5-2680 | 2 x 8 | 2.7GHz             | 20MB  | 8 x 8GB        |

Table 3.4: The features of benchmarks used for Performance Prediction

| benchmarks        | description                          | input size       | com proportion |

|-------------------|--------------------------------------|------------------|----------------|

| Matrix            | Matrix multiple                      | $256\times256$   | 28.2%          |

| Linear[78]        | Image filter to compute 9-pixels avg | $800 \times 800$ | 45.84%         |

| Sepia[78]         | Filter for artificially aging images |                  | 52.97%         |

| Black-scholes[78] | bles[78] European option pricing     |                  | 86.97%         |

#### 3.5.2 Results

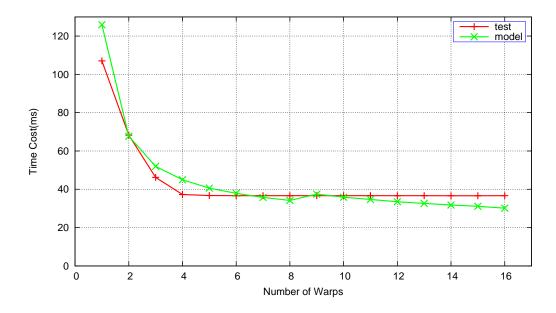

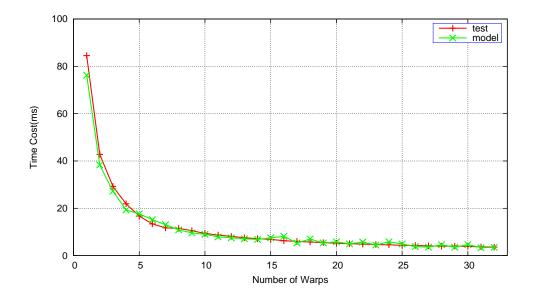

As GTX 260 and Tesla C2050 are old GPUs and Tesla C2075 and Tesla K20c are much newer than the previous two, the maximum thread numbers of Tesla C2075 and Tesla K20c are larger than GTX 260 and Tesla C2050. We change the number of warps to run the kernel with the same data size. For GTX 260 and Tesla C2050, we vary the number of warps from 1 to 16. For Tesla C2075 and Tesla K20c, we vary the number of warps form 1 to 32. Besides comparing the execution time cost with the prediction results, we also discuss about the accuracy. We define the accuracy as follow:

$$P_{acc} = \min\{T_{test}, T_{model}\} / \max\{T_{test}, T_{model}\}. \tag{3.15}$$

$P_{acc}$ : the accuracy for a specific number of warps;

$T_{test}$ : the time cost for a specific number of warps from actual measured results;  $T_{model}$ : the time cost for a specific number of warps from predicted results.

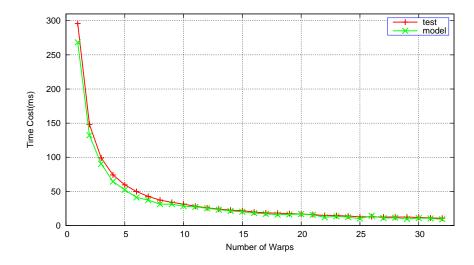

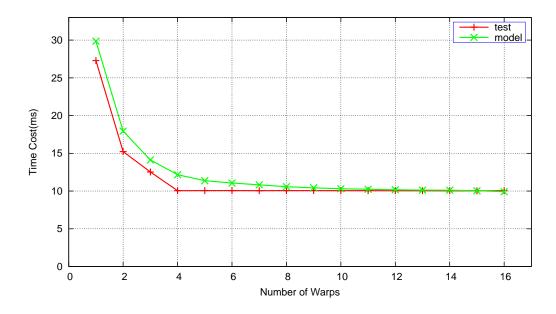

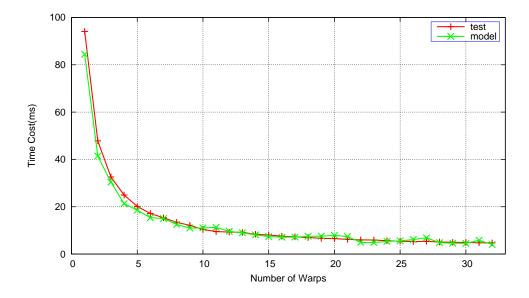

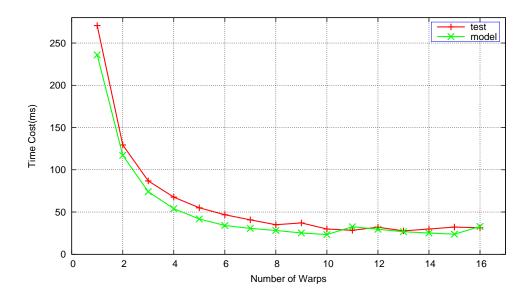

Figure 3.9: Linear Filter Results in GTX260

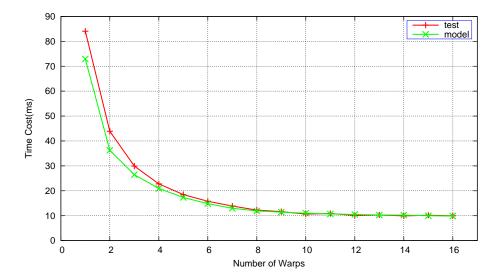

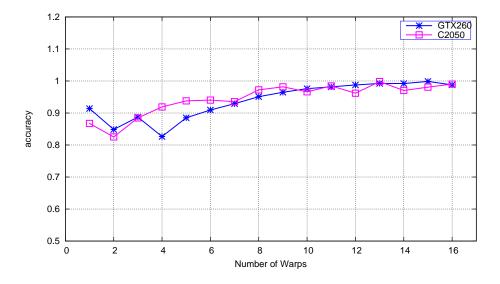

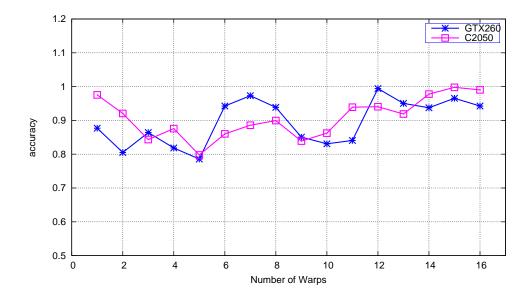

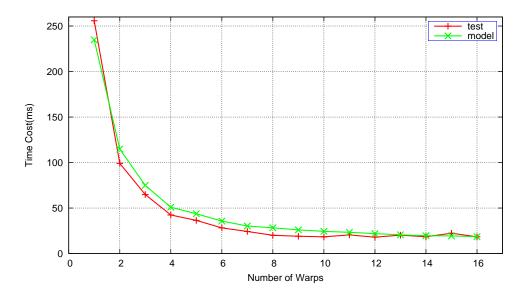

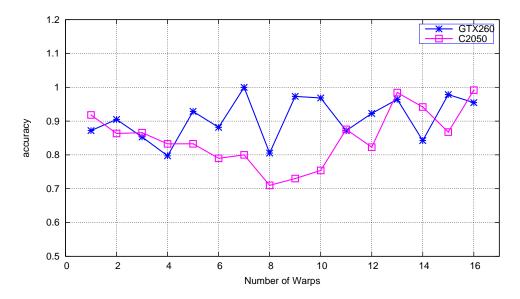

First of all, we use linear filter benchmark to test our work in the four type GPUs. The computation instruction proportion of linear filter benchmark is 45.86%. The execution results of GTX 260 and Tesla C2050 are shown in Figure 3.9 and Figure 3.10. The accuracy results of GTX 260 and Tesla C2050 are shown in Figure 3.11. We can find the performance of GTX 260 is much faster than Tesla C2050.

With our performance model, the average accuracy of GTX 260 is 91.18% while the average accuracy of Tesla C2050 is 89.52% as shown in Table 3.5. As we have

some error factors in the performance model such as the empirical CPD model, we can hardly achieve perfect prediction. Due to lack of cache simulation, the prediction accuracy of Tesla C2050 is poorer than GTX 260 because GTX 260 has no cache while Tesla C2050 has.

Figure 3.10: Linear Filter Results in Tesla C2050

Figure 3.11: The Accuracy of Linear Filter in GTX260 and Tesla C2050  $\,$

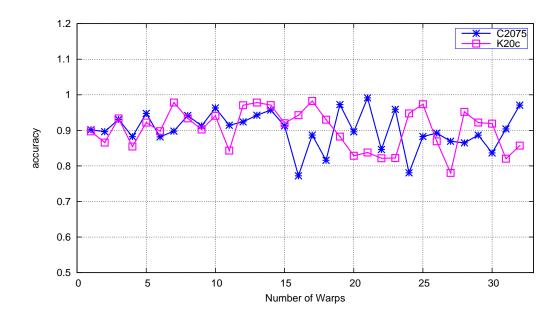

Figure 3.12: Linear Filter Results in Tesla C2075

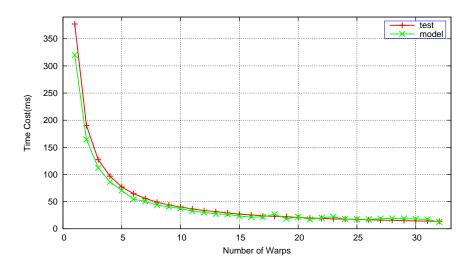

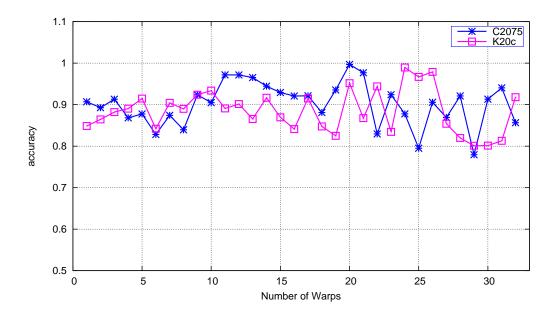

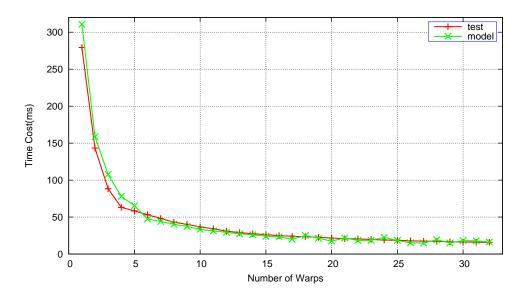

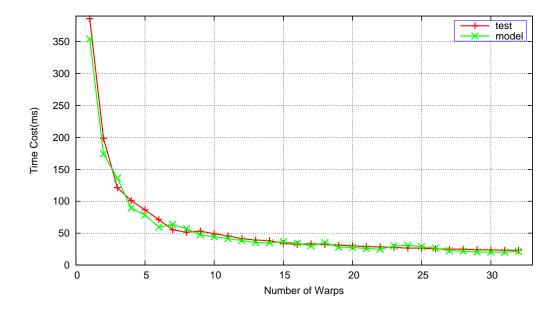

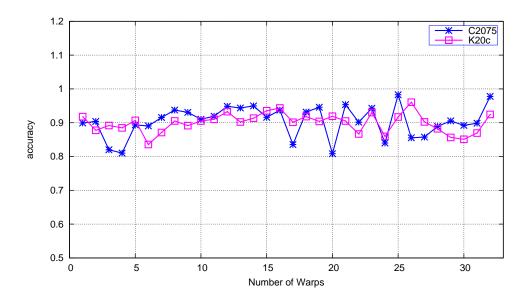

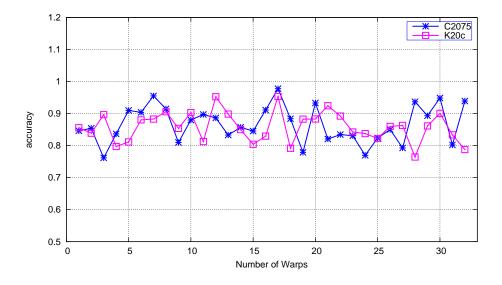

We also repeated the experiments in Tesla C2075 and Tesla K20c which is much newer than the previous two GPUs. The execution results of Tesla C2075 and Tesla K20c are shown in Figure 3.12 and Figure 3.13. The accuracy results of Tesla C2075 and Tesla K20c are shown in Figure 3.14. Although the peak performance of K20c is much better than C2075, the GPU frequency of K20c is slower than C2075. Therefore, the execution of C2075 is faster than K20c with the same thread configuration. The average accuracy of C2075 is 90.17% while the average accuracy of K20c is 89.46%.

Figure 3.13: Linear Filter Results in Tesla K20c

Figure 3.14: The Accuracy of Linear Filter in Tesla C2075 and Tesla K20c  $\,$

Figure 3.15: Sepia Filter Results in GTX260

Figure 3.16: Sepia Filter Results in Tesla C2050

Then we use sepia filter benchmark to test our performance model. The computation instruction proportion is 52.97% which is a little higher than linear filter benchmark. First of all, we test our work in the two old GPUs. The execution time results are shown in Figure 3.15 and Figure 3.16 and the accuracy results are shown in Figure 3.17. The average accuracy for GTX 260 is 93.94% and 94.47% in Tesla C2050 which is much higher than linear filter. This is because the influence of cache decreases due to high computation instruction proportion.

Figure 3.17: The Accuracy of Sepia Filter in Two GPUs

Figure 3.18: Sepia Filter Results in Tesla C2075

We repeated the sepia filter experiments in Tesla C2075 and Tesla K20c. The execution time results are shown in Figure 3.18 and Figure 3.19 and the accuracy results are shown in Figure 3.20. The average accuracy of Tesla C2075 is 91.1% and the average accuracy of Tesla K20c is 91.3%. This results show we can have a good prediction in the new GPU as well.

Figure 3.19: Sepia Filter Results in Tesla K20c

Figure 3.20: The Accuracy of Sepia Filter in Tesla C2075 and Tesla K20c  $\,$

Figure 3.21: Black-scholes Results in GTX 260

Figure 3.22: Black-scholes Results in Tesla C2050

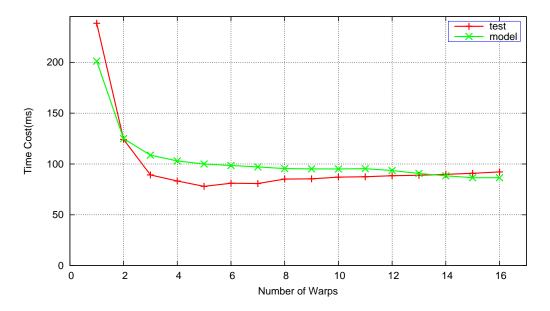

We also use black-scholes benchmark which has 86.97% high computation instruction proportion to test our work. First of all, we test in the two old GPUs. The execution results are shown in Figure 3.21 and Figure 3.22 and the accuracy results are shown in Figure 3.23.

We can find that the execution decreases along with the increase of warp numbers and finally comes to a limitation. This is because there are enough computing resources for all threads when the number of threads is small. Therefore, the increase of thread number can improve the performance as more data are processed in parallel. However, when the number of threads is very large, there are no enough computing resources to support all thread execution. This results in resources waiting for some threads.

Table 3.5: The Arithmetic Means of Accuracy for Each Benchmark

| benchmarks   | linear filter | sepia filter | black-scholes | matrix |

|--------------|---------------|--------------|---------------|--------|

| GTX260(100%) | 91.18         | 93.94        | 89.48         | 90.73  |

| C2050(100%)  | 89.52         | 94.47        | 90.78         | 84.87  |

| C2075(100%)  | 90.17         | 91.11        | 90.44         | 86.62  |

| K20c(100%)   | 89.46         | 91.3         | 89.97         | 85.86  |

Figure 3.23: The Accuracy of Black-scholes in Two GPUs

Our performance model can well predict the kernel execution no matter the number of thread is large or small. The average accuracy of GTX 260 is 89.48% and the average accuracy of Tesla C2050 is 90.78%. Here the accuracy of Tesla C2050 is better than GTX 260. That is because the influence of cache hit is very low as the memory access instruction proportion of black-scholes is very low.

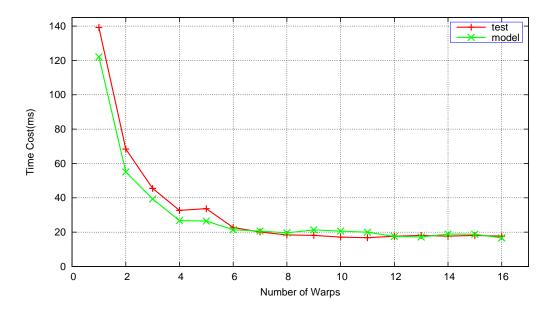

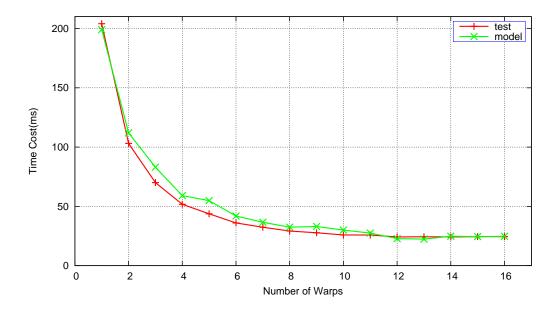

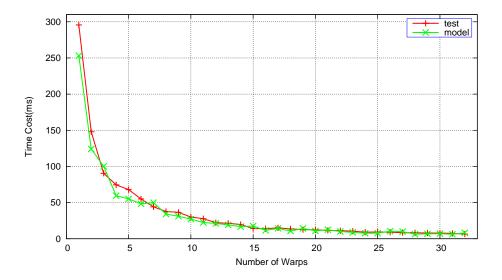

Figure 3.24: Black-scholes Results in C2075

Then we repeat the black-scholes experiments in Tesla C2075 and Tesla K20c. The execution time results are shown in Figure 3.24 and Figure 3.25 and the accuracy results are shown in Figure 3.26. The average accuracy of Tesla C2075 is 90.44% and the average accuracy of Tesla K20c is 89.97%.

Figure 3.25: Black-scholes Results in Tesla K20c

Figure 3.26: The Accuracy of Black-scholes in Tesla C2075 and Tesla K20c

Finally we use matrix multiplication benchmark to test our work. The computation instruction proportion of matrix multiplication is 28.2% which is the lowest in all benchmarks used in this thesis. The execution time results of GTX 260 and Tesla C2050 are shown in Figure 3.27 and Figure 3.28 and the accuracy results are shown in Figure 3.29.

Figure 3.27: Matrix Multiplication Results in GTX260

Figure 3.28: Matrix Multiplication Results in Tesla C2050

The average accuracy of GTX 260 is 90.73% while the average accuracy of Tesla C2050 is 84.87%. As matrix multiplication benchmark is memory access bound, the cache hits can greatly affect the performance. Without cache simulation, our performance model can hardly have the same prediction results in GPUs with cache comparing to GPUs without cache.

Figure 3.29: The Accuracy of Matrix Multiplication in Two GPUs

Figure 3.30: Matrix Multiplication Results in Tesla C2075

We repeat the matrix multiplication benchmark in Tesla C2075 and Tesla K20c. The execution time results are shown in Figure 3.30 and Figure 3.31 and the accuracy results are shown in Figure 3.32. The average accuracy of Tesla C2075 is 86.62% and the average accuracy of Tesla K20c is 85.86%. The accuracy of Tesla C2075 and Tesla K20c is not as good as the accuracy of GTX 260 due to cache.

Figure 3.31: Matrix Multiplication Results in Tesla K20c

Figure 3.32: The Accuracy of Matrix Multiplication in Tesla C2075 and Tesla K20c

# A Task Partitioning and Scheduling Method

| Contents | 5              |                                                             |           |

|----------|----------------|-------------------------------------------------------------|-----------|

| 4.1      | App            | olication Classification                                    | 37        |

| 4.2      | TPS            | SM for Single GPU Architecture                              | 39        |

|          | 4.2.1          | Partitioning and Scheduling for Kernel Bound Applications . | 40        |

|          | 4.2.2          | Partitioning and Scheduling for Data Transfer Bound Appli-  |           |

|          |                | cations                                                     | 47        |

| 4.3      | TPS            | SM for Symmetric Multiple GPUs Architecture                 | <b>55</b> |

|          | 4.3.1          | Time Optimal Data Transfer Algorithm for Symmetric Multi-   |           |

|          |                | ple GPUs Architecture                                       | 55        |

|          | 4.3.2          | TPSM                                                        | 62        |

| 4.4      | TPS            | SM for Non-symmetric Multiple GPUs Architecture             | 77        |

|          | 4.4.1          | Time Optimal Data Transfer Algorithm for Non-symmetric      |           |

|          |                | GPUs Architecture                                           | 78        |

|          | 4.4.2          | TPSM                                                        | 80        |

| 4.5      | $\mathbf{Exp}$ | erimental Evaluation                                        | 82        |

|          | 4.5.1          | Symmetric Architecture                                      | 83        |

|          | 4.5.2          | Non-symmetric Architecture                                  | 100       |

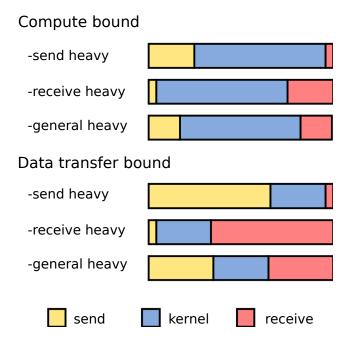

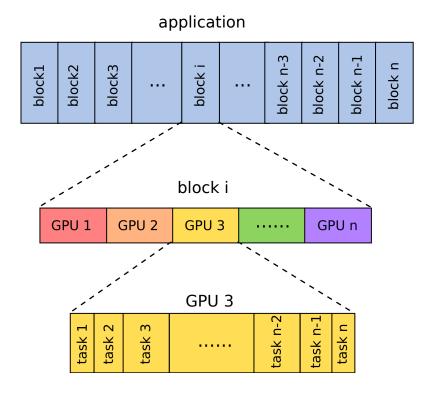

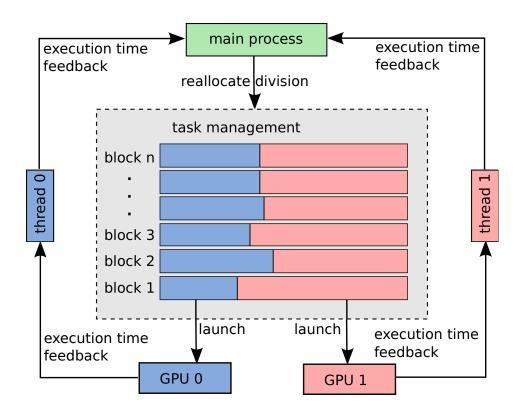

To have good partitioning and scheduling, we need to take the characteristic of applications into consideration. Also we need to notice that the limited bandwidth between CPU and GPU is shared by all GPUs in multiple GPU architecture. Therefore, we propose an application classification and a time optimal data transfer algorithm besides the task partitioning and scheduling method in this section.

## 4.1 Application Classification

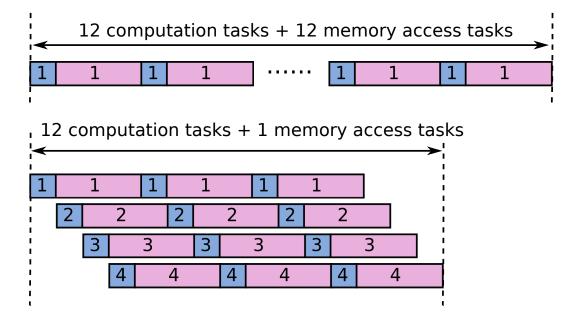

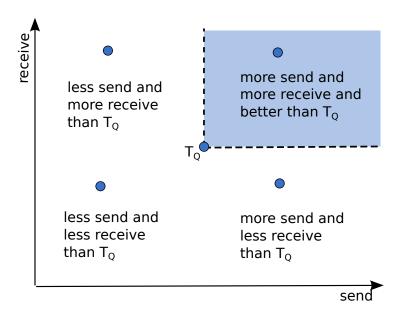

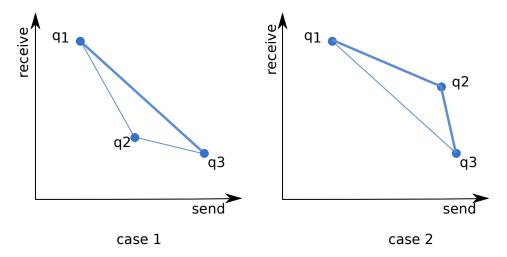

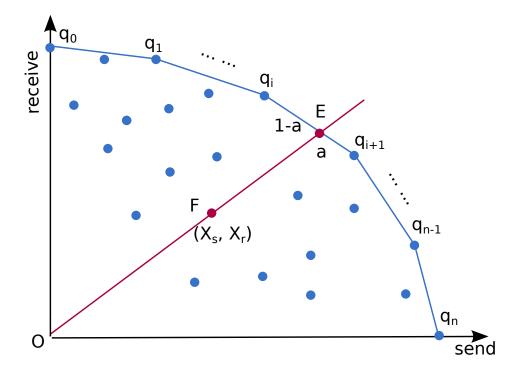

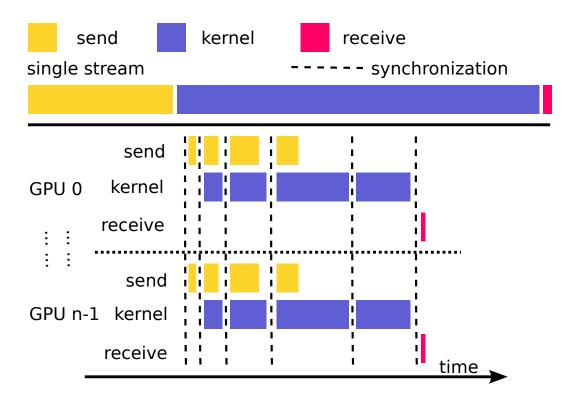

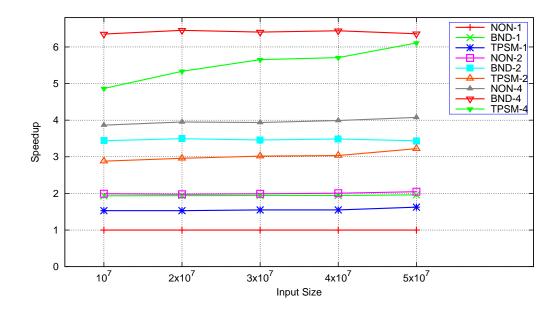

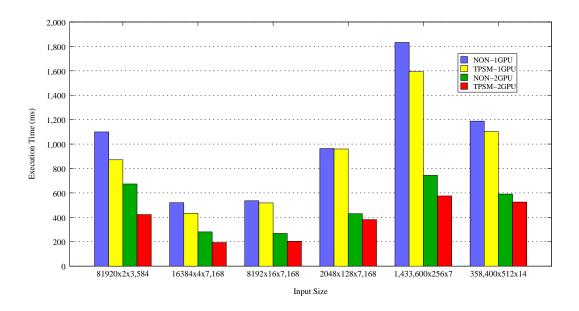

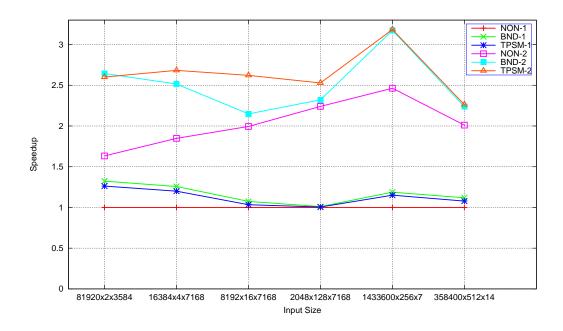

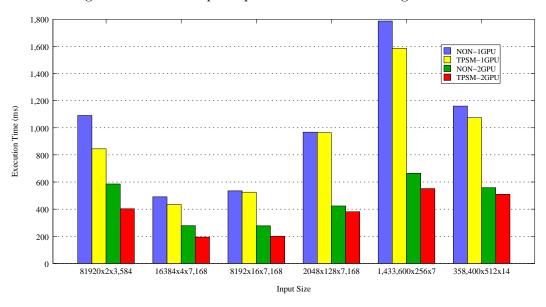

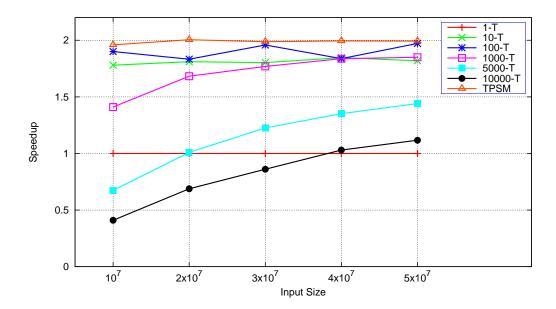

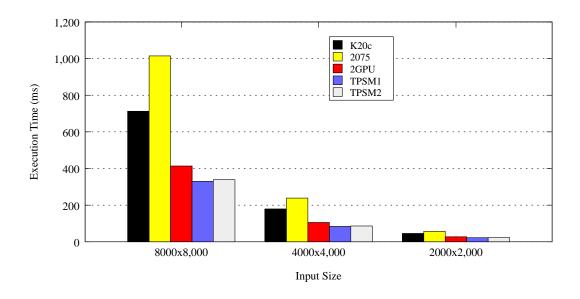

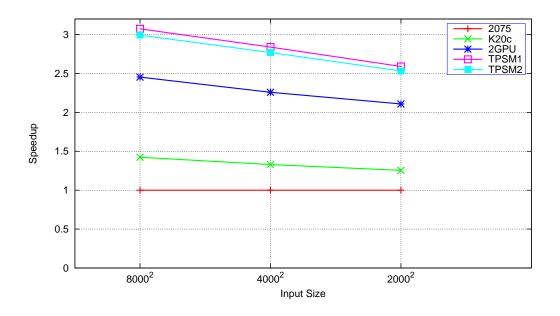

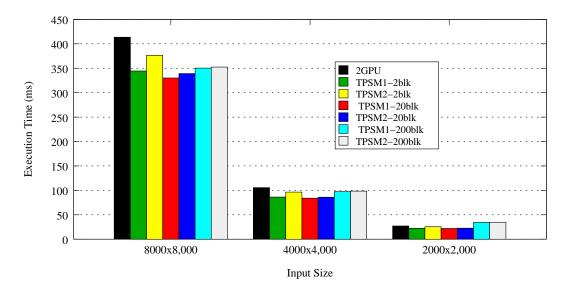

It is important to analyze the features of applications for achieving high performance. The GPGPU applications are classified into several basic types. For the

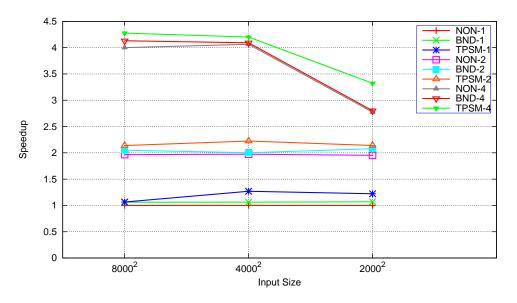

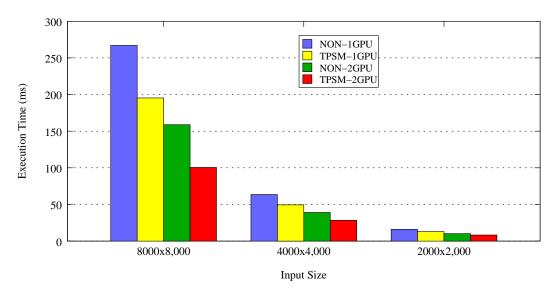

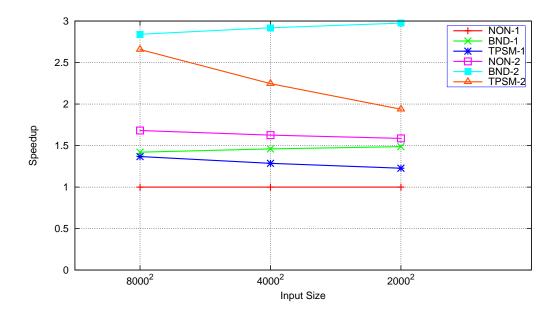

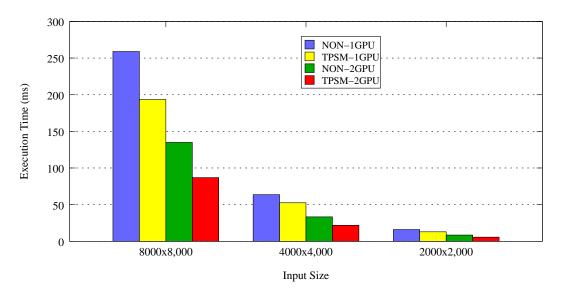

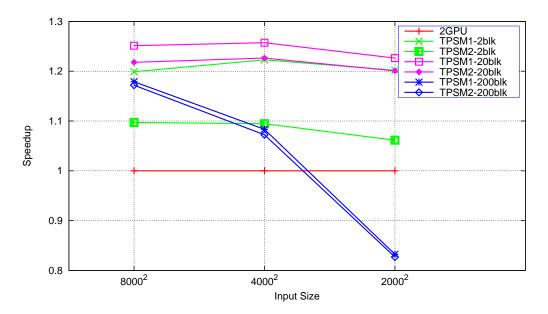

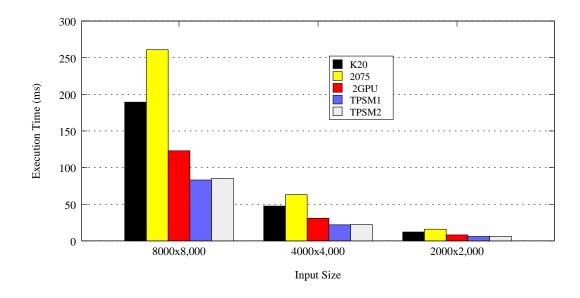

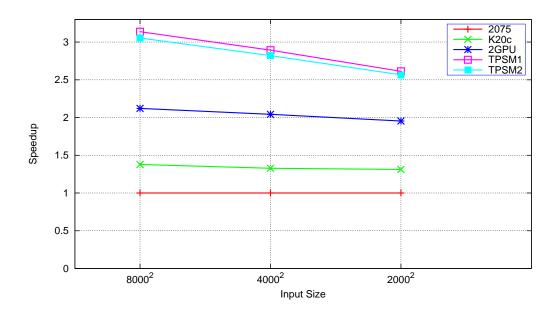

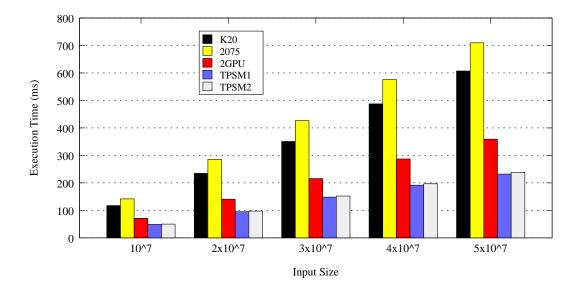

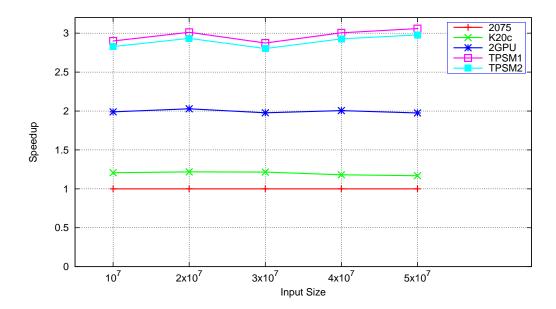

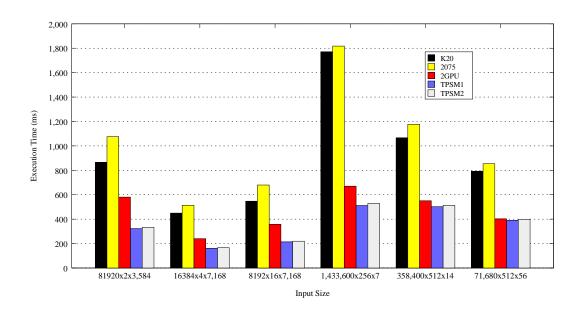

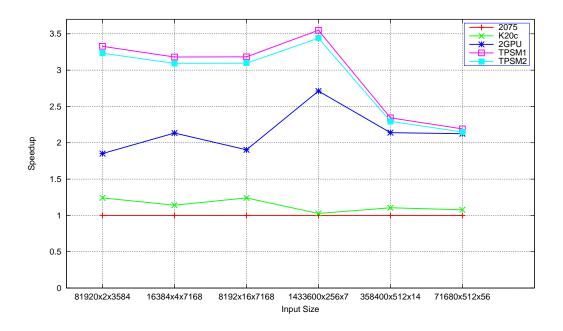

classification, the computation-to-communication ratio of applications and the send-to-receive ratio of applications are taken into consideration as shown in Figure 4.1.